SPICE运行收敛问题探索

pspice不收敛问题总结

3.1 PSPICE中555多谐振荡器不能起振的原因分析分析可知,PSPICE中555多谐振荡器不能起振的原因在于起振源,实际振荡电路之所以能自行起振是由于起振源的存在。

实际振荡电路的起振源主要由两方面因素构成:一是由振荡电路晶体管内部的噪声和电路噪声(电阻热噪声等)引起;二是由电路接通电源瞬间的冲击电流引起。

但是直接利用PSPICE对图7电路进行模拟仿真时,PSPICE会将电路中的555定时器、电阻、电容、电源等元件和电路的接通过程都理想化,所以不能产生任何噪声。

没有起振源,自然就不能产生振荡。

3.2 有效起振方法通过多次实验,找出了模拟实际振荡电路的一种有效起振方法,即可在电容c1 两端加一个微小的电压初始值具体步骤为:进行瞬态分析时,在simulstion settings中激活Skip the initial transient biaspoint calculation选项,从而忽略初始瞬态偏置点的计算,直接使用各元件的起始条件来作瞬态分析。

利用电容上的初始电压来模拟起振源,从而激发振荡电路产生持续的振荡。

3.3 仿真结果在PSPICE中采用前面提出的模拟振荡电路的起振方法得到555振荡电路输出端的矩形脉冲电压波形,如图9所示。

图9中,电容C1周期性地从Vcc/3充电到2Vcc/3,再从2Vcc/3放电到Vcc/3,从而在555的输出端V out形成周期性的矩形脉冲波,构成多谐振荡器。

矩形脉冲的周期约为0.62 ms,占空比约为56%,且其值只与电阻、电容值有关,与理论计算结果相符。

仿真结果表明,电容上的初始电压,只是激发了振荡电路的振荡,并不会改变电路起振后的输出波形,也不会影响对振荡电路起振特性的研究。

因此,本文提出的PSPICE中555多谐振荡器的起振方法是一种快速、有效的起振方法。

收敛问题的本质及解决办法(转)在大家用软件仿真的时候总会碰到不收敛这个问题...这个问题.有时候解决起来很麻烦...有的情况下根本没办法解决...今天看到这篇文章,我就把它转下给大家共享下...HE HE...下面是以HSPICE为例.其实也是和别的SPICE内核的软件一样...希望对大家有帮助...用hspice仿真电路,不收敛怎么办?Hspice仿真电路不收敛,说白了就是就是计算机解矩阵解不出来了。

eclipse收敛性解决方法2

3、动态数据的信息与实际不一致,如某油井在某时刻后停产,而动态 模型中却仍旧使该井以0产量生产,这样在运算过程中该井井口产量为零, 但井筒之间射孔节点还会根据压力及饱和度变化计算产出量,从而引起计

第八部分 模型收敛 性

一、数值模拟求解过程

二、如何控制模型收敛性

二、如何控制模型收敛性

对于一个确定的模拟模型,其模拟计算的时间在很大程度上 取决于时间步的大小。如果模型没有发生时间步的截断而且能 保持长的时间步,那表明该模型没有收敛性问题,反之如果经 常发生时间步截断,那模型收敛性差,计算将很慢。而时间步 的大小又主要取决于非线形迭代次数。如果模型只用一次非线 形迭代计算就可以收敛,那表明模型很容易收敛,如果需要2 到3次,模型较易收敛,如果需要4到9次,那模型不易收敛, 大于10次的话模型可能有问题,如果大于12次,时间步将截 断。因此,如何避免时间步的截断,是提高模型收敛性的关键 问题。

Байду номын сангаас

局部网格加密设计:

在使用局部网格加密模拟后,在求解局部网格加密过程中,会有很多 数据在全局网格和局部网格之间进行传递,由于设计上的不合理,若果存 在压力及饱和度的分布不连续光滑,就有可能导致收敛性错误。主要表现 在:

存在局部网格与全局网格之间的物质平衡问题,或运算过程中存在由 于气顶膨胀或底水锥进到局部网格内部从而发生流体相变,使得局部网格 内部小网格与本地全局大网格之间的流体相混和物不同等。

VFP表数据:

1、所建立的VFP表没有给定包含油藏预期可能的所有情况下的指标(包 括产量、压力、持水率、持气率等)变化范围,从而在计算过程中会出现 VFP曲线的外推。同所有形式的外推一样,其结果不能保证在实际物理意 义上的正确性。

PSpice仿真中的收敛问题及解决方法

写在前面:本文是作者平常学习和工作中记录的一些笔记,有些零碎,但是很有用,主要是从原理的角度阐述了PSpice仿真中的收敛性,以及应对仿真不收敛的方法。

适合使用PSpice仿真很久并且碰到过较多问题的高手!注意:有些东西是最原始的spice语言的,在OrCAD PSpice 中不一定有相应的选项。

By: Michael Wang 2010年12月17简介PSpice在设定的仿真次数内,如果不能得到满足精度要求的解,就会出现收敛性问题,该问题可能有两大类原因导致:第一:容许的仿真次数太少或者仿真精度要求太高。

第二:电路方程本身无解。

针对不同的仿真类型,都会有一些问题的探讨和分析以及相应的应对策略。

DC分析:在PSpice执行一些定制的仿真前,首先执行DC工作点分析,PSpice通过特定数量的迭代得到DC静态工作点,否则PSpice会有电路不收敛的提醒,并且退出仿真程序。

默认收敛限定描述如下:.options ITL1=100如果不收敛,上式中的ITL1可以增加到大于500更多的DC收敛参数:GMIN步长设置、信号源步长设置、初始电容电压设置及伪瞬态设置。

.NODESET可以设置电路节点的DC电压值,PSpice会识别这个电压值作为电路仿真的初始电压值,可以减少对收敛的迭代次数。

如果不能通过节点设置和ITL1来得到收敛结果,可以设置ITL6=100或者其他非零值,这个设定时运用信号源步长算法,从一个开始值逐渐减少信号源电压直到0电平,或者减少得到一个收敛解,这时,信号源再逐渐减回设置的初始设置。

这个方法可以解决所有DC偏置点不收敛的问题,但是ITL6函数本身有缺陷,所以在最后万不得已才能用。

(OrCAD没有引入这个参数)如果电路包含半导体器件,该器件导电区域会包含零电导率。

这样仿真会出现一个“把零作除”的错误。

为了消除这个错误的产生,在每个半导体器件的PN结点处用GMIN跨导与每个PN结点处并联。

GMIN是一个全局参数,默认值100PΏ,GMIN的参数值越大,牛顿拉夫申算法会越快完成收敛计算。

ISE经验总结及问答

polygon [ (5.1 0 1) (5.1 0 3.7) (5.25 0.1 3.85) (5.25 0.1 1) ]

作者:金伯利岩 QQ:1585568 email: development@

value 越小网格划分越细,另外 dopingconcentration 可以变成 boronconcentration 等。 mdraw 中的对话框如下图:

右下角的小窗口是点击左面的 Add…按钮出来的,这样就可以定义 dopingconcentration 的 梯度变化值或 boronconcentration 的变化值。 2, 梯度细化,在 ISE 中称为 multibox(该方法适用于 2D): 这种方法可以对一个矩形区域内的网格以一定规律和一定的起始值开始变疏或变密,这个和 medici 和 silvaco 的划分十分类似。语句如下: Multibox "multibox reference name" { MaxElementSize = value | vector MinElementSize = value | vector Ratio = (ratio_width, ratio_height) } 然后把这个网格划分应用到一个矩形区域中。 mdraw 中的对话框如下图:

作者:金伯利岩 QQ:1585568 email: development@

1,关于 dessis 和 inspect 中应用的 tcl 语言的问题总结:

首先在一些复杂的例子中,比如晶体管频率增益的提取中,inspect中应用了好多自定 义的库,并在inspect的cmd文件中调用的这些库,对一般应用来说,也只需要引用该库, 并把该库文件copy到自己的工程文件夹中,不过对于inspect的cmd文件应该要理解并明白 其中每个语句的意思,大部分语句可以通过看inspect手册就可以明白,如一些画曲线的语 句、定义曲线线型的语句等。还有一部分是tcl语言中的一些基本算术语句与结构语句,这部 分可以参考tcl语言手册,该手册可以在/man/tcl8.5/TclCmd/contents.htm看 到,/index.htm是一个中文网站,有些基础知识的介绍。对于有提 取器件参数需要的人,还是应该了解一下tcl语言,这将对你了解提取过程有一定帮助。

关于针对CASTEP收敛问题的参数调试总结

大家好:我根据自己在计算过程中遇到的收敛性的问题,做了一点关于CASTEP计算参数调试的总结。

当然,这些只是我的个人心得体会,大家如果觉得有什么问题请提出指正,或是如果有自己独到的见解,请跟帖加上来,供大家一起学习提高。

如果计算在Max. cycle全部用完之后仍然不能收敛,要先查看一下.castep文件,如果能量比刚开始计算时有明显下降,而且震动幅度也明显减小,只是还没有降到收敛标准以下,那说明Max. cycle还不够,要增加这个数值。

但多数情况下,我们会发现,能量并没有比刚开始计算时的能量有明显下降,而是围绕着某个平均值在反复地震荡,而且震动幅度也没有减小。

那说明是参数设定的问题,此时就算再怎么增加Max. cycle的数值,计算最终还是不会收敛的。

这个时候,最好是增加energy cutoff的数值,降低K point set的数值,增加smearing width数值(当然,如果通过调试前两个数值就可以使计算收敛的话,就最好不要动这个数值)。

再有,如果计算是使用的density mixing的话,那要将mix_charge_amp,mix_spin_amp的数值降低,将mix_energy_cutoff的数值增加到 energy cutoff 数值的3到4倍,增加mix_history_length的数值。

当然,如果调试上面的参数仍然发现收敛很辛苦的话,就将mixing scheme转成All Band/EDFT,这会解决收敛问题,但是计算时间将会是使用density mixing 计算所用时间的3倍以上。

1. 参数调试过于经验化,如果楼主能结合对程序原理的认识,或许能够把每个参数调节的意义给阐述的更为清晰些;从优化算法,体系特性,物理过程等方面着手来进行分析,或许可以得到更加全面的认识(如果楼主能够结合上述内容对CASTEP收敛进行详细的分析和总结的话,我会考虑接受楼主的文章,并且发表在小木虫计算与模拟研究RCS期刊上)。

Pspice中的收敛

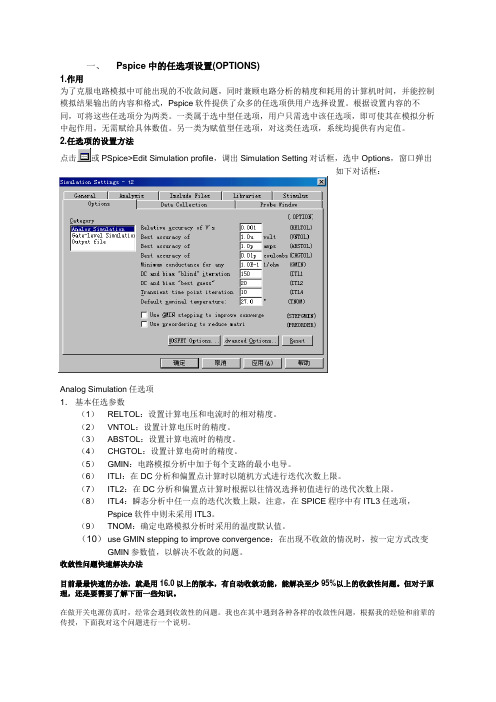

一、Pspice中的任选项设置(OPTIONS)1.作用为了克服电路模拟中可能出现的不收敛问题,同时兼顾电路分析的精度和耗用的计算机时间,并能控制模拟结果输出的内容和格式,Pspice软件提供了众多的任选项供用户选择设置。

根据设置内容的不同,可将这些任选项分为两类。

一类属于选中型任选项,用户只需选中该任选项,即可使其在模拟分析中起作用,无需赋给具体数值。

另一类为赋值型任选项,对这类任选项,系统均提供有内定值。

2.任选项的设置方法点击或PSpice>Edit Simulation profile,调出Simulation Setting对话框,选中Options,窗口弹出如下对话框:Analog Simulation任选项1.基本任选参数(1)RELTOL:设置计算电压和电流时的相对精度。

(2)VNTOL:设置计算电压时的精度。

(3)ABSTOL:设置计算电流时的精度。

(4)CHGTOL:设置计算电荷时的精度。

(5)GMIN:电路模拟分析中加于每个支路的最小电导。

(6)ITLI:在DC分析和偏置点计算时以随机方式进行迭代次数上限。

(7)ITL2:在DC分析和偏置点计算时根据以往情况选择初值进行的迭代次数上限。

(8)ITL4:瞬态分析中任一点的迭代次数上限,注意,在SPICE程序中有ITL3任选项,Pspice软件中则未采用ITL3。

(9)TNOM:确定电路模拟分析时采用的温度默认值。

(10)use GMIN stepping to improve convergence:在出现不收敛的情况时,按一定方式改变GMIN参数值,以解决不收敛的问题。

收敛性问题快速解决办法目前最最快速的办法,就是用16.0以上的版本,有自动收敛功能,能解决至少95%以上的收敛性问题。

但对于原理,还是要需要了解下面一些知识。

在做开关电源仿真时,经常会遇到收敛性的问题。

我也在其中遇到各种各样的收敛性问题,根据我的经验和前辈的传授,下面我对这个问题进行一个说明。

PSpice学习与使用心得

NF 1

VAF 100

IKF .0224

ISE 69.280000E-18

NE 1.186

BR 1

NR 1

ISS 0

RB 10

RE 0

RC 4

CJE 939.800000E-15

VJE .75

MJE .3453

CJC 893.100000E-15

VJC .75

MJC .3017

XCJC 1

IB 1.59E-03 5.47E-06 4.17E-06

IC 4.72E-02 3.45E-04 2.59E-04

VBE 9.14E-01 7.44E-01 7.36E-01

VBC -1.17E+01 -1.25E+01 -1.27E+01

VCE 1.26E+01 1.33E+01 1.34E+01

V(VOUT)/V_V1 = -8.881E-01

INPUT RESISTANCE AT V_V1 = 1.027E+03

OUTPUT RESISTANCE AT V(VOUT) = 4.897E+01

第六部分:敏感度分析。观察的是共发射极放大电路,所以与另外两个电路(共基、共极)中元件没有关系(在下表中相应的体现是敏感度为0)。

V_V3 2.631E-04

V_Vcc2 -2.589E-04

V_Vbias2 -4.170E-06

TOTAL POWER DISSIPATION 7.21E-01 WATTS

第四部分:三极管工作点参数

**** OPERATING POINT INFORMATION TEMPERATURE = 27.000 DEG C

从原理的角度阐述了PSpice仿真中的收敛性,以及应对仿真不收敛的方法

写在前面:本文是作者平常学习和工作中记录的一些笔记,有些零碎,但是很有用,主要是从原理的角度阐述了PSpice仿真中的收敛性,以及应对仿真不收敛的方法。

适合使用PSpice仿真很久并且碰到过较多问题的高手!注意:有些东西是最原始的spice语言的,在OrCAD PSpice中不一定有相应的选项。

By: Michael Wang 2010年12月17简介PSpice在设定的仿真次数内,如果不能得到满足精度要求的解,就会出现收敛性问题,该问题可能有两大类原因导致,第一:容许的仿真次数太少或者仿真精度要求太高。

第二:电路方程本身无解。

针对不同的仿真类型,都会有一些问题的探讨和分析以及相应的应对策略。

DC分析:在PSpice执行一些定制的仿真前,首先执行DC工作点分析,PSpice通过特定数量的迭代得到DC静态工作点,否则PSpice会有电路不收敛的提醒,并且推出仿真程序。

默认收敛限定描述如下:.options ITL1=100如果不收敛,上式中的ITL1可以增加到大于500更多的DC收敛参数:GMIN步长设置、信号源步长设置、初始电容电压设置及伪瞬态设置。

.NODESET可以设置电路节点的DC电压值,PSpice会识别这个电压值作为电路仿真的初始电压值,可以减少对收敛的迭代次数。

如果不能通过节点设置和ITL1来得到收敛结果,可以设置ITL6=100或者其他非零值,这个设定时运用信号源步长算法,从一个开始值逐渐减少信号源电压直到0电平,或者减少得到一个收敛解,这时,信号源再逐渐减回设置的初始设置。

这个方法可以解决所有DC偏置点不收敛的问题,但是ITL6函数本身有缺陷,所以在最后万不得已才能用。

(OrCAD没有引入这个参数)如果电路包含半导体器件,该器件导电区域会包含零电导率。

这样仿真会出现一个“把零作除”的错误。

为了消除这个错误的产生,在每个半导体器件的PN结点处用GMIN跨导与每个PN结点处并联。

GMIN是一个全局参数,默认值100PΏ,GMIN的参数值越大,牛顿拉夫申算法会越快完成收敛计算。

开关电源Pspice仿真技巧及收敛性问题

开关电源Pspice仿真技巧及收敛性问题摘要:本文主要讲述了开关电源的Pspice仿真中,速度与精度的权衡,收敛性问题的常规解决方法。

收敛性问题快速解决办法目前最最快速的办法,就是用16.0以上的版本,有自动收敛功能,能解决至少95%以上的收敛性问题。

但对于原理,还是要需要了解下面一些知识。

在做开关电源仿真时,经常会遇到收敛性的问题。

我也在其中遇到各种各样的收敛性问题,根据我的经验和前辈的传授,下面我对这个问题进行一个说明。

如果在仿真时遇到收敛性问题,快速解决办法如下:设置.OPTION设置里的一些选项。

_ ABSTOL = 0.01μ (Default=1p)_ VNTOL = 10μ (Default=1μ)_ GMIN = 0.1n (Default=1p)_ RELTOL = 0.05 (Default=0.001)_ ITL4 = 500 (Default=10)这些设置可以解决大多收敛性问题,当然如果电路中的错误,它是解决不了的。

如果模型不够精确,上面的设置需要实时调整才能得到想要的结果。

开关仿真中速度与精度的权衡开关仿真就是仿真时有很多重复的周期性的上升下降信号的仿真,比如开关电源的仿真。

在这种仿真中,需要丢弃一些仿真时间点,不然仿真将会非常慢。

而尽管如此,开关电源的仿真还是非常慢。

这种仿真中,pspice的时间步长会在一个很大的步长范围内波动。

这个波动范围主要由一些设置限定,比如RELTOL,ABSTOL,VNTOL等。

因为它是线性迭代算法,为了在信号的上升沿和下降沿得到限定精度范围内的值,在沿处理时,它需要提高步长细度,否则难以得到限定的仿真精度。

因为一般可信的仿真精度是不可能有太大的误差的。

为解决这种问题,通常可以通过设置TRTOL=25(DEFAULT 7),和TMAX,将时间步长限定在开关周期的1/10到1/100之间。

这样做基本可以提高一倍的仿真速度。

当然精度应该在可接受范围内。

LLC变换器PSPICE仿真的收敛性及参数优化_刘海成

第9卷 第5期 信息与电子工程Vo1.9,No.5 2011年10月 INFORMATION AND ELECTRONIC ENGINEERING Oct.,2011 文章编号:1672-2892(2011)05-0651-04LLC变换器PSPICE仿真的收敛性及参数优化刘海成(信息工程大学信息工程学院,河南郑州 450002)摘 要:针对LLC变换器使用PSPICE仿真器进行DC分析和瞬态分析时经常遇到不收敛的问题进行实验,列出了5种有效改进方法。

比较了LLC谐振变换器3个参数优化设计的各种方案,提出并验证了运用PSPICE进行多参数优化设计的方法。

实验表明,合理运用PSPICE,在谐振开关电源设计中常常会取得比其他方法(软件)更令人满意的效果。

关键词:LLC谐振变换器;PSPICE仿真;收敛;参数优化中图分类号:TN86 文献标识码:AConvergence of PSPICE simulation and optimization designfor LLC resonant converterLIU Hai-cheng(Institute of Information Engineering,Information Engineering University,Zhengzhou Henan 450002,China)Abstract:Study of high frequency switching power has focused on Inductor-Inductor-Capacitor(LLC) resonant converter recently, and simulation with Personal Simulation Program with Integrated CircuitEmphasis(PSPICE) for switching power has become an important computer-aided analysis and designmeasure.To solve the non-convergence problems encountered in using the PSPICE simulator for switchingpower DC analysis and transient analysis, experiments were carried out on how to improve the convergenceproblem about the LLC PSPICE circuit simulation. Five improved effective methods were listed. Variousprograms proposed for the design optimization of three parameters of the LLC resonant converter werecompared, and the multi-parameter optimization method using PSPICE was presented and validated.Experiments results show that the reasonable use of PSPICE can obtain more satisfactory results thanusing other methods (software) in the design of switching power supply.Key words:LLC resonant converter;PSPICE simulation;convergence;optimization designLLC串联谐振变换器由于结构简单、效率高、输入范围宽等优点,近几年得到了快速发展,受到了国内外学者的普遍关注[1-5]。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第27卷第1期1997年2月微电子学M icroelectron icsV o l.27,№.1Feb.1997 SP I CE运行收敛问题探索李伟华(东南大学微电子中心,江苏南京,210096)摘 要 电路模拟软件SP I CE因模拟能力强、模拟精度高而得到广泛应用。

探讨了SP I CE模拟不收敛的现象和原因,提出了处理各种不收敛问题的方法和途径,并通过一个模拟实例说明了实现SP I CE运行收敛的具体过程。

关键词 电路模拟 SP I CE 计算机辅助设计 电子设计自动化中图法分类号 T P317 T P399:TN402An I nvestiga tion i n to SP I CE Convergence ProblemL I W eihuaM icroelectronics Center,S ou theast U niversity,N anj ing,J iang su210096Abstract C ircuit si m ulati on p rogram SP I CE is a very useful EDA softw are.In th is paper,the convergence p roblem in the p ractice of operati on is dealt w ith.Causes fo r nonconvergence are dis2 cussed.T he relevant instructi ons and op ti on ter m s are summ arized.F inally,the convergence p ro2 cess in si m ulati on is illustrated by a si m ulati on examp le.Keywords C ircuit si m ulati on,SP I CE,E lectronic design autom ati on,CADEEACC 1130B,2570A1 引 言通用电路模拟程序SP I CE以其很强的模拟能力和较高的模拟精度受到广大的集成电路设计人员和其他电子线路设计者的喜爱。

尤其是在微机上运行的高版本PSP I CE,因其对硬件要求不高,并且带有器件模型部分的源程序,为半开放软件,更是运用广泛。

但是,SP I CE也和其他EDA软件一样,在对电路作某些模拟或分析时会出现不收敛的现象。

我们在长期的运用实践中,针对SP I CE 的不收敛问题作了一些探索。

2 SP I CE模拟不收敛的现象和原因 SP I CE的不收敛现象主要发生在直流偏置点计算和瞬态分析的求解过程中。

在出现不收敛时,计算机会停止计算并发出声响和提示出错,告诉用户程序不能正常结束分析,并在屏幕界面的下方提示停止的时刻,在输出文件中还有较详细的错误提示。

这些提示告诉用户计算在何时停止、已迭代次数或迭代次数溢出或其他提示,并给出计算停止之前的部分结果。

收稿日期:1996—05—02图1 迭代运算示意图模拟不收敛的根本原因是因为软件在对电路进行分析时采用了迭代计算方法,而迭代方法存在不收敛的可能性。

图1显示了牛顿2拉夫森迭代的过程。

首先,选择迭代初值X0,并在曲线的X0坐标处作切线与X轴相交得到X1,再在曲线的X1坐标处作切线得到X2。

依次类推,逐渐逼近精确解X3。

而判断是否迭代结束的依据是两次X值之间的差的范数是否小于规定误差或迭代次数是否超过规定的最大迭代次数。

由此可见,迭代计算不收敛的情况主要有几类:一是初值选取不恰当。

由图1可见,若将迭代初值选为X’,则迭代计算收敛于X3的概率很低;二是计算过程太长。

如果从迭代初值逼近精确解的过程太长,即迭代次数超过了规定的最大迭代次数,则也会出现不收敛提示;三是高精度要求使迭代次数溢出。

如果初值选取适当,通常情况下两次X值之间的差会逐渐减小,两次X差的范数小于规定的误差后,迭代结束。

因此,如果规定的最大迭代次数比较小或精度要求比较高,就有可能在迭代收敛之前结束运算,而表现出迭代不收敛。

在直流偏置点计算过程中,除了电路连接或模型参数选取不当外,电路中包括双稳态单元、无稳态单元、再生式开关单元和正反馈单元时,或当信号幅度较大即电路存在高值电压源或电流源时,程序会因为初值选取不当,或者因最大迭代次数限制或精度要求不当而使迭代不收敛。

在瞬态分析时,SP I CE采用变阶变步长的计算方法,将分析时间区间离散为若干时间点,在每个时间点上用迭代的方法计算节点电参量。

瞬态分析分两步进行,首先计算瞬态分析的偏置值,然后再计算瞬态值。

程序在计算偏置值和瞬态值时都可能因参数设置不当而导致不收敛。

3 处理不收敛的对策在SP I CE软件中,为帮助计算收敛,已设计有一套计算方法并设置了一些命令和可修正参数,可以通过对参数的修正或初值的强制设置使模拟达到收敛。

例如,在计算直流偏置时,当程序无法计算收敛时会自动采用降低电源功率的方法。

当满载功率下无法收敛时,程序会自动降低四分之一的功率,再重新计算一次,如仍不收敛,再降低四分之一进行模拟,直至功率降低为零。

在计算机屏幕上,用户可以看到供电功率不断降低的提示。

311 设置适当的初值在SP I CE中有几条命令用于设置初值。

NOD SET指令。

这条指令用于定义直流分析时用户赋予电路中某些节点的初始估计值,即迭代初值,帮助SP I CE在计算直流工作点时趋向收敛。

它在计算电路直流偏置点和瞬态分析的偏置点时有效,用于计算双稳态电路或其他类似的有多个稳定工作点的场合。

I C指令。

这个指令用于设置瞬态分析的初始条件。

在程序计算瞬态分析的偏置点时有效,一旦偏置点计算完成,瞬态分析开始,定义的节点参数值将被释放。

另外,在SP I CE输入文件的电路描述语句中,二极管、三极管、场效应管等有源元件描述语句与电容、电感描述语句的“I C=数值”也可用于设置初始条件。

值得注意的是,如果用户要使用I C项所设定的内容,必须在瞬态分析语句中加入选项U I C。

只有在瞬态分析语句中含有选项U I C,瞬态分析才会跳过偏置点计算而采用I C项所定义的参数。

312 修改SP I CE的任选项SP I CE的任选项共有28项,与帮助收敛有关的任选项如表1所示。

表1 可帮助收敛的任选项一览表任选项 意 义补缺值单 位ITL1求解DC和偏置点时无效迭代极限次数40ITL2求解DC和偏置点时估解迭代极限次数20ITL4瞬态分析中无效求解迭代极限次数10ITL5瞬态分析求解所有点总迭代极限次数5000R EL TOL计算电压和电流的相对精度0.001ABSTOL电流绝对精度1pA CH GTOL电荷绝对精度0.01pC VN TOL电压绝对精度1ΛV 用户可以通过对任选项的修改,调节模拟过程和控制输出。

任选项的修改可通过“O PT I ON S”命令进行。

如果电压或电流在计算时的数值非常大,即强电流或强电压情况,可以通过修改电压绝对精度VN TOLL和电流绝对精度AB2 STOL值降低精度进行模拟。

实际上,当电压或电流为大信号时,并不需要过高的计算精度。

对于直流分析和偏置点计算,我们认为采用初值设置和计算精度的修改可以有效地帮助收敛。

如果必要,偏置点计算可以采用两步过程。

首先降低精度进行模拟,得到初步结果后进行初值设置,再以高精度进行模拟。

在模拟实践中,瞬态分析不收敛的概率是比较大的。

如果不收敛是发生在瞬态分析的偏置点计算,如前所述,可以通过设初值的方法跳过偏置点计算,如果不能立即确定初值,可以通过和上述类似的方法两步计算设定初值。

对于瞬态分析,我们认为最有效的收敛途径是降低模拟精度。

如果电路主要的参数是电流,则可设置电流绝对精度AB STOL 项为一个较大的值;如果电路的主要参数是电压,可通过电压绝对精度VN TOL项的修改帮助收敛;如果计算参数中电流、电压混合,则可对两个绝对精度进行设置,或对电压电流相对精度项R EL TOL进行设置。

当然,如果是因为迭代次数的限制,可通过迭代总次数极限的任选项ITL5的设置实现收敛。

4 分析实例与结果3ANAL YS IS LA R GE S IGNAL LA SER D I OD E M OD ELI01PUL SE(0800.01P0.01P10M S)I0001S I N(00.37860.97G30N)I0101S I N(00.37861G30N)R01050L1130.001PHD134D I OD EM OD EL D I OD E D(IS=1E211R S=0 N=2)V1400G110133.02E6F117POL Y(2)V1V20021.8010.0252 0020.014VV700FF02VV0.7F302V10.0007R1261V2600C1292.5PF.L I B D I O I D E.L I B.O PT I ON L I M PT S=2000.TRAN0.1N S1300N S.PROB E.END以上是SP I CE的一个输入文件,是一个大信号运用的例子。

在这个分析例子中,电流源I是一个大信号的脉冲源,如果以上面的文件作为SP I CE的输入文件进行分析,模拟将不收敛。

对这个电路进行分析可知,电路的主要参数是电流,我们对文件进行修改,加入任选项语句“O PT I ON AB STOL=15UA”再作模拟,结果计算收敛。

如果采用任选项R EL2 TOL=0.01,模拟也是收敛的。

将这个例子运用PSP I CE V510进行模拟,如采用PSP I CE V4102模拟,则电流绝对精度还应取得更大,并且还会提示迭代超过最大迭代极限5000点。

遇到这种情况,只要在任选项语句中加入ITL5设备更多的迭代点即可使计算结束。

参考文献1 T uinenga P.SP I CE—A Guide to C ircuit Si m ula2 ti on and A nalysis U sing PSP I CE,P rentice2H all Internati onal,Inc2 尤雷.PSP I CE(V4.02)电路模拟设计软件适用手册1北京:海洋出版社,1992李伟华,男,讲师,1956年6月出生,江苏南京人,1988年3月获东南大学半导体物理与器件专业硕士学位,主要从事集成电路CAD的教学与研究。

简 讯I C卡市场前景看好据S e m icond.Int′l1996年第12期报道:由于越来越多的人希望用一张卡来处理储蓄和购物等日常生活琐事,所以全世界I C卡市场将迅速从1996年的7174亿美元增加到2001年的34亿美元,这是美国圣何塞D ataque2 st公司对市场研究的结果。