集成电路故障诊断

集成电路设计中的故障诊断与修复技术研究

集成电路设计中的故障诊断与修复技术研究近年来随着技术的不断提升和应用场景的扩展,集成电路(Integrated Circuit, IC)在各个领域得到了广泛的应用。

在这个过程中,随着芯片规模的不断增大和复杂度的提高,芯片出现故障和问题的概率也不断增加。

因此,研究芯片故障诊断与修复技术,可以提升芯片的可靠性和安全性,保障芯片在不同场景下的工作稳定性和持久性。

一、故障诊断技术芯片故障通常可以分为硬故障(Hard Fault)和软故障(Soft Fault)两种类型。

硬故障一般是由于芯片设计、制造、测试等环节中的物理缺陷引起的,比如杂质、松动、缺陷等,通常较难修复。

软故障则是由于芯片中的电气问题、磁故障、时序问题等问题导致,比硬故障更加难以发现。

目前,常用的故障诊断技术主要包括随机测试、专门的故障诊断电路和在线故障诊断。

随机测试是在芯片制造完毕后,通过一系列的测试来发现芯片中可能存在的故障。

这种方法适用于软故障的发现,缺点是测试时间长且对芯片开销大。

专门的故障诊断电路可以在使用过程中不间断检测芯片中的错误,并及时将错误信息反馈到CPU中进行处理。

这种方法比较适用于硬故障的发现,但需要添加额外的电路支持,会增加芯片复杂度和成本。

在线故障诊断是通过芯片内部的监控器来检测芯片状态的变化,可以及时发现芯片中的软硬故障。

这种方法几乎不需要额外的硬件支持,在线性能也更好,但需要芯片内部集成专门的故障检测电路,对芯片的设计提出了更高的要求。

二、故障修复技术芯片故障的修复通常可以分为软件修复和硬件修复两种类型。

软件修复主要是通过重新配置或调整系统参数来解决软故障问题,比较容易实现。

而硬件修复则需要对芯片进行物理改动,比较复杂。

目前,常用的故障修复技术主要包括块复制、逻辑割裂、金手指等。

块复制指复制故障节点的正常运行节点,并将其用来替换故障节点的操作。

这种方法适用于小规模的芯片,只需添加额外的数据存储即可。

逻辑割裂指将芯片逻辑分成多段来寻找故障节点,当芯片的逻辑被割裂后,所有与割裂点相关的逻辑都会被重组,以便于确定故障的具体位置。

jtag标准ieee1149.1解析

IEEE1149.1标准是一项用于测试和故障诊断集成电路的重要标准,而JTAG(Joint Test Action Group)是这项标准的主要推动者之一。

本文将对IEEE1149.1标准进行解析,从其定义、原理、应用等多个角度进行分析,帮助读者更好地理解和应用这一标准。

一、 IEEE1149.1标准的定义IEEE1149.1标准,也称为边界扫描标准或JTAG标准,是一项由IEEE 制定的用于测试集成电路的标准。

该标准于1990年发布,已被广泛应用于半导体工业、电子制造业等领域。

通过在芯片内部设置边界扫描链,可以实现对芯片内部连接和状态的测试和调试,从而提高了集成电路的可靠性和稳定性。

二、 IEEE1149.1标准的原理1. 边界扫描链IEEE1149.1标准的核心是边界扫描链(boundary scan ch本人n),通过在集成电路的引脚上添加扫描逻辑,实现了对芯片内部连接和状态的测试。

这种边界扫描链可以将芯片的内部引脚与外部引脚进行连接,从而实现对芯片内部信号的观测和控制。

2. TAP控制器IEEE1149.1标准还引入了TAP(Test Access Port)控制器,用于与边界扫描链进行通信和控制。

TAP控制器可以对边界扫描链进行初始化、数据传输和状态控制,从而实现对集成电路的测试和调试。

三、 IEEE1149.1标准的应用1. 芯片测试IEEE1149.1标准最主要的应用是用于集成电路的测试。

通过在芯片内部设置边界扫描链,可以实现对芯片内部连接和状态的测试,从而发现潜在的故障和缺陷。

2. 芯片调试除了测试功能,IEEE1149.1标准还可以用于集成电路的调试。

通过边界扫描链和TAP控制器,工程师可以对集成电路进行状态观测和信号控制,从而快速定位和分析故障原因。

3. 芯片编程IEEE1149.1标准还可以用于集成电路的编程。

一些可编程逻辑器件(如FPGA)可以通过边界扫描信息口进行编程,实现对逻辑器件内部配置和状态的控制。

集成电路测试

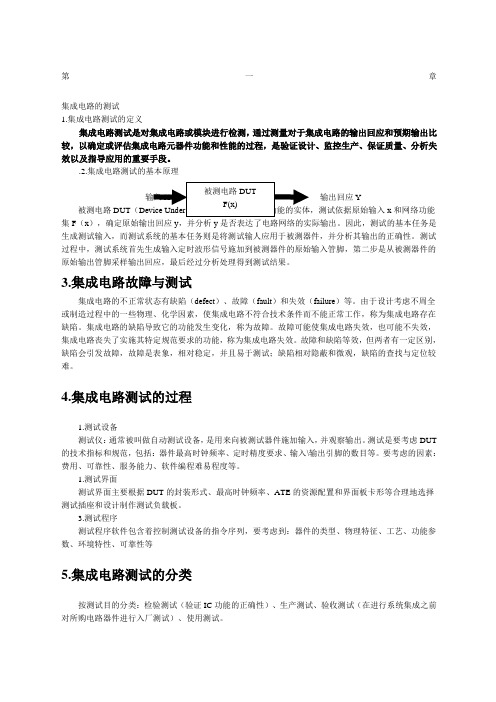

第一章集成电路的测试1.集成电路测试的定义集成电路测试是对集成电路或模块进行检测,通过测量对于集成电路的输出回应和预期输出比较,以确定或评估集成电路元器件功能和性能的过程,是验证设计、监控生产、保证质量、分析失效以及指导应用的重要手段。

.2.集成电路测试的基本原理输出回应Y 被测电路DUT(x和网络功能集F(x),确定原始输出回应y,并分析y是否表达了电路网络的实际输出。

因此,测试的基本任务是生成测试输入,而测试系统的基本任务则是将测试输人应用于被测器件,并分析其输出的正确性。

测试过程中,测试系统首先生成输入定时波形信号施加到被测器件的原始输入管脚,第二步是从被测器件的原始输出管脚采样输出回应,最后经过分析处理得到测试结果。

3.集成电路故障与测试集成电路的不正常状态有缺陷(defect)、故障(fault)和失效(failure)等。

由于设计考虑不周全或制造过程中的一些物理、化学因素,使集成电路不符合技术条件而不能正常工作,称为集成电路存在缺陷。

集成电路的缺陷导致它的功能发生变化,称为故障。

故障可能使集成电路失效,也可能不失效,集成电路丧失了实施其特定规范要求的功能,称为集成电路失效。

故障和缺陷等效,但两者有一定区别,缺陷会引发故障,故障是表象,相对稳定,并且易于测试;缺陷相对隐蔽和微观,缺陷的查找与定位较难。

4.集成电路测试的过程1.测试设备测试仪:通常被叫做自动测试设备,是用来向被测试器件施加输入,并观察输出。

测试是要考虑DUT 的技术指标和规范,包括:器件最高时钟频率、定时精度要求、输入\输出引脚的数目等。

要考虑的因素:费用、可靠性、服务能力、软件编程难易程度等。

1.测试界面测试界面主要根据DUT的封装形式、最高时钟频率、ATE的资源配置和界面板卡形等合理地选择测试插座和设计制作测试负载板。

3.测试程序测试程序软件包含着控制测试设备的指令序列,要考虑到:器件的类型、物理特征、工艺、功能参数、环境特性、可靠性等5.集成电路测试的分类按测试目的分类:检验测试(验证IC功能的正确性)、生产测试、验收测试(在进行系统集成之前对所购电路器件进行入厂测试)、使用测试。

集成电路测试书籍

集成电路测试书籍

在集成电路测试领域,有许多专业的书籍可供选择。

这些书籍包括有

关测试基础知识、测试方案以及测试技术的信息。

以下是一些值得推

荐的集成电路测试书籍:

1. 《集成电路测试工具导论》:本书是一本综合性的测试工具指南,

介绍了各种测试工具的原理和使用方法。

作者还提供了许多实例,帮

助读者更好地理解和应用测试工具。

2. 《集成电路测试》:这是一本全面介绍集成电路测试技术的参考书,内容包括测试前的设计、测试技术以及测试数据分析。

本书还包括实

例和练习题,让读者更好地理解和掌握测试技术。

3. 《模拟与数字混合集成电路测试》:本书是一本介绍模拟与数字混

合集成电路测试技术的指南。

其中包括许多案例,涉及不同类型的测

试方法。

通过实例,读者能够更好地理解和应用混合信号集成电路测

试技术。

4. 《集成电路测试设计》:这是一本面向测试工程师和测试设计人员

的参考书,介绍了集成电路测试设计的基础知识、策略和方法。

本书

还包括实例和练习题,帮助读者更好地掌握测试设计方法。

5. 《集成电路故障诊断与测试》:本书介绍了集成电路故障诊断技术和测试方法。

本书包括故障诊断方法、测试台和测试程序的设计、测试的数据分析和故障排除方法。

通过本书,读者能够了解集成电路测试并学会如何进行故障诊断。

这些书籍涵盖了集成电路测试的不同方面,其中一些还提供了实例和练习题,帮助读者更好地理解和掌握测试技术。

如果您正在考虑学习集成电路测试或者需要帮助解决测试问题,这些书籍将会对您的工作和职业生涯产生积极的影响。

集成电路测试中的自动化方法与工具

集成电路测试中的自动化方法与工具集成电路测试是在集成电路设计完成后进行的一项重要工作,其目的是验证集成电路的功能和性能,并确保其正常工作。

随着集成电路设计的复杂性不断增加,传统的手工测试方法已经无法满足测试的要求,因此自动化方法和工具在集成电路测试中得到广泛应用。

自动化方法与工具在集成电路测试中的应用可以大大提高测试效率和测试质量,同时也减少了测试过程中的人为错误。

下面将介绍一些常用的自动化方法与工具。

1. 设计验证工具:设计验证工具主要用于验证集成电路的设计是否符合规范和性能要求。

常见的设计验证工具包括仿真工具、形式验证工具和冲突检测工具等。

- 仿真工具:仿真工具可以通过建立电路模型,对集成电路的功能进行仿真验证。

其中最常用的是电路级仿真和系统级仿真。

电路级仿真主要验证电路的逻辑功能和时序性能,而系统级仿真则验证整个集成电路的功能和性能。

- 形式验证工具:形式验证工具主要用于验证设计中的特定性质,如安全性和正确性等。

它可以通过数学方法和形式化语言对设计进行验证,并生成详细的验证报告。

- 冲突检测工具:冲突检测工具主要用于检测设计中可能存在的冲突和错误。

通过对设计的电路拓扑和逻辑进行检测,可以帮助设计人员及时发现并解决问题。

2. 自动化测试生成工具:自动化测试生成工具可以根据给定的测试要求和测试用例生成测试代码和测试数据。

这些工具可以自动生成大量的测试用例,包括功能测试、时序测试和边界测试等,从而大大减少了测试人员的工作量和时间。

- 测试生成工具:测试生成工具是使用自动化测试方法生成测试用例的工具。

它根据特定的测试目标和测试要求,自动生成一系列的测试用例,并根据预定的测试标准进行执行和评估。

- 测试代码生成工具:测试代码生成工具是为了简化测试编程过程而开发的工具。

它可以根据测试要求和测试用例生成相应的测试代码,包括测试脚本和测试驱动程序等。

- 测试数据生成工具:测试数据生成工具是用于生成测试数据的工具。

集成电路专业公开发过的论文摘要参考

集成电路专业公开发过的论文摘要参考集成电路专业是电子工程的一个重要分支,在现代电子技术发展中发挥着至关重要的作用。

以下是一些公开发过的集成电路专业论文的摘要,希望能够给读者提供一些参考和启示。

论文一:基于图像处理技术的集成电路缺陷检测该论文旨在通过图像处理技术,实现对集成电路制造过程中可能存在的缺陷进行高效、精准的检测。

其中,研究人员首先对待检测的集成电路样品进行图像采集和预处理,之后通过图像分割、形态学处理等方法,得到集成电路的纹理特征和周边信息;接着,研究人员结合机器学习算法,对图像特征进行训练,并建立了一套自适应的缺陷检测模型,该模型可以根据不同物理特性的缺陷进行分类检测。

最终,实验结果表明,该方法可以高效地检测出所有缺陷,并具有较高的准确率和鲁棒性。

论文二:集成电路中时钟树设计优化该论文针对时钟树在集成电路设计中的重要性,研究了一种基于最短路径算法的时钟树设计方法,并将其在FPGA芯片的设计中进行了验证。

研究人员首先通过全局路径搜索,得到了传输时钟所需的最短路径,然后利用具有流动性的O(1)时钟基准树来构建大型时钟树,并利用所提出的动态调度算法实现了布图。

最后,以Xilinx Virtex-6系列FPGA芯片为例验证了该方法的有效性和性能。

结果表明,该时钟树设计方法能够提高系统时钟频率,减少功耗,并且实现的时钟延迟在一个可接受的范围内。

论文三:基于ICM方法的真实时间温度补偿电路设计该论文通过Intelligent Compensation Method (ICM)算法,提出了一种适应环境温度变化的实时温度补偿电路设计方法,该方法较好地解决了温度变化对集成电路的影响。

该方法的设计流程具有非常高的仿真准确率和强鲁棒性,通过对多组不同情况下的温度测试数据进行仿真分析,可以得出该方法的设计误差率和热滞后现象均比传统方法更低。

最终,实验结果表明,该设计方法可以有效地提高真实时间系统的可靠性和鲁棒性。

片上系统的片上测试与故障诊断技术研究

片上系统的片上测试与故障诊断技术研究片上系统的片上测试与故障诊断技术研究随着集成电路技术的不断发展和应用,片上系统成为现代电子产品中不可或缺的关键组成部分。

片上系统具有高度集成、复杂性高、功能强大等特点,但也随之带来了测试和故障诊断的挑战。

因此,片上系统的片上测试与故障诊断技术研究变得尤为重要。

片上测试是指在芯片制造过程中对芯片进行测试,以保证芯片的质量和可靠性。

传统的片上测试方法主要包括功能测试和结构测试。

功能测试是通过输入一系列测试向量,观察芯片的输出是否符合预期来检测芯片的功能是否正常。

结构测试则是通过测试芯片内部的逻辑门、存储器等电路,以检测芯片内部是否存在电路缺陷。

这些传统的测试方法虽然已经取得了一定的成果,但随着芯片的复杂性和集成度的不断提高,这些方法已经无法满足现代芯片的测试需求。

为了解决这一问题,研究人员提出了一系列新的片上测试技术。

其中一种比较常见的技术是基于扫描链的测试方法。

扫描链是一种特殊的设计结构,通过将芯片内部的寄存器连接成一个长链,可以在测试过程中通过控制信号将测试数据输入到芯片内部,以实现对芯片内部电路的测试。

扫描链测试方法具有测试覆盖率高、测试时间短等优点,已经成为现代芯片测试的主流方法之一。

除了扫描链测试方法外,还有一些其他的片上测试技术被提出和研究。

例如,基于内部观测点的测试方法,可以通过在芯片内部插入观测点,监测芯片内部电路的状态,以实现对芯片的测试。

另外,还有一些基于重构技术的测试方法,可以通过对芯片进行重构,提取出芯片的功能模块,并对功能模块进行测试。

然而,片上测试只能检测到芯片制造过程中存在的电路缺陷,无法检测到芯片在使用过程中出现的故障。

因此,故障诊断技术也成为片上系统研究的重要方向之一。

故障诊断是指当芯片出现故障时,通过一系列测试和分析手段,确定故障原因和位置的过程。

传统的故障诊断方法主要包括故障模型建立、测试生成和故障定位三个步骤。

其中,故障模型建立是指根据芯片的设计结构和制造工艺,建立芯片的故障模型。

英语作文-如何进行集成电路设计中的故障诊断与可靠性分析

英语作文-如何进行集成电路设计中的故障诊断与可靠性分析In the intricate world of integrated circuit (IC) design, fault diagnosis and reliability analysis are paramount. These processes ensure that ICs function correctly over their intended lifespan, despite the presence of inherent manufacturing defects or external stresses encountered during operation.Fault diagnosis in IC design is a methodical approach to detect, localize, and characterize faults within the circuit. It begins with the creation of a test plan that includes a suite of electrical tests designed to be sensitive to potential faults. Once testing is conducted, data analysis tools are employed to compare the electrical responses of the IC to expected values. Deviations indicate the presence of a fault, and advanced algorithms can then pinpoint its location.The complexity of modern ICs, with billions of transistors on a single chip, necessitates the use of sophisticated diagnostic tools. These tools often employ machine learning techniques to recognize patterns in test data that correlate with specific types of faults. For instance, a recurrent voltage drop at a particular node might suggest a resistive open circuit fault, while unexpected logic states could indicate a bridging fault.Reliability analysis, on the other hand, is concerned with predicting and enhancing the long-term performance of ICs. It involves studying the failure mechanisms that can affect the circuit over time, such as electromigration, hot carrier injection, and time-dependent dielectric breakdown. By understanding these mechanisms, engineers can design ICs to mitigate their effects, thereby improving reliability.One key aspect of reliability analysis is accelerated life testing, where ICs are subjected to elevated stress conditions to induce failures more quickly than would occur under normal operating conditions. This allows engineers to observe failure modes and gather data on the IC's lifespan in a condensed timeframe. Statistical models are thenapplied to extrapolate these findings to normal usage conditions, providing estimates of the IC's mean time to failure (MTTF).To further enhance reliability, redundancy can be built into the IC design. This involves incorporating additional circuit elements that can take over the function of a failed component without interrupting the operation of the IC. Such redundancy is crucial in applications where uninterrupted operation is critical, such as in aerospace or medical devices.In conclusion, fault diagnosis and reliability analysis are essential components of IC design that work in tandem to ensure the functionality and longevity of electronic devices. Through meticulous testing, data analysis, and proactive design strategies, engineers can identify potential issues before they become problems and engineer circuits that stand the test of time. This relentless pursuit of perfection not only drives technological advancement but also underpins the reliability we have come to expect from our electronic devices. 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

本文的主要工作是基于集成电路的电流信息和模式识别理论对电路进行静态

电流检测、动态电流检测、以及故障定位等方面的基础性研究。

具体包括静态电

流的检测方法及仿真实验,动态电流的检测方法及仿真实验,基于近邻法和连接

的模式识别法的故障定位法,基于神经网络的故障诊断方法四个方面:

在静态电流检测方面:通过查阅和学习大量的国内外文献和资料,分析了静

态电流检测的基本原理,分析了COMS 电路的特点,并用PSPICE 对CMOS 或非

门和与门电路做了故障注入的仿真实验,给出了仿真试验结果,由于采用静态电

流测试产生了测试逃逸,故引入了动态电流测试方法增加故障覆盖率。

在动态电流检测方面:通过分析IDDT 的波形,用动态电流尖锋值的方法对

CMOS 电路作了故障注入和故障诊断。

通过对CMOS 电路的桥接故障、参数改变、

短路故障等的检测,说明了采用动态电流对故障检测的可行性。

在故障定位方面:由于静态电流检测方法对CMOS 电路的桥接故障不能准确

定位,我们利用小波分析对故障电路的IDDT 电流信息进行特征提取,然后分别采

用基于近邻法和连接的模式识别法对电路进行了故障定位实验,实验结果证实了

两种算法在故障定位应用上的可行性。

最后通过比较两种算法的仿真结果,说明

了用连接的模式识别方法的定位更加可靠。

在神经网络的故障诊断方面:通过采用小波变换,对电路正常模式和故障模式

的IDDT 采样信号进行故障特征提取,建立样本集;然后利用神经网络对各种状态

下的特征向量进行分类决策,实现电路的故障诊断。

论文的具体安排如下:

第一章介绍本课题的研究意义以及集成电路故障诊断的发展概述。

第二章集成电路故障诊断的基础理论介绍

第三章利用静态电流方法对CMOS 电路的故障进行仿真实验

第四章利用动态电流方法对CMOS 电路的故障进行仿真实验

第五章分别利用基于近邻法和连接的模式识别法进行故障定位仿真实验及

利用基于神经网络的故障诊断算法进行仿真实验

第六章给出全文工作的总结和今后的展望

本章主要介绍了集成电路故障诊断的基础理论和方法。

首先我们介绍了传统

电路的检测方法,然后详细介绍了软故障及硬故障模型,并讨论了本文将用到的

近邻法,小波分解,神经网络等模式识别相关理论知识,最后针对后续故障诊断

实验中将使用的PSPICE 和MA TLAB 仿真工具进行了相关介绍。

静态电流(IDDQ)检测与电压检测不一样,

本章首先对IDDQ 的基本原理和检测方法进行了简单介绍,然后为了验证

IDDQ 检测方法的可行性,我们在已有研究成果的基础上,针对集成电路常见的桥

接故障、漏电流故障模型,进行了仿真实验。

实验结果表明本文方法能充分利用静态电流中的故障信息对故障进行检测。

但该方法的有效性受测试向量诊断能力

的影响,今后研究的重点应是如何为这种故障诊断算法提供有效的测试生成向量。

并且从本实验可以看出,IDDQ 的测试覆盖率有限,所以在故障检测中,需要采用

的动态电流检测法(IDDT)对IDDQ 法进行补充。

本章首先简单介绍了动态电流的基本原理,并将IDDT 检测法与IDDQ 检测法

进行了比较。

然后通过分析IDDT 波形的尖峰值,实现了对CMOS 与非门的短路

故障、开路故障、和参数故障进行检测,验证了动态电流检测法的可行性。

根据

仿真实验,我们证实了IDDT 法能成功得检测出电压测试和IDDQ 所不能检测出的

故障,说明了用动态电流检测法可以增大了故障覆盖率,IDDT 是电压测试和静态

电流测试方法的有力补充。

5.4 本章小结

本章首先分别采用基于近邻法和基于连接的模式识别法对CMOS 与非门电路

和TTL 或非门电路进行了故障诊断实验,仿真结果证明了两种算法都能有效地对

软硬故障进行诊断。

但两种算法相比,基于连接的模式识别法准确率更高,并具

有更高的故障分辨率。

然后针对软故障,本章特别采用了基于神经网络的IDDT

故障诊断方法,应用小波变换,对电路正常模式和故障模式的IDDT 采样信号进行故障特征提取,建立样本集;然后利用神经网络具有非线性映射优点,对各种状

态下的特征向量进行分类决策,实现对电路的故障诊断。

本论文以对集成电路进行故障

诊断为应用背景,结合电流检测和模式识别领域中的相关技术,对集成电路的检

测与定位进行了较为系统的研究。

在分析和总结现有各种电路故障诊断方法的基

础上,分别对静态电流故障检测、动态电流故障检测和基于IDDT 的故障诊断算法

方面进行了大量研究,取得的成果可总结如下:

(1) 静态电流故障检测:利用静态电流检测法,针对集成电路常见的桥接故障、

漏电流故障模型进行了仿真实验。

实验结果表明该方法能充分利用静态电流中的

故障信息对故障进行检测。

(2) 动态电流故障检测:利用动态电流变化波形,对集成电路的桥接故障、开

路故障、参数故障进行了仿真实验,实验结果表明该方法能检测出电压检测和静

态电流检测无法检测的故障,提高了故障检测的覆盖率。

(3) 基于动态电流的故障诊断实现:基于动态电流信息,采用近邻法和基于连

接的模式识别法对CMOS 与非门电路和TTL 或非门电路进行了故障诊断实验,实

验结果表明两种算法能正确的诊断出各类故障。

但相比之下,基于连接的模式识

别法的准确率和故障分辨率更高。

本文还对基于神经网络的诊断算法进行了一次

有益尝试研究,仿真实验结果表明该方法对于解决集成电路的故障诊断问题是切

实有效的。

6.2 展望

基于电流的故障诊断是集成电路诊断领域的一个研究热点,有许多急待解决

的问题,本文的研究只局限于一定深度,还需要在以下一些方面作进一步的研究:

(1) 本文所做的研究工作尚停留在理论层次,离实际工程应用还有一定差距。

主要是对简单电路的单故障进行检测,针对大规模集成电路或其它复杂系统的多

故障诊断还需进一步研究。

(2) 由于IDDT 测试是一种高速条件下的参数式测试,电流测量精度远不如

IDDQ 测试的精度高,因此非常需要将故障电流与正常电流的差别进行最大化,但

如何来做,人们还没有好的办法;

(3) 被测电路工作速度很快,动态过程的时间很短,要捕捉完整的电流信息需

要用比被测电路工作速度更高的测试设备,而简单方法所得到的故障信息又非常

有限,对提高故障覆盖率不利。

(4) 随着网络规模扩大,怎样保证系统内部的稳定性和定位的精确性,以及该系统能否通过硬件实现等都是今后待解决的问题。