电气规则检查

电气接线及检验规范

以常规设备控制系统有不同的控制元件及执行元件,可分组依 次通过孔位接入电气柜,根据设备不同孔位可空缺或顺移。

4.2 机组电气接线由电气柜上接线、电气柜箱 门上接线、按钮盒分线盒接线及设备内部接 线三部分组成

其中: 电气柜上接线包括主回路接线和控制回路接线两部分。主 回路接线主要是AC380V和AC220V的动力电源回路,包括用 户电源回路、电机回路、风机回路、水泵回路变频器、电 源保护器等接线;控制回路接线主要是弱电回路,包括控制电 源、风扇、控制器输入输出、传感器及通讯连接等接线。 电气柜门上接线有电源指示、报警指示、蜂鸣器和急停按 钮等接线。 设备内部接线包括电机、水泵、风机、电磁阀、相关传感 器、压力开关、液位开关等接线。

5) 6) 7)

图三

7.设备内部接线

7.1 设备内部接线 7.2 设备内部走线规定

7.1 机组内部接线

7.1.1 电机接线 7.1.2 电磁阀接线 7.1.4 传感器接线

7.1.1 电机接线

电机接线采用4芯RVV护套线,具体线径须按照电气图纸上 标示的线径选用正确的导线。将护套线剪下合适长度后,其一端 剥去80mm的护套,将四根导线分别剥头10mm,压上适合线 径的圆形预绝缘端头,对应接在水泵接线端子上。接好后,盖好 接线盒盖,并将导线另一端沿约定走线方式引至电控箱内,依次 按导线颜色接到电控盘对应接线端子上。 接好后,用万用表测量导线是否接正确,并检查电机相序正 确,各个电机接线及导线颜色是否一致。

5.电气柜上接线

5.1 主回路接线 5.2 控制回路接线

5.1主回路接线

5.1.1 用户电源 5.1.2 电机回路 5.1.3 变频器或伺服电机

5.1.1 用户电源 一般公司的生产的产品采用三相五线制连接方式供电,若 用 户是三相四线制,可以将零线和地线并联连接。电源进线 分 U、V、W、N、PE,AC380V电源线可用黑色颜色但必须 严格按照国家标准区分应用热缩管或颜色辨识,U——黄色, V——绿色,W——红色,N——蓝色,PE——黄绿色。 用户电源回路是从电源接线端子到断路器上进线端子和熔 断器这一回路。使用型号为BVR的导线,其线径在电气图纸上 作有标示,接线时请严格按照标示线径选用导线。接电源线 时,应用合适的管形预绝缘端头或窥口铜接线端头压接导线, 剥线长度要按端头金属部分长度剥线,压接时须压接牢固、饱 满。 电源线可以不套线号。

电气设备检维修管理制度

电气设备检维修管理制度•相关推荐电气设备检维修管理制度(通用9篇)在生活中,我们都跟制度有着直接或间接的联系,制度泛指以规则或运作模式,规范个体行动的一种社会结构。

这些规则蕴含着社会的价值,其运行表彰着一个社会的秩序。

一般制度是怎么制定的呢?下面是小编整理的电气设备检维修管理制度(通用9篇),供大家参考借鉴,希望可以帮助到有需要的朋友。

电气设备检维修管理制度1电气维修管理规定一、电气维修人员必须持上岗证,严格按照国家建设部颁发的标准《电气安装工作规程》作业。

二、在进行电气维修时维修人员应戴好安全防护用品,配备绝缘良好的电工工具。

三、维修和保养电气设备时,应按要求做好保证安全的组织和技术措施。

四、维修班班长在分配工作的同时向维修人员说明工作中的安全注意事项,并在工作中检查监督执行情况。

五、一般情况下,尽量避免带电工作,若因特殊需要而必须带电作业时,应装设隔音挡板,并有专人监护。

六、在一经分闸即可送电到工作地点的形状和刀闸的操作把手上,应悬挂“禁止合闸,有人作业”的标牌。

配电房管理规定一、配电房是供电系统的关键部位,设专职电工对其实行24小时运行值班,未经许可,非工作人员不得入内。

二、值班员必须持证上岗,熟悉配电设备状况,操作方法和安全注意事项。

三、值班员应密切注意电压表、电流表,功率表的指示情况,严禁变压器空气开超载运行。

四、经常保持配电房地面及设备外表清洁无尘。

五、经常保持配电房消防设施的完好齐备,保证应急灯在停电状态下能正常使用。

六、做好配电房的防水、防潮,堵塞漏洞,严防蛇、鼠等小动物进入配电房。

电气设备检维修管理制度2第一条电气设备检修时必须严格执行停(送)电制度。

第二条井下不得带电检修、搬迁电气设备、电缆和电线。

第三条检修或搬迁前,必须切断电源,检查瓦斯,在其巷道风流中瓦斯浓度符合规定时,再用与电源电压相适应的验电笔检验;检验无电后,方可进行导体对地放电。

第四条所有开关的闭锁装置必须能可靠地防止擅自送电,防止擅自开盖操作。

电气规则检查-ERC

电气规则检查-ERCERC全称为electrical rule checking,翻译为电气规则检查。

检测的是GDS版图中是否存在电学连接问题,属于PV(physical verification)的一个项目。

这也算是一个后端signoff的基本概念,今天就给大家简单介绍一下ERC。

什么叫电气规则呢?其实它的种类也不多,主要包括:1. MOS的gate不能直接连supply。

2. cell input永远不能floating。

3. 一个cell的driver最多一个,或者说output不能发生short。

4. N/P区(衬底或阱)不能floating。

可能还有别的,不过我目前只知道这四种了,可以先了解一下。

我下面分别说一下这四条规则的理由。

对于1,我们在设计芯片的时候总是会按最悲观的情况考虑问题,因此我们会认为PG的供电总是不稳定的。

人们的初衷可能都是简单的,希望一个mos常开或者常关,但如果直接将PG接到gate上,在电压出现波动的时候(比如说由于静电),这个mos的开关就不那么稳定,其沟道电阻相应会受到影响。

甚至电压波动很大的时候会发生逻辑错误,或者击穿mos管。

因此实际应用的时候,对于那些输入一直为0或者一直为1的情况,我们会从PG接一个TIE cell,再接到gate上。

TIE cell可以起到一个稳定电压、中继的作用。

Multiple driver的情况,会导致电路VDD和VSS发生short。

还是假设两个反相器,它们的output接在了一起,当第一个反相器输出逻辑1(高电平),第二个反相器输出逻辑0(低电平)的时候,相当于产生一条从VDD直接到VSS的电流通路。

这是绝对不被允许的。

N/P floating,还是主要为了防止latch up。

一般会将N well接VDD,P substrate接VSS,减小well/substrate和drain/source之间的电势差,可以防止latch up产生。

版图的物理验证

版图的物理验证版图的物理验证主要有DRC,ERC(电气规则检查)和LVS三种方法。

DRC 表示设计规则检查,是Design Rule Checking的缩写,LVS是Layout Versus Schematic的缩写,ERC是Electrical Rule Checking。

DRC用来检查版图的几何图形符合工艺规则要求,以便芯片能在工艺线上生产出来;LVS把设计得到的版图和逻辑网表进行比较,检查各器件大小和连接关系是否完全一致;ERC主要是检查版图电性能(如衬底是否正确接电源或地,又无栅极悬空等)以保证各器件能正常工作。

物理验证成功则可以出带(Tapeout),或生成macro cell 做作为整个设计的一部份来使用,数据格式一般采用GDSII。

下面以Mentor公司的物理验证Calibre来说明版图的验证过程。

1.ANT流程2.DRC流程DRC验证需要输入版图文件(GDSII格式)和规则文件,规则文件一般由厂商提供。

Mentor 公司的Calibre软件是DRC方面的主流工具。

其规则文件的语法简单,但规则较繁杂。

规则文件通常包括描述模块(Description Block)、输入层模块(Inputlayer Block)、操作模块(Operation Block)三个部分。

每一个模块有一个开始标志(如:*DESCRIPTION)和结束标志(*END)。

描述模块定义了Dracula运行环境。

包括运行模式、基本单元名、输入/输出设备、文件名、格式、图形比例元素、网格大小、输出记录文件、警告消息显示等。

输入层模块把布局图的层名或层编号和Calibre的层名对应起来,并提供Calibre进行验证所需的其他关于层的信息。

主要是:要输出的层、层名、掩膜顺序、要输出的层、文本层。

操作层定义要进行的操作和应用程序并且标出错误。

它定义的操作类型有:逻辑、电气节点、缩放、参数、空间、ERC、DRC、LVS、LPE和PRE。

2.6电气规则检查和标注(protel课件)

2.6 电气规则检查和标注2.6.1 检查矩阵菜单【工具】|【ERC 】主要用于电气规则检查。

检查的内容很多,但是最主要的是检查元件之间的相互连接。

启动菜单【工具】|【ERC 】后,屏幕显示如图2.54所示的对话窗口。

在电气检查窗口上显示的是电气检查规则,这些规则主要分为两个页面的设置。

1. Setup 页面电气规则检查Setup 页面设置见图2.54。

ERC Options 区域:该区域设置检查错误的种类。

有如下几种:Multiple net names on net :一个网络上有多个网络标号。

Unconnected net labels :网络标号无连接,即只有一个网络标号。

Unconnected power objects :无连接的电源和地线。

Duplicate sheet numbers :在多原理图设置中,原理图的图号重复。

Duplicate component designator :重复的元件序号。

Bus label format errors :总线名称格式错误。

Floating input pins :输入管脚悬空。

Suppress warnings :不将警告信息记录在错误报告中。

Options 区域:该区域给出处理错误的方法。

Create Report File :建立报告文件。

Add Error Markers :在错误的地方加错误标记。

Descend Into Sheet Parts :设定检查范围是否包括图纸符号中的电路。

Sheets to Netlist 下拉列表框:设置检查范围 Active sheet :只检查当前窗口中的原理图。

Active project :检查当前项目。

Active sheet plus sub sheets :检查当前电路图和它的子图。

Net Identifier Scope 下拉列表框:设置端口和网络标号的有效范围。

Net Label and Parts global :网络标号和端口全局有效。

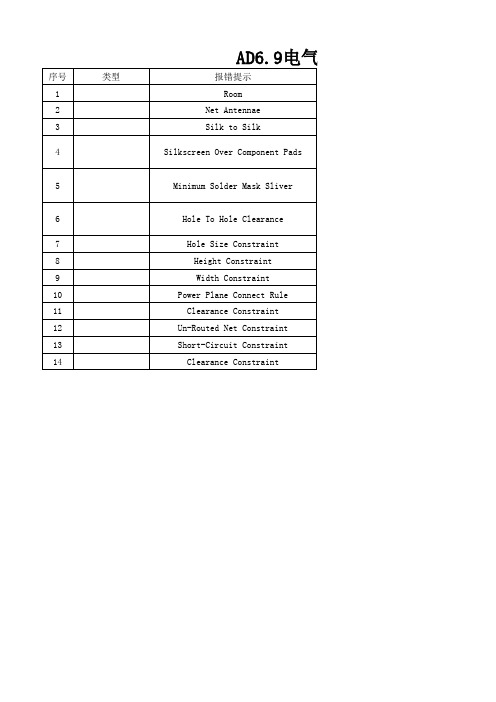

AD6.9电气规则检查报错说明

最低焊接面罩银

洞孔间隙 孔尺寸不在约束范围内 高度不在约束范围内 线径不在约束范围内 功率平面连接规则 线、元器之间距离不在约束范围内 有线路未连接 短路约束 间隙约束

调整线宽 检查未连接的走线,将其连上

AD6.9电气规则检查报错说明

序号 1 2 3 4 类型 报错提示 Room Net Antennae Silk to Silk Silkscreen Over Componiver

6 7 8 9 10 11 12 13 14

Hole To Hole Clearance Hole Size Constraint Height Constraint Width Constraint Power Plane Connect Rule Clearance Constraint Un-Routed Net Constraint Short-Circuit Constraint Clearance Constraint

9电气规则检查报错说明

错误原因 元器件超过Room界线 网络天线 丝印层与丝印层之间的间隙 顶层丝印与元件焊盘距离 有线路独立存在于Room中,未删除或者未连接 两个丝印之间的距离太近,这个错误可以忽略 按D、R将规则中的Silkscreen Over Component Pads 改小一些就可以了 你的某个元件的焊盘间距 大于1mil,你可以选 择该规则或者把封装中的焊盘间距改大一点。 引脚安全间距问题,一般是封装的问题,如果 确定封装没问题,这个错误基本可以忽略 解决办法

【精品课件】原理图电气规则检查及报表

“Only Ports Global”: 使得只有I/O端口可以在整个 项目中被承认。

“Sheet Symbol/Port Connections”:此选项设置使得 电气连接只发生在方块电路端口和对应的下层电路的I/O 端口。

执行电气规则检查后,系统会在电路原理图的错误处放置红色的符号, 以提示设计者注意,如下图所示。

8.2 生成报表文件

8.2.1 生成元件材料表 元件材料表主要用于整理一个电路或者一个项目文件中所有的元 件,它主要包括元件的名称、标号、封装等内容。 1)选择“File”菜单,然后在弹出的下拉菜单中选择“Open”选 项,打开需要生成元件材料表的原理图文件。如果此原理图文件已 经打开,则此步操作可以省略。 2)选择“Reports”菜单,然后在弹出的下拉菜单中选择“Bill of Material”选项,如下图所示。此操作也可用下面的操作代替: 按下R键,松开后按下B键。

3) 出现生成元件材料表文件的向导 “ Bom Wizard”对话框,如左下图 所示。确定元件材料表文件的来源后,用鼠标左键单击“Next”按钮,进入下 一步操作。

8.1.3 进行电气规则检查 设置电气规则完成后,用鼠标左键单击“OK”按钮,退出对话框, 并使系统进入文本编辑器并生成相应的错误结果的报告(存为 *.ERC文件)。如下图所示。

报告中逐条列出了电路原理图的电学错误。每条错误报告的 第一行以“#”开头,显示了电学错误的内容;第二行后显示与 错误相关联的元件管脚号和该错误在原理图上的具体位置。

2.“Rule Matrix(电气法则测试矩阵)”标签页 用鼠标左键单击“Setup Electrical Rule Check”对话框的“Rule Matrix”标签,即可进入“Rule Matrix”标签页,如下图所示。

电气规则检查中英文对照

Violations associated with buses 与总线有关的错误Bus indices out of range 总线指数超出范围Bus range syntax errors 总线语法错误Illegal bus definitions 非法总线定义Illegal bus range values 非法总线范围值Mismatched bus label ordering 总线标签不匹配Mismatched bus widths 总线宽度不匹配Mismatched bus-section index ordering 设定的总线Mismatched bus/wire object on wire/bus 不匹配的总线Mismatched electrical types on bus 总线电气类型不匹配Mismatched generics on bus (first index)Mismatched generics on bus (second index)Mixed generic and numeric bus labeling 一般数字与总线标签混合Violations associated with components 违反元件用法Component implementations with duplicate pins usage 元件重复使用引脚Component implementations with invalid pin mappings 元件引脚无效Component implementations with missing pins in sequence 元件缺失引脚Component containg duplicate sub-parts 部分子元件重复Component with duplicate implementations 有元件重复Component with duplicate pins 元件引脚重复Duplicate component models 重复元件模型Duplicate part designators 零件标号重复Errors in component model parameters 元件模型参数错误Extra pin found in component display mode 在元件显示模型上发现额外的引脚Mismatched hidden pin connections 隐藏的元件引脚连接Mismatched pin visibility 可见的引脚不匹配Missing component model parameters 元件模型参数丢失Missing component models 元件模型丢失Missing component models in model files 在模型文档中丢失元件模型Missing pin found in component display mode 在元件显示方式中发现引脚缺失Models found in different model locations 在不同的模型地点发现模型Sheet symbol with duplicate entries 原理图符号重复Un-designatde parts requiring annotation 未标识部分需要注解Un sub-part in componentViolations associated with documents 与文件相关的错误Conflicting constraints 冲突的约束Duplicate sheet numbers 数字部分重复Duplicate sheet symbol names 原理图名称重复Missing child sheet for sheet symbol 缺少图纸符号表Missing configuration target 缺少配置目标Missing sub-project sheet for component 缺少分项目元件表Multiple configuration targets 多配置目标Multiple top-level documents 多个顶层文件Port not linked to parent sheet symbol 子图表没有连接到总原理图Sheet entry not linked to child sheet 条目表没有连接到子表Unique identifiers errors 唯一标识符错误Violations associated with nets 网络相关错误Adding hidden net to sheet 给图表添加隐藏的网络Adding items from hidden net to net 从隐藏的网络添加项目Auto-assigned ports to device pins 自动分配元件引脚Duplicate nets 重复网络Floating net labels 网络标签没连接Floating power objects 电源未连接Global power-object scope changesNet parameters with no name 网络参数没有名称Net parameters with no value 网络参数没有值Nets containing floating input pins 网络引脚未连接Nets containing multiple similar objects 网络包含多个类似项目Net with multiple names 网络中使用多个名称Net with no driving source 没有驱动源Nets with only one pin 只有一个引脚Net with possible connection problems 可能出现的连接问题Sheets containing duplicate ports 表中有重复的端口Signals with multiple drivers 多个驱动信号Signals with no driver 信号源无驱动Signals with no load 信号源无负载Unconnected objects in net 有项目未连接进网络Unconnected wires 有未连接的导线Violations associated with others 其他的相关错误No error 无错误Object not completely within sheet boundaries 项目超出图表范围Off-grid object 项目偏离网络Violations associated with parameters 与参数相关的错误Same parameter containing different types 不同的类型相同的参数Same parameter containing different values 相同的参数不同的值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

.

电气规则检查

●电气规则检查 在原理图设计过程中,对项目进行编译是非常重要的一环。

原理图中的连线、元件的引脚都具有实际的电气意义,在使用 时必须遵守一定的规则,这个规则就是电气规则。在原理图绘 制结束后,必须对原理图进行编译,即电

●电气规则检查 在对原理图进行编译时,系统将按照设定的规则对原理图

进行ERC检查,并给出原理图的元件信息、网络信息和错误信息。 编译的方法如下:

打开编译设置窗口的方法如下: 执行菜单命令:项目管理→编译文件 按快捷键:C→D

.

电气规则检查

执行命令后,系统开始对文件进行编译。编译完成后, 将生成信息报告。在信息对话框中,列出了原理图中的违规 信息,当原理图中没有违规现象时,对话框是空的。

双击其中的违规信息,将弹出和该信息对应的编译错误 对话框。在对话框中,列出了该违规信息的原因和相关的导 线、网络、元件引脚等。单击其中的对象,可在原理图中定 位该对象,并作过滤显示,可根据该信息修改原理图。

.

电气规则检查

在原理图中编译中,Protel DXP 2004给出的编译信息并 不都是正确的,用户可根据自己的设计思想和原理判断该违 规信息是否合理。

有些违规信息是可以忽略的,此时单击配线工具栏中的 “放置忽略ERC检查指令符”按钮,放到合适位置。再次编译, 将不作错误报告。

.

.