微机原理第八章--8251

微机原理第八章 串行通信及串行接口

1. 可编程串行接口典型结构

✓状态寄存器

✓控制寄存器

✓数据输入寄存器--串行输入/并行 输出移位寄存器

✓数据输出寄存器--并行输入/串行 输出移位寄存器

2. 串行通信基本概念

在串行通信时,数据和联络信号使用同一条信号线 来传送,所以收发双方必须考虑解决如下问题: ❖ 波特率---双方约定以何种速率进行数据的发送和接收 ❖ 帧格式---双方约定采用何种数据格式 ❖ 帧同步---接收方如何得知一批数据的开始和结束 ❖ 位同步--- -接收方如何从位流中正确地采样到位数据 ❖ 数据校验--- -接收方如何判断收到数据的正确性 ❖差错处理---收发出错时如何处理 收发双方必须遵守一些共同的通信协议才能解决上述问题。

串行通信适于长距离、中低速通信

并行通信

将数据的各位同时在多根并行传输线上进行传输。

D0 0

D1 1

D2 0

源

D3 1

D4 D5

0 1

D6 1

D7 0

D0 D1 D2 D3 目 D4 的 D5 D6 D7

数据的各位同时由源到达目的地 → 快 多根数据线 → 短距离(远程费用高)

并行通信适于短距离、高速通信

工作方式下。

(8)错误检测 • 传输错误 • 覆盖错误

二、 接口与系统的连接

从结构上,可把接口分为两个部分,其中和 外设相连的接口结构与具体外设的传输要求及数 据格式相关,因此,各接口的该部分互不相同; 而与系统总线相连的部分,各接口结构类似,一 般都包括:

1. 总线收发器和相应的逻辑电路

2. 联络信号逻辑电路

接收端需要一个时钟来测定每一位的

时间长度。

波特率/位传输率---每秒传输的离散信号 的数目/每秒传输的位数。 波特率因子---

第八章 8251

微机原理与接口技术

北京工商大学信息工程学院

8.2.1 RS-232C的引脚定义

232C接口标准使用一个25针连接器 绝大多数设备只使用其中9个信号,所以就有了9针连接器 232C包括两个信道:主信道和次信道

微机原理与接口技术

北京工商大学信息工程学院

RS-232C的引脚(1)

TxD:发送数据

高电平:+2.4V~+5V 低电平:0V~0.4V

微机原理与接口技术

北京工商大学信息工程学院

8.3 可编程串行通信接口8251

串行传输,需要并行到串行和串行到并行的转换,并按照传 输协议发送和接收每个字符(或数据块) 通用同异步接收发送器USART是串行同异步通信的接口电路 芯片 典型芯片: Intel 8251,Zilog SIO, TNS公司生产的8250 , Motorola公司生产的6850、6952、8654。

微机原理与接口技术

北京工商大学信息工程学院

5. 8251A编程举例

[例1]编写接收数据的初始化程序。要求8251A 采用同步传送方式、2个同步字符、内同步、 偶校验、7位数据位和同步字符为16H。

微机原理与接口技术

北京工商大学信息工程学院

连接调制解调器

微机 MODEM MODEM 微机

2 3 4 5 6 7 8 20 22

发送数据TxD 接收数据RxD 请求发送RTS 允许发送CTS 数据装置准备好DSR 信号地GND 载波检测CD 数据终端准备好DTR 振铃指示RI

2 3 4 5 6 7 8 20 22

RxC:接收器时钟

控制数据终端接收串行数据的时钟信号

微机原理与接口技术

北京工商大学信息工程学院

微机原理与接口技术第八章

五、 8259A的初始化编程举例

包含的内容: ① 8259A的初始化 ② 完成中断向量表的设置 例:将单片8259A接入8088系统中,设计其端口地址为0FFF0H 和0FFF1H。 分析:控制字写入的时序,见下表:

A0 0 1 0 0 0 1 其连接如图所示 0 0 1 0 1 D4 D3

RD

WR

8.3 中断控制器8259A

Intel8259A是一种可编程的中断控制器,有如下功能:

1.可管理8个中断源电路的中断,并对其进行优先级管理; 2.具有8级中断优先控制,通过级连可以扩展至64级优先权控制; 3.对中断源有屏蔽或允许申请中断的操作; 4.CPU响应中断时,能自动提供中断类型码。

一、 8259A的内部结构

三、 8259A的工作过程

① 中断源 ② IRR

经IR0~IR7 请求

8259A,使IRR相应位置“1”; PR,PR 经判优,将最高INT CPU的INTR;

两个INTA

经IMR允许置位

③ 若CPU处于开中断,则完成当前指令后

8259A;

其中:8259收到第一个INTA时,a>使ISR相应位置“1”; b>使IRR相应位清“0”; 8259收到第二个INTA时

中断类型号

DB

④ 若8259工作在自动结束方式AEOI,则8259清除ISR相应位,

否则到全结束,发出EOI命令,才使ISR清“0”。

四、8259可编程命令

1. 初始化命令字 1)ICW1 --芯片控制字,格式如图所示 作用:对8259复位 a>对中断请求信号边沿检测电路复位,使信号低时产生中断 b>清除IMR c>设置全嵌套方式 2)ICW2字--中断类型号,格式如图所示 3)ICW3字--主/从片初始字(单片时不用此字) 主/从片8259A的格式分别如图所示 4)ICW4字格式--中断方式字,格式如图所示 主要用于决定8259工作于8080还是8086,以及是否要EOI命令

微机原理第八章--8251..

与读/写控制电路的控制信号: ①RESET:高电平复位,等待对其初始化。 ②CLK:为芯片内有关电路工作提供时钟的输入端。 同步:该频率大于接收/发送器的时钟频率的30倍;异步:大于4.5倍。 ③ WR、RD 、C/D 、CS、 D0 ~ D7 发送 并/串 数据总线 TXD 缓冲器 转换 缓冲器 TXRDY 发送控制电 TXEMPTY 内 路 RESET TXC 部 总 CLK 读/写 线 C/D 控制逻辑 O 电路 RD O WR 接收 串/并 RXD O 缓冲器 转换 CS RXRDY O DSR RXC 接收控制电路 O 调制 DTR 解调 SYNDET O CTS 电路 O RTS

(b)双同步

数据字节1 数据字节2 … 数据字节N CRC1 CRC2 (c)外同步 面向字符型同步通信数据格式

帧

帧

图

单同步:传送数据之前,先传送一个同步 字符“SYNC”,接收端检测到同步字符 后,开始接收数据。 双同步:两个同步字符“SYNC”,其后, 接着是数据。 外同步:用一条专用控制线来传送同步字 符,使接收方与发送方实现同步。

3.状态字:报告8251A何时才能开始发送或接收,以及接收数据 有无错误。状态位为 1 ,表示有效。在读状态期间, 8251A 将自 动禁止改变状态位。

D7 DSR D6 SYN D5 FE D4 OE D3 PE D2 TXE D1 D0 RXRDY TXRDY

1:进入SYN 搜索方式

例 3 :若要使 8251A 内部复位,假定命令口地址 为309H,则程序段为: MOV DX,309H ;8251命令口 MOV AL,40H ;置D6=1,使内部复位。 OUT DX,AL

例 4 :异步通信时,允许接收,同时允许发送, 则程序段为(命令口地址为309H): MOV DX,309H ;8251命令口 MOV AL,05H ;D2=1,D0=1,允许接收和发送。 OUT DX,AL

微机原理与接口技术[8-1]课件资料

![微机原理与接口技术[8-1]课件资料](https://img.taocdn.com/s3/m/d02de6180740be1e650e9a42.png)

. . .

息,引导程序进入中断服务子程序,这些中断在内

存中专门开辟一个区域,存放中断向量表(也称中 断矢量表)。

00000H

中断服务程序的入口地址构成的表 称为中断向量表

00004H

00008H

0000CH

003FCH

类型255的中断服 务程序入口地址

8086的中断向量表示意图

18:01

7

§8-1 概述-中断概念

4.中断优先级

当有多个中断源请求中断时,中断系统判别中 断申请的优先级,CPU响应优先级高的中断,挂起 优先级低的中断。 当CPU在运行中断服务子程序时,又有新的更 高优先级的中断申请进入,CPU要挂起原中断进入 更高级的中断服务子程序,实现中断嵌套功能。

18:01 3

§8-1 概述-中断概念

1.中断源

当CPU正常运行程序时,由于微处理器内部 事件或外设请求,引起CPU中断正在运行的程序, 转去执行请求中断的外设(或内部事件)的中断 服务子程序,中断服务程序执行完毕,再返回被 中止的程序,该过程称为中断。 中断源:引起程序中断的事件

中断源 中断响应 中断向量表 中断优先级 中断屏蔽

§8-1 概述-Βιβλιοθήκη 中断分类1. 外部中断① 不可屏蔽中断请求

INT n 指令 INTO 指令 除法 出错 单步 TF=1

非屏蔽中断请求

NMI

中断逻辑

INTR

8259A

可 屏 蔽 中 断 请 求

由CPU的引脚NMI引入,采用边沿触发,上升沿之后维持两个时钟

周期高电平有效。

微机原理CH8 微型计算机的中断系统(ok)

这一过程称为中断。

(2)特点

中断方式是一种常用的数据传送的控制方式

,利用中断可以避免不断检测外部设备状态,提 高CPU的效率。

3

第八章

2、中断源 引起程序中断的事件称为中断源。中断源有内部 中断和外部中断两种。内部中断由程序预先安排的指

令(INT n)引起,或CPU运算中产生某些错误引起;外

部中断是外部设备向CPU发出中断申请引起的。

13

第八章

2、CPU响应可屏蔽中断的过程 (1)CPU在每条指令的最后一个T周期,检测INTR,若

为高电平,且IF=1,则CPU响应中断。

(2)响应过程中自动依次完成以下工作:

① CPU向外设发两个/INTA ,外设收到第2个/INTA 后

,立即往数据线上给CPU送中断类型号。

② CPU从数据线上读取中断类型号; ③ 将PSW入栈;

8

第八章

2、内部中断(软件中断) 由三种情况引起: (1)由软中断指令INT n引起 INT n指令,类型号n(0-255)。

(2)由CPU运算错误引起

① 除法错中断:类型号0; ② 溢出中断:类型号4,由INTO指令引起的中断。

9

第八章

(3)由调试程序debug设置的中断

① 单步中断:

类型号1,TF=1时产生(当前指令需执行完), Debug状态下的T命令执行时产生;

绍可屏蔽中断的处理过程。

可屏蔽中断处理过程:

中断请求 中断响应 保护现场 转入执行中断服务子程序 恢复现场 中断返回

12

第八章

一、CPU响应可屏蔽中断过程

1、CPU响应可屏蔽中断的条件

(1)外设提出中断申请;

(2)本中断未被中断控制器屏蔽;

微机原理第八章

8255A作为A/D和D/A接口

MOV DX, 303H OUT DX,10110000B;端口A方式1 OUT DX,0001111B; OUT DX,0001110B;输出单脉冲启动AD转换 MOV DX,302H IN AL,DX TEST AL,0010000B;判断输入缓冲区满(IBF) MOV DX,300H IN AL,DX MOV DX,301H OUT DX,AL

PA:独立的8位I/O口,内部有对数据输入/输出的锁存功能。 PB:独立的8位I/O口,仅对输出数据的锁存功能 PC:可以是一个独立的8位I/O口;也可以是两个独立的4位I/O口。仅对输 出数据进行锁存。

三个通道分成两组控制:A组(PA+PC高4位)、B组(PB+PC低4位) 与CPU接口:数据总线缓冲器、读写逻辑控制

I/O PC7 ~ PC4 I/O PC3 ~ PC0

B组控 制电路

A组端口(8)

I/O PB7 ~ PB0

8255A的控制寄存器

功能 控制工作方式,最高位为1

D0:端口C低4位输入或输出(0--输出) D1:端口B输入或输出(0--输出) D2:端口B工作方式(1--方式1;0--方式0) D3:端口C高4位输入或输出 D4:端口A输入或输出 D6、D5:端口A工作方式(00:方式0;01:方式1;1X:方式2) D7:1

串行通信协议(同步和异步) 串行数据在传输线上的形式 串行通信连接形式

单工 半双工 全双工

波特率(传输率)

是衡量数据传送速率的指标。表示每秒钟传送的二进制位数。例如数据 传送速率为120字符/秒,而每一个字符为10位,则其传送的波特率为 10×120=1200字符/秒=1200波特 110、300、600、1200、2400、3600、4800、9600、19200

微机原理与应用第八章

无条件传送的输出实例:

300 x 8 数 据 总 线

+5V

74LS373

LE OE

CS WR

MOV DX, 160H MOV AL, [BX] OUT DX, AL

可认为: LED发光二极管 是“始终就绪” 的外设。

无条件传送的输入输出接口:

A0~A15

IOR IOW

译码 8000 H +5V G LS244 三态 缓冲器 CLK LS273 8D 锁存器 LS06 反相 驱动器

⑴ CPU对DMA控制器进行初始化设置 ⑵ 外设、DMAC和CPU三者通过应答信号建立 联系:CPU将总线交给DMAC控制 传送流程 ⑶ DMA传送

DMA读存储器:存储器 → 外设 DMA写存储器:存储器 ← 外设

8.1 8.2 8.3 8.4

微型计算机的输入/输出接口 并行通信与并行接口 可编程并行通信接口芯片8255A 串行通信与串行接口

DB

数据 信息

主

AB

机

CB

接口 电路

外 设

数据通常有四种类型:

状态 信息

控制 信息

模拟量不能直接进 入计算机,必须经 过A/D转换器

数字量:二进制形式的数据,或 是已经编过码的二进制 形式的数据。 (1位、8位、16位或32位) 模拟量:用模拟电压或电流幅值大 小表示的物理量。 开关量:有两个状态,即“开”或“关” 一位二进制数就可表示的量 脉冲量:以脉冲形式表示的一种信号

LED7

K0 K1

…

LED0

K7

+5V …

D0~D7

8086

next:

mov dx,8000h in al,dx not al out dx,al call delay jmp next

第8章(8251)PPT课件

1位,低电平“0”

5~8位,由低至高

0/1位,无/奇/ 偶

1/1.5/2位,高电平“1”

起 始 位

MARK

第n个字符 7位数据

奇 偶 校停 验止 位位

第(n+1)个字符

空

闲

位

下一个字符起始位

1 0 0/1 0/1 0/1 0/1 0/1 0/1 0/1 0/1 1 1 1 1 0 0/1 0/1

低 位 一位时间

第八章 可编程接口技术

0717-6394358,

三峡大学

1 8255A 2 8253/8254 3 8251A 4 DAC0832

5 ADC0809

串行通信基础

并行通信

➢ 一次传送多位,速度较快 ➢ 占用线路多,成本较高 ➢ 传送距离小(3m以内) ➢ 应用范围有限

串行通信

➢ 逐位顺序传送,速度较慢 ➢ 占用线路少,成本较低 ➢ 传送距离较远(≥15m) ➢ 应用范围很广

设位周期为Td,外部时钟周期为Tc,则存在等式:

Tc

Td K

其中K即为波特率因子,常见的波特率因子有1、16、64。

停止位或空闲位

接收输入数据 (110bps)

起始位(Td≈16Tc)

外部时钟 (16×110bps

1 1000000000

连续读出 9个 “0”

从此开始,下降沿指出 下一个字符的开始

9:16判别法

线上的AD7~AD0直接相连。

接收CPU向8251A发出的控制字; 接收并暂存CPU发来的数据; 暂存从串行接收器中接收的数据,等待CPU读取; 存放8251A的工作状态信息,便于CPU读取。

读/写控制逻辑

完成CPU对8251A接口芯片的寻址与读/写控制操作 ; 对数据在8251A的内部总线上传送的方向进行控制 。 C/D通常接地址线A0,占用两个口地址,与RD、CS相互配合,实现读写4个

微机原理_8251

8251 串行接口应用实验PB07210249 马运聪PB07210267 李嘉浩实验目的1.掌握8251 的工作方式及应用;2.了解有关串口通讯的知识。

实验设备1. PC机两台2. TD-PITE 实验装置两套实验内容1.数据信号的串行传输实验,循环向串口发送一个数,使用示波器测量TXD 引脚上的波形,以了解串行传输的数据格式。

2.自收自发实验,将3000H 起始的10 个单元中的初始数据发送到串口,然后自接收并保存到4000H 起始的内存单元中。

实验原理1.8251 的基本性能8251 是可编程的串行通信接口,可以管理信号变化范围很大的串行数据通信。

有下列基本性能:1)通过编程,可以工作在同步方式,也可以工作在异步方式;2)同步方式下,波特率为0~64K,异步方式下,波特率为0~19.2K;3)在同步方式时,可以用5~8位来代表字符,内部或外部同步,可自动插入同步字符;4)在异步方式时,也使用5~8位来代表字符,自动为每个数据增加1个启动位,并能够根据编程为每个数据增加1 个、1.5 个或2 个停止位;5)具有奇偶、溢出和帧错误检测能力;6)全双工,双缓冲器发送和接收器。

注意:8251 尽管通过了RS-232 规定的基本控制信号,但并没有提供规定的全部信号。

2.8251的编程对8251 的编程就是对8251 的寄存器的操作,下面分别给出8251 的几个寄存器的格式。

(1)方式控制字方式控制字用来指定通信方式及其方式下的数据格式,具体各位的定义如下图所示:(2)命令控制字命令控制字用于指定8251 进行某种操作(如发送、接收、内部复位和检测同步字符等)或处于某种工作状态,以便接收或发送数据。

下图所示的是8251 命令控制字各位的定义。

(3)状态字CPU 通过状态字来了解8251 当前的工作状态,以决定下一步的操作,8251 的状态字如下图:实验步骤1.数据信号的串行传输发送往串口的数据会以串行格式从TXD 引脚输出,编写程序,观察串行输出的格式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

校验选择 01:奇校验 11 :偶校验 ×0 :不校验

00 01 10 11 字符长度 00 —5位 01 —6位 10 —7位 11 —8位

同步方式 异步 1 异步 16 异步 64

波 特 率 因 子

例1:在某异步通信中,数据格式采用8位数据位,1位 起始位,2位停止位,奇校验,波特率因子是16,求 其方式命令字?将该方式命令字写入命令口,则程 序段为(假定命令口地址为309H): MOV DX, 309H 方式命令字=? MOV AL, 0DEH 11011110B=DEH OUT DX,AL 例2:在同步通信中,若帧数据格式为:字符长度8位, 双同步字符,内同步方式,奇校验,求其方式命令字? 将其方式命令字写入命令口,则程序段为(假定命令口 地址为309H): MOV DX, 309H 同步方式命令字=? MOV AL, 1CH 00011100B=1CH OUT DX,AL

发送

(a)单工通信 发送

接收

发送 (b)半工通信

接收

发送 接收 图8-21

接收

发送

(c)全工通信 串行通信线路的三种连接方式

接收

串行通信的特点: 串行通信只要一条传输线,将数据逐位顺序传送; 通信成本低,速度慢,接口复杂。

8.4.2串行接口

并串变换寄存器 通信线路

……..

………...

串并变换寄存器

2、操作命令控制字:命令8251A进行某种操作(如发 送、接收、内部复位和检测同步字符等)或处于某种 工作状态(如DTR),以便接收或发送数据。

D7 EH D6 IR D5 RTS D4 ER D3 SBRK D2 RXE D1 DTR D0 TXEN

1:发送允许 0:不允许

1:使DTR引脚 = 0 1 :接收允许 1 :TXD送低电平(断开信号) 0 :正常工作 1:使错误标志复位(状态寄存器) 1:使RTS引脚 = 0 1:软件复位(下一条命令是方式字)

1 、方式命令:指定通信方式、数据格式、传送速 率及停止位长度等。(分成4组,每组2位)

S2 S1 EP PEN L2

L1

B2

B1

异步(D1D0≠00) 同步(D1:D0)=00) ×0:内同步 ×1:外同步 0×:双SYN 1×:单SYN 00 无效 01, 1个停止位 10 ,1.5个停止位 11,2个停止位

D2 D3 RXD GND D4 D5 D6 D7 TXC WR CS C/D RD RXRDY

D1 D0 VCC RXC

DTR RTS DSR RESET CLK TXD TXEMPTY CTS SYNDET/ BRKDET TXRDY

图

8251引脚分布

8.5.2 8251A的控制字及其工作方式

与读/写控制电路的控制信号: ①RESET:高电平复位,等待对其初始化。 ②CLK:为芯片内有关电路工作提供时钟的输入端。 同步:该频率大于接收/发送器的时钟频率的30倍;异步:大于4.5倍。 ③ WR、RD 、C/D 、CS、 D0 ~ D7 发送 并/串 数据总线 TXD 缓冲器 转换 缓冲器 TXRDY 发送控制电 TXEMPTY 内 路 RESET TXC 部 总 CLK 读/写 线 C/D 控制逻辑 O 电路 RD O WR 接收 串/并 RXD O 缓冲器 转换 CS RXRDY O DSR RXC 接收控制电路 O 调制 DTR 解调 SYNDET O CTS 电路 O RTS

RXD

RXRDY RXC SYNDET

DTR CTS RTS

O

O

调制 解调 电路

接收控制电路

与接收器有关信号: ①RXD:数据接收端。RXD在时钟RXC上升沿采样信号。 ②RXRDY:接收器已准备好信号,表示已收到一个数据, 当CPU读数据后,RXRDY变为低电平。 ③SYNDET/BRKDET——双功能的检测信号,高电平有效。 内同步:收到一个或两个同步字符时,SYNDET输出高 电平。 外同步:当从SYNDET端收到同步字符,接收器开始接 收数据。 ④RXC:接收器时钟,由外部输入。若采用同步方式, 接收器时钟频率等于接收数据的频率;异步方式,用 软件设置波特率,TXC和RXC往往连接在一起。 对于异步方式,当RXD端口连续收到8个“0”信号, 则BRKDET变成高电平,表示当前处于数据断缺状态。

(2)面向比特型的数据格式:根据同步数据链 路控制规程( SDLC ),面向比特型的数据以 帧为单位传输,每帧由6个部分组成。如下图:

帧

7EH 地址场 控制场 D0 D1 … DN CRC1 CRC2 7EH

开始 标志 图

数据 面向比特型的数据格式

结束 标志

在SDLC规程中,不允许在数据段和CRC段中出 现6个“1”,否则会误认为是结束标志。因此要求 在发送端进行检验,当连续出现5个“1”,则立即 插入一个“0”,接收端要将这个插入的“0”去掉, 恢复原来的数据。同步通信的效率比异步通信高。

(b)双同步

数据字节1 数据字节2 … 数据字节N CRC1 CRC2 (c)外同步 面向字符型同步通信数据格式

帧

帧

图

单同步:传送数据之前,先传送一个同步 字符“SYNC”,接收端检测到同步字符 后,开始接收数据。 双同步:两个同步字符“SYNC”,其后, 接着是数据。 外同步:用一条专用控制线来传送同步字 符,使接收方与发送方实现同步。

1:进入SYN 搜索方式

例 3 :若要使 8251A 内部复位,假定命令口地址 为309H,则程序段为: MOV DX,309H ;8251命令口 MOV AL,40H ;置D6=1,使内部复位。 OUT DX,AL

例 4 :异步通信时,允许接收,同时允许发送, 则程序段为(命令口地址为309H): MOV DX,309H ;8251命令口 MOV AL,05H ;D2=1,D0=1,允许接收和发送。 OUT DX,AL

O O O O O

接收 串/并 缓冲器 转换

RXD RXRDY RXC SYNDET

DTR CTS RTS

O

调制 解调 电路

接收控制电路

图 8251A内部结构流程图

与发送器有关信号: ①TXD:发送数据。在时钟TXC的下降沿发送数据。 ②TXC:发送器时钟信号,输入。 ③ TXRDY:发送器已准备好信号。表示发送数据缓 冲存储器空。 ④ TXEMPTY:发送器空闲标志。表示发送移位寄存 器已空。

波特率与发送/接收时钟的关系为: 收/发时钟 b/ s = n

n:波特率因子,(可取 1, 16, 64)

1.异步通信方式

异步通信的数据格式是以一组不定“位数” 数组成。第 1 位起始位,低电平;接着传送若 干个数据位,先发低位,后发高位;最后是停 止位,宽度可以是 1 位, 1.5 位或 2 位;在两个 数据组之间可有空闲。其数据格式如图所示。 标准波特率: 300,600,900,1200,2400,4800,9600,19200。

RXD

RXRDY RXC SYNDET

DTR CTS RTS

O

O

调制 解调 电路

接收控制电路

4、读/写控制和调制控制: 读/写控制电路用来接收一系列的控制信号, 并向其内部各功能部件发出有关的控制信号。

与读/写控制电路的控制信号: ①RESET:高电平复位,等待对其初始化。 ②CLK:为芯片内有关电路工作提供时钟的输入端。 同步:该频率大于接收/发送器的时钟频率的30倍;异步: 大于4.5倍。 ③ WR、RD 、C/D 、CS、

5 、调制 / 解调控制电路:当远距离串行通信时, 发送时,MODEN将数字信号转换成模拟信号;接 收时,MODEN将模拟信号转换为数字信号。 与MODEN的控制信号 ①DTR(Data Terninal Ready):向MODEN输出, CPU已准备好,工作命令字的D1置‘1’变为有效。 ②DSR(Data Set Ready):由MODEN输入,表 示MODEN已准备好,CPU通过读状态寄存器的D7 位检测该信号。 ③RTS(Request To Send):通知MODEN,CPU 准备好发送,工作命令字的D5置‘1’变为有效。 ④CTS(Clear To Send):当有效时,表示 8251A方可发送数据。

8.5 可编程串行接口芯片8251A

INTEL 8251A 是一个通用串行输入 / 输出 接口,可以同步方式(或异步方式)与外设 进行串行通信。广泛应用于长距离通信系统 及计算机网络。 8.5.1 8251A芯片内部结构及其功能 8251A由发送器、接收器、数据缓冲存储器、 读/写控制电路及调制/解调控制电路等5部分组 成,如图所示。

2、接收器:外部通信数据从RXD端,逐位进入接收移位 寄存器中。

D0 ~ D7

数据总线 缓冲器

发送 并/串 缓冲器 转换 内 部 总 线 发送控制电 路

TXD

TXRDY TXEMPTY TXC

RESET CLK C/D RD WR CS

DSR

O O

读/写 控制逻辑 O 电路

O O

接收 串/并 缓冲器 转换

8.4

串行通信及串行接口

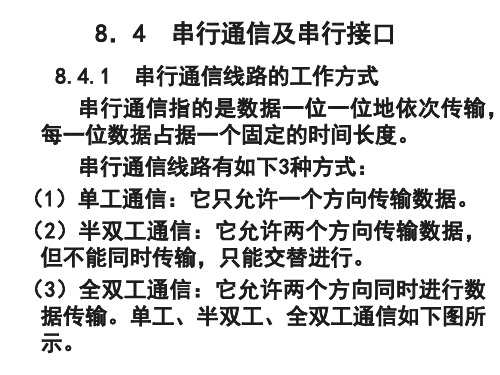

8.4.1 串行通信线路的工作方式 串行通信指的是数据一位一位地依次传输, 每一位数据占据一个固定的时间长度。 串行通信线路有如下3种方式: (1)单工通信:它只允许一个方向传输数据。 (2)半双工通信:它允许两个方向传输数据, 但不能同时传输,只能交替进行。 (3)全双工通信:它允许两个方向同时进行数 据传输。单工、半双工、全双工通信如下图所 示。

3.状态字:报告8251A何时才能开始发送或接收,以及接收数据 有无错误。状态位为 1 ,表示有效。在读状态期间, 8251A 将自 动禁止改变状态位。

D7 DSR D6 SYN D5 FE D4 OE D3 PE D2 TXE D1 D0 RXRDY TXRDY

5~8数据位 空闲