Makefile两个实验教案

Makefile编程实验

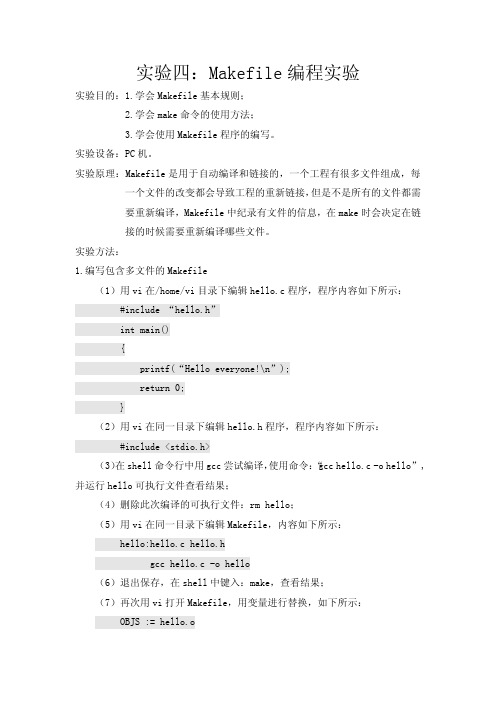

实验四:Makefile编程实验实验目的:1.学会Makefile基本规则;2.学会make命令的使用方法;3.学会使用Makefile程序的编写。

实验设备:PC机。

实验原理:Makefile是用于自动编译和链接的,一个工程有很多文件组成,每一个文件的改变都会导致工程的重新链接,但是不是所有的文件都需要重新编译,Makefile中纪录有文件的信息,在make时会决定在链接的时候需要重新编译哪些文件。

实验方法:1.编写包含多文件的Makefile(1)用vi在/home/vi目录下编辑hello.c程序,程序内容如下所示:#include“hello.h”int main(){printf(“Hello everyone!\n”);return0;}(2)用vi在同一目录下编辑hello.h程序,程序内容如下所示:#include<stdio.h>(3)在shell命令行中用gcc尝试编译,使用命令:“gcc hello.c-o hello”,并运行hello可执行文件查看结果;(4)删除此次编译的可执行文件:rm hello;(5)用vi在同一目录下编辑Makefile,内容如下所示:hello:hello.c hello.hgcc hello.c-o hello(6)退出保存,在shell中键入:make,查看结果;(7)再次用vi打开Makefile,用变量进行替换,如下所示:OBJS:=hello.oCC:=gcchello:$(OBJS)$(CC)$^-o$@(8)退出保存,在shell中键入make,查看结果;(9)用vi在同一目录下编辑makefile1,内容如下所示:hello:hello.ogcc hello.o-o hellohello.o:hello.c hello.hgcc-c hello.c-o hello.o(10)退出保存,在shell中键入:make-f makefile1,查看结果;(11)再次用vi编辑makefile1,内容如下所示:OBJS1:=hello.oOBJS2:=hello.c hello.hCC:=gcchello:$(OBJS1)$(CC)$^-o$@$(OBJS1):$(OBJS2)$(CC)-c$<-o$@在这里请注意区别“$^”和“$<”;(12)退出保存,在shell中键入:make-f makefile1,查看结果;2.使用autotools生成包含多文件的Makefile(1)在/home/vi目录下新建文件夹auto:#mkdir./auto(2)将/home/vi目录下的hello.c和hello.h文件复制到/home/vi/auto 目录下,然后进入到/home/vi/auto目录里面:#cp/home/vi/hello.*/home/vi/auto#cd/home/vi/auto(3)执行命令:#autoscan(4)使用vi编辑当前目录下的configure.scan文件为,主要是蓝色部分:#-*-Autoconf-*-#Process this file with autoconf to produce a configure script.AC_PREREQ(2.59)AC_INIT(hello, 1.0)AM_INIT_AUTOMAKE(hello,1.0)AC_CONFIG_SRCDIR([hello.h])AC_CONFIG_HEADER([config.h])#Checks for programs.AC_PROG_CC#Checks for libraries.#Checks for header files.#Checks for typedefs,structures,and compiler characteristics.#Checks for library functions.AC_OUTPUT(makefile)(5)保存退出,并重命名为configure.in;(6)执行命令:#aclocal(7)执行命令:#autoconf并用ls或ll命令查看是否生成了configure可执行文件;(8)执行命令:#autoheader(9)在当前目录下用vi创建makefile.am文件为:AUTOMAKE_OPTIONS=foreignbin_PROGRAMS=hellohello_SOURCES=hello.c hello.h(10)执行命令:#automake然后再执行下面的命令:#automake-a(11)执行命令:#./configure(12)执行命令:#make(13)执行命令:#./hello查看结果是否正确;(14)执行命令:#Make install(15)执行命令:#hello查看结果是否正确;(16)执行命令:#make dist(17)在当前目录下解压文件hello-1.0.tar.gz:#tar-zxvf hello-1.0.tar.gz(18)进入解压目录:#cd./hello-1.0(19)下面开始Linux下常见的安装软件步骤:#./configure(20)执行命令:#make(21)执行命令:#./hello注意:在正常安装时这一步可省略;(22)执行命令:#make install(23)执行命令:#hello查看结果是否正确。

Makefile两个实验

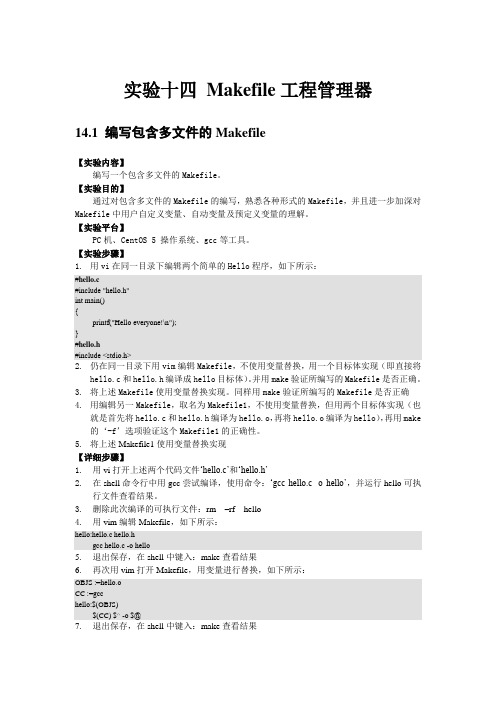

实验十四Makefile工程管理器14.1 编写包含多文件的Makefile【实验内容】编写一个包含多文件的Makefile。

【实验目的】通过对包含多文件的Makefile的编写,熟悉各种形式的Makefile,并且进一步加深对Makefile中用户自定义变量、自动变量及预定义变量的理解。

【实验平台】PC机、CentOS 5 操作系统、gcc等工具。

【实验步骤】1.用vi在同一目录下编辑两个简单的Hello程序,如下所示:#hello.c#include "hello.h"int main(){printf("Hello everyone!\n");}#hello.h#include <stdio.h>2.仍在同一目录下用vim编辑Makefile,不使用变量替换,用一个目标体实现(即直接将hello.c和hello.h编译成hello目标体)。

并用make验证所编写的Makefile是否正确。

3.将上述Makefile使用变量替换实现。

同样用make验证所编写的Makefile是否正确4.用编辑另一Makefile,取名为Makefile1,不使用变量替换,但用两个目标体实现(也就是首先将hello.c和hello.h编译为hello.o,再将hello.o编译为hello),再用make 的‘-f’选项验证这个Makefile1的正确性。

5.将上述Makefile1使用变量替换实现【详细步骤】1.用vi打开上述两个代码文件‘hello.c’和‘hello.h’2.在shell命令行中用gcc尝试编译,使用命令:‘gcc hello.c -o hello’,并运行hello可执行文件查看结果。

3.删除此次编译的可执行文件:rm –rf hello4.用vim编辑Makefile,如下所示:hello:hello.c hello.hgcc hello.c -o hello5.退出保存,在shell中键入:make查看结果6.再次用vim打开Makefile,用变量进行替换,如下所示:OBJS :=hello.oCC :=gcchello:$(OBJS)$(CC) $^ -o $@7.退出保存,在shell中键入:make查看结果8.用vim编辑Makefile1,如下所示:hello:hello.ogcc hello.o -o hellohello.o:hello.c hello.hgcc -c hello.c -o hello.o9.退出保存,在shell中键入:make –f Makefile1查看结果10.再次用vi编辑Makefile1,如下所示:OBJS1 :=hello.oOBJS2 :=hello.c hello.hCC :=gcchello:$(OBJS1)$(CC) $^ -o $@$(OBJS1):$(OBJS2)$(CC) -c $< -o $@在这里请注意区别‘$^’和‘$<’。

linux实验二交叉编译和Makefile实验报告

[root @localhost hehui]# ./hmily

④使用交叉编译器编译并运行。

A.[root @localhost hehui]# arm-linux-gcc -o hmily ji_oushu.c

B.打开另外一个终端,输入minicom进入板子里去。

C.操作一下命令。

[root @localhost ~]# cd 2008550533

[root @localhost 2008550533]# mkdir hehui

[root @localhost ~]# cd hehui

[root @localhost hehui]# vi ji_oushu.c

/*输出50以内的奇数和偶数*/

④使用gcc编译,查看运行结果。

[root @localhost prime]# gcc prime.c -oprime_hehui

[root @localhost prime]# ./prime_hehui

⑤编写Makefile文件实现第④步功能,并使用make工具生成这个可执行文件。

[root @localhost prime]# rm -r prime_hehui

all:prime

prime:prime.o main.o

$(CC) $(CFLAGS) $^ -o $@

prime.o:prime.c

$(CC) $(CFLAGS) -c $< -o $@

main.o:main.c prime.h

$(CC) $(CFLAGS) -c $< -o $@

clean:

rm -fr prime_hehui *.o

clean: 37

实验二 Makefile实验

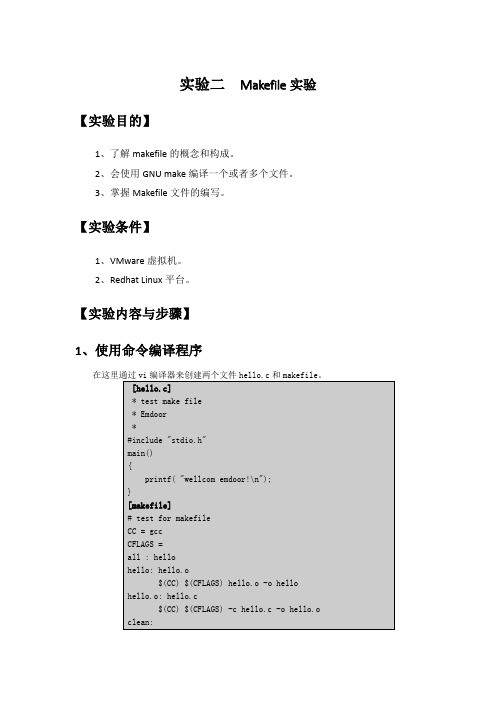

实验二M akefile实验【实验目的】1、了解makefile的概念和构成。

2、会使用GNU make编译一个或者多个文件。

3、掌握Makefile文件的编写。

【实验条件】1、VMware虚拟机。

2、Redhat Linux平台。

【实验内容与步骤】1、使用命令编译程序在这里通过vi编译器来创建两个文件hello.c和makefile。

[hello.c]* test make file* Emdoor*#include "stdio.h"main(){printf( "wellcom emdoor!\n");}[makefile]# test for makefileCC = gccCFLAGS =all : hellohello: hello.o$(CC) $(CFLAGS) hello.o -o hellohello.o: hello.c$(CC) $(CFLAGS) -c hello.c -o hello.o clean:在将上述Makefile文件与源文件hello.c保存到同一目录之后,就可以在命令行中输入“make”命令来编译整个项目了。

make在执行过程中,首先会查找到Makefile文件第一条规则中的目标,即上述文件中的all。

根据设定好的规则,该目标需要依赖于hello。

由于all并不是一个已经存在的文件,所以每次在make被调用的时候,显然都需要先检查hello。

继续往下不难发现,hello目标是依赖于hello.o。

当make处理到目标hello.o时,会先查看其对应的依赖对象,这个以来对象是hello.c,此时就会对hello.c进行编译,得到目标文件hello.o,然后是目标文件hello.o被连接,得到可执行文件hello。

先后执行如下命令:可以看到输出结果:在Makefile中,并不是所有的目标都对应于磁盘上的文件。

有的目标存在只是为了形成一条规则,从而完成特定的工作,并不生成新的目标文件,这样的目标称为伪目标。

实验二 Makefile实验

6

Makefile主要预定义变量及隐含 规则

预定义变量及其含义 CC CCFLAGS …… GNU make 支持两种类型的隐含规则: 后缀规则(Suffix Rule) 模式规则(pattern rules)

亿道电子有限公司出品

亿道电子有限公司出品

4

Makefile的基本结构

目标 --- 需要由 make 工具创建的项目, 通常是目标文件和可执行文件 。 依赖 ---要创建的项目依赖于哪些文件 命令 ---创建每个项目时需要运行的命令 target : dependency ...

make编译一个或者多个文件

亿道电子有限公司出品

3

Makefile的规则

如果这个工程没有编译过,那么我们的所 有C文件都要编译并被链接。 如果这个工程的某几个C文件被修改,那 么我们只编译被修改的C文件,并链接目 标程序。 如果这个工程的头文件被改变了,那么我 们需要编译引用了这几个头文件的C文件, 并链接目标程序。

亿道电子有限公司出品

12

思考与习题

工程中多级目录中存在着多个makefile时, 编译的顺序如何? 如果要编译生成的文件能够在EELIOD实验 平台上面使用,应该怎么对makefile修改?

亿道电子有限公司出品

13

亿道电子有限公司出品

10

使用wildcard对多个.c文件编译

wildcard’函数的一个功能是找出目录中所 有的’.c’文件: $(wildcard *.c) SOURCES = $(wildcard *.c) 这行会产生一个所有以 '.c' 结尾的文件 的列表,然后存入变量 SOURCES 里。 当然你不需要一定要把结果存入一个变量。

linux实验三makefile,linux内核编译生成makefile文件实验报告.doc

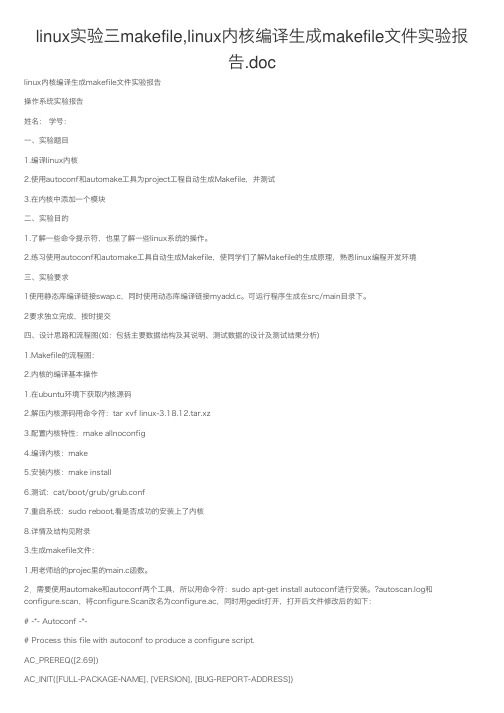

linux实验三makefile,linux内核编译⽣成makefile⽂件实验报告.doclinux内核编译⽣成makefile⽂件实验报告操作系统实验报告姓名: 学号:⼀、实验题⽬1.编译linux内核2.使⽤autoconf和automake⼯具为project⼯程⾃动⽣成Makefile,并测试3.在内核中添加⼀个模块⼆、实验⽬的1.了解⼀些命令提⽰符,也⾥了解⼀些linux系统的操作。

2.练习使⽤autoconf和automake⼯具⾃动⽣成Makefile,使同学们了解Makefile的⽣成原理,熟悉linux编程开发环境三、实验要求1使⽤静态库编译链接swap.c,同时使⽤动态库编译链接myadd.c。

可运⾏程序⽣成在src/main⽬录下。

2要求独⽴完成,按时提交四、设计思路和流程图(如:包括主要数据结构及其说明、测试数据的设计及测试结果分析)1.Makefile的流程图:2.内核的编译基本操作1.在ubuntu环境下获取内核源码2.解压内核源码⽤命令符:tar xvf linux-3.18.12.tar.xz3.配置内核特性:make allnoconfig4.编译内核:make5.安装内核:make install6.测试:cat/boot/grub/grub.conf7.重启系统:sudo reboot,看是否成功的安装上了内核8.详情及结构见附录3.⽣成makefile⽂件:1.⽤⽼师给的projec⾥的main.c函数。

2.需要使⽤automake和autoconf两个⼯具,所以⽤命令符:sudo apt-get install autoconf进⾏安装。

?autoscan.log和configure.scan,将configure.Scan改名为configure.ac,同时⽤gedit打开,打开后⽂件修改后的如下:# -*- Autoconf -*-# Process this file with autoconf to produce a configure script.AC_PREREQ([2.69])AC_INIT([FULL-PACKAGE-NAME], [VERSION], [BUG-REPORT-ADDRESS])AC_CONFIG_SRCDIR([main.c])AC_CONFIG_HEADERS([config.h])AM_INIT_AUTOMAKE(main,1.0)# Checks for programs.AC_PROG_CC# Checks for libraries.# Checks for header files.# Checks for typedefs, structures, and compiler characteristics.# Checks for library functions.AC_OUTPUT(Makefile)4.新建Makefile⽂件,如下:AUTOMAKE_OPTIONS=foreignbin_PROGRAMS=mainfirst_SOURCES=main.c5.运⾏命令aclocal命令成功之后,在⽬录下会产⽣aclocal.m4和autom4te.cache两个⽂件。

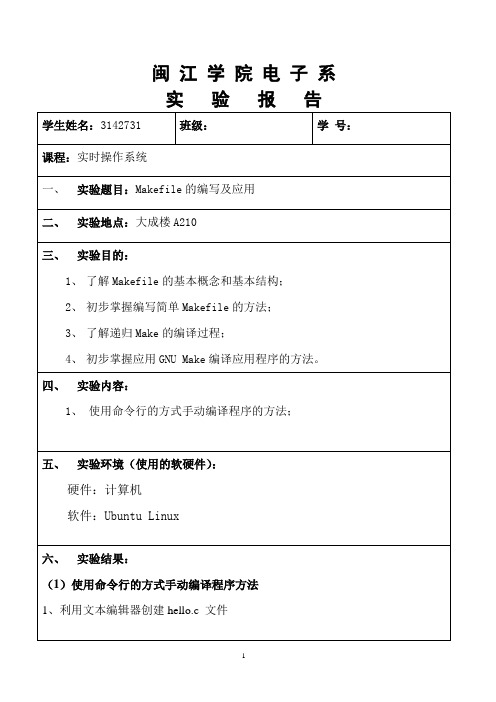

实验三 Makefile的编写及应用

闽江学院电子系实验报告2、手动编译hello 应用程序在hello.c 的目录的终端下输入:#gcc -c hello.c#gcc hello.o -o hello通过ls 命令查看当前目录下是否生成源代码hello.c 的object 文件hello.o 和可执行文件hello,运行可执行文件hello。

查看一下运行结果。

3、修改hello.c 文件,重新手动编译应用程序。

4、删除hello.o 和hello 文件#rm -f hello.o#rm -f hello(2) 利用GNU make 自动编译应用程序方法1、利用文本编辑器创建一个Makefile 文件,并将其保存到与hello.c 相同的目录下。

2、先执行如下命令。

#make#ls#./hello查看并记录所生成的文件和运行的结果。

3、执行make clean 命令:4、修改hello.c 文件,重复第2、3 步操作,查看并记录所生成的文件和运行结果,并与手动编译进行比较,写出你的结论。

5、重新编辑Makefile 文件(斜黑体表示修改部分)6、重复第2,3 步操作,查看并记录所生成的文件和运行的结果。

比较这两种操作,写出你的结论。

同时指出$^ 、$@、$<在上述Makefile 中的含义。

说明: $@ 规则目标文件名$< 规则第一个依赖文件名$^ 规则的所有文件列表使用自动化变量可以不必写出目标文件名及依赖文件表列。

尤其在生成多个目标文件生成一个可执行文件中优点更加突出。

(3)多个.c 文件的编译1、创建文件hello1.c、hello2.c、hello.h2、参考前文Makefile样例,动手编写编译多文档的Makefile文件。

3、先后执行如下命令#make -f Makefile1#ls#./hello4、修改Makefile 文件,添加两个变量定义,并修改相应的规则及指令。

5、重复第3 步操作,查看并记录所生成的文件和运行的结果, 写出你的结论。

makefile工具的使用实验原理

makefile工具的使用实验原理一、Makefile工具概述Makefile是一种自动化编译工具,用于管理程序的编译和链接过程。

它可以根据程序的依赖关系,自动判断哪些文件需要重新编译,从而提高程序的编译效率。

二、Makefile工具的基本语法Makefile文件由一系列规则组成,每个规则包含一个目标、依赖关系和命令。

其中,目标指的是要生成的文件,依赖关系指的是生成该文件所需要依赖的其他文件或目标,命令指的是生成该目标文件所需要执行的命令。

三、Makefile工具中变量和函数在Makefile中可以定义变量和函数来简化代码和提高可维护性。

变量可以用来存储常量或计算结果,函数可以用来处理字符串等操作。

四、Makefile工具中常见命令1. 编译命令:gcc -c source.c -o object.o2. 链接命令:gcc object.o -o target3. 清除命令:rm -f target object.o五、Makefile工具实验步骤1. 创建源代码文件和头文件。

2. 创建Makefile文件,并定义变量和函数。

3. 定义规则,并设置目标、依赖关系和命令。

4. 执行make命令进行编译链接。

5. 执行make clean命令清除生成的目标文件。

六、Makefile工具实验注意事项1. Makefile文件中的变量和函数必须使用$符号进行引用。

2. 目标文件和依赖关系之间必须使用冒号分隔符。

3. 命令必须以Tab键开头,否则会报错。

4. Makefile文件中的注释可以使用#符号。

七、Makefile工具实验示例以下是一个简单的Makefile示例,用于编译一个C语言程序:```# 定义变量CC = gccCFLAGS = -Wall -g# 定义规则target: main.o func.o$(CC) main.o func.o -o targetmain.o: main.c func.h$(CC) $(CFLAGS) -c main.cfunc.o: func.c func.h$(CC) $(CFLAGS) -c func.cclean:rm -f target *.o```在该示例中,定义了两个变量CC和CFLAGS,分别表示编译器和编译选项。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Makefile工程管理器14.1 编写包含多文件的Makefile【实验内容】编写一个包含多文件的Makefile。

【实验目的】通过对包含多文件的Makefile的编写,熟悉各种形式的Makefile,并且进一步加深对Makefile中用户自定义变量、自动变量及预定义变量的理解。

【实验平台】PC机、CentOS 5 操作系统、gcc等工具。

【实验步骤】1.用vi在同一目录下编辑两个简单的Hello程序,如下所示:#hello.c#include "hello.h"int main(){printf("Hello everyone!\n");}#hello.h#include <stdio.h>2.仍在同一目录下用vim编辑Makefile,不使用变量替换,用一个目标体实现(即直接将hello.c和hello.h编译成hello目标体)。

并用make验证所编写的Makefile是否正确。

3.将上述Makefile使用变量替换实现。

同样用make验证所编写的Makefile是否正确4.用编辑另一Makefile,取名为Makefile1,不使用变量替换,但用两个目标体实现(也就是首先将hello.c和hello.h编译为hello.o,再将hello.o编译为hello),再用make的‘-f’选项验证这个Makefile1的正确性。

5.将上述Makefile1使用变量替换实现【详细步骤】1.用vi打开上述两个代码文件‘hello.c’和‘hello.h’2.在shell命令行中用gcc尝试编译,使用命令:‘gcc hello.c -o hello’,并运行hello可执行文件查看结果。

3.删除此次编译的可执行文件:rm –rf hello4.用vim编辑Makefile,如下所示:hello:hello.c hello.hgcc hello.c -o hello5.退出保存,在shell中键入:make查看结果6.再次用vim打开Makefile,用变量进行替换,如下所示:OBJS :=hello.oCC :=gcchello:$(OBJS)$(CC) $^ -o $@7.退出保存,在shell中键入:make查看结果8.用vim编辑Makefile1,如下所示:hello:hello.ogcc hello.o -o hellohello.o:hello.c hello.hgcc -c hello.c -o hello.o9.退出保存,在shell中键入:make –f Makefile1查看结果10.再次用vi编辑Makefile1,如下所示:OBJS1 :=hello.oOBJS2 :=hello.c hello.hCC :=gcchello:$(OBJS1)$(CC) $^ -o $@$(OBJS1):$(OBJS2)$(CC) -c $< -o $@在这里请注意区别‘$^’和‘$<’。

11.退出保存,在shell中键入:make –f Makefile1查看结果14.2嵌套Makefile实验【实验目的】1、读懂makefile文件,能根据makefile文件理清程序结构2、能编写简单makefile3、掌握嵌套执行makefile【实验环境】PC机、CentOS 5 操作系统,gcc等工具。

【实验步骤】我们要创建的目录结构如下:顶层Makefile1.创建顶层目录我们首先在用户目录下创建一个makefileTest的文件夹:#cd /opt#mkdir makefileTest#cd makefileTest创建好需要用到的文件夹#mkdir f1 f2 main obj include进入include文件夹创建一个共用头文件#cd include#vim myinclude.h输入如下内容:#include <stdio.h>保存退出返回顶层目录:#cd ..2.创建顶层Makefile文件#vim Makefile输入以下内容:CC = gccSUBDIRS = f1 \f2 \main \objOBJS = f1.o f2.o main.oBIN = myappOBJS_DIR = objBIN_DIR = binexport CC OBJS BIN OBJS_DIR BIN_DIRall : CHECK_DIR $(SUBDIRS)CHECK_DIR :mkdir -p $(BIN_DIR) $(SUBDIRS) : ECHOmake -C $@ECHO:@echo $(SUBDIRS)@echo begin compileCLEAN :@$(RM) $(OBJS_DIR)/*.o@rm -rf $(BIN_DIR)3.进入在f1目录下创建makefile #cd f1#vim f1.c输入如下测试代码:#include “../include/myinclude.h”void print1(){printf("Message from f1.c...\n");return;}保存退出。

#vim Makefile输入如下内容:../$(OBJS_DIR)/f1.o: f1.c$(CC) -c $^ -o $@保存退出。

进入f2目录#cd ../f2#vim f2.c输入如下测试代码:#include “../include/myinclude.h”void print2(){printf("Message from f2.c…\n");return;}保存退出。

#vim Makefile输入如下内容:../$(OBJS_DIR)/f2.o: f2.c$(CC) -c $^ -o $@保存退出。

进入main目录#cd ../main#vim main.c输入如下内容:#include <stdio.h>int main(){print1();print2();return 0;}保存退出。

#vim Makefile输入如下内容:../$(OBJS_DIR)/main.o: main.c$(CC) -c $^ -o $@保存退出。

进入obj目录#cd ../obj#vim Makefile输入如下内容:../$(BIN_DIR)/$(BIN) : $(OBJS)$(CC) -o $@ $^好了,到此准备工作已经完毕,然我们来测试一下写的makefile是否好用。

进入顶层Makefile所在目录,即makefileTest目录。

#make会出现如下信息:目录树结构如下:我们看到在bin目录下生成了我们的目标文件myapp,在obj目录下生成了.o的中间文件。

让我们运行下myapp看下结果吧。

#bin/myapp我们也可以用如下命令清除中间文件和目标文件,恢复make之前的状态:#make CLEAN我们可以看到已经变为make之前的目录状态了。

大功告成。

最后给大家解释一下顶层makefile中一些命令的的含义吧。

a)我们注意到有一句@echo $(SUBDIRS)@echo其实是一句显示命令通常,make会把其要执行的命令行在命令执行前输出到屏幕上。

当我们用“@”字符在命令行前,那么,这个命令将不被make显示出来,最具代表性的例子是,我们用这个功能来像屏幕显示一些信息。

如:@echo 正在编译XXX模块......当make执行时,会输出“正在编译XXX模块......”字串,但不会输出命令,如果没有“@”,那么,make将输出:echo 正在编译XXX模块......正在编译XXX模块......如果make执行时,带入make参数“-n”或“--just-prin t”,那么其只是显示命令,但不会执行命令,这个功能很有利于我们调试我们的Makefile,看看我们书写的命令是执行起来是什么样子的或是什么顺序的。

而make参数“-s”或“--slient”则是全面禁止命令的显示。

b)@(RM)并不是我们自己定义的变量,那它是从哪里来的呢?通常在清除文件的伪目标所定义的命令中“rm”使用选项“–f”(--force)来防止在缺少删除文件时出错并退出,使“make clean”过程失败。

也可以在“rm”之前加上“-”来防止“rm”错误退出,这种方式时 make 会提示错误信息但不会退出。

为了不看到这些讨厌的信息,需要使用上述的第一种方式。

另外 make存在一个内嵌隐含变量“RM”,它被定义为:“RM = rm –f”。

因此在书写“clean”规则的命令行时可以使用变量“$(RM)”来代替“rm”,这样可以免出现一些不必要的麻烦!这是我们推荐的用法。

c)make -C $@这是一句嵌套makefile的语法,在一些大的工程中,我们会把我们不同模块或是不同功能的源文件放在不同的目录中,我们可以在每个目录中都书写一个该目录的Makefile,这有利于让我们的Makefile变得更加地简洁,而不至于把所有的东西全部写在一个Makefile中,这样会很难维护我们的Makefile,这个技术对于我们模块编译和分段编译有着非常大的好处。

例如,我们有一个子目录叫subdir,这个目录下有个Makefile文件,来指明了这个目录下文件的编译规则。

那么我们总控的Makefile可以这样书写:subsystem:cd subdir && $(MAKE)其等价于:subsystem:$(MAKE) -C subdir定义$(MAKE)宏变量的意思是,也许我们的make需要一些参数,所以定义成一个变量比较利于维护。

这两个例子的意思都是先进入“subdir”目录,然后执行make命令。

d)export CC OBJS BIN OBJS_DIR BIN_DIR我们把这个Makefile叫做“总控Makefile”,总控Makefile的变量可以传递到下级的Makefile中(如果你显示的声明),但是不会覆盖下层的Makefile中所定义的变量,除非指定了“-e”参数。

如果你要传递变量到下级Makefile中,那么你可以使用这样的声明:export <variable ...>。