Makefile两个实验

Makefile编程实验

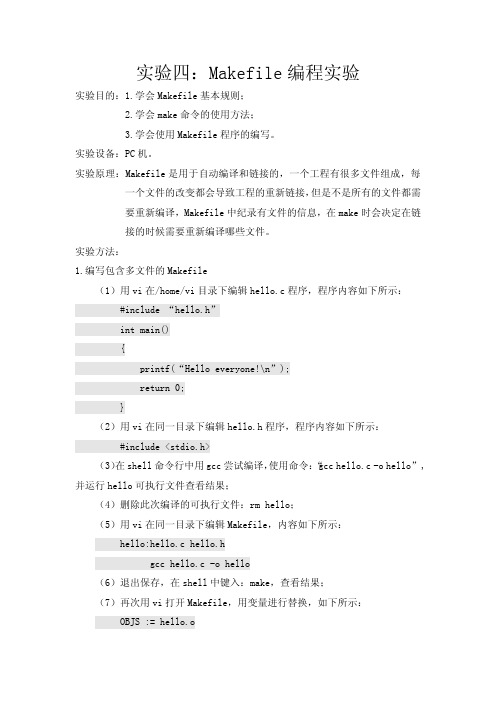

实验四:Makefile编程实验实验目的:1.学会Makefile基本规则;2.学会make命令的使用方法;3.学会使用Makefile程序的编写。

实验设备:PC机。

实验原理:Makefile是用于自动编译和链接的,一个工程有很多文件组成,每一个文件的改变都会导致工程的重新链接,但是不是所有的文件都需要重新编译,Makefile中纪录有文件的信息,在make时会决定在链接的时候需要重新编译哪些文件。

实验方法:1.编写包含多文件的Makefile(1)用vi在/home/vi目录下编辑hello.c程序,程序内容如下所示:#include“hello.h”int main(){printf(“Hello everyone!\n”);return0;}(2)用vi在同一目录下编辑hello.h程序,程序内容如下所示:#include<stdio.h>(3)在shell命令行中用gcc尝试编译,使用命令:“gcc hello.c-o hello”,并运行hello可执行文件查看结果;(4)删除此次编译的可执行文件:rm hello;(5)用vi在同一目录下编辑Makefile,内容如下所示:hello:hello.c hello.hgcc hello.c-o hello(6)退出保存,在shell中键入:make,查看结果;(7)再次用vi打开Makefile,用变量进行替换,如下所示:OBJS:=hello.oCC:=gcchello:$(OBJS)$(CC)$^-o$@(8)退出保存,在shell中键入make,查看结果;(9)用vi在同一目录下编辑makefile1,内容如下所示:hello:hello.ogcc hello.o-o hellohello.o:hello.c hello.hgcc-c hello.c-o hello.o(10)退出保存,在shell中键入:make-f makefile1,查看结果;(11)再次用vi编辑makefile1,内容如下所示:OBJS1:=hello.oOBJS2:=hello.c hello.hCC:=gcchello:$(OBJS1)$(CC)$^-o$@$(OBJS1):$(OBJS2)$(CC)-c$<-o$@在这里请注意区别“$^”和“$<”;(12)退出保存,在shell中键入:make-f makefile1,查看结果;2.使用autotools生成包含多文件的Makefile(1)在/home/vi目录下新建文件夹auto:#mkdir./auto(2)将/home/vi目录下的hello.c和hello.h文件复制到/home/vi/auto 目录下,然后进入到/home/vi/auto目录里面:#cp/home/vi/hello.*/home/vi/auto#cd/home/vi/auto(3)执行命令:#autoscan(4)使用vi编辑当前目录下的configure.scan文件为,主要是蓝色部分:#-*-Autoconf-*-#Process this file with autoconf to produce a configure script.AC_PREREQ(2.59)AC_INIT(hello, 1.0)AM_INIT_AUTOMAKE(hello,1.0)AC_CONFIG_SRCDIR([hello.h])AC_CONFIG_HEADER([config.h])#Checks for programs.AC_PROG_CC#Checks for libraries.#Checks for header files.#Checks for typedefs,structures,and compiler characteristics.#Checks for library functions.AC_OUTPUT(makefile)(5)保存退出,并重命名为configure.in;(6)执行命令:#aclocal(7)执行命令:#autoconf并用ls或ll命令查看是否生成了configure可执行文件;(8)执行命令:#autoheader(9)在当前目录下用vi创建makefile.am文件为:AUTOMAKE_OPTIONS=foreignbin_PROGRAMS=hellohello_SOURCES=hello.c hello.h(10)执行命令:#automake然后再执行下面的命令:#automake-a(11)执行命令:#./configure(12)执行命令:#make(13)执行命令:#./hello查看结果是否正确;(14)执行命令:#Make install(15)执行命令:#hello查看结果是否正确;(16)执行命令:#make dist(17)在当前目录下解压文件hello-1.0.tar.gz:#tar-zxvf hello-1.0.tar.gz(18)进入解压目录:#cd./hello-1.0(19)下面开始Linux下常见的安装软件步骤:#./configure(20)执行命令:#make(21)执行命令:#./hello注意:在正常安装时这一步可省略;(22)执行命令:#make install(23)执行命令:#hello查看结果是否正确。

c语言makefile编写实例

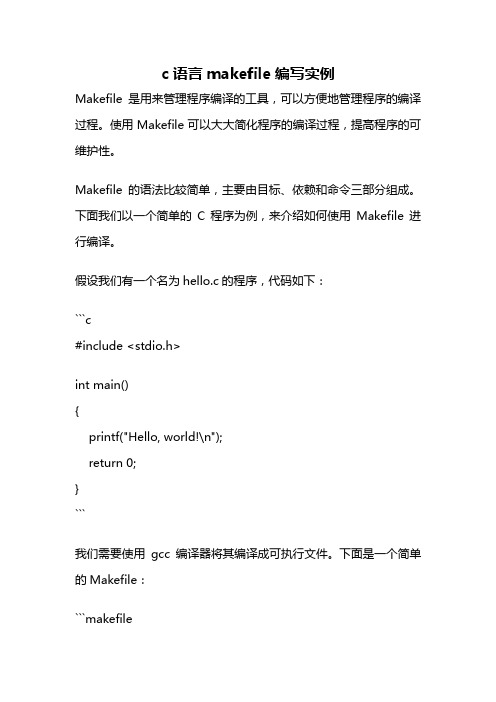

c语言makefile编写实例Makefile是用来管理程序编译的工具,可以方便地管理程序的编译过程。

使用Makefile可以大大简化程序的编译过程,提高程序的可维护性。

Makefile的语法比较简单,主要由目标、依赖和命令三部分组成。

下面我们以一个简单的C程序为例,来介绍如何使用Makefile进行编译。

假设我们有一个名为hello.c的程序,代码如下:```c#include <stdio.h>int main(){printf("Hello, world!\n");return 0;}```我们需要使用gcc编译器将其编译成可执行文件。

下面是一个简单的Makefile:```makefilehello: hello.cgcc -o hello hello.c```这个Makefile很简单,它定义了一个名为hello的目标,该目标依赖于hello.c文件,并使用gcc命令将其编译成可执行文件。

如果我们在终端中输入make命令,Makefile会自动执行编译过程:```$ makegcc -o hello hello.c```Makefile还可以定义多个目标,每个目标可以有多个依赖和多个命令。

下面是一个稍微复杂一些的Makefile:```makefileCC=gccCFLAGS=-Wall -gall: hello goodbyehello: hello.o$(CC) $(CFLAGS) -o hello hello.ogoodbye: goodbye.o$(CC) $(CFLAGS) -o goodbye goodbye.ohello.o: hello.c$(CC) $(CFLAGS) -c hello.cgoodbye.o: goodbye.c$(CC) $(CFLAGS) -c goodbye.cclean:rm -f *.o hello goodbye```这个Makefile定义了两个目标:all和clean。

make高效性实验注意事项

make高效性实验注意事项

Makefile 中使用条件控制可以做到处理的灵活性和高效性。

注意:条件语句只能用于控制 make 实际执行的 Makefile 文件部分,不能控制规则的 shell 命令执行的过程。

需要解决的问题:要根据判断,分条件执行语句。

条件语句的作用:条件语句可以根据一个变量的值来控制make 执行或者时忽略Makefile 的特定部分,条件语句可以是两个不同的变量或者是常量和变量之间的比较。

三个关键字“ifeq”、“else”、“endif”。

其中:“ifeq”表示条件语句的开始,并指定一个比较条件(相等)。

括号和关键字之间要使用空格分隔,两个参数之间要使用逗号分隔。

参数中的变量引用在进行变量值比较的时候被展开。

“ifeq”,后面的是条件满足的时候执行的,条件不满足忽略;“else”表示当条件不满足的时候执行的部分,不是所有的条件语句都要执行此部分;“endif”是判断语句结束标志,Makefile 中条件判断的结束都要有。

Linu 系统编程实验gccgdb的使用以及Makefile文件的编写

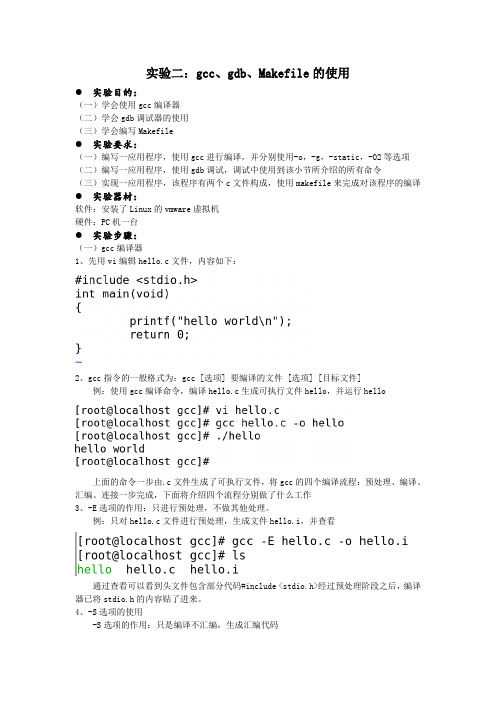

实验二:gcc、gdb、Makefile的使用●实验目的:(一)学会使用gcc编译器(二)学会gdb调试器的使用(三)学会编写Makefile●实验要求:(一)编写一应用程序,使用gcc进行编译,并分别使用-o,-g,-static,-O2等选项(二)编写一应用程序,使用gdb调试,调试中使用到该小节所介绍的所有命令(三)实现一应用程序,该程序有两个c文件构成,使用makefile来完成对该程序的编译●实验器材:软件:安装了Linux的vmware虚拟机硬件:PC机一台●实验步骤:(一)gcc编译器1、先用vi编辑hello.c文件,内容如下:2、gcc指令的一般格式为:gcc [选项] 要编译的文件 [选项] [目标文件]例:使用gcc编译命令,编译hello.c生成可执行文件hello,并运行hello上面的命令一步由.c文件生成了可执行文件,将gcc的四个编译流程:预处理、编译、汇编、连接一步完成,下面将介绍四个流程分别做了什么工作3、-E选项的作用:只进行预处理,不做其他处理。

例:只对hello.c文件进行预处理,生成文件hello.i,并查看通过查看可以看到头文件包含部分代码#include <stdio.h>经过预处理阶段之后,编译器已将stdio.h的内容贴了进来。

4、-S选项的使用-S选项的作用:只是编译不汇编,生成汇编代码例:将hello.i文件只进行编译而不进行汇编,生成汇编代码hello.s5、-c选项的使用-c选项的作用:只是编译不连接,生成目标文件.o例:将汇编代码hello.s只编译不链接成hello.o文件6、将编译好的hello.o链接库,生成可执行文件hello7、-static选项的使用-static选项的作用:链接静态库例:比较hello.c连接动态库生成的可执行文件hello和链接静态库生成的可执行文件hello1的大小可以看到静态链接库的可执行文件hello1比动态链接库的可执行文件hello要大的多,他们的执行效果是一样的8、-g选项的使用-g选项的作用:在可执行程序中包含标准调试信息例:将hello.c编译成包含标准调试信息的可执行文件hello2带有标准调试信息的可执行文件可以使用gdb调试器进行调试,以便找出逻辑错误9、-O2选项的使用-O2选项的作用:完成程序的优化工作例:将hello.c用O2优化选项编译成可执行文件hello3,和正常编译产生的可执行文件hello进行比较(二)gdb调试器1、先用vi编辑文件test.c用于gdb调试器调试,内容如下#include <stdio.h>int main(void){int sum(int sum);int i,result=0;sum(100);for(i=1;i<=100;i++){result+=i;}printf("The sum in main function is %d\n",result);return 0;}int sum(int num){int i,n=0;for(i=0;i<=num;i++){n+=i;}printf("The sum in sum function is %d\n",n);}2、将test.c文件编译成包含标准调试信息的文件test3、启动gdb进行调试可以看到gdb启动界面中显示了gdb的版本、自由软件等信息,然后进入了有”gdb”开头的命令行界面4、l(list)命令l命令用于查看文件可以看到每行代码面前都有对应的行号,这样方便我们设置断点。

linux实验二交叉编译和Makefile实验报告

[root @localhost hehui]# ./hmily

④使用交叉编译器编译并运行。

A.[root @localhost hehui]# arm-linux-gcc -o hmily ji_oushu.c

B.打开另外一个终端,输入minicom进入板子里去。

C.操作一下命令。

[root @localhost ~]# cd 2008550533

[root @localhost 2008550533]# mkdir hehui

[root @localhost ~]# cd hehui

[root @localhost hehui]# vi ji_oushu.c

/*输出50以内的奇数和偶数*/

④使用gcc编译,查看运行结果。

[root @localhost prime]# gcc prime.c -oprime_hehui

[root @localhost prime]# ./prime_hehui

⑤编写Makefile文件实现第④步功能,并使用make工具生成这个可执行文件。

[root @localhost prime]# rm -r prime_hehui

all:prime

prime:prime.o main.o

$(CC) $(CFLAGS) $^ -o $@

prime.o:prime.c

$(CC) $(CFLAGS) -c $< -o $@

main.o:main.c prime.h

$(CC) $(CFLAGS) -c $< -o $@

clean:

rm -fr prime_hehui *.o

clean: 37

实验二 Makefile实验

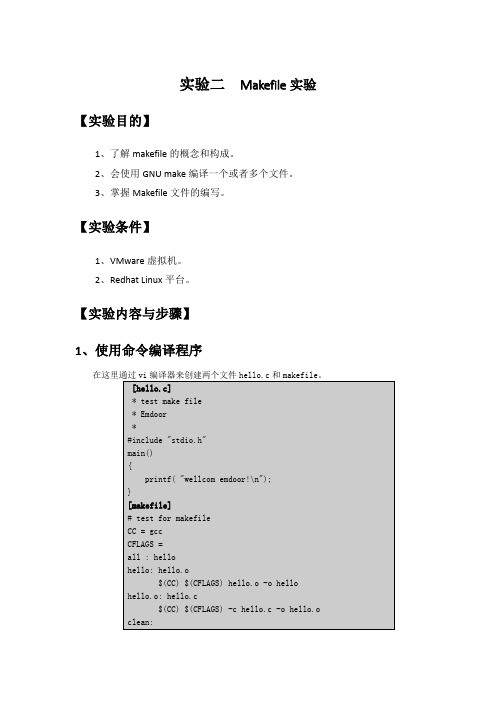

实验二M akefile实验【实验目的】1、了解makefile的概念和构成。

2、会使用GNU make编译一个或者多个文件。

3、掌握Makefile文件的编写。

【实验条件】1、VMware虚拟机。

2、Redhat Linux平台。

【实验内容与步骤】1、使用命令编译程序在这里通过vi编译器来创建两个文件hello.c和makefile。

[hello.c]* test make file* Emdoor*#include "stdio.h"main(){printf( "wellcom emdoor!\n");}[makefile]# test for makefileCC = gccCFLAGS =all : hellohello: hello.o$(CC) $(CFLAGS) hello.o -o hellohello.o: hello.c$(CC) $(CFLAGS) -c hello.c -o hello.o clean:在将上述Makefile文件与源文件hello.c保存到同一目录之后,就可以在命令行中输入“make”命令来编译整个项目了。

make在执行过程中,首先会查找到Makefile文件第一条规则中的目标,即上述文件中的all。

根据设定好的规则,该目标需要依赖于hello。

由于all并不是一个已经存在的文件,所以每次在make被调用的时候,显然都需要先检查hello。

继续往下不难发现,hello目标是依赖于hello.o。

当make处理到目标hello.o时,会先查看其对应的依赖对象,这个以来对象是hello.c,此时就会对hello.c进行编译,得到目标文件hello.o,然后是目标文件hello.o被连接,得到可执行文件hello。

先后执行如下命令:可以看到输出结果:在Makefile中,并不是所有的目标都对应于磁盘上的文件。

有的目标存在只是为了形成一条规则,从而完成特定的工作,并不生成新的目标文件,这样的目标称为伪目标。

python makefile 用法

python makefile 用法在使用Python编写程序时,我们通常需要编译和运行代码,这就需要用到makefile。

makefile是一种可以自动化地构建程序的工具,它可以根据代码修改的情况自动判断哪些文件需要重新编译,从而提高程序的编译效率。

使用makefile的基本步骤如下:1. 创建一个名为makefile的文件,通常放在程序的根目录下。

2. 在makefile中定义一些变量,如编译器、编译选项等。

3. 定义一些规则,如编译规则、目标规则等。

4. 运行make命令,根据makefile的规则进行编译和链接。

下面是一个简单的makefile示例:```# 定义编译器和编译选项CC=gccCFLAGS=-Wall -g# 定义编译规则%.o: %.c$(CC) $(CFLAGS) -c $< -o $@# 定义目标规则main: main.o sub.o$(CC) $(CFLAGS) main.o sub.o -o main# 清除中间文件clean:rm -f *.o main```在这个示例中,我们定义了两个变量CC和CFLAGS,分别表示编译器和编译选项。

接着定义了一个编译规则,表示将.c文件编译成.o文件的过程。

其中,$<表示依赖文件(即输入文件),$@表示目标文件(即输出文件)。

最后定义了一个目标规则,表示将main.o和sub.o链接成可执行文件main。

最后,我们定义了一个清除中间文件的规则,可以通过运行make clean来清除中间文件。

可以通过运行make命令来编译和链接程序。

例如,如果你有一个名为main.c和sub.c的源文件,并想将它们编译成可执行文件main,可以在终端中输入以下命令:```$ make main```这将根据makefile中定义的规则自动编译和链接程序,并生成可执行文件main。

总之,makefile是一个非常有用的编译工具,可以帮助我们自动化地构建程序,提高编译效率。

实验二 Makefile实验

6

Makefile主要预定义变量及隐含 规则

预定义变量及其含义 CC CCFLAGS …… GNU make 支持两种类型的隐含规则: 后缀规则(Suffix Rule) 模式规则(pattern rules)

亿道电子有限公司出品

亿道电子有限公司出品

4

Makefile的基本结构

目标 --- 需要由 make 工具创建的项目, 通常是目标文件和可执行文件 。 依赖 ---要创建的项目依赖于哪些文件 命令 ---创建每个项目时需要运行的命令 target : dependency ...

make编译一个或者多个文件

亿道电子有限公司出品

3

Makefile的规则

如果这个工程没有编译过,那么我们的所 有C文件都要编译并被链接。 如果这个工程的某几个C文件被修改,那 么我们只编译被修改的C文件,并链接目 标程序。 如果这个工程的头文件被改变了,那么我 们需要编译引用了这几个头文件的C文件, 并链接目标程序。

亿道电子有限公司出品

12

思考与习题

工程中多级目录中存在着多个makefile时, 编译的顺序如何? 如果要编译生成的文件能够在EELIOD实验 平台上面使用,应该怎么对makefile修改?

亿道电子有限公司出品

13

亿道电子有限公司出品

10

使用wildcard对多个.c文件编译

wildcard’函数的一个功能是找出目录中所 有的’.c’文件: $(wildcard *.c) SOURCES = $(wildcard *.c) 这行会产生一个所有以 '.c' 结尾的文件 的列表,然后存入变量 SOURCES 里。 当然你不需要一定要把结果存入一个变量。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验十四Makefile工程管理器14.1 编写包含多文件的Makefile【实验内容】编写一个包含多文件的Makefile。

【实验目的】通过对包含多文件的Makefile的编写,熟悉各种形式的Makefile,并且进一步加深对Makefile中用户自定义变量、自动变量及预定义变量的理解。

【实验平台】PC机、CentOS 5 操作系统、gcc等工具。

【实验步骤】1.用vi在同一目录下编辑两个简单的Hello程序,如下所示:#hello.c#include "hello.h"int main(){printf("Hello everyone!\n");}#hello.h#include <stdio.h>2.仍在同一目录下用vim编辑Makefile,不使用变量替换,用一个目标体实现(即直接将hello.c和hello.h编译成hello目标体)。

并用make验证所编写的Makefile是否正确。

3.将上述Makefile使用变量替换实现。

同样用make验证所编写的Makefile是否正确4.用编辑另一Makefile,取名为Makefile1,不使用变量替换,但用两个目标体实现(也就是首先将hello.c和hello.h编译为hello.o,再将hello.o编译为hello),再用make 的‘-f’选项验证这个Makefile1的正确性。

5.将上述Makefile1使用变量替换实现【详细步骤】1.用vi打开上述两个代码文件‘hello.c’和‘hello.h’2.在shell命令行中用gcc尝试编译,使用命令:‘gcc hello.c -o hello’,并运行hello可执行文件查看结果。

3.删除此次编译的可执行文件:rm –rf hello4.用vim编辑Makefile,如下所示:hello:hello.c hello.hgcc hello.c -o hello5.退出保存,在shell中键入:make查看结果6.再次用vim打开Makefile,用变量进行替换,如下所示:OBJS :=hello.oCC :=gcchello:$(OBJS)$(CC) $^ -o $@7.退出保存,在shell中键入:make查看结果8.用vim编辑Makefile1,如下所示:hello:hello.ogcc hello.o -o hellohello.o:hello.c hello.hgcc -c hello.c -o hello.o9.退出保存,在shell中键入:make –f Makefile1查看结果10.再次用vi编辑Makefile1,如下所示:OBJS1 :=hello.oOBJS2 :=hello.c hello.hCC :=gcchello:$(OBJS1)$(CC) $^ -o $@$(OBJS1):$(OBJS2)$(CC) -c $< -o $@在这里请注意区别‘$^’和‘$<’。

11.退出保存,在shell中键入:make –f Makefile1查看结果14.2嵌套Makefile实验【实验目的】1、读懂makefile文件,能根据makefile文件理清程序结构2、能编写简单makefile3、掌握嵌套执行makefile【实验环境】PC机、CentOS 5 操作系统,gcc等工具。

【实验步骤】我们要创建的目录结构如下:顶层Makefile1.创建顶层目录我们首先在用户目录下创建一个makefileTest的文件夹:#cd /opt#mkdir makefileTest#cd makefileTest创建好需要用到的文件夹#mkdir f1 f2 main obj include进入include文件夹创建一个共用头文件#cd include#vim myinclude.h输入如下内容:#include <stdio.h>保存退出返回顶层目录:#cd ..2.创建顶层Makefile文件#vim Makefile输入以下内容:CC = gccSUBDIRS = f1 \f2 \main \objOBJS = f1.o f2.o main.oBIN = myappOBJS_DIR = objBIN_DIR = binexport CC OBJS BIN OBJS_DIR BIN_DIRall : CHECK_DIR $(SUBDIRS)CHECK_DIR :mkdir -p $(BIN_DIR)$(SUBDIRS) : ECHOmake -C $@ECHO:@echo $(SUBDIRS)@echo begin compileCLEAN :@$(RM) $(OBJS_DIR)/*.o@rm -rf $(BIN_DIR)3.进入在f1目录下创建makefile #cd f1#vim f1.c输入如下测试代码:#include “../include/myinclude.h”void print1(){printf("Message from f1.c...\n");return;}保存退出。

#vim Makefile输入如下内容:../$(OBJS_DIR)/f1.o: f1.c$(CC) -c $^ -o $@保存退出。

进入f2目录#cd ../f2#vim f2.c输入如下测试代码:#include “../include/myinclude.h”void print2(){printf("Message from f2.c…\n");return;}保存退出。

#vim Makefile输入如下内容:../$(OBJS_DIR)/f2.o: f2.c$(CC) -c $^ -o $@保存退出。

进入main目录#cd ../main#vim main.c输入如下内容:#include <stdio.h>int main(){print1();print2();return 0;}保存退出。

#vim Makefile输入如下内容:../$(OBJS_DIR)/main.o: main.c$(CC) -c $^ -o $@保存退出。

进入obj目录#cd ../obj#vim Makefile输入如下内容:../$(BIN_DIR)/$(BIN) : $(OBJS)$(CC) -o $@ $^好了,到此准备工作已经完毕,然我们来测试一下写的makefile是否好用。

进入顶层Makefile所在目录,即makefileTest目录。

#make会出现如下信息:目录树结构如下:我们看到在bin目录下生成了我们的目标文件myapp,在obj目录下生成了.o的中间文件。

让我们运行下myapp看下结果吧。

#bin/myapp我们也可以用如下命令清除中间文件和目标文件,恢复make之前的状态:#make CLEAN我们可以看到已经变为make之前的目录状态了。

大功告成。

最后给大家解释一下顶层makefile中一些命令的的含义吧。

a)我们注意到有一句@echo $(SUBDIRS)@echo其实是一句显示命令通常,make会把其要执行的命令行在命令执行前输出到屏幕上。

当我们用“@”字符在命令行前,那么,这个命令将不被make显示出来,最具代表性的例子是,我们用这个功能来像屏幕显示一些信息。

如:@echo 正在编译XXX模块......当make执行时,会输出“正在编译XXX模块......”字串,但不会输出命令,如果没有“@”,那么,make将输出:echo 正在编译XXX模块......正在编译XXX模块......如果make执行时,带入make参数“-n”或“--just-print”,那么其只是显示命令,但不会执行命令,这个功能很有利于我们调试我们的Makefile,看看我们书写的命令是执行起来是什么样子的或是什么顺序的。

而make参数“-s”或“--slient”则是全面禁止命令的显示。

b)@(RM)并不是我们自己定义的变量,那它是从哪里来的呢?通常在清除文件的伪目标所定义的命令中“rm”使用选项“–f”(--force)来防止在缺少删除文件时出错并退出,使“make clean”过程失败。

也可以在“rm”之前加上“-”来防止“rm”错误退出,这种方式时 make 会提示错误信息但不会退出。

为了不看到这些讨厌的信息,需要使用上述的第一种方式。

另外 make存在一个内嵌隐含变量“RM”,它被定义为:“RM = rm –f”。

因此在书写“clean”规则的命令行时可以使用变量“$(RM)”来代替“rm”,这样可以免出现一些不必要的麻烦!这是我们推荐的用法。

c)make -C $@这是一句嵌套makefile的语法,在一些大的工程中,我们会把我们不同模块或是不同功能的源文件放在不同的目录中,我们可以在每个目录中都书写一个该目录的Makefile,这有利于让我们的Makefile变得更加地简洁,而不至于把所有的东西全部写在一个Makefile中,这样会很难维护我们的Makefile,这个技术对于我们模块编译和分段编译有着非常大的好处。

例如,我们有一个子目录叫subdir,这个目录下有个Makefile文件,来指明了这个目录下文件的编译规则。

那么我们总控的Makefile可以这样书写:subsystem:cd subdir && $(MAKE)其等价于:subsystem:$(MAKE) -C subdir定义$(MAKE)宏变量的意思是,也许我们的make需要一些参数,所以定义成一个变量比较利于维护。

这两个例子的意思都是先进入“subdir”目录,然后执行make命令。

d)export CC OBJS BIN OBJS_DIR BIN_DIR我们把这个Makefile叫做“总控Makefile”,总控Makefile的变量可以传递到下级的Makefile中(如果你显示的声明),但是不会覆盖下层的Makefile中所定义的变量,除非指定了“-e”参数。

如果你要传递变量到下级Makefile中,那么你可以使用这样的声明:export <variable ...>。