时序逻辑电路作业

(完整版)时序逻辑电路习题与答案

第12章时序逻辑电路自测题一、填空题1.时序逻辑电路按状态转换情况可分为时序电路和时序电路两大类。

2.按计数进制的不同,可将计数器分为、和N进制计数器等类型。

3.用来累计和寄存输入脉冲个数的电路称为。

4.时序逻辑电路在结构方面的特点是:由具有控制作用的电路和具记忆作用电路组成。

、5.、寄存器的作用是用于、、数码指令等信息。

6.按计数过程中数值的增减来分,可将计数器分为为、和三种。

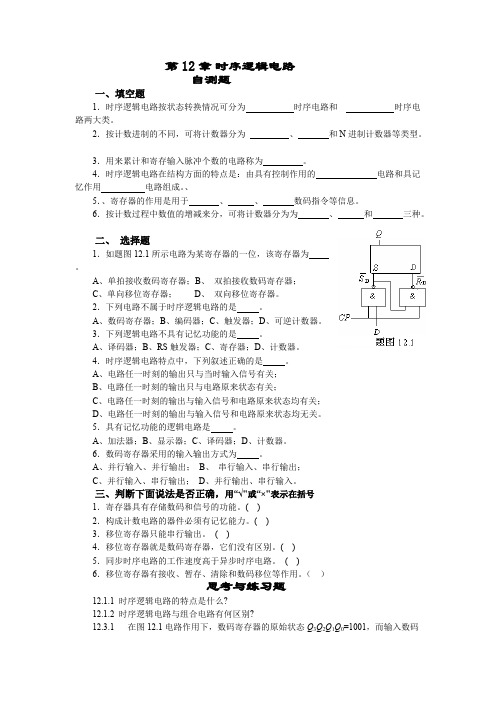

二、选择题1.如题图12.1所示电路为某寄存器的一位,该寄存器为。

A、单拍接收数码寄存器;B、双拍接收数码寄存器;C、单向移位寄存器;D、双向移位寄存器。

2.下列电路不属于时序逻辑电路的是。

A、数码寄存器;B、编码器;C、触发器;D、可逆计数器。

3.下列逻辑电路不具有记忆功能的是。

A、译码器;B、RS触发器;C、寄存器;D、计数器。

4.时序逻辑电路特点中,下列叙述正确的是。

A、电路任一时刻的输出只与当时输入信号有关;B、电路任一时刻的输出只与电路原来状态有关;C、电路任一时刻的输出与输入信号和电路原来状态均有关;D、电路任一时刻的输出与输入信号和电路原来状态均无关。

5.具有记忆功能的逻辑电路是。

A、加法器;B、显示器;C、译码器;D、计数器。

6.数码寄存器采用的输入输出方式为。

A、并行输入、并行输出;B、串行输入、串行输出;C、并行输入、串行输出;D、并行输出、串行输入。

三、判断下面说法是否正确,用“√"或“×"表示在括号1.寄存器具有存储数码和信号的功能。

( )2.构成计数电路的器件必须有记忆能力。

( )3.移位寄存器只能串行输出。

( )4.移位寄存器就是数码寄存器,它们没有区别。

( )5.同步时序电路的工作速度高于异步时序电路。

( )6.移位寄存器有接收、暂存、清除和数码移位等作用。

()思考与练习题12.1.1 时序逻辑电路的特点是什么?12.1.2 时序逻辑电路与组合电路有何区别?12.3.1 在图12.1电路作用下,数码寄存器的原始状态Q3Q2Q1Q0=1001,而输入数码D3D2D1D0=0110时,在CP的作用下,Q3Q2Q1Q0状态如何变化?12.3.2 题图12.2所示移位寄存器的初始状态为111,画出连续3个C P脉冲作用下Q2Q1Q0各端的波形和状态表。

(完整版)触发器时序逻辑电路习题答案

第4章 触发器4.3 若在图4.5电路中的CP 、S 、R 输入端,加入如图4.27所示波形的信号,试画出其Q 和Q 端波形,设初态Q =0。

SRCP图4.27 题4.3图解:图4.5电路为同步RS 触发器,分析作图如下:S RQ4.5 设图4.28中各触发器的初始状态皆为Q =0,画出在CP 脉冲连续作用下个各触发器输出端的波形图。

Q 11CPQ 3CPCPQ 2Q 6Q 4Q 5CP图4.28 题4.5图解:Q Q nn 111=+ Q Q n n 212=+ Q Q nn 313=+Q Q n n 414=+ Q Q n n 515=+ Q Q nn 616=+Q 1CP Q 2Q 3Q 4Q 5Q64.6 试写出 图4.29(a)中各触发器的次态函数(即Q 1 n+1 、 Q 2 n+1与现态和输入变量之间的函数式),并画出在图4.29(b )给定信号的作用下Q 1 、Q 2的波形。

假定各触发器的初始状态均为Q =0。

1A BCP>1D C1=1A BQ 1Q 2Q 2(a)BA(b)图4.29题4.6图解:由图可见:Q B A AB Q n n 111)(++=+ B A Q n ⊕=+12B A Q 2Q 14.7 图4.30(a )、(b )分别示出了触发器和逻辑门构成的脉冲分频电路,CP 脉冲如图4.30(c )所示,设各触发器的初始状态均为0。

(1)试画出图(a )中的Q 1、Q 2和F 的波形。

(2)试画出图(b )中的Q 3、Q 4和Y 的波形。

Y(b )(c )CPQ 1Q 2(a )图4.30 题4.7图解: (a )Q Q nn 211=+ QQ nn 112=+ Q F 1CP ⊕= R 2 = Q 1 低电平有效CPQ 1Q 2F(b )Q Q Q n n n 4313=+ Q Q Q n n n 4314=+ Q Q Y nn43=CP 3= CP 上降沿触发 CP 4= CP 下降沿触发CPQ 3Q 4Y4.8 电路如图4.31所示,设各触发器的初始状态均为0。

时序逻辑电路练习题讲解学习

时序逻辑电路练习题一、填空题1. 基本RS触发器,当R、S都接高电平时,该触发器具有____ ___功能。

2.D 触发器的特性方程为 ___ ;J-K 触发器的特性方程为______。

3.T触发器的特性方程为。

4.仅具有“置0”、“置1”功能的触发器叫。

5.时钟有效边沿到来时,输出状态和输入信号相同的触发器叫____ _____。

6. 若D触发器的D端连在Q端上,经100 个脉冲作用后,其次态为0,则现态应为。

7.JK触发器J与K相接作为一个输入时相当于触发器。

8. 触发器有个稳定状态,它可以记录位二进制码,存储8 位二进制信息需要个触发器。

9.时序电路的次态输出不仅与即时输入有关,而且还与有关。

10. 时序逻辑电路一般由和两部分组成的。

11. 计数器按内部各触发器的动作步调,可分为___ ___计数器和____ __计数器。

12. 按进位体制的不同,计数器可分为计数器和计数器两类;按计数过程中数字增减趋势的不同,计数器可分为计数器、计数器和计数器。

13.要构成五进制计数器,至少需要级触发器。

14.设集成十进制(默认为8421码)加法计数器的初态为Q4Q3Q2Q1=1001,则经过5个CP脉冲以后计数器的状态为。

15.将某时钟频率为32MHz的CP变为4MHz的CP,需要个二进制计数器。

16. 在各种寄存器中,存放N位二进制数码需要个触发器。

17. 有一个移位寄存器,高位在左,低位在右,欲将存放在该移位寄存器中的二进制数乘上十进制数4,则需将该移位寄存器中的数移位,需要个移位脉冲。

18.某单稳态触发器在无外触发信号时输出为0态,在外加触发信号时,输出跳变为1态,因此其稳态为态,暂稳态为态。

19.单稳态触发器有___ _个稳定状态,多谐振荡器有_ ___个稳定状态。

20.单稳态触发器在外加触发信号作用下能够由状态翻转到状态。

21.集成单稳态触发器的暂稳维持时间取决于。

22. 多谐振荡器的振荡周期为T=tw1+tw2,其中tw1为正脉冲宽度,tw2为负脉冲宽度,则占空比应为_______。

时序逻辑电路试题及答案

时序逻辑电路试题及答案一、单选题1.CP有效时,若JK触发器状态由1翻转为0,则此时JK输入端必定有A、J=0B、J=1C、K=0D、K=1【正确答案】:D2.主从RS触发器是在时钟脉冲CP的( ),根据输入信号改变状态。

A、低电平期间B、高电平期间C、上升沿时刻D、下降沿时刻【正确答案】:D3.仅具有置0和置1功能的触发器是A、RS触发器B、JK触发器C、D触发器D、T触发器【正确答案】:C4.关于JK触发器的错误表述是A、对于输入信号没有制约条件B、不允许JK同时为1C、允许JK同时为1D、允许JK同时为0【正确答案】:B5.D触发器当D=Q时,实现的逻辑功能是A、置0B、置1C、保持D、翻转【正确答案】:C6.JK触发器有( )触发信号输入端。

A、一个B、二个C、三个D、四个【正确答案】:B7.下列哪项表示基本RS触发器的符号A、B、C、D、【正确答案】:A8.D触发器在CP脉冲有效的情况下能实现的功能是A、置0和置1B、置1和保持C、置0和保持D、保持和翻转【正确答案】:A9.基本RS触发器是( )。

A、组合逻辑电路B、单稳态触发器C、双稳态触发器D、无稳态触发器10.双D集成触发器CD4013的时钟脉冲CP的引脚是A、14脚B、7脚C、3脚与11脚D、5脚与11脚【正确答案】:C11.与非型同步RS触发器,CP=1期间,( ),触发器维持原态。

A、R=0,S=0B、R=0,S=1C、R=1,S=0D、R=1,S=1【正确答案】:A12.主从JK触发器的初态为0,JK=01时,经过2021个触发脉冲后,其状态变化及输出状态为A、一直为0B、由0变为1,然后一直为1C、在01间翻转,最后为1D、在01间翻转,最后为013.对双JK集成触发器74LS112引脚功能叙述错误的是A、16脚是VccB、8脚是GNDC、1脚是CP1D、16脚是GND【正确答案】:D14.D触发器用作计数型触发器时,输入端D的正确接法是A、D=0B、D=1C、D=D=Q【正确答案】:C15.JK触发器中,当JK取值相同时,则Q等于A、J⊕QB、QC、1D、016.在RS触发器的逻辑符号中表示A、低电平时置1B、高电平时置1C、低电平时置0D、高电平时置0【正确答案】:C17.JK触发器,若J=,K= Q,则可实现的逻辑功能是A、置0B、置1C、保持D、翻转【正确答案】:D18.D触发器有( )触发信号输入端。

第9章时序逻辑电路习题解答

第九章习题参考答案9-1对应于图9-la 逻辑图,若输入波形如图9-54所示,试分别画出原态为0和原 态为1对应时刻得Q 和◎波形。

3D 八图9-54逆9-1图解得到的波形如题9-1解图所示。

9-2逻辑图如图9-55所示,试分析它们的逻辑功能,分别画出逻辑符号,列出逻辑 真值表,说明它们是什么类型的触发器。

解 对于(a ):由图可写出该触发器的输出与输入的逻辑关系式为:(9-1)原态为•丿京态为a) b)图9-55题9-2图下面按输入的不同组合,分析该触发器的逻辑功能。

(1) R n =1、S D =0若触发器原状态为0,由式(9-1)可得Q=0、Q =1 ;若触发器原状态为1,由式(9-1) 同样可得Q =0、Q = 1。

即不论触发器原状态如何,只要R D =1、S° =0,触发器将置成0态。

(2) R D=0、S°=l用同样分析可得知,无论触发器原状态是什么 > 新状态总为:Q =1・Q=0,即触发器被置成1态。

(3) R[)=Sj)=0按类似分析可知,触发器将保持原状态不变。

⑷= s° = 1两个“与非”门的输出端Q和Q全为0,这破坏了触发器的逻辑关系,在两个输入信号同时消失后,由于“或非”门延迟时间不可能完全相等,故不能确定触发器处于何种状态。

因此这种情况是不允许出现的。

逻辑真值表如表9-1所示,这是一类用或非门实现的基本RS触发器,逻辑符号如題9-2(a) 的逻辑符号所示。

对于(b):此图与(a)图相比,只是多加了一个时钟脉冲信号,所以该逻辑电路在CP =1时的功能与(a)相同,真值表与表9-1相同;而在CP=0时相当于(a)中(3)的情况,触发器保持原状态不变。

逻辑符号见趣9-2 (b)逻辑符号。

这是一类同步RS触发器。

Q1000]表9」題9・2 (a)真值表00不变1 1 不定题9・2 (a)的逻辑符号9-3同步RS 触发器的原状态为1,R 、S 和CP 端的输入波形如图9-56所示,试画出 对应的Q 和。

数字电子技术时序逻辑电路习题

5、画逻辑电路图

T1 = Q1 + XQ0 T0 = XQ0 + XQ0 Z = XQ1Q0

第43页/共55页

6、检查自启动

全功能状态转换表

现 入 现 态 次 态 现驱动入 现输出

Xn Q1n Q0nQ1n+1Q0n+1 T1 T0

Zn

1/0

0/0 0 0 0 0 1 0 1

0

现入 现态 次 态

X Q1 Q0 Q1 Q0 0 0 00 1 0 0 11 0 0 1 00 0

1 0 00 1 1 0 11 0 1 1 01 1 1 110 0

现驱动入 现输出

D1 D0 01 10 00

Z1 Z2

00 00 10

01 10 11 00

00 00 00 01

D1 = Q1Q0 + Q1Q0X

标题区

节目录

第14页/共55页

X/Z

S0 1/0

S1

1/1

0/0

S2

10101…

题6.2(1)的状态转移图

③ 状态间的转换关系

标题区

节目录

第15页/共55页

X/Z

0/0 S0 1/0

S1 1/0

1/1

11…

0/0

0/0

100…

S2

题6.2(1) 的原始状态转移图

标题区

节目录

第16页/共55页

(2) 解:① 输入变量为X、输出变量为Z;

S1 1/0

11…

0/0

1/1

0/0

100…

S2

题6.2(2) 的原始状态转移图

标题区

节目录

第19页/共55页

第6章 时序逻辑电路-习题答案

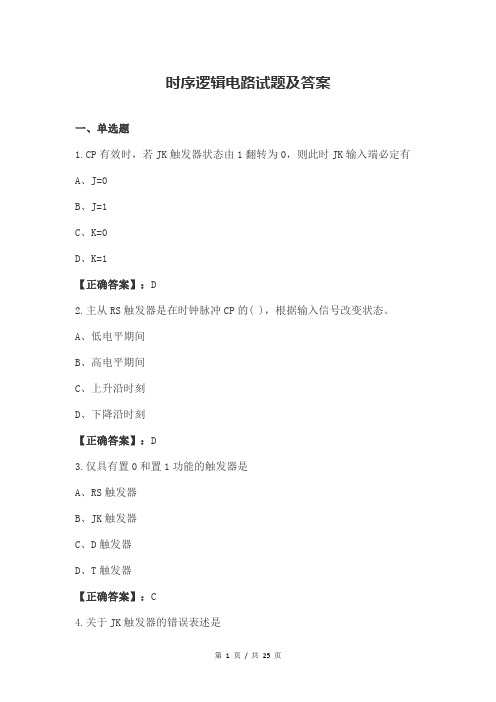

第六章 时序逻辑电路6-1 分析题图6-1所示的同步时序电路,画出状态图。

题图6-1解: 11221211n n n n J K Q T Q Z Q Q ====,,,,11111111212n n n n nn n nQ J Q K Q Q Q Q Q Q +=+=+=+122212n n n n Q T Q Q Q +=⊕=⊕,状态表入答案表6-1所示,状态图如图答案图6-1所示。

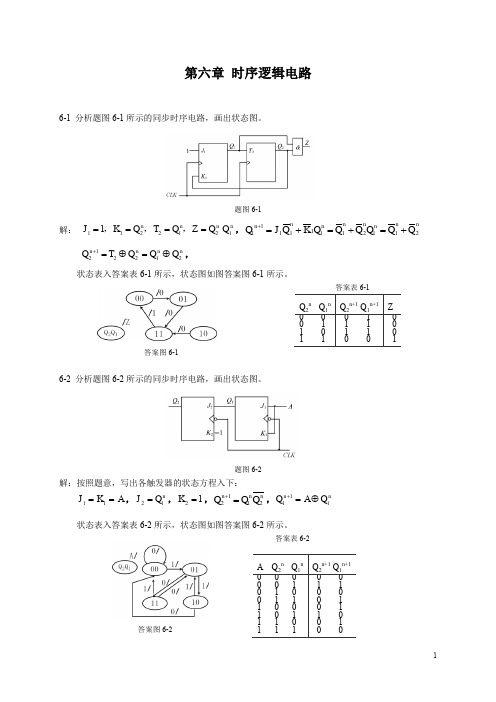

答案表6-1答案图6-16-2 分析题图6-2所示的同步时序电路,画出状态图。

题图6-2 解:按照题意,写出各触发器的状态方程入下:11J K A ==,21n J Q =,21K =,1212n n nQ Q Q +=,111n n Q A Q +=⊕状态表入答案表6-2所示,状态图如图答案图6-2所示。

答案表6-2答案图6-2Q 2n Q 1n Q 2n+1 Q 1n+1 Z0 0 0 1 1 0 1 1 0 1 1 1 1 1 0 0 0 0 0 1A Q 2n Q 1n Q 2n+1 Q 1n+1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 0 1 1 0 0 0 1 0 1 1 0 0 1 0 0CLK D 1D 2D 3Q 3Q 2Q 1Q 2Q 3Q 1Q 1Q 2Q 3&6-3分析题图6-3所示的同步时序电路,画出状态图。

题图6-3解:按照题意,写出各触发器的状态方程入下:1112213232131n n n nn J K T J K Q Q T J Q Q K Q ========1,,, 133********n n n n n n n nQ J Q K Q Q Q Q Q Q +=+=+ 1222132n n n n nQ T Q Q Q Q +=⊕=⊕ 1111111n n n n Q T Q Q Q +=⊕=⊕=答案表6-3答案图6-36-4 在题图6-4所示的电路中,已知寄存器的初始状态Q 1Q 2Q 3=111。

时序逻辑电路练习题

一、填空题1. 基本RS触发器,当R、S都接高电平时,该触发器具有____ ___功能。

2.D 触发器的特性方程为___ ;J-K 触发器的特性方程为______。

3.T触发器的特性方程为。

4.仅具有“置0”、“置1”功能的触发器叫。

5.时钟有效边沿到来时,输出状态和输入信号相同的触发器叫____ _____。

6. 若D触发器的D端连在Q端上,经100 个脉冲作用后,其次态为0,则现态应为。

7.JK触发器J与K相接作为一个输入时相当于触发器。

8. 触发器有个稳定状态,它可以记录位二进制码,存储8 位二进制信息需要个触发器。

9.时序电路的次态输出不仅与即时输入有关,而且还与有关。

10. 时序逻辑电路一般由和两部分组成的。

11. 计数器按内部各触发器的动作步调,可分为___ ____计数器和____ ___计数器。

12. 按进位体制的不同,计数器可分为计数器和计数器两类;按计数过程中数字增减趋势的不同,计数器可分为计数器、计数器和计数器。

13.要构成五进制计数器,至少需要级触发器。

14.设集成十进制(默认为8421码)加法计数器的初态为Q4Q3Q2Q1=1001,则经过5个CP脉冲以后计数器的状态为。

15.欲将某时钟频率为32MHz的CP变为16MHz的CP,需要二进制计数器个。

16. 在各种寄存器中,存放N位二进制数码需要个触发器。

17. 有一个移位寄存器,高位在左,低位在右,欲将存放在该移位寄存器中的二进制数乘上十进制数4,则需将该移位寄存器中的数移位,需要个移位脉冲。

18.某单稳态触发器在无外触发信号时输出为0态,在外加触发信号时,输出跳变为1态,因此其稳态为态,暂稳态为态。

19.单稳态触发器有___ _个稳定状态,多谐振荡器有_ ___个稳定状态。

20.单稳态触发器在外加触发信号作用下能够由状态翻转到状态。

21.集成单稳态触发器的暂稳维持时间取决于。

22. 多谐振荡器的振荡周期为T=tw1+tw2,其中tw1为正脉冲宽度,tw2为负脉冲宽度,则占空比应为_______。