VHDL自动售邮票机的代码

基于VHDL语言自动售货机设计实验报告-绝对原创

自动售货机设计实验报告一设计题目:g) 自动售货机设计FPGA模块模拟自动售货机的工作过程,要求如下(1)售货机有两个进币孔,可以输入硬币和纸币,售货机有两个进币孔,一个是输入硬币,一个是输入纸币,硬币的识别范围是5角和1 元的硬币,纸币的识别范围是1 元、5 元,10 元,20元,50元,100元。

乘客可以连续多次投入钱币。

(2)顾客可以选择的商品种类有16种,价格分别为1-16元,顾客可以通过输入商品的编号来实现商品的选择。

即有一个小键盘(0-9按键)来完成,比如输入15时要先输入1,再输入5。

(3)顾客选择完商品后,可以选择需要的数量。

然后可以继续选择商品及其数量,每次可以选择最多三个商品。

然后显示出所需金额。

顾客此时可以投币,并且显示已经投币的总币值。

当投币值达到或超过所需币值后,售货机出货,并扣除所需金额,并找出多余金额。

在投币期间,顾客可以按取消键取消本次操作,钱币自动退出。

二程序代码:三程序实现功能:FPGA模块模拟自动售货机:(1)售货机有两个进币孔,分别输入硬币和纸币,硬币的识别范围是5角和1 元的硬币,纸币的识别范围是1 元、5 元,10 元,20元,50元,100元。

乘客可以连续多次投入钱币。

(2)顾客可以选择的商品种类有16种,价格分别为1-16元,顾客可以通过输入商品的编号来实现商品的选择。

(3)顾客选择完商品后,可以选择需要的数量。

然后可以继续选择商品及其数量,每次最多选择最种商品,每种商品最多购买三个。

然后显示出所需金额。

顾客此时可以投币,并且显示已经投币的总币值。

当投币值达到或超过所需币值后,售货机出货,并扣除所需金额,并找出多余金额。

在投币期间,顾客可以按取消键取消本次操作,钱币自动退出。

四程序功能模块分析:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;实体说明:entity sellor isport ( clk:in std_logic; --系统时钟sel,cancel,reset: in std_logic; --选择、取消、开始(用于进入初始状态)变量定义:coin: in std_logic_vector(1 downto 0); --5角硬币、1元硬币crash:in std_logic_vector(5 downto 0); --100元、50元、20元、10元、5元、一元纸币item: in std_logic_vector(3 downto 0); --16种商品quantity:in std_logic_vector(1 downto 0); --商品数量(一次最多购买3件)change_out :out std_logic_vector(10 downto 0); --找零item_out :out std_logic_vector(3 downto 0); --是否购买了商品(1表示有商品出来、0表示没有商品出来)change :out std_logic ); --是否有找零end sellor;结构体说明:architecture behave of sellor issignal price:std_logic_vector(7 downto 0);signal counter: std_logic_vector(10 downto 0); --币数计数器signal total_price:std_logic_vector(10 downto 0); --控制系统的时钟信号type state_type is (initial_state,item1_state,quantity_state,money_state,sell_state,change_state);signal state:state_type;signal temp:std_logic_vector(1 downto 0);signal quan:std_logic_vector(3 downto 0);begincom:process(reset,sel,clk)beginif (clk'event and clk='1')thenif reset='1' then state<=initial_state;temp<="00";quan<="0000";end if;case state iswhen initial_state=>item_out<="0000"; --出票口关闭change_out<="00000000000"; --找零口关闭total_price<="00000000000"; --票价总额记录清零counter<="00000000000";--投入钱币总额记录清零change<='0';state<=item1_state; 设定initial_state选择物品程序:when item1_state=>if temp<"11" thenelse state<=money_state;end if;when quantity_state=>if(cancel='1')then --按下“取消”按钮state<=initial_state;else 取消操作程序if quantity="00" thenitem_out<="0000";change<='0';change_out<="00000000000";state<=initial_state;else 当选择0个商品total_price<=total_price+price*quantity;temp<=temp+1;quan<=quan+quantity;if (sel='1') then state<=item1_state;elsestate<=money_state;end if;end if;end if;货币识别:when money_state=>if(cancel='1')then --按下“取消”按钮state<=initial_state;end if;case crash is --纸币识别end case;case coin is --硬币识别end case;if counter>=total_price thenstate<=sell_state;--系统进入出票状态end if;购物操作程序:when sell_state =>if(cancel='1')thenitem_out<="0000";change<='1';change_out<=counter; --按下“取消”按钮state<=initial_state;elseif counter>=total_price thenitem_out<=quan; --判断是否还有找零state<=change_state; --系统进入找零状态elseitem_out<="0000";state<=initial_state;end if;end if;when change_state=>if(cancel='1')thenitem_out<="0000";change<='1';change_out<=counter; --按下“取消”按钮state<=initial_state;elseif counter>total_price thenchange<='1';change_out<=counter-total_price;item_out<=quan;elsechange<='0';change_out<="00000000000";state<=initial_state;end if;end if;end case;end if;end process;end behave;五、仿真波形六、个人总结与感想:良好的沟通与分工是十分重要的,这对程序的实现和质量具有至关重要的作用。

基于VHDL的自动售货机设计50329

北华大学电子系统综合实习报告学院 : 电气信息工程学院专业班级 : 通信工程姓名 : 闫梦迪学号 :指导老师 : 董胜实习时间 : 2015.11.30 — 12.11目录1.实习题目……………………………………………………………P32.实习目的……………………………………………………………P33.实习技术要求………………………………………………………P34.实现过程……………………………………………………………P35.功能及代码…………………………………………………………P56.仿真及硬件测试……………………………………………………P97.实习心得…………………………………………………………P128. 教师评语…………………………………………………………P14一.实习题目自动售货机设计二.实习目的通过本课题的研究,可以掌握电子控制系统的基本原理与其实现,通过对各个模块的编程及其仿真,对QuartusII软件的使用有所了解。

每个波形模块的VHDL实现加深了硬件描述语言的学习。

最终的顶层文件的调试,更是体现了综合知识的运用。

三.实习技术要求本设计要实现自动售货机的基本功能,如货物信息存储、商品选择、进程控制、硬币处理、余额计算、显示等功能。

利用软件QuartusII 平台,采用VHDL硬件描述语言编程的设计方法设计系统核心电路的硬件程序,与一般的软件开发不同,VHDL编程更需要熟悉一些底层的硬件知识,特别是数字逻辑电路的设计,因此VHDL编程的方法、思路都要更多的与硬件电路联系起来。

完成系统各个功能模块的硬件程序设计后,在软件平台上进行编译和电路仿真,最后生成的目标文件下载到实验台内的FPGA芯片以实现该系统,并在实验台上对设计进行验证。

四.实现过程1)、根据设计要求实现过程分两部分:a、面向客户端模块设计基于Quartus2软件环境下,应用VHEDL语言进行程序设计。

以clk输入端口进行商品选择,coin1输入端口做钱数输入,Finish输入端口做确认,进而完成商品购买。

基于VHDL的地铁自动售票机系统设计

毕业设计说明书(论文)作者: 学号:系:专业:题目: 基于VHDL的地铁自动售票机系统设计指导者:(姓名) (专业技术职务)评阅者:(姓名) (专业技术职务)2014 年 5 月毕业设计(论文)评语学生姓名:班级、学号:题目:综合成绩:毕业设计(论文)评语毕业设计说明书(论文)中文摘要毕业设计说明书(论文)外文摘要本科毕业设计说明书(论文)第Ⅰ页共Ⅰ页目次1 引言 (1)1.1 研究意义 (1)1.2 研究背景 (1)1.3 研究任务 (2)1.4 研究内容 (2)2 理论基础 (3)2.1 FPGA (3)2.2 VHDL语言 (4)2.3 QuartusⅡ软件 (6)3 课题设计 (9)3.1 设计要求 (9)3.2 系统分析与设计方案 (9)4 程序仿真 (16)4.1 自动售票机主控模块的波形仿真 (16)4.2 车票选择模块的波形仿真 (17)4.3 纸、硬币处理模块的波形仿真 (18)4.4 自动找零、出票模块的波形仿真 (19)4.5 整个售票机系统的波形仿真图 (20)5硬件验证 (22)5.1 上箱过程 (22)5.2 上箱结果 (23)结论 (25)致谢 (26)参考文献 (27)附录 (28)1 引言自动售票机主要的控制模块可以用多种语言设计完成。

但这些语言有较大的差异,不利于后期的修改和使用者之间的交流。

而VHDL语言是一种功能强大、标准化的硬件描述语言。

用VHDL语言设计程序时可以先分块编写再合并,所以能够编写出多层次的程序,与此同时,VHDL语言编写的程序避免了其他语言只能在各自环境中使用的缺陷。

本章主要讨论了地铁的起源、发展,以及随着社会的发展,为了简化购票流程,从而设计出了自动售票机来代替人工售票等。

1.1 研究意义近年来,国民经济快速发展,城市的各项设施也越来越好,进而人们对交通的要求也不断增加。

因此,安全又快捷的地铁就出现了。

地铁的速度较快,且在行驶过程的载客数较多,这是公交所不具备的,而且它的出现增加了乘客的选择,也可以很好的缓解交通拥挤的情况。

基于VHDL语言的地铁自动售票系统设计与实现

摘要本文主要介绍了利用VHDL设计语言和Altera公司的MAX+PLUS II软件开发平台, 来设计实现地铁自动售票系统的核心控制部分的功能:站点选择,票数选择,投币处理,余额计算,自动出票等功能。

在本设计中采用了有限状态机的设计方法,将整个售票系统的控制部分化分为五个状态: 选站状态,选票状态,投币状态,出票状态和余额找零状态。

最后通过对程序的调试以及相应部分功能的仿真,验证了整个系统的原理和本设计方案的正确性。

由于采用了有限状态机的设计方法,使得本系统运行可靠性高,非法状态易控制。

关键词: FPGA,CPLD, VHDL语言,MAX+PLUS II 软件,有限状态机, ,地铁自动售票系统目录第一章绪论 (1)1.1 电子器件的发展和现状 (1)1.2 设计方法的发展 (3)1.3 层次化的设计与VHDL的应用 (5)1.4 本课题的提出与意义 (8)1.5 本课题研究内容 (8)第二章 VHDL语言介绍 (10)2.1什么是VHDL (10)2.2 VHDL语言的特点 (10)2.3 VHDL的设计流程 (11)2.4 VHDL程序的基本结构 (13)第三章 MAX+PLUS II软件介绍 (14)3.1 MAX+PLUS II简介 (14)3.2Max+PlusⅡ开发系统的特点 (15)3.3 Max+PlusⅡ功能简介 (16)3.4 Max+plusⅡ设计过程 (20)第四章地铁售票系统的设计与实现 (24)4.1 课题要求 (24)4.2设计分析 (24)4.3状态机设计 (26)第五章结束语 (33)附录 (34)参考文献 (41)致谢 (42)第一章绪论1.1 电子器件的发展和现状电子技术的发展总是同电子器件的发展密切相关的,由于电子器件的不断更新换代,电子技术得到了飞速发展,当今信息技术被广泛应用在国民经济的方方面面。

多媒体技术的普及、高速宽带网络的建设、数字电视的出现以及与我们日常生活息息相关的各种家用电器,都离不开微处理器、存储器和一些采用行业标准的专用芯片。

自动售货机VHDL程序与仿真

自动售货机VHDL程序与仿真(1)自动售货机VHDL程序如下:--文件名:pl_auto1.vhd。

--功能:货物信息存储,进程控制,硬币处理,余额计算,显示等功能。

--说明:显示的钱数coin的以5角为单位。

--最后修改日期:2004.3.23。

library ieee;use ieee.std_logic_arith.all;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity PL_auto1 isport ( clk:in std_logic; --系统时钟set,get,sel,finish: in std_logic; --设定、买、选择、完成信号coin0,coin1: in std_logic; --5角硬币、1元硬币price,quantity :in std_logic_vector(3 downto 0); --价格、数量数据item0 , act:out std_logic_vector(3 downto 0); --显示、开关信号y0,y1 :out std_logic_vector(6 downto 0); --钱数、商品数量显示数据act10,act5 :out std_logic); --1元硬币、5角硬币end PL_auto1;architecture behav of PL_auto1 istype ram_type is array(3 downto 0)of std_logic_vector(7 downto 0);signal ram :ram_type; --定义RAMsignal item: std_logic_vector(1 downto 0); --商品种类signal coin: std_logic_vector(3 downto 0); --币数计数器signal pri,qua:std_logic_vector(3 downto 0); --商品单价、数量signal clk1: std_logic; --控制系统的时钟信号begincom:process(set,clk1)variable quan:std_logic_vector(3 downto 0);beginif set='1' then ram(conv_integer(item))<=price & quantity;act<="0000";--把商品的单价、数量置入到RAM elsif clk1'event and clk1='1' then act5<='0'; act10<='0';if coin0='1' thenif coin<"1001"then coin<=coin+1; --投入5角硬币,coin自加1else coin<="0000";end if;elsif coin1='1' thenif coin<"1001"then coin<=coin+2; --投入1元硬币,coin自加2else coin<="0000";end if;elsif sel='1' then item<=item+1; --对商品进行循环选择elsif get='1' then --对商品进行购买if qua>"0000" and coin>=pri then coin<=coin-pri;quan:=quan-1;ram(conv_integer(item))<=pri & quan;if item="00" then act<="1000"; --购买时,自动售货机对4种商品的操作elsif item="01" then act<="0100";elsif item="10" then act<="0010";elsif item="11" then act<="0001";end if;end if;elsif finish='1' then --结束交易,退币(找币)if coin>"0001" then act10<='1';coin<=coin-2; --此IF语句完成找币操作elsif coin>"0000" then act5<='1'; coin<=coin-1;else act5<='0'; act10<='0';end if;elsif get='0' then act<="0000";for i in 4 to 7 looppri(i-4)<=ram (conv_integer(item))(i); --商品单价的读取end loop;for i in 0 to 3 loopquan(i):=ram(conv_integer(item))(i); --商品数量的读取end loop;end if;end if;qua<=quan;end process com;m32:process(clk) --此进程完成对32Mhz的脉冲分频variable q: std_logic_vector( 24 downto 0);beginif clk'event and clk='1' then q:=q+1;end if;if q="111111111111111111111111" then clk1<='1';else clk1<='0';end if;end process m32;code0:process(item) --商品指示灯译码begincase item iswhen "00"=>item0<="0111";when "01"=>item0<="1011";when "10"=>item0<="1101";when others=>item0<="1110";end case;end process;code1: process (coin) --钱数的BCD到七段码的译码begincase coin iswhen "0000"=>y0<="0000001";when "0001"=>y0<="1001111";when "0010"=>y0<="0010010";when "0011"=>y0<="0000110";when "0100"=>y0<="1001100";when "0101"=>y0<="0100100";when "0110"=>y0<="0100000";when "0111"=>y0<="0001111";when "1000"=>y0<="0000000";when "1001"=>y0<="0000100";when others=>y0<="1111111";end case;end process;code2: process (qua) --单价的BCD到七段码的译码begincase qua iswhen "0000"=>y1<="0000001";when "0001"=>y1<="1001111";when "0010"=>y1<="0010010";when "0011"=>y1<="0000110";when "0100"=>y1<="1001100";when "0101"=>y1<="0100100";when "0110"=>y1<="0100000";when "0111"=>y1<="0001111";when "1000"=>y1<="0000000";when "1001"=>y1<="0000100";when others=>y1<="1111111";end case;end process;end behav;(2)程序仿真图8.21.2 系统仿真全图图8.21.3 系统仿真图-预置部分图21.4 系统仿真图-商品种类选择部分图8.21.5 系统仿真图-投币部分图8.21.6 系统仿真图-购买、找币结束交易部分。

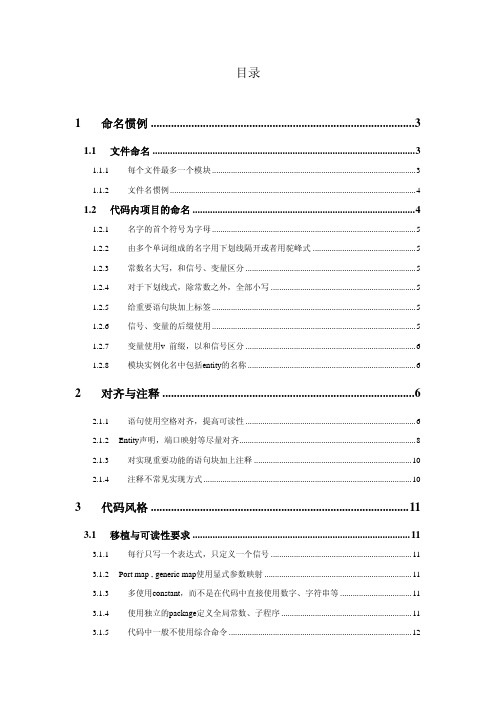

VHDL代码规范

3

3.1

代码风格 .........................................................................................11

移植与可读性要求 ....................................................................................... 11

3.1.1 3.1.2 3.1.3 3.1.4 3.1.5

3.1.6 3.1.7 3.1.8 3.1.9

常数之间有确定的关系时,使用关系定义 ...............................................................12 定义地址时,使用基址+偏移方式 .............................................................................13 常数可能变动的情况下使用generic map方式传递,而不是在模块中定义 ...............13 表达式使用括号表示优先级 .......................................................................................13

3.2

3.2.1 3.2.2 3.2.3 3.2.4 3.2.5 3.2.6 3.2.7 3.2.8 3.2.9

语句使用 .......................................................................................................13

自动售货机控制模块VHDL程序设计及FPGA实现

自动售货机控制模块VHDL程序设计及FPGA实现 近年来,随着集成电路技术的迅猛发展,特别是可编程逻辑器件的高速发展, EDA(Electronic Design Automation,电子设计自动化)技术成为电子设计工程师的新宠。

EDA技术以计算机为工具完成数字系统的逻辑综合、布局布线和设计仿真等工作。

电路设计者只需要完成对系统功能的描述,就可以由计算机软件进行系统处理,最后得到设计结果,并且修改设计方案如同修改软件一样方便。

利用EDA工具可以极大地提高设计效率。

利用硬件描述语言编程来表示逻辑器件及系统硬件的功能和行为,是EDA设计方法的一个重要特征。

VHDL(Very High Speed Integrated Circuit Hardware Description Language,超高速集成电路硬件描述语言)是硬件描述语言的一种,对系统硬件的描述功能很强而语法又比较简单。

VHDL具有强大的行为描述能力,设计者可以不懂硬件的结构,只需集中精力进行电子系统的设计和性能优化;具有方便的逻辑仿真与调试功能,在设计早期就能查验系统的功能,方便地比较各种方案的可行性及其优劣。

目前,VHDL作为IEEE的工业标准硬件描述语言,得到众多EDA公司的支持,在电子工程领域已经成为事实上通用硬件描述语言。

本文采用VHDL作为工具描述了自动售货机控制模块的逻辑控制电路,并在FPGA上实现。

该自动售货机能够根据投入硬币额度,按预定的要求在投入硬币大于规定值时送出饮料并找零。

设计方案 本文所设计的简易自动售货机可销售矿泉水,假设每瓶1.5元。

设两个投币孔,分别接收1元和5角两种硬币,两个输出口,分别输出购买的商品和找零。

假设每次只能投入一枚1元或5角硬币,投入1元5角硬币后机器自动给出一瓶矿泉水;投入2元硬币后,在给出一瓶矿泉水的同时找回一枚5角的硬币。

另外设置一复位按钮,当复位按钮按下时,自动售货机回到初始状态。

自动售邮票机的设计

自动售邮票机的设计一、摘要:通过参考文献资料仔细分析自动售货机的原理本文详细的介绍了(Very High Speed Integrated Circuit Hardware Description Language)语言的一些特点及语法结构;介绍了自动售货机系统的基本原理、系统组成和主要功能;并分析讨论了用VHDL语言开发自动售货机系统的设计流程。

本设计利用Altera公司的开发软件Quartus II平台,采用VHDL硬件描述语言编程的设计方法设计系统核心电路的硬件程序,在Quartus II软件平台上进行编译和电路仿真,最后生成的目标文件下载到实验台内的FPGA芯片以实现该系统,并在实验台上对设计进行了验证。

最终完成的自动售货机系统具有投币处理、商品选择、购货撤销、异常退币、计算存货等主要功能,整个系统的开发体现了在Quartus II软件平台上用VHDL 设计数字控制系统的实用性。

二、综述电子技术的发展,特别是专用集成电路(ASIC)设计技术的日趋进步和完善,推动力数字系统设计的迅猛发展。

电子设计自动化(EDA)工具给电子设计带来了巨大的变革,尤其是硬件描述语言的出现和发展,解决了传统用电路原理设计系统工程时的诸多不便,成为电子电路设计人员的最得力助手。

学习VHDL 已日益成为我国高等学校学生和工程技术人员的迫切需要。

本设计是利用VHDL,用模块合成的方式来完成的。

根据自动售票机的功能以及顾客的各种买卖行为,将其分为几大模块来处理。

目前最通用的硬件描述语言有VHDL与Verilog两种。

1982年美国国防部的一个分支专案要求所有的数字电路必须用VHDL语言设计。

1983年的IBH及TI等公司在此专案规定下,开始开发VHDL。

随后IEEE1076号标准。

后来将一种可配合集成工具的VHDL程序包,特别命名为IEEE1076.3,并成为1076号IEEE标准的一部分。

最近,新标准包IEEE1076.4被开发出来,成为建立ASIC 及FPGA的模型函数库。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

自动售邮票机代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity xrg4 is

port(clk,clk1:in bit;

coin1,coin5,coin10:in std_logic; --投入1、5、10角硬币

reset,reset1:in std_logic; --清零信号,1有效

six,eight:in std_logic; --6,8角的邮票

light:out std_logic; --购买成功指示灯

retlight:out std_logic_vector(3 downto 0) );--找回的硬币

end entity xrg4;

architecture xxrr of xrg4 is

type state is (s0,s1,s2);--状态机

signal n_state:state;--次态

signal c_state:state;--现态

signal touru:std_logic_vector(3 downto 0); --投入硬币面值

signal tincoint:std_logic_vector(4 downto 0);--计算出硬币总值(进程中)signal stamp:std_logic_vector(3 downto 0); --邮票面值

signal ret:std_logic_vector(3 downto 0); --找零值

signal zong:std_logic_vector(4 downto 0); --状态机硬币总值

begin

p1:process(clk1) --次态给现态

begin

if reset1='1'then c_state<=s2;

elsif clk1'event and clk1='1'then

c_state<=n_state;

end if;

end process p1;

p2:process(clk) --投入钱并计算总值

begin

if reset1='1'then tincoint<="00000";

elsif clk'event and clk='1' then

if coin1='1'then touru<="0001";

elsif coin5='1'then touru<="0101";

elsif coin10='1'then touru<="1010";

elsif coin1='0' and coin5='0' and coin10='0' then touru<="0000";

end if;

tincoint<=touru+tincoint;

end if;

end process p2;

p3:process(c_state) --进行购买,找零,退钱

begin

zong<=tincoint;

case c_state is

when s0=> if six='1' then stamp<="0110";n_state<=s1; --选通6角或8角邮票elsif eight='1' then stamp<="1000"; n_state<=s1;

else zong<="00000";ret<="0000";light<='0';n_state<=s0;

end if;

when s1=> if zong<stamp then

if reset='1' then ret<=zong(3 downto 0); n_state<=s2;

end if;

elsif zong>=stamp then light<='1';ret<=(zong-stamp);

end if;

when s2=> if six='1'or eight='1'then

ret<=zong(3 downto 0);light<='0';zong<="00000";

n_state<=s0;

end if;

end case;

end process p3;

p4:process(ret) --找钱,退钱的相应指示灯

begin

case ret is

when "0000" => retlight<="0000"; when "0001" => retlight<="0001";

when "0010" => retlight<="0010"; when "0011" => retlight<="0011"; when "0100" => retlight<="0100"; when "0101" => retlight<="0101"; when "0110" => retlight<="0110"; when "0111" => retlight<="0111"; when "1000" => retlight<="1000"; when "1001" => retlight<="1001"; when others => null;

end case;

end process p4;

end xxrr;

波形图:。