cd4017计数器的工作原理

CD4017资料

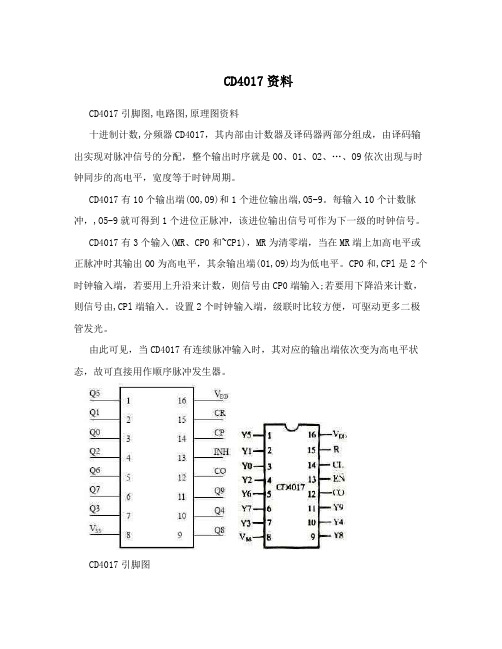

CD4017资料CD4017引脚图,电路图,原理图资料十进制计数,分频器CD4017,其内部由计数器及译码器两部分组成,由译码输出实现对脉冲信号的分配,整个输出时序就是O0、O1、O2、…、O9依次出现与时钟同步的高电平,宽度等于时钟周期。

CD4017有10个输出端(O0,O9)和1个进位输出端,O5-9。

每输入10个计数脉冲,,O5-9就可得到1个进位正脉冲,该进位输出信号可作为下一级的时钟信号。

CD4017有3个输入(MR、CP0和~CP1),MR为清零端,当在MR端上加高电平或正脉冲时其输出O0为高电平,其余输出端(O1,O9)均为低电平。

CP0和,CPl是2个时钟输入端,若要用上升沿来计数,则信号由CP0端输入;若要用下降沿来计数,则信号由,CPl端输入。

设置2个时钟输入端,级联时比较方便,可驱动更多二极管发光。

由此可见,当CD4017有连续脉冲输入时,其对应的输出端依次变为高电平状态,故可直接用作顺序脉冲发生器。

CD4017引脚图一、用一个CD4017制成的彩灯电路1.用一个CD4017制作的彩灯电路如图1 所示。

VCC1R110KU?2R048RSTVCC6P13THR20k57CVOLTDISC24TRIG163R2135GNDOUT14210K15 4NE555D6871210C17131C21150.01uF100pF896cd4017910.电路工作原理CD4017输出高电平的顺序分别是?、?、?、?、?、?、?、?、?脚,故?、?、?、?、?、?脚的高电平使6串彩灯向右顺序发光,?、?、?脚的高电平使6串彩灯由中心向两边散开发光。

各种发光方式可按自己的需要进行具体的组合,若要改变彩灯的闪光速度,可改变电容C1的大小。

二、用三个CD4O17彩灯电路图CD4017的级连,如图2所示。

2(CD4017级连后可以顺序输出24个高电平,同上理可组合出各种不同的发光方式,见图3,可使6串彩灯向右流水发光,再向左流水发光,中心向两边散开后再向中心靠拢发光,1、3、5、2、4、6串间隔发光等等CD4017功能简述:CD4017是5位Johnson计算器,具有10个译码输出端,CP,CR,INH输入端。

cd4017工作原理

cd4017工作原理

CD4017是一种常见的十进制计数器芯片,它可以将输入信号

按照顺序分配到10个输出引脚上。

该芯片是由一个主计数器

和一个辅助计数器组成的。

主计数器用于存储当前的计数值,辅助计数器则用于控制主计数器的计数顺序。

在CD4017工作时,首先要保证RESET引脚的电平为低电平,这样可以将主计数器复位为初始状态。

其次,时钟信号(CLOCK)被输入到CLOCK引脚上,当CLOCK信号的边沿触

发器工作时,主计数器就会根据时钟信号的变化进行计数。

当计数达到10时,主计数器会自动重置为0,并且辅助计数器

会自动加1。

辅助计数器的输出由十个输出引脚(Q0-Q9)表示。

对于每个输

入时钟脉冲,辅助计数器会使得相应的输出引脚(Q0-Q9)变为

高电平,而其他的输出引脚则保持低电平。

这样,我们可以通过检测Q0-Q9引脚的电平变化来实现对输入信号的分配。

需要注意的是,CD4017只能实现十进制的计数,而且它是一

个顺序计数器,即每次只能计数1个单位。

如果需要实现其他进制或者多单位的计数,就需要使用其他的计数器芯片。

通过这样的工作原理,CD4017计数器芯片能够在很多电子电

路中实现各种不同的功能,比如时序控制、信号分配等。

CD4017的原理及应用电路

CD4017的原理及应用电路一、原理介绍:CD4017是一种CMOS逻辑芯片,由10位二进制计数器和十个输出引脚组成。

它有一个时钟输入引脚(CLK)和一个复位引脚(RST),CLK触发计数器计数,RST用于将计数器复位为0。

当CLK引脚接收到上升沿时,计数器会递增1,同时输出引脚中的一个将变为高电平,其余输出引脚将变为低电平。

二、工作原理:当CD4017复位后,输出引脚0(Q0)为高电平,其余引脚为低电平。

当CLK输入引脚接收到上升沿时,计数器会递增1、输出引脚中的其中一位(从Q0到Q9)将变为高电平,而上一个高电平输出引脚将变为低电平。

每次计数由上升沿触发,从0到9循环,所以接收到10个时钟脉冲时,所有输出引脚都会被触发一次。

三、应用电路:1.LED跑马灯:CD4017常用于驱动LED的控制电路。

一个简单的应用是LED跑马灯电路。

可以将CD4017与LED灯串联,其中CLK接入一个时钟发生器,RST接入复位开关。

每当接收到一个时钟脉冲时,CD4017会将高电平依次传递给LED灯,使得LED灯按照顺序依次亮起。

2.计数显示器:将CD4017与七段数码管连接,可以构建一个简单的计数显示器。

当接收到时钟脉冲时,CD4017会递增1,并将当前计数值的二进制编码通过输出引脚传递给七段数码管,显示相应的数字。

通过适当的编码和解码电路,可以实现各种不同计数方式的显示。

3.触发摇摆器:4.步进电机控制器:CD4017可以用于步进电机的控制。

通过将CD4017的输出引脚与步进电机控制器的输入引脚连接,可以实现步进电机的顺序控制。

每当接收到时钟脉冲时,CD4017会将高电平输出引脚依次切换,从而控制步进电机的运动方向和步数。

以上是对CD4017的原理与常见应用电路的介绍。

CD4017是一种十分常见的分频计数器,具有较高的性能和稳定性,在各种电子设备中都有广泛的应用。

cd4017工作原理

cd4017工作原理CD4017是一款常用的分频器和计数器IC芯片,能够将一个时钟信号分频为不同的频率,并以二进制的形式进行计数。

CD4017工作原理简单易懂,是电子爱好者和工程师们常用的集成电路之一。

CD4017的主要特点是具有10个输出端口,分别对应0~9的数字。

当输入一个高电平脉冲信号时,CD4017会将输出信号从Q0开始依次向后移位,每个输出端口依次输出高电平信号,直到Q9输出高电平。

此时,CD4017会自动将输出信号重新指向Q0,开始下一轮计数。

CD4017的工作原理可以进一步解释为:当输入一个高电平脉冲信号时,CD4017的时钟输入端(SCK)会将信号传递到内部计数器,在下一次时钟信号到来之前,计数器会保持原来的状态。

而CD4017的输出端口则与计数器相连,通过输出端口的高低电平信号来判断当前计数器的状态。

CD4017的工作原理也可以通过电路原理图来理解。

当时钟信号到来时,CD4017的时钟输入端会将信号传入计数器并更新计数器的值。

同时,计数器的输出信号会经过10个与门,每个与门都与计数器的一个输出端口相连。

只有当计数器的某个输出端口为高电平时,与门才会输出一个高电平信号,进而驱动外部电路的工作。

除了常规的计数功能,CD4017还可以被用于设计各种电子应用,如LED跑马灯、数字钟表、电子游戏等。

通过外部电路的设计,CD4017可以实现更加复杂的功能。

例如,当计数器的某一位达到指定值时,可以通过中断信号来触发其他电路的工作。

此外,CD4017还可以与其他集成电路配合使用,如与74HC595芯片配合使用,可以实现更多复杂的功能。

CD4017作为一款常见的计数器和分频器IC芯片,其工作原理简单易懂,可以应用于各种电子设计中,是电子工程师和爱好者们不可或缺的集成电路之一。

数字电路CD4017的原理及应用电路之欧阳生创编

数字电路CD4017的原理及应用电路数字电路CD4017是十进制计数/分频器,它的内部由计数器及译码器两部分组成,由译码输出实现对脉冲信号的分配,整个输出时序就是Q0、Q1、Q2、…、Q9依次出现与时钟同步的高电平,宽度等于时钟周期。

CD4017有10个输出端(Q0~Q9)和1个进位输出端~Q5-9。

每输入10个计数脉冲,~Q5-9就可得到1个进位正脉冲,该进位输出信号可作为下一级的时钟信号。

CD4017有3个输(MR、CP0和~CP1),MR为清零端,当在MR端上加高电平或正脉冲时其输出Q0为高电平,其余输出端(Q1~Q9)均为低电平。

CP0和~CPl是2个时钟输入端,若要用上升沿来计数,则信号由CP0端输入;若要用下降沿来计数,则信号由~CPl端输入。

设置2个时钟输入端,级联时比较方便,可驱动更多二极管发光。

由此可见,当CD4017有连续脉冲输入时,其对应的输出端依次变为高电平状态,故可直接用作顺序脉冲发生器。

CD4017有两个时钟端 CP 和 EN,若用时钟脉冲的上沿计数,则信号从 CP 端输入;若用下降沿计数,则信号从EN 端输入。

设置两个时钟端是为了级联方便。

CD4017 与CD4022 是一对姊妹产品,主要区别是CD4022 是八进制的,所以译码输出仅有 Y0~Y7,每输入8 个脉冲周期,就可得到一个进位输出,它们的管脚相同,不过 CD4022 的 6、9 脚是空脚。

cd4017方框图 cd4017引脚图一、用一个CD4017制成的彩灯电路1.用一个CD4017制作的彩灯电路如图1 所示。

cd4017电路图2.电路工作原理 CD4017输出高电平的顺序分别是③、②、④、⑦、⑩、①、⑤、⑥、⑨脚,故③、②、④、⑦、⑩、①脚的高电平使6串彩灯向右顺序发光,⑤、⑥、③脚的高电平使6串彩灯由中心向两边散开发光。

各种发光方式可按自己的需要进行具体的组合,若要改变彩灯的闪光速度,可改变电容C1的大小。

cd4017计数器的工作原理

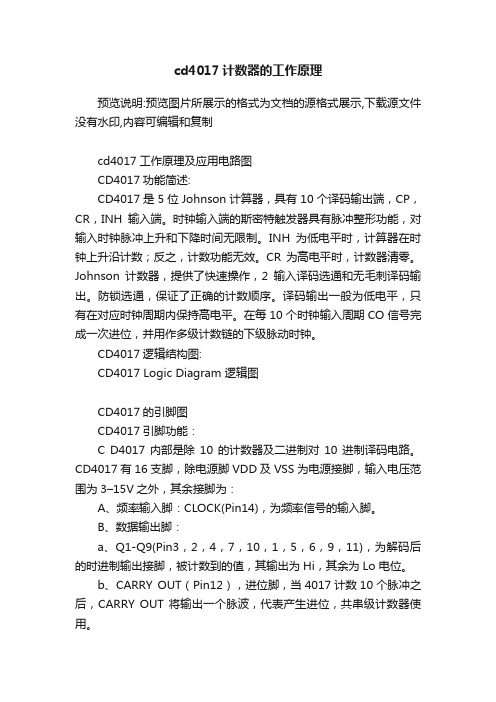

cd4017计数器的工作原理预览说明:预览图片所展示的格式为文档的源格式展示,下载源文件没有水印,内容可编辑和复制cd4017工作原理及应用电路图CD4017功能简述:CD4017是5位Johnson计算器,具有10个译码输出端,CP,CR,INH输入端。

时钟输入端的斯密特触发器具有脉冲整形功能,对输入时钟脉冲上升和下降时间无限制。

INH为低电平时,计算器在时钟上升沿计数;反之,计数功能无效。

CR为高电平时,计数器清零。

Johnson计数器,提供了快速操作,2输入译码选通和无毛刺译码输出。

防锁选通,保证了正确的计数顺序。

译码输出一般为低电平,只有在对应时钟周期内保持高电平。

在每10个时钟输入周期CO信号完成一次进位,并用作多级计数链的下级脉动时钟。

CD4017逻辑结构图:CD4017 Logic Diagram 逻辑图CD4017的引脚图CD4017引脚功能:C D4017内部是除10的计数器及二进制对10进制译码电路。

CD4017有16支脚,除电源脚VDD及VSS为电源接脚,输入电压范围为3–15V之外,其余接脚为:A、频率输入脚:CLOCK(Pin14),为频率信号的输入脚。

B、数据输出脚:a、Q1-Q9(Pin3,2,4,7,10,1,5,6,9,11),为解码后的时进制输出接脚,被计数到的值,其输出为Hi,其余为Lo 电位。

b、CARRY OUT(Pin12),进位脚,当4017计数10个脉冲之后,CARRY OUT 将输出一个脉波,代表产生进位,共串级计数器使用。

D、控制脚:a、CLEAR(Pin15):清除脚或称复位(Reset)脚,当此脚为Hi时,会使CD4017的Q0为”1”,其余Q1-Q9为”0”。

b、CLOCK ENABLE(Pin13),时序允许脚,当此脚为低电位,CLOCK输入脉波在正缘时,会使CD4017计数,并改变Q1-Q9的输出状态。

方框图:十进制计数/分频器CD4017,其内部由计数器及译码器两部分组成,由译码输出实现对脉冲信号的分配,整个输出时序就是O0、O1、O2、…、O9依次出现与时钟同步的高电平,宽度等于时钟周期。

4017芯片

数字电路CD4017的原理及应用电路2008/10/18 00:26数字电路CD4017是十进制计数/分频器,它的内部由计数器及译码器两部分组成,由译码输出实现对脉冲信号的分配,整个输出时序就是Q0、Q1、Q2、…、Q9依次出现与时钟同步的高电平,宽度等于时钟周期。

CD4017有10个输出端(Q0~Q9)和1个进位输出端~Q5-9。

每输入10个计数脉冲,~Q5-9就可得到1个进位正脉冲,该进位输出信号可作为下一级的时钟信号。

CD4017有3个输(MR、CP0和~CP1),MR为清零端,当在MR端上加高电平或正脉冲时其输出Q0为高电平,其余输出端(Q1~Q9)均为低电平。

CP0和~CPl是2个时钟输入端,若要用上升沿来计数,则信号由CP0端输入;若要用下降沿来计数,则信号由~CPl端输入。

设置2个时钟输入端,级联时比较方便,可驱动更多二极管发光。

由此可见,当CD4017有连续脉冲输入时,其对应的输出端依次变为高电平状态,故可直接用作顺序脉冲发生器。

CD4017有两个时钟端 CP 和 EN,若用时钟脉冲的上沿计数,则信号从 CP 端输入;若用下降沿计数,则信号从 EN 端输入。

设置两个时钟端是为了级联方便。

CD4017 与 CD4022 是一对姊妹产品,主要区别是 CD4022 是八进制的,所以译码输出仅有 Y0~Y7,每输入 8 个脉冲周期,就可得到一个进位输出,它们的管脚相同,不过 CD4022 的 6、9 脚是空脚。

cd4017方框图 cd4017引脚图一、用一个CD4017制成的彩灯电路1.用一个CD4017制作的彩灯电路如图1 所示。

cd4017电路图2.电路工作原理CD4017输出高电平的顺序分别是③、②、④、⑦、⑩、①、⑤、⑥、⑨脚,故③、②、④、⑦、⑩、①脚的高电平使6串彩灯向右顺序发光,⑤、⑥、③脚的高电平使6串彩灯由中心向两边散开发光。

各种发光方式可按自己的需要进行具体的组合,若要改变彩灯的闪光速度,可改变电容C1的大小。

cd4017工作原理及应用电路图

cd4017工作原理及应用电路图CD4017功能简述:CD4017是5位Johnson 计算器,具有10个译码输岀端, CP , CR , INH 输入端。

时钟输入 端的斯密特触发器具有脉冲整形功能,对输入时钟脉冲上升和下降时间无限制。

INH 为低电平时, 计算器在时钟上升沿计数;反之,计数功能无效。

CR 为高电平时,计数器清零。

Johnson 计数器,提供了快速操作, 2输入译码选通和无毛刺译码输出。

防锁选通,保证了正确的计数顺序。

译码输岀一般为低电平,只有在对应时钟周期内保持高电平。

在每 10个时钟输入周期 CO 信号完成一次进位,并用作多级计数链的下级脉动时钟。

CD4017逻辑结构图:CD4017BCD4017 Logic Diagram 逻辑图CD4017引脚图:Hr.D QC *CD4017BCD4017的引脚图CD4017引脚功能:CD4017内部是除10的计数器及二进制对 10进制译码电路。

CD4017有16支脚,除电源脚 VDD 及VSS 为电源接脚,输入电压范围为3 -5V 之外,其余接脚为:A 、 频率输入脚:CLOCK(P in 14),为频率信号的输入脚。

B 、 数据输出脚:a 、 Q1-Q9(Pin3,2,4,7,10,1,5,6,9,11),为解码后的时进制输岀接脚,被计数到的 值,其输岀为 Hi ,其余为Lo 电位。

b 、 CARRY OUT (Pin12 ),进位脚,当4017计数10个脉冲之后, CARRY OUT 将输岀一个脉 波,代表产生进位,共串级计数器使用。

D 、 控制脚:a 、 CLEAR(Pin 15):清除脚或称复位(Reset)脚,当此脚为 Hi 时,会使 CD4017的Q0为” 1,” 其余Q1-Q9为” 0”b 、 CLOCK ENABLE(Pin13),时序允许脚,当此脚为低电位, CLOCK 输入脉波在正缘时,会 使CD4017计数,并改变 Q1-Q9的输岀状态。

cd4017芯片手册

cd4017芯片手册

CD4017是一款逻辑IC,拥有10个解码输出,输入包括一个时钟、复位和cLock INHIBIT_signal。

以下是CD4017芯片手册的部分内容:

1. 功能描述:CD4017是一个十进制计数器,具有使能输入、时钟输入、复位输入和十个输出。

当使能输入为低电平时,计数器在时钟上升沿时增加。

当使能输入为高电平时,计数器被复位到0。

2. 引脚排列:CD4017采用16脚封装,引脚排列如下:

1、2、3、4脚:共同连接到一个公共端子,通常接地。

5脚:复位输入,低电平有效。

6脚:使能输入,高电平有效。

7~16脚:十个输出端。

14脚:时钟输入。

3. 工作原理:当使能输入端为高电平,并且当时钟输入端有上升沿时,计数器将增加1。

如果计数器的值达到9(即十进制中的9),则对应的输出将变为低电平。

当计数器的值再次减少到0时,所有输出将恢复为高电平。

4. 应用:CD4017广泛应用于各种数字电路中,如计数器、分频器、脉冲发生器等。

由于其具有十个输出,可以同时驱动多个LED或其他负载。

如需获取更详细的信息,建议查阅CD4017芯片手册或咨询相关技术人员。

cd4017工作原理

cd4017工作原理CD4017是一种常用的集成电路,它广泛应用于各种计数和时序控制电路中。

本文将介绍CD4017的工作原理及其在电子电路中的应用。

CD4017是一种16脚的CMOS数字集成电路,它具有10个输出引脚和一个时钟输入引脚。

CD4017的工作原理基于它内部的十进制计数器。

当时钟信号输入时,CD4017能够按照特定的顺序在其10个输出引脚之间进行切换,实现计数功能。

在每个时钟脉冲到来时,CD4017会将输出信号从一个引脚切换到下一个引脚,直到所有的输出引脚都被触发一次,然后再次从第一个引脚开始。

CD4017的工作原理可以通过一个简单的实例来解释。

假设我们将CD4017的输出引脚连接到LED灯,当时钟信号输入时,LED灯将按照顺序依次亮起。

这种计数功能可以被广泛应用于各种电子设备中,比如数字显示器、计数器、时序控制器等。

除了基本的计数功能,CD4017还可以通过外部电路进行扩展,实现更复杂的控制功能。

例如,我们可以通过外部逻辑门和触发器来实现CD4017的分频功能,从而得到更高精度的计数。

此外,CD4017还可以与其他集成电路结合,实现更复杂的逻辑控制功能。

在实际应用中,CD4017常常与其他集成电路和外部元件结合,构成各种复杂的计数和控制电路。

比如,在LED跑马灯电路中,CD4017可以实现LED灯的顺序点亮;在数字显示器中,CD4017可以实现数码管的驱动和显示控制;在定时器和计数器中,CD4017可以实现精确的计时和计数功能。

总之,CD4017是一种功能强大的集成电路,它具有简单的工作原理和灵活的应用方式,可以广泛应用于各种电子电路中。

通过深入理解CD4017的工作原理,我们可以更好地发挥它在电子设计中的作用,实现更多样化、更灵活的控制功能。

希望本文能够对读者理解CD4017的工作原理和应用提供帮助。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

cd4017工作原理及应用电路图

CD4017功能简述:

CD4017是5位Johnson计算器,具有10个译码输出端,CP,CR,INH输入端。

时钟输入端的斯密特触发器具有脉冲整形功能,对输入时钟脉冲上升和下降时间无限制。

INH为低电平时,计算器在时钟上升沿计数;反之,计数功能无效。

CR为高电平时,计数器清零。

Johnson计数器,提供了快速操作,2输入译码选通和无毛刺译码输出。

防锁选通,保证了正确的计数顺序。

译码输出一般为低电平,只有在对应时钟周期内保持高电平。

在每10个时钟输入周期CO信号完成一次进位,并用作多级计数链的下级脉动时钟。

CD4017逻辑结构图:

CD4017 Logic Diagram 逻辑图

CD4017的引脚图

CD4017引脚功能:

C D4017内部是除10的计数器及二进制对10进制译码电路。

CD4017有16支脚,除电源脚VDD及VSS为电源接脚,输入电压范围为3–15V之外,其余接脚为:

A、频率输入脚:CLOCK(Pin14),为频率信号的输入脚。

B、数据输出脚:

a、Q1-Q9(Pin3,2,4,7,10,1,5,6,9,11),为解码后的时进制输出接脚,被计数到的值,其输出为Hi,其余为Lo 电位。

b、CARRY OUT(Pin12),进位脚,当4017计数10个脉冲之后,CARRY OUT 将输出一个脉波,代表产生进位,共串级计数器使用。

D、控制脚:

a、CLEAR(Pin15):清除脚或称复位(Reset)脚,当此脚为Hi时,会使CD4017的Q0为”1”,其余Q1-Q9为”0”。

b、CLOCK ENABLE(Pin13),时序允许脚,当此脚为低电位,CLOCK输入脉波在正缘时,会使CD4017计数,并改变Q1-Q9的输出状态。

方框图:

十进制计数/分频器CD4017,其内部由计数器及译码器两部分组成,由译码输出实现对脉冲信号的分配,整个输出时序就是O0、O1、O2、…、O9依次出现与时钟同步的高电平,宽度等于时钟周期。

CD4017有10个输出端(O0~O9)和1个进位输出端~O5-9。

每输入10个计数脉冲,~O5-9就可得到1个进位正脉冲,该进位输出信号可作为下一级的时钟信号。

CD4017有3个输(MR、CP0和~CP1),MR为清零端,当在MR端上加高电平或正脉冲时其输出O0为高电平,其余输出端(O1~O9)均为低电平。

CP0和~CPl是2个时钟输入端,若要用上升沿来计数,则信号由CP0端输入;若要用下降沿来计数,则信号由~CPl端输入。

设置2个时钟输入端,级联时比较方便,可驱动更多二极管发光。

由此可见,当CD4017有连续脉冲输入时,其对应的输出端依次变为高电平状态,故可直接用作顺序脉冲发生器。