第10章 数据处理指令与移位寄存器

移位寄存器

移位寄存器移位寄存器是暂时存放数据的部件,同时它还具有移位功能。

一、特点和分类从逻辑结构上看,移位寄存器有以下两个显著特征:(1)移位寄存器是由相同的寄存单元所组成。

一般说来,寄存单元的个数就是移位寄存器的位数。

为了完成不同的移位功能,每个寄存单元的输出与其相邻的下一个寄存单元的输入之间的连接方式也不同。

(2)所有寄存单元共用一个时钟。

在公共时钟的作用下,各个寄存单元的工作是同步的。

每输入一个时钟脉冲,寄存器的数据就顺序向左或向右移动一位。

通常可按数据传输方式的不同对CMOS移位寄存器进行分类。

移位寄存器的数据输入方式有串行输入和并行输入之分。

串行输入就是在时钟脉冲作用下,把要输入的数据从一个输入端依次一位一位地送入寄存器;并行输入就是把输入的数据从几个输入端同时送入寄存器。

在CMOS移位寄存器中,有的品种只具有串行或并行中的一种输入方式,但也有些品种同时兼有串行和并行两种输入方式。

串行输入的数据加到第一个寄存单元的D端,在时钟脉冲的作用下输入,数据传送速度较慢;并行输入的数据一般由寄存单元的R、S端送入,传送速度较快。

移位寄存器的移位方向有右移和左移之分。

右移是指数据由左边最低位输入,依次由右边的最高位输出;左移时,右边的第一位为最低位,最左边的则为最高位,数据由低位的右边输入,由高位的左边输出。

移位寄存器的输出也有串行和并行之分。

串行输出就是在时钟脉冲作用下,寄存器最后一位输出端依次一位一位地输出寄存器的数据;并行输出则是寄存器的每个寄存单元均有输出。

CMOS移位寄存器有些品种只有一种输出方式,但也有些品种兼具两种输出方式。

实际上,并行输出方式也必然具有串行输出功能。

表1表1是CMOS移位寄存器的分类。

二、常用CMOS移位寄存器简介1.串入-串出移位寄存器CD4006图1是18位移位寄存器CD4006的逻辑框图和引脚功能图。

由图可见,CD4006由四组移位寄存器组成,其中的两组为4位,每组有一输出端,由最高位引出。

移位寄存器指令

(2)I/O分配 输入 (常开)起动按钮:I0.0 (常闭)停止按钮:I0.1

输出 L1:Q0.0 L5、L9: Q0.4 L2:Q0.1 L6、L10:Q0.5 L3:Q0.2 L7、L11:Q0.6 L4:Q0.3 L8、L12:Q0.7

M10.0

Q0.7

Q0.6

Q0.5

Q0.4

Q0.3

Q0.2

Q0.1

Q0.0

DATA

I0.0 M1.0 M1.T37(M10.0)延时0.5s导通一个扫描周期

T37 IN +5 PT TON

数据输入端 M10.0

第八个脉冲到来时M11.0置位为1,同时通过与 T37并联的M11.0常开触点使M10.0置位为1

3. 移位寄存器指令

• (2)DATA和S-BIT的操作数为I, Q, M, SM, T, C, V, S, L 。 • 数据类型为:BOOL变量。 • N的操作数为VB, IB, QB, MB, SB, SMB, LB, AC, 常量。 • 数据类型为:字节。

【例5-6】移位寄存器应用举例。

时序图

M0.0 EN M10.0 M10.1 +8 M10.1 M10.2 M10.3 M10.4 M10.5 M10.6 M10.7 M11.0 I0.1

SHRB

ENO

DATA S_BIT N

Q0.0 Q0.1 Q0.2 Q0.3 Q0.4 Q0.5 Q0.6 Q0.7 M10.1 R 8

3. 移位寄存器指令(SHRB)

SHRB DATA,S-BIT,N

3. 移位寄存器指令(SHRB)

(1)移位寄存器指令SHRB将DATA数值移入移位 寄存器。 EN为使能输入端,连接移位脉冲信号,每次使 能有效时,整个移位寄存器移动1位。DATA为数据 输入端,连接移入移位寄存器的二进制数值。 S_BIT指定移位寄存器的最低位。 N:移位寄存器的长度和移位方向,移位寄存 器的最大长度为64位,N为正值表示左移位,输入 数据(DATA)移入移位寄存器的最低位 (S_BIT),并移出移位寄存器的最高位。

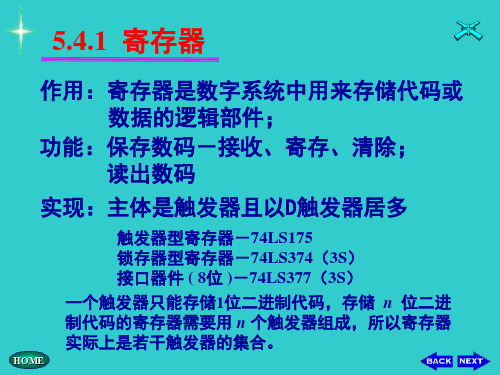

寄存器和移位寄存器

作用:寄存器是数字系统中用来存储代码或 数据的逻辑部件; 功能:保存数码-接收、寄存、清除; 读出数码

实现:主体是触发器且以D触发器居多

触发器型寄存器-74LS175 锁存器型寄存器-74LS374(3S) 接口器件 ( 8位 )-74LS377(3S) 一个触发器只能存储1位二进制代码,存储 n 位二进 制代码的寄存器需要用 n 个触发器组成,所以寄存器 实际上是若干触发器的集合。

CR D OL

&

1D >C1 R

& FF0

1D >C1 R

& FF1

1D >C1 R

&

FF3 1D > C1 R D

OR

Q

0

Q

1

Q

2

Q

3

S=1 S=0

D0 DSR D0 Q1

D1 Q 0

D1 Q2

D2 Q 1 D2 Q 3

D3 Q2 D3 QSL

右移 左移

5.5.2 集成移位寄存器

串行数据输 出端

D2=Q1

D3=Q2

D触发器的特性方程

Qn+1=D

Q0n+1=DI Q1n+1 =Q0 Q2n+1 =Q1 Q3n+1 =Q2

5.5.1

移位寄存器电路分析

Q0 DI D0 FF0 1D Q D1

并

行 Q1

输 Q2 FF2 1D Q D3

出 Q3 FF3 1D Q 串行输出

FF1 1D Q

4

1

1

0

1

1

Q0 Q1 Q2 Q3 CP 经过4 个CP脉冲作用后,从 DI 端串行输入的数码 就可以从 串入0 并出 2Q 1 Q0 Q1 Q1( D3并行输出。 ) 0 0

S7-200系列PLC的数据处理指令

VW200 1110 0010 1010 1101

第一次循环移位后

溢出

第一次移位后

溢出

AC0

1010 0000 0000 0000

1 VW200 1100 0101 0101 1010

1

第二次循环移位后 AC0 0101 0000 0000 0000

0 标志位(SM1.0 )=0 溢出标志位(SM1.1 )= 0

中。

在梯形图中,可以设定OUT和IN指向同一内存单元,这

样

可节省内存。

(6)双字的循环右移/左移指令

指令

说明

ROR_ 双字的循环右移/左移指令把源双字IN指定的内容向右/左循环

DW 移N位,结果存入OUT指定的目标字中。

EN

操作数:

IN

IN:VD,ID,QD,MD,SMD,AC,HC,*VD,*AC,

可节省内存。

执行结果对特殊标志位影响。SM1.0(0),SM1.1 溢出

。

CPU212和CPU214无此指令。

(5) 字的循环右移/左移指令

指令

说明

ROR_W 字的循环右移/左移指令把源字IN指定的内容向右/左循环移

EN

N位,结果存入OUT指定的目标字中。

IN

操作数:

N OUT

IN:VW,T,C,IW,QW,MW,SMW,AC,AIW, 常

N:VB,IB,QB,MB,SMB,AC,常数,*VD ,

*AC,SB

(6)字的块传送指令

指令

说明

BLKMOV_W

字的块传送指令:

EN

将从IN开始的连续N个字的数据块的内容复制到

IN1

从字OUT开始的数据块里。N的有效范围是1~255

寄存器和移位寄存器(共15张PPT)

第2页,共15页。

寄存器的结构特点

Q0 Q0

FF0 1D C1 R

Q1 Q1

FF1 1D C1 R

Q2 Q2

FF2 1D C1 R

Q3 Q3

FF3 1D C1 R

D0 CP CR D1

D2

D3

各触发器均为 D 功能且并行使用。

1 个触发器能存放 1 位二进制数码,因此 N 个触 发器可构成 N 位寄存器。

(1) 用同步置零端或置数端获得 N 进制计数器 。这时应根据 SN-1 对应的二进制代码写反馈函数。

4 位寄存器 理解寄存器和移位寄存器的作用和工作原理。

翻转是否同步分有:同步计数器和异步计数器 理解寄存器和移位寄存器的作用和工作原理。

M1 M0 = 01 时,右移功能。 和状态转换真值表,然后由此分析时序逻 按计数进制分有:二进制计数器、十进制计数器和任意进制计数器;

。计数器除了用于计数外,还常用于分频、定 每输入一个移位脉冲,移位寄存器中的数码依次向左移动 1 位。

6.4 寄存器和移位寄存器

主要要求:

理解寄存器和移位寄存器的作用和工作原理。 了解集成移位寄存器的应用。

第1页,共15页。

一、寄存器

RQe0g~isQte3r,是同用时于输存出放的二,进这制种数输码出。方式称

并行输出。

DQ00 Q0 QD11 Q1 QD22 Q2 QD33 Q3

4 位 寄

FF0 1D C1 R

有关。时序逻辑电路的工作状态由触发器存

储和表示。

第9页,共15页。

时序逻辑电路按时钟控制方式不同分为同步时序逻 辑电路和异步时序逻辑电路。前者所有触发器的时 钟输入端 CP 连在一起,在同一个时钟脉冲 CP 作用

数字电路寄存器和移位寄存器PPT学习教案

真值表:(同步触发器)

____

CPi

Di

Q n1 i

Q n1 i

__

0 X Qin Qin

10 0 1

11 1 0

2.带公共时钟和复位的六位寄存器 (TTL74174)

Q1

Q2

Q3

Q4

Q5

Q6

D1

D2

D3

D4

D5

D6

Rd

Rd

Rd

Rd

Rd

Rd

CP

__

Cr

CP

__

Cr

真值表:(边沿触发器)

状态图: 有效循环(六进制计数器或六分频器)

Q0Q1Q2 000 100 110

001 011 111

无效循环

101 010

第10页/共13页

c . 奇数分频器(数据右移)

f CP 7

1 0

CP QA QB QC QD

0

0

0

0

CP

1000

0 QA QB QC QD

S

1

S

__

Cr DR A B C D DL

并行输出 Q2

D F2

第3页/共13页

CP Q0 Q1 Q2 000

1 0 0 DL0 2 0 DL0 DL1 3 DL0 DL1 DL2

CP Q0 Q1 Q2

第4页/共13页

Q0 Q1

R

右移数据输入 D

J

J

F0

F1

K

K

三位右移寄存器

CP Q0 Q1 Q2 000

1 DR0 0 0 2 DR1 DR0 0 3 DR2 DR1 DR0

第5页/共13页

《移位寄存器》课件

技术挑战与展望

高精度与高稳定性

随着应用需求的不断升级,对移位寄存器的精度和稳定性要求也越来越高。未来的研究将 致力于提高移位寄存器的性能指标,以满足各种高端应用的需求。

低功耗与高能效

在便携式和移动设备中,功耗和能效是至关重要的性能指标。未来的移位寄存器设计将更 加注重节能和能效提升,以延长设备的续航时间和降低运行成本。

硬件描述语言实现

使用Verilog或VHDL等硬件描述语言编写移位寄存器的逻辑 电路,通过仿真和综合工具生成可编程逻辑门阵列(FPGA) 或专用集成电路(ASIC)的配置文件。

集成电路实现

将移位寄存器的逻辑电路直接集成在一片集成电路(IC)中 ,通过外部接口与其它电路或系统连接。

基于软件的实现方式

ASIC实现

将移位寄存器的逻辑电路定制集成到专用集成电路(ASIC)中,通过硬件实现移位寄 存器的功能。ASIC具有高性能和低功耗的特点,但开发周期较长且成本较高。

05 移位寄存器的性能指标与 优化

性能指标

吞吐量

衡量移位寄存器处理数据的能 力,通常以每秒传输的位数( bps)或每秒传输的帧数(fps

。

02

小型化

随着便携式电子设备的普及,移位寄存器的小型化需求也越来越迫切。

小型化移位寄存器的设计需要综合考虑性能、功耗和集成度等多个因素

。

03

智能化

智能化是当前电子设备的重要发展方向,移位寄存器也不例外。通过集

成智能算法和传感器,移位寄存器可以实现自适应控制和预测性维护等

功能,提高设备的整体性能和可靠性。

集成化与模块化

集成化和模块化是提高移位寄存器可靠性和可维护性的重要手段。未来的移位寄存器将更 加注重模块化和可扩展性设计,以方便设备的组装和维护。同时,集成化设计也有助于减 小设备体积和重量,满足便携式应用的需求。

数据移位和数据转换指令

可逆移位寄存器的用法

① 控制通道C的含义

15 14 13 12

不使用 移位方向 1:左移(低→高) 0:右移(高→低) 数据输入 移位脉冲输入

SFTR (84)

C St E

复位

1: St~E及CY清零 0:根据C的状态移位

② 左、右移位的控制

●通道C之bit 15为0时,在移位脉冲的作用下, 根据C之bit 12的状态进行左移或右移。 ○ C之bit 12为1 左移:每个扫描周期,从St到 E按位依次左移一位,C之bit13的数据移入St 之bit 0中,E之bit15的数据 移入CY中。 ○ C之bit 12为0右移:每个扫描周期,从E到 St按位依次右移一位,C之bit13的数据移入E 之bit15中,St之bit0的数据移入CY中。

00000

25502 00001 25315 20003

IN SP

SFT(10)

200 200

R

01000

25502的秒脉冲作为移位脉冲

第一个移位脉冲输入后,00000的ON状态移入20000。

经过4个移位脉冲20003 ON,于是01000 ON。

第五个移位脉冲时20003 OFF,于是01000 也OFF。 移位过程中,只要00001为ON,移位寄存器即复位。

St:移位首通道

E:移位结束通道

功能:当执行条件为ON时,执行指令将St~E中的数 据以数字为单位依次左移位1位。如下图:

溢出 ←

E St

…

←0

4. 算术左/右移位指令ASL (25)/ ASR(26)

算术左/右移位指令的功能和使用方法相似

以算术左移指令为例,介绍它们的功能和使用方法 ASL(25)

指令-数据处理指令(一)

0 1 0 0 1

7

LD I0.1 EU

0 0 0 1 1

1

I0.2

溢出位 7 溢出位

0 0 1 1 0

0

I0.2

SHRB I0.2, V10.0, 4

移位寄存器指令举例

用定时中断将CPU226的全部16个输出每200ms左循环移 动一位。初始状态是Q0.0,Q0.4,Q1.0,Q1.4为1。 NETWORK 1 LD SM0.1 MOVW +16#1111, QW0 MOVB 200, SMB34 ATCH INT_0, 10 ENI INT_0 NETWORK 1 LD SM0.0 RLW QW0, 1

IN2,OUT

整数完全除法指令,把输入端(IN)指定的两个16位整数相除,产生一个32位 结果,并送到输出端(OUT)指定的存储单元中去。其中高16位是余数,低16 位是商。

算术运算举例

LD +R *R I0.0 AC1, AC0 AC1, VD100

MOVR VD100, VD200 /R VD10, VD200

OUT

DTR

IN, OUT

ROUND

IN, OUT

TRUNC

IN, OUT

双字整数转为实数(DTR)指令:将输入端(IN)指定的32位有符 号整数转换成32位实数 ROUND取整指令,转换时实数的小数部分四舍五入。 TRUNC取整指令,实数舍去小数部分后,转换成32位有符号整数。

取整指令被转换的输入值应是有效的实数,如果实数值太大,使输出 无法表示,那末溢出位(SM1.1)被置位。

Network 1 SM0.0 AIW4

Sample AIW4.

MOV_W EN ENO

IN OUT VW100

数字电路与逻辑设计2寄存器移位寄存器

并行读出脉冲必须在经过5个移存脉冲后出 现,而且和移存脉冲出现旳时间错开。

D5

D4

D3

D2

D1

&

&

&

&

&

并行读出指令

串行输 入 1D

11001

CI

1D Q1

CI

1D Q2

CI

1D Q3

CI

1D

Q4

Q5

CI

移存脉冲CP

分析:假设串行输入旳数码为10011(左边先入)

串—并行转换状态表

序号 Q1 Q2 Q3 Q4 Q5

工作过程: ①在开启脉冲和时钟CP作用下,执行并

行置入功能。片ⅡQ3=DI6。 ②开启脉冲消失,在CP作用下,因为标志位0

旳存在,使门G1输出为1,使得SH/LD =1,执行右移移位寄存功能。 ③后来在移存脉冲作用,并行输入数据由片Ⅱ旳 Q3逐位串行输出,同步又不断地将片Ⅰ旳串 行输入端J,K=1旳数据移位寄存到寄存器。

末级输出反相后,接到串行输入端。

Q3Q2Q1Q0

1

0000

0001

0011

0111

∧

Q0Q 1Q2Q 3

CP D SR

74194

S0

1

S1

0

RD D 0 D 1 D2 D 3 D SL

1000

1100

1110

1111

0010

0101

1011

0110

清零

1001 0100

1010

1101

移位寄存器构成旳移位计数器

异步清零 同步置数

高位向低位移动(左移) 低位向高位移动(右移)

保持

3 、用集成移位寄存器实现任意模值 旳计数分频

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

立即数, 标签

要存储在 FIFO 内的数据

Source 将转换为数组标签的数据类型。较小的整数将通过符 号扩展转换为较大的整数。

FIFO

SINT ,INT, DINT, REAL 数组标签 字符串, 结构

要修改的 FIFO 指定 FIFO 的第一个元素 不要在下标中使用

CONTROL.POS

Control CONTROL

• 移位寄存器是一个允许将寄存器中的内容向左或 向右移动的逻辑控制器。

• 通过一个寄存器或一组寄存器,串行地将一个位 移位到相邻的位置。

MSB

LSB

初始格式 1 0 1 1 0 0 0 1 1 0 1 1 0 1 1 0

数据位=1 时钟

MSB

LSB

1101100011011011

第一次移位时钟之后的移位寄存器格式

字0 .EN

.DN

.ER .UL 未使用

字1 Length 位数组的大小( 位数)

字2 Position 指令指向的位的当前位置 (currently not used)

• Logix系统的左移指令 • Logix系统的右移指令

Logix PLC指令BSL(BSR)参数说明

操作数

Array

Control Source bit Length

数据位=0 时钟

MSB

LSB

0110110001101101

第二次移位时钟之后的移位寄存器格式

数据位=1 时钟

时钟 时钟

MSB

LSB

1011000110110110

MSB

LSB

1101100011011011

MSB

LSB

0110110001101101

具有多寄存器的移位寄存器

MSB

LSB

1011000110110110

FIFO和LIFO操作)实现的数据传输和操作 – 展示SLC 500和Logix PLC中如何应用数据处理和位移指令

• 目标

– 能够解释数据是如何由位、字和文件处理的 – 描述逻辑指令:与、或、异或 – 描述文件—算术—逻辑功能 – 解释概念:移位寄存器 – 描述先入先出和后入先出移位功能的操作 – 描述复制和充填指令的操作 – 描述SLC 500和Logix系统的数据处理和操作指令并使用其开发梯

空位指示 FIFO 为空。如果 .LEN ≤ 0 或 .POS < 0,将 置位 .EM 位和 .DN 位。

长度指定 FIFO 可同时容纳元素的最多个数。

位置标识 FIFO 中的位置,指令将在其中装载下一个 值。

说明: FFU 指令可以和 FFL 指令配合使用,按照先入先出的顺 序存储和检 索数据。 使能后, FFU 指令将从 FIFO 的第一个元 素中卸载数据,并将该值放 在 Destination 中。指令每使能一 次,便会卸载一个值,直至 FIFO 清 空为止。如果 FIFO 为空, FFU 将 0 返回到 Destination。

例: 使能后, FFL 指令会将 value_1

装载到 FIFO 中的下一个位置 ( 在本 示例中是 array_dint[5])。

装载 FIFO 之前

装载 FIFO 之后

array_dint[0] 00000

00000

11111

11111

22222 33333 44444

control_1.pos = 5 value_1 = 55555

MSB

LSB

0101100011011011

右循环移位寄存器

19

左位移(BSL)和右位移(BSR)指令

• SLC的左移指令 将要被移动的位数组的地址

将要被移入的数据位地址 • SLC的右文移件指的令位长度

– Control结构

操作结构的地址

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

第10章 数据处理指令与移位寄存器

10.1 目的及目标 10.2 数据处理 10.3 Allen-Bradley数据转移和操作指令 10.4 位和字操作指令的经验设计 10.5 故障诊断 10.6 指令的位置

10.1 目的及目标

• 目的

– 介绍位、字和文件在PLC中是如何处理的 – 讨论由逻辑指令、文件—算术—逻辑指令和移位寄存器(包括

标签

操作的控制结构 通常与关联的 FFU 使用相同的 CONTROL

Length DINT

立即数 FIFO 可同时容纳元素的最多个数

Position DINT

立即数

FIFO 中的下一个位置,指令将在 其 中装载数据 初始值通常为 0

• 队列卸载指令FFU

– FFU指令从FIFO的第一个元素卸载数据,并将该值放置到 Destination。每次卸载一个值,直到FIFO空为止。如果FIFO为 空,FFU向Destination返回0。

卸载 FIFO 之前 卸载

array_dint[0] 00000

卸载 FIFO 之后

11111

11111

22222

22222

33333

33333 44444

移动

44444 55555

array_dint[5]

55555 00000

control_1.pos = 6

00000 00000

control_1.pos = 5 Value_2=00000

– 数值模式将数组运算分配到若干次扫描中。 – 此模式常用于处理非时间性数据或大量 数据。 – 输入每次扫描要运算的元素个数,这样可 缩短扫描时间。

11

当梯级输入条件从假变为真时,将触发执行。指 令将在每次扫描时执 行,扫描次数为完成整个 数组运算所需的次数。一旦触发,梯级输入 条 件即使反复改变,也不会中断指令的执行。

2.字到文件 3.文件到字

N7:10 7589

N7:4 N7:5 N7:6 N7:7

473 589 3490

25

7589 7589 7589 7589

N10:3 N10:4 N10:5 N10:6

25 N10:15

10.3 A-B数据转移和操作指令

10.3.1 AND,OR和XOR指令

源A

0 1 0 1

到程序清零.ER 位。 .POS 值包含产生溢出的元素的位置。

.L•ENLenDgItNhT—文长件度长用于度指及定位FAL置指指令针操作,的立数即组元数素,数在目。指令中输入

.POS DINT 位置包含指令正在访问的当前元素的位置。

• 运算模式 Mode(有3种)

– 整体(ALL)、数值、增量(INC)

22222 33333 44444

array_dint[5] 00000

55555

00000

00000 control_1.pos = 6

00000

00000

00000

00000

00000

00000

例: 使能后 FFU 指令将

array_dint[0] 卸载到 value_2 中,并 对 array_dint 中其余的元素进行移位 。

• 队列加载指令FFL

– FFL指令将Source值加载到FIFO中有.POS值标识的位置。每次启 用该指令时加载一个值,直到FIFO满为止

– 通常Source和FIFO属于相同数据类型 – 使用FFL和FFU指令按先进先出的顺序存储和取回数据。

操作数

类型

格式

说明

Source

SINT ,INT, DINT, REAL 字符串, 结构

类型

格式

DINT

数组标签

CONTROL 标签

BOOL

标签

DINT

立即数

说明

要修改的数组,指定要开始移位的元素; 不要在下标中使用CONTROL.POS 操作的控制结构 要装载的位 要移位的数组中位的个数

BSL(BSR)指令Control结构

助记符 .EN .DN .UL .ER .LEN

数据类型 BOOL BOOL BOOL BOOL DINT

形图 – 在经验设计中加入数据处理和操作指令 – 将指令描述用于故障诊断

10.2 数据处理

• 数据处理包括在位、字和文件上进行算术和逻辑操作实现 的数据转移和操作。其中字也叫寄存器,文件被称为表、 块或列

10.2.1 字中的位格式

– 字中的位格式可以转移到另一个字中。 – 可以利用一个掩码来改变一个字中的一个单独的位

00000

00000

00000

00000

00000

00000

10.3.5 后入先出(LIFO)功能

• LIFO的功能与FIFO一样,但是移动的顺序相反。即最先 收到的最后输出,最后收到的则最先输出。

• LIFO的存储空间通常被称为堆栈 • SLC系列PLC功能限制与(FIFO)相同。 • LIFO操作指令有LFL与LFU • 本节重点介绍Logix的LIFO指令

一次 扫描

梯级输入条件

.EN位

.DN位

指令的扫描

每当梯级由假变真 ,处理一个数据元

不执素行运算

运算完成

清除状态位和.POS值

用于FAL指令的标准梯形图

将一个单元复制 到一个数组

将一个数组复制 到另一个数组

16

将一个数组复制 到另一个单元

p327,PLC 5转 换成Logix指令

10.3.3 移位寄存器

• 文件算术逻辑指令FAL对数组内存储的数据进行复制、算 术、逻辑及函数运算操作

• SLC 500不支持FAL指令 • 本节介绍Logix的FAL指令,如图所示

• Control—具有Control数据类型的标签,数据操作的控制 结构。Control结构如下表