模拟电路设计 基础知识(笔试时候容易遇到的题目)

模拟电路笔试题及答案

模拟电路笔试题及答案一、选择题1. 在模拟电路中,基本的放大器类型是:A. 差分放大器B. 运算放大器C. 电流放大器D. 电压放大器答案:A2. 理想运算放大器的输入阻抗是:A. 有限的B. 无穷大C. 零D. 负无穷大答案:B3. 一个理想的二端口网络,其输出端口短路时,输入端口的输入阻抗称为:A. 短路阻抗B. 开路阻抗C. 负载阻抗D. 源阻抗答案:A二、简答题1. 简述什么是负反馈,并说明其在放大器中的作用。

答案:负反馈是指将放大器的输出信号的一部分或全部以相反的相位反馈到输入端。

在放大器中,负反馈可以提高放大器的稳定性,减小非线性失真,增加带宽,改善放大器的性能。

2. 解释什么是共模抑制比(CMRR)以及它在差分放大器中的重要性。

答案:共模抑制比(CMRR)是指差分放大器对共模信号的抑制能力,即差分放大器对共模信号的增益与差模信号增益的比值。

CMRR是衡量差分放大器性能的一个重要参数,高CMRR意味着差分放大器能更好地抑制共模干扰,从而提高信号的信噪比。

三、计算题1. 给定一个理想运算放大器电路,输入电压为\( V_{in} \),反馈电阻\( R_f = 10k\Omega \),输入电阻\( R_i = 1k\Omega \),求输出电压\( V_{out} \)。

答案:由于理想运算放大器的输入阻抗为无穷大,所以输入电压\( V_{in} \)将完全施加在输入电阻\( R_i \)上。

根据电压跟随器的原理,输出电压\( V_{out} \)等于输入电压\( V_{in} \)。

2. 一个差分放大器,其差模增益为\( A_d = 10 \),共模增益为\( A_c = 0.1 \),求共模抑制比(CMRR)。

答案:共模抑制比(CMRR)可以通过差模增益与共模增益的比值来计算,即\( CMRR = A_d / A_c \)。

将给定的值代入公式,得到\( CMRR = 10 / 0.1 = 100 \)。

模拟的电路考试试题10套和问题详解(打印版)

坑爹的模电试卷编号 01 ………………………………………………………………………………………………………………一、填空(本题共20分,每空1分):1.整流电路的任务是__________;滤波电路的任务是__________。

2.在PN结的形成过程中,载流子的扩散运动是由于__________而产生的,漂移运动是__________作用下产生的。

3.放大器有两种不同性质的失真,分别是__________失真和__________失真。

4.在共射阻容耦合放大电路中,使低频区电压增益下降的主要原因是__________的影响;使高频区电压增益下降的主要原因是__________的影响。

5.在交流放大电路中,引入直流负反馈的作用是__________;引入交流负反馈的作用是___________。

6.正弦波振荡电路一般由__________、__________、__________、__________这四个部分组成。

7.某多级放大器中各级电压增益为:第一级25dB 、第二级15dB 、第三级60dB ,放大器的总增益为__________,总的放大倍数为__________。

8.在双端输入、单端输出的差动放大电路中,发射极公共电阻R e对__________信号的放大无影响,对__________信号的放大具有很强的抑制作用。

共模抑制比K CMR为__________之比。

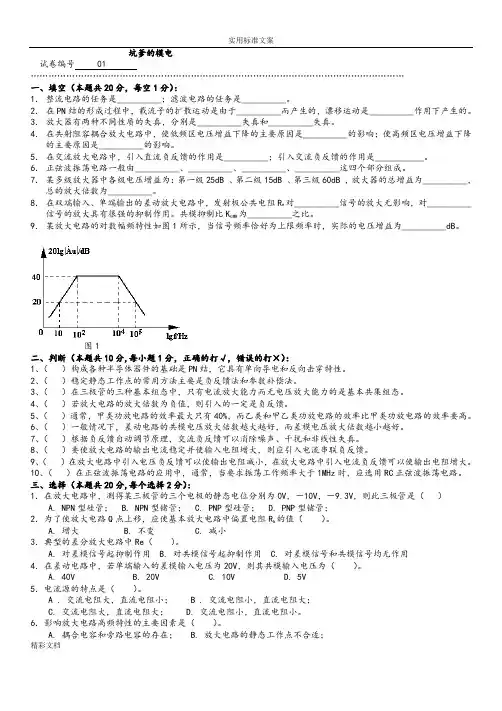

9.某放大电路的对数幅频特性如图1所示,当信号频率恰好为上限频率时,实际的电压增益为__________dB。

图1二、判断(本题共10分,每小题1分,正确的打√,错误的打×):1、()构成各种半导体器件的基础是PN结,它具有单向导电和反向击穿特性。

2、()稳定静态工作点的常用方法主要是负反馈法和参数补偿法。

3、()在三极管的三种基本组态中,只有电流放大能力而无电压放大能力的是基本共集组态。

4、()若放大电路的放大倍数为负值,则引入的一定是负反馈。

电路基础模拟考试题含参考答案

电路基础模拟考试题含参考答案一、单选题(共60题,每题1分,共60分)1、不允许把()以上的照明灯作为机床的局部照明中。

A、36VB、40VC、50VD、以上皆正确正确答案:A2、三极管各管脚的电流分配关系是()。

A、Ie=Ib+IcB、Ib=Ie+IcC、Ic=Ib+IeD、以上皆正确正确答案:A3、低电压单相触电、两相触电会造成()。

A、电击B、电伤C、无法确定D、以上皆正确正确答案:C4、周期和频率之间有()关系。

A、倒数B、乘数C、被除数D、以上皆正确正确答案:A5、通常()是一种严重事故,应尽力预防。

A、开路B、闭路C、回路D、短路正确答案:D6、“”的灯泡接入的电路中,通过灯丝的实际电流是()。

A、2;B、0.25。

C、0.5;D、1;正确答案:B7、电流的大小用电流强度来表示,其数值等于单位时间内穿过导体横截面的()代数和。

A、电量(电荷)B、电流强度C、功率D、电流正确答案:A8、一只电阻阻值为4Ω,另一只为8Ω,把两电阻串联起来,其电阻值为()。

A、4ΩB、12ΩC、9ΩD、以上皆正确正确答案:B9、要在220V交流电电路中接入一个电容器,其工作电压应取()。

A、220VB、25OVC、400VD、1000V正确答案:C10、单相桥式全波整流电路,使用个二极管()。

A、2B、6C、4D、以上皆正确正确答案:C11、万用表不能直接用来测量()。

A、电阻B、电流C、电功率D、电压正确答案:C12、周期T和频率f三者之间的关系正确的为()。

A、T=fB、T与f无关C、T=1/f正确答案:C13、交流电变化得越快,说明交流电的周期()。

A、无法判断B、越大C、越小正确答案:C14、相量只能表示交流电的有有效值(或最大值)和()。

A、初相位B、相位C、频率正确答案:A15、为了保证连接导线的机械高度,导线的截面积最小不低于()平方毫米。

A、1.0B、0.5C、2.0D、0.1正确答案:B16、并联电阻的等效电阻,它的倒数等于各支路电阻倒数()。

模拟电路笔试及面试问题

模拟电路1.基尔霍夫定理的内容是什么?(仕兰微电子)a.基尔霍夫电流定律:在电路的任一节点,流入、流出该节点电流的代数和为零b.基尔霍夫电压定律:在电路中的任一闭合电路,电压的代数和为零。

2.平板电容公式(C=εS/4πkd)。

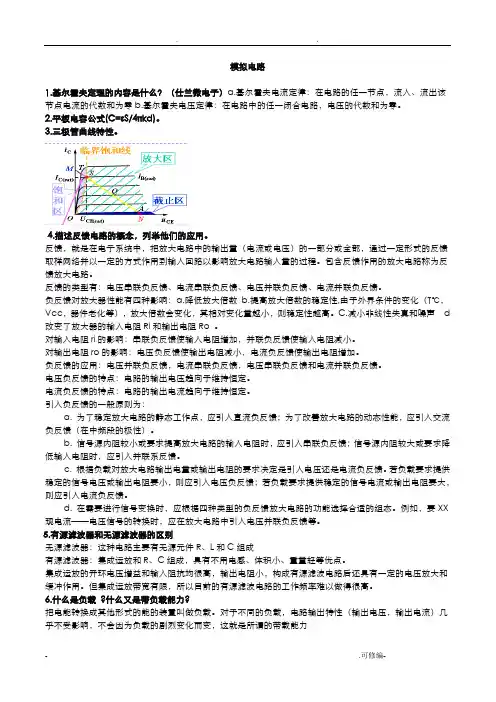

3.三极管曲线特性。

4.描述反馈电路的概念,列举他们的应用。

反馈,就是在电子系统中,把放大电路中的输出量(电流或电压)的一部分或全部,通过一定形式的反馈取样网络并以一定的方式作用到输入回路以影响放大电路输入量的过程。

包含反馈作用的放大电路称为反馈放大电路。

反馈的类型有:电压串联负反馈、电流串联负反馈、电压并联负反馈、电流并联负反馈。

负反馈对放大器性能有四种影响:a.降低放大倍数b.提高放大倍数的稳定性,由于外界条件的变化(T℃,Vcc,器件老化等),放大倍数会变化,其相对变化量越小,则稳定性越高。

C.减小非线性失真和噪声d 改变了放大器的输入电阻Ri和输出电阻Ro 。

对输入电阻ri的影响:串联负反馈使输入电阻增加,并联负反馈使输入电阻减小。

对输出电阻ro的影响:电压负反馈使输出电阻减小,电流负反馈使输出电阻增加。

负反馈的应用:电压并联负反馈,电流串联负反馈,电压串联负反馈和电流并联负反馈。

电压负反馈的特点:电路的输出电压趋向于维持恒定。

电流负反馈的特点:电路的输出电流趋向于维持恒定。

引入负反馈的一般原则为:a. 为了稳定放大电路的静态工作点,应引入直流负反馈;为了改善放大电路的动态性能,应引入交流负反馈(在中频段的极性)。

b. 信号源内阻较小或要求提高放大电路的输入电阻时,应引入串联负反馈;信号源内阻较大或要求降低输入电阻时,应引入并联系反馈。

c. 根据负载对放大电路输出电量或输出电阻的要求决定是引入电压还是电流负反馈。

若负载要求提供稳定的信号电压或输出电阻要小,则应引入电压负反馈;若负载要求提供稳定的信号电流或输出电阻要大,则应引入电流负反馈。

d. 在需要进行信号变换时,应根据四种类型的负反馈放大电路的功能选择合适的组态。

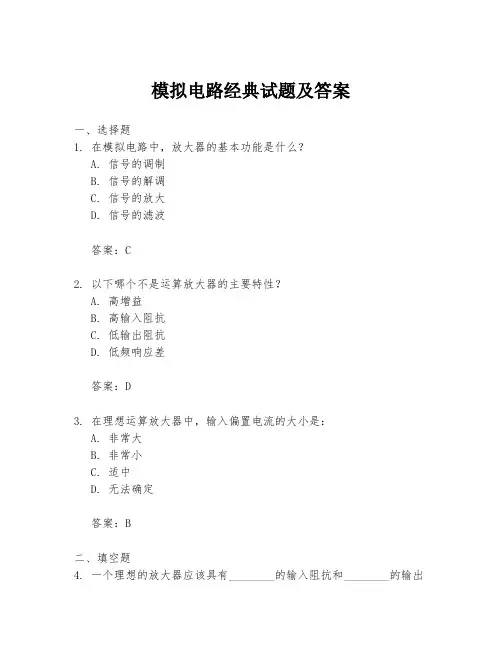

模拟电路经典试题及答案

模拟电路经典试题及答案一、选择题1. 在模拟电路中,放大器的基本功能是什么?A. 信号的调制B. 信号的解调C. 信号的放大D. 信号的滤波答案:C2. 以下哪个不是运算放大器的主要特性?A. 高增益B. 高输入阻抗C. 低输出阻抗D. 低频响应差答案:D3. 在理想运算放大器中,输入偏置电流的大小是:A. 非常大B. 非常小C. 适中D. 无法确定答案:B二、填空题4. 一个理想的放大器应该具有________的输入阻抗和________的输出阻抗。

答案:无穷大;零5. 在模拟电路设计中,________是用来减少噪声和干扰的一种电路。

答案:滤波器三、简答题6. 简述共射放大器的工作原理。

答案:共射放大器是一种使用NPN或PNP型晶体管构成的放大器,其特点是晶体管的发射极作为公共端接地,基极作为输入端,集电极作为输出端。

当基极电压增加时,晶体管导通程度增加,导致集电极电流增加,从而在集电极与电源之间形成电压变化,实现信号的放大。

四、计算题7. 假设有一个共射放大器,其晶体管的β值为100,基极电流为1mA,求集电极电流。

答案:由于基极电流为1mA,根据β值的定义,集电极电流Ic =β * Ib = 100 * 1mA = 100mA。

8. 如果在上述放大器中,集电极电阻Rc的值为1kΩ,求放大器的电压增益。

答案:电压增益Av = -Rc / (β * re),其中re为晶体管的内部电阻。

假设re为β / Ic,则Av = -1kΩ / (100 * (100 / 100mA)) = -1kΩ。

五、分析题9. 分析在模拟电路设计中,为何需要考虑频率响应。

答案:在模拟电路设计中,频率响应是一个重要的考虑因素,因为它决定了电路对不同频率信号的放大能力。

如果电路的频率响应不佳,可能会导致高频信号的损失或失真,影响信号的完整性和质量。

因此,设计时需要确保电路在整个工作频率范围内都能提供稳定的增益和相位特性。

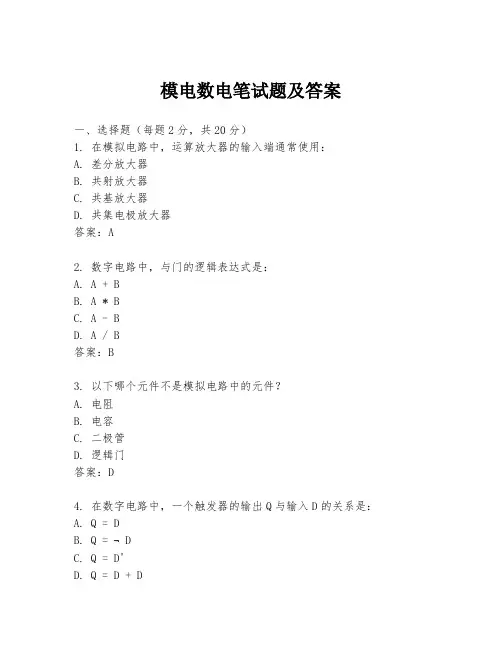

模电数电笔试题及答案

模电数电笔试题及答案一、选择题(每题2分,共20分)1. 在模拟电路中,运算放大器的输入端通常使用:A. 差分放大器B. 共射放大器C. 共基放大器D. 共集电极放大器答案:A2. 数字电路中,与门的逻辑表达式是:A. A + BB. A * BC. A - BD. A / B答案:B3. 以下哪个元件不是模拟电路中的元件?A. 电阻B. 电容C. 二极管D. 逻辑门答案:D4. 在数字电路中,一个触发器的输出Q与输入D的关系是:A. Q = DB. Q = ¬ DC. Q = D'D. Q = D + D5. 模拟电路中,放大器的增益通常用以下哪个参数表示?A. 电阻值B. 电容值C. 电压增益D. 电流增益答案:C6. 在数字电路中,一个D触发器的时钟输入端的信号是:A. 正脉冲B. 负脉冲C. 正弦波D. 锯齿波答案:A7. 模拟电路中,滤波器的作用是:A. 放大信号B. 衰减信号C. 过滤噪声D. 产生振荡答案:C8. 在数字电路中,一个计数器的输出Q0、Q1、Q2、Q3表示的是:A. 十进制数B. 二进制数C. 八进制数D. 十六进制数答案:B9. 模拟电路中,理想运算放大器的输入阻抗是:B. 无穷大C. 零D. 负值答案:B10. 数字电路中,一个寄存器的输出Q与输入D的关系是:A. Q = DB. Q = ¬ DC. Q = D'D. Q = D + D答案:A二、填空题(每题2分,共20分)1. 在模拟电路中,理想运算放大器的输出阻抗是______。

答案:零2. 数字电路中的逻辑门电路包括与门、或门、非门、______。

答案:异或门3. 在模拟电路中,电压跟随器的电压增益是______。

答案:14. 数字电路中,一个D触发器的时钟输入端的信号是______。

答案:正脉冲5. 模拟电路中,滤波器的截止频率是指______。

答案:通过频率6. 数字电路中,一个计数器的输出Q0、Q1、Q2、Q3表示的是______进制数。

模拟电路设计 基础知识(笔试时候容易遇到的题目)

模拟电路设计基础知识(笔试时候容易遇到的题目)1、最基本的如三极管曲线特性(太低极了点)2、基本放大电路,种类,优缺点,特别是广泛采用差分结构的原因3、反馈之类,如:负反馈的优点(带宽变大)4、频率响应,如:怎么才算是稳定的,如何改变频响曲线的几个方法5、锁相环电路组成,振荡器(比如用D触发器如何搭)6、A/D电路组成,工作原理如果公司做高频电子的,可能还要RF知识,调频,鉴频鉴相之类,不一一列举太底层的MOS管物理特性感觉一般不大会作为笔试面试题,因为全是微电子物理,公式推导太罗索,除非面试出题的是个老学究 ic设计的话需要熟悉的软件adence, Synopsys, Advant,UNIX当然也要大概会操作实际工作所需要的一些技术知识(面试容易问到)如电路的低功耗,稳定,高速如何做到,调运放,布版图注意的地方等等,一般会针对简历上你所写做过的东西具体问,肯定会问得很细(所以别把什么都写上,精通之类的词也别用太多了),这个东西各个人就不一样了,不好说什么了。

2、数字电路设计当然必问Verilog/VHDL,如设计计数器逻辑方面数字电路的卡诺图化简,时序(同步异步差异),触发器有几种(区别,优点),全加器等等比如:设计一个自动售货机系统,卖soda水的,只能投进三种硬币,要正确的找回钱数1、画出fsm(有限状态机)2、用verilog编程,语法要符合fpga设计的要求系统方面:如果简历上还说做过cpu之类,就会问到诸如cpu如何工作,流水线之类的问题3、单片机、DSP、FPGA、嵌入式方面(从没碰过,就大概知道几个名字胡扯几句,欢迎拍砖,也欢迎牛人帮忙补充)如单片机中断几个/类型,编中断程序注意什么问题 DSP的结构(冯、诺伊曼结构吗?)嵌入式处理器类型(如ARM),操作系统种类(Vxworks,ucos,winCE,linux),操作系统方面偏CS方向了,在CS篇里面讲了4、信号系统基础拉氏变换与Z变换公式等类似东西,随便翻翻书把如、h(n)=-a*h(n-1)+b*δ(n)a、求h(n)的z变换b、问该系统是否为稳定系统c、写出F IR数字滤波器的差分方程以往各种笔试题举例利用4选1实现F(x,y,z)=xz+yz 用mos管搭出一个二输入与非门。

模电笔试题及答案

模电笔试题及答案一、单项选择题(每题2分,共20分)1. 在模拟电路中,以下哪个元件不是基本的线性元件?A. 电阻B. 电容C. 电感D. 二极管答案:D2. 理想运算放大器的输入阻抗是:A. 有限值B. 零C. 无穷大D. 负值答案:C3. 以下哪种波形不是周期性波形?A. 正弦波B. 方波C. 锯齿波D. 随机噪声答案:D4. 放大器的增益是指:A. 输出电压与输入电压的比值B. 输出电流与输入电流的比值C. 输出功率与输入功率的比值D. 输入阻抗与输出阻抗的比值答案:A5. 理想二极管的正向导通电压为:A. 0VB. 0.7VC. 0.6VD. 1.5V答案:A6. 以下哪种器件不是模拟集成电路?A. 运算放大器B. 模拟开关C. 逻辑门D. 模拟多路复用器答案:C7. 在模拟电路中,信号的频率范围通常是指:A. 直流到几十兆赫兹B. 几十兆赫兹到吉赫兹C. 吉赫兹到太赫兹D. 太赫兹以上答案:A8. 以下哪种类型的放大器不能提供电压增益?A. 共射放大器B. 共基放大器C. 共集电极放大器D. 共源放大器答案:C9. 在模拟电路设计中,通常使用哪种类型的电容作为滤波电容?A. 陶瓷电容B. 电解电容C. 钽电容D. 所有选项答案:D10. 以下哪种元件不适用于模拟信号的整形?A. 运算放大器B. 逻辑门C. 比较器D. 晶体管答案:B二、填空题(每题2分,共10分)1. 在模拟电路中,信号的幅度、频率和_________是信号的三个基本参数。

答案:相位2. 模拟电路中,使用_______可以提高电路的输入阻抗。

答案:缓冲器3. 在模拟电路中,为了减少噪声干扰,通常采用_______技术。

答案:接地4. 模拟信号的频率响应是指在一定频率范围内,信号的_________保持不变的特性。

答案:幅度5. 在模拟电路中,为了实现信号的隔离,可以使用_________变压器。

答案:隔离三、简答题(每题5分,共20分)1. 简述运算放大器的虚短和虚断概念。

模拟电路考试题及答案

模拟电路考试题及答案一、单项选择题(每题3分,共30分)1. 在模拟电路中,放大器的基本功能是()。

A. 信号的整形B. 信号的放大C. 信号的滤波D. 信号的调制答案:B2. 理想运算放大器的输入电阻是()。

A. 有限值B. 零C. 无穷大D. 负无穷大答案:C3. 共发射极放大电路中,输出信号与输入信号的相位关系是()。

A. 同相B. 反相C. 无关系D. 随机答案:B4. 场效应管(FET)的控制方式是()。

A. 电压控制B. 电流控制C. 温度控制D. 光控制答案:A5. 在双极型晶体管(BJT)中,基极电流对集电极电流的影响是()。

A. 无关B. 线性C. 指数关系D. 反比关系答案:C6. 为了减少放大器的非线性失真,可以采用()。

A. 增加电源电压B. 增加输入信号C. 增加负反馈D. 减少输入信号答案:C7. 模拟电路中的噪声主要来源于()。

A. 电源B. 电阻C. 晶体管D. 所有选项答案:D8. 模拟电路中的带宽是指()。

A. 电路的最大工作频率B. 电路的最小工作频率C. 电路的频率响应范围D. 电路的电压增益答案:C9. 负反馈在放大器中的主要作用是()。

A. 增加增益B. 减少增益C. 增加稳定性D. 增加非线性失真答案:C10. 在模拟电路中,差分放大器的主要优点是()。

A. 提高共模抑制比B. 增加输入阻抗C. 减少输出阻抗D. 增加增益答案:A二、填空题(每题2分,共20分)11. 在共集电极放大电路中,输出电压与输入电压的关系是______。

12. 运算放大器的开环增益通常可以达到______以上。

答案:100000(或10^5)13. 场效应管的三个主要极是栅极、源极和______。

答案:漏极14. 双极型晶体管的三个主要极是发射极、基极和______。

答案:集电极15. 放大器的输入阻抗越高,对前级电路的______影响越小。

答案:负载16. 放大器的输出阻抗越低,对后级电路的______影响越小。

模拟电路考试题和答案

模拟电路考试题和答案第一部分:选择题1.运放放大电路的基本组成部分是: A. 正反馈网络、直流电源 B. 输入电阻、输出电阻 C. 输入电路、放大电路、输出电路 D. 比较器、反相器2.当仔细观察一个使用负反馈的运放电路时,可以发现输出电压始终在变化,这是因为: A. 负反馈增加了运放输入端的电压 B. 运放本身导致了基本反馈 C. 运放放大级没有理想的开环增益 D. 输入信号的变化引起运放放大电路的响应3.在理想运放中,输入端的电流为: A. 零 B. 正无穷大 C. 负无穷大 D. 任意值4.当使用运放作为比较器时,输出电压为: A. 输入端电压的比值 B. 输入端电压的积分 C. 输入端电压的差值 D. 输入端电压的平均值5.放大电路与比较电路的区别在于: A. 放大电路的输出是输入信号的放大 B. 比较电路的输出是两个输入信号的差值 C. 放大电路的输出是输入信号和反馈信号的加权和 D. 比较电路的输出是输入信号的积分第二部分:填空题1.当运放工作在不同的输入信号倍数时,输出电压也会按照输入信号倍数的 _______ 倍进行放大。

2.当电路有一个虚拟地点时,该点的电压等于 ___________。

3.在一个电流放大器中,如果输入电流为2mA,放大倍数为1000,则输出电流为 ___________。

4.当使用负反馈电路时,可以有效地降低电路输出的_______。

第三部分:解答题1.请解释什么是运放的本振?答:运放的本振是指输入端没有任何输入信号时,输出端产生的固定的偏移电压。

这个固定的偏移电压可以导致电路的不稳定性,并且会引入误差。

2.请描述运放的开环增益和闭环增益之间的关系。

答:运放的开环增益是指在没有任何反馈的情况下,运放输出端电压与输入端电压之间的比值。

闭环增益是指运放在负反馈条件下的输出电压与输入电压之间的比值。

闭环增益是通过在运放输入和输出之间添加反馈电路来控制的。

开环增益大,说明运放具有较大的放大能力,但同时也会引入较大的误差。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

模拟电路设计基础知识(笔试时候容易遇到的题目)1、最基本的如三极管曲线特性(太低极了点)2、基本放大电路,种类,优缺点,特别是广泛采用差分结构的原因3、反馈之类,如:负反馈的优点(带宽变大)4、频率响应,如:怎么才算是稳定的,如何改变频响曲线的几个方法5、锁相环电路组成,振荡器(比如用D触发器如何搭)6、A/D电路组成,工作原理如果公司做高频电子的,可能还要RF知识,调频,鉴频鉴相之类,不一一列举太底层的MOS管物理特性感觉一般不大会作为笔试面试题,因为全是微电子物理,公式推导太罗索,除非面试出题的是个老学究 ic设计的话需要熟悉的软件adence, Synopsys, Advant,UNIX当然也要大概会操作实际工作所需要的一些技术知识(面试容易问到)如电路的低功耗,稳定,高速如何做到,调运放,布版图注意的地方等等,一般会针对简历上你所写做过的东西具体问,肯定会问得很细(所以别把什么都写上,精通之类的词也别用太多了),这个东西各个人就不一样了,不好说什么了。

2、数字电路设计当然必问Verilog/VHDL,如设计计数器逻辑方面数字电路的卡诺图化简,时序(同步异步差异),触发器有几种(区别,优点),全加器等等比如:设计一个自动售货机系统,卖soda水的,只能投进三种硬币,要正确的找回钱数1、画出fsm(有限状态机)2、用verilog编程,语法要符合fpga设计的要求系统方面:如果简历上还说做过cpu之类,就会问到诸如cpu如何工作,流水线之类的问题3、单片机、DSP、FPGA、嵌入式方面(从没碰过,就大概知道几个名字胡扯几句,欢迎拍砖,也欢迎牛人帮忙补充)如单片机中断几个/类型,编中断程序注意什么问题 DSP的结构(冯、诺伊曼结构吗?)嵌入式处理器类型(如ARM),操作系统种类(Vxworks,ucos,winCE,linux),操作系统方面偏CS方向了,在CS篇里面讲了4、信号系统基础拉氏变换与Z变换公式等类似东西,随便翻翻书把如、h(n)=-a*h(n-1)+b*δ(n)a、求h(n)的z变换b、问该系统是否为稳定系统c、写出F IR数字滤波器的差分方程以往各种笔试题举例利用4选1实现F(x,y,z)=xz+yz 用mos管搭出一个二输入与非门。

用传输门和倒向器搭一个边沿触发器用运算放大器组成一个10倍的放大器微波电路的匹配电阻。

名词解释,无聊的外文缩写罢了,比如PCI、ECC、DDR、interrupt、pipeline IRQ,BIOS,USB,VHDL,VLSI VCO(压控振荡器)RAM (动态随机存储器),FIR IIR DFT(离散傅立叶变换)或者是中文的,比如 a量化误差 b、直方图 c、白平衡共同的注意点1、一般情况下,面试官主要根据你的简历提问,所以一定要对自己负责,把简历上的东西搞明白;2、个别招聘针对性特别强,就招目前他们确的方向的人,这种情况下,就要投其所好,尽量介绍其所关心的东西。

3、其实技术面试并不难,但是由于很多东西都忘掉了,才觉得有些难。

所以最好在面试前把该看的书看看。

4、虽然说技术面试是实力的较量与体现,但是不可否认,由于不用面试官/公司所专领域及爱好不同,也有面试也有很大的偶然性,需要冷静对待。

不能因为被拒,就否认自己或责骂公司。

5、面试时要take it easy,对越是自己钟情的公司越要这样。

1.集成电路设计前端流程及工具。

2。

FPGA和ASIC的概念,他们的区别3。

LATCH和DFF的概念和区别4。

用DFF实现二分频。

5。

用VERILOG或VHDL写一段代码,实现消除一个glitch6。

给一个表达式f=xxxx+xxxx+xxxxx+xxxx用最少数量的与非门实现(实际上就是化简)7。

用VERILOG或VHDL写一段代码,实现10进制计数器。

8。

给出一个门级的图,又给了各个门的传输延时,问关键路径是什么,还问给出输入,使得输出依赖于关键路径。

9。

A,B,C,D,E进行投票,多数服从少数,输出是F(也就是如果A,B,C,D,E中1的个数比0多,那么F输出为1,否则F为0),用与非门实现,输入数目没有限1、可参考各EDA厂商的开发工具2、 FPGA与ASIC的可参阅各种EDA相关书籍。

3、 LATC是H锁存器,DFF是触发器,其电路形式完全不同。

4、 always @(posedge clk)if (reset)begin sel <=1; clk1 <=1; clk2 <=1; end else begin sel <= ~sel; if (sel)clk1 <= ~clk1; else clk2 <= ~clk2; end5、 glitch主要发生在组合逻辑电路输出,可以加DFF输出稳定信号6,7,8,9:。

制。

2.负数与正数相乘的问题3.1010(-6)*0010(2)用补码相乘时应该进行相应的符号扩展,比如上面是4bit相乘,结果应该为8bit。

这样符号扩展后分别为和,然后再用这两个数直接相乘,结果为,取其低8位,作为-6*2的结果。

这也是个补码形式,再判断一下高位恢复为原码,得到结果。

以前讨论过相关问题,可以翻出来看看检测信号的上升沿LIBRARY ieee; USE ieee、std_logic_1164、all; ENTITY sync IS PORT(clk: IN STD_LOGIC; rst: IN STD_LOGIC; sync_in: IN STD_LOGIC; sync_out: OUTSTD_LOGIC); END sync; ARCHITECTURE arch OF sync IS SIGNAL sync_int1, sync_int2: STD_LOGIC; BEGIN------------------------------------------------------- PROCESS(clk, rst, sync_in)BEGIN IF rst=0 THEN sync_out<=0; ELSIFrising_edge(clk)THEN sync_int1<=sync_in; sync_int2<=sync_int1; IF (sync_int1=1 AND sync_int2=0)THEN sync_out<=1; ELSE sync_out<=0; END IF; END IF; END PROCESS; END arch; 并入串出? library IEEE; use IEEE、STD_LOGIC_1164、ALL; use IEEE、STD_LOGIC_ARITH、ALL; use IEEE、STD_LOGIC_UNSIGNED、ALL; entity piso is port( datain :instd_logic_vector(39 downto 0); clk : in std_logic; nLoad:in std_logic; data_out: out std_logic); end piso; architecture Behavioral of piso is signal q:std_logic_vector(39 downto 0); begin process (nLoad,clk)begin if nLoad= 0 then q<=datain; elsif clkevent and clk=1 then q(1)<=q(0); for i in1 to39 loop q(i)<=q(i-1); end loop; end if; end process; process (nLoad,clk) begin if nLoad=0 then data_out<=0; elsif clkevent and clk=1 then data_out <=q(39); end if; end process; end Behavioral; 把所有的39改成15就可以了有一些基本概念我可能还不太清楚,说错的地方,请大家批评指教。

我要设计的是is-95cdma系统的48阶fir滤波器。

输入串行数据(每个clk输入1位)输入数据宽度为1位,系数h[0]=-0、(进制)=_(16位二进制,_为小数点位置,_前面是符号扩展),-h[0]=+0、(进制)_(16位二进制)。

其他系数略。

我用的是映射的方法,即不用乘法,只对应由查找表查出的结果,输入1时,映射为+1,查表输出h[0],输入0时,映射为-1,查表输出-h[0]。

再送入加法器求48个系数的和。

系数宽度16位,输出宽度22位(防溢出)datain=1 ,dataout=16116a(六进制)=(22位二进制)这是48个正系数的和(这里的正系数不一定全是正数,而只是标准,所以把它看作“正数”) datain=0 ,dataout=19ee96(六进制)=(22位二进制)这是48个负系数的和。

这个结果我对照进制的数运算结果验证了一下,是对的,但是只能取22位的后16位来计算,因为高位的都是加法的进位溢出。

我主要由两个问题:1)这种映射法,恕我愚钝,根本没明白(我也是看的论文,但没有明白其真正含义),因为它和普通的比如m位输入和n位的系数相乘得到m+n位的结果,思路完全不一样。

这个1,0映射为+1,-1,和普通的输入(m位二进制数代表一个x(n))有何关系?我的到16116a,19ee96这些结果还要累加吗?(此问题可能比较愚蠢,欢迎扔鸡蛋)2)我运算的是有符号数,那溢出的这些多出的位怎么处理?因为下一步这些数据还要送到下一个模块处理。

保留的话,多出的哪些位显然没用。

扔掉的话,行吗?学了FOR LOOP的用法以后,有点想法那么在此基础上怎么实现并口的输出呢? 如: Q(0)<=DIN; FOR I IN1 DOWNTO7 LOOPQ(I)<=Q(I-1); END LOOP; OP<=Q; OP 定义为STD_LOGIC_vector(7 downto 0)我总感觉每次触发输出的都是在Q(7)口,而且该值就是DIN在8个周期前的值那么要是想实现DIN8个连续数据的同时输出,应该怎么做? 感觉每次触发输出的都是在Q(7)口这句话不是很明白。

反正这样的转换很快的,只要有触发,马上可以完成分析如下: q(0)->q(1),然后q(1)->q(2),然后q(2)->q(3)、、、、、、、、q(6)->q(7)实际上只是延迟了几个周期,也就是q(7)<=din, 并没有实现串行向并行的转换不大理解用这个for loop语句如何实现串并转换的望告知把 Q(0)<=DIN; FOR I IN1 DOWNTO7 LOOPQ(I)<=Q(I-1); END LOOP; 放在进程里面就可以。