ISE 14.7教程

ISE教程

光盘放进DVD光驱,等待其自动运行(如果没有自动运行,直接执行光盘目录下的Setup.exe文件程序即可),会弹出图4-1所示的欢迎界面,点击“Next”进入下一页。

图4-1 ISE安装过程的欢迎界面2.接着进入注册码获取、输入对话框,如图4-2所示。

注册码可以通过网站、邮件和传真方式申请注册码。

如果已有注册码,输入后单击“Next”按键后继续。

图4-2 ISE9.1安装程序的注册码输入界面购买了正版软件后,最常用的方法就是通过网站注册获取安装所需的注册码。

首先在Xilinx的官方主页上建立自己的帐号,然后点击图4-1中的“Website”按键,登陆帐号,输入CD盒上的产品序列号(序号的格式为:3个字符+9个数字),会自动生成16位的注册码,直接记录下来即可,同时Xilinx网站会将注册码的详细信息发送到帐号所对应的邮箱中。

3.下一个对话框是Xilinx软件的授权声明对话框,选中“I accept the terms of this software license”,单击“Next”后进入安装路径选择界面,如图4-3所示。

单击“Browse”按键后选择自定义安装路径,单击“Next”按键继续图4-3 ISE软件安装路径选择对话框4.接下来的几个对话框分别是选择安装组件选择,如图4-4所示,用户需要选择自己使用的芯片所对应的模块,这样才能在开发中使用这些模块。

在计算机硬盘资源不紧张的情况下,通常选择“Select All”。

图4-4 ISE安装组件选择界面评论[支持者: 0 人,反对者: 0 人,中立者: 0 人] 查看评论信息2008-11-26 20:53:00第3楼小大个性首页| QQ5.随后进入设置环境变量页面,保持默认即可。

如果环境变量设置错误,则安装后不能正常启动ISE。

选择默认选项,安装完成后的环境变量,其值为安装路径。

最后进入安装确认对话框,单击Install按钮,即可按照用户的设置自动安装ISE,如图4-5所示图4-5 ISE安装进程示意图6.安装完成后,会在桌面以及程序菜单中添加Project Navigator的快捷方式。

ISE14.7下创建一个Microblaze软核的流水灯和串口输出程序

ISE14.7下创建一个Microblaze软核的流水灯和串口输出程序使用硬件平台Xilinx Spartan6系列的FPGA,开发环境为ISE14.7。

废话少说,直接上图创建一个ISE工程,工程名字为UART_LED_TEST。

点击完成,完成工程的创建。

往工程中添加MICROBLAZE IP核

工程创建完成图。

点击完成后进入XPS,然后开始创建核

选择PLB system,我也不知道为什么?

按向导点击下一步。

给microblaze添加UART核

波特率可以根据自己情况修改,下面添加LED跑马灯

导出刚才创建的软核平台。

选择Export Only,仅仅只导出平台。

Console中显示Done!说明软核平台导出完成。

右键点击SYS_CPU,选择Add Copyof Source,添加约束文件。

选择SYS_CPU,双击GenerateTop HDL Source,创建顶层模块文件。

创建完成后,如下图。

双击Export Hardware Design To SDK With bitstream,编译刚才创建的软核平台。

此过程大约需要十几分钟。

编译完成后弹出如下对话框,选择SDK的工作目录。

创建一个SDK_Workspace文件夹,并选择该文件夹为SDK 的工作目录。

进入SDK主界面。

创建工程完成后的SDK界面图。

将FPGA上电,并接上USB下载线。

点击下图中标记的图标。

打完收功!。

ISE_Design_Flow_14.7

ISE_Design_Flow_14.7ISE设计流程指导⼿册——14.7在本⼿册中,我们将以⼀个简单的实验案例,⼀步⼀步的完成ISE的整个设计流程。

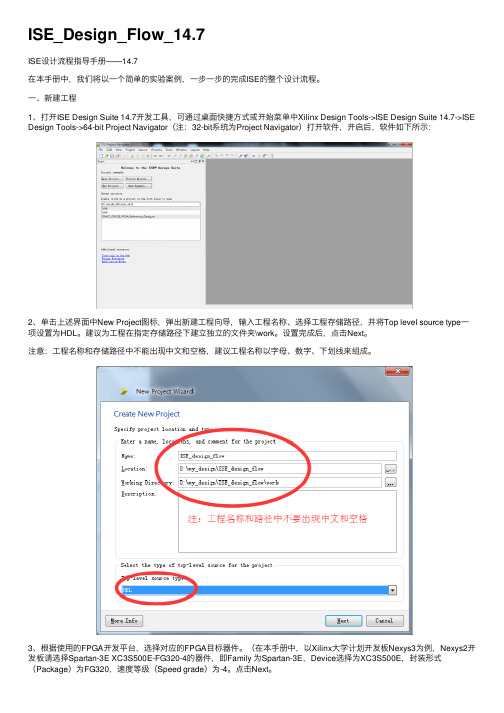

⼀、新建⼯程1、打开ISE Design Suite 14.7开发⼯具,可通过桌⾯快捷⽅式或开始菜单中Xilinx Design Tools->ISE Design Suite 14.7->ISE Design Tools->64-bit Project Navigator(注:32-bit系统为Project Navigator)打开软件,开启后,软件如下所⽰:2、单击上述界⾯中New Project图标,弹出新建⼯程向导,输⼊⼯程名称、选择⼯程存储路径,并将Top level source type⼀项设置为HDL。

建议为⼯程在指定存储路径下建⽴独⽴的⽂件夹\work。

设置完成后,点击Next。

注意:⼯程名称和存储路径中不能出现中⽂和空格,建议⼯程名称以字母、数字、下划线来组成。

3、根据使⽤的FPGA开发平台,选择对应的FPGA⽬标器件。

(在本⼿册中,以Xilinx⼤学计划开发板Nexys3为例,Nexys2开发板请选择Spartan-3E XC3S500E-FG320-4的器件,即Family 为Spartan-3E,Device选择为XC3S500E,封装形式(Package)为FG320,速度等级(Speed grade)为-4。

点击Next。

4、确认相关信息与设计所⽤的的FPGA器件信息是否⼀致,⼀致请点击Finish,不⼀致,请修改。

5、得到如下的空⽩ISE⼯程界⾯,完成空⽩⼯程新建。

⼆、设计⽂件输⼊1、如下图所⽰,点击New Source快捷图标,或在空⽩处右击选择New Source,或在File->NewSource选项,打开设计⽂件添加向导对话框。

2、选择Verilog Module,并输⼊设计⽂件名称如图所⽰,点击Next。

ISE使用教程(修改稿)

点击project菜单的New Source

设计输入

• 要完成这个计数器模块,可以在ISE自动生成的代 码框架基础上通过自己编写代码完成,也可使用 ISE的语言模板(ISE Language Template)工具 来完成。 • 选择Edit->Language Template或者通过点击工 具栏中最右端的灯泡按钮 来打开语言模板。 在语言模版(Language Template )窗口中,有 很多Xilinx提供的参考代码片断,找到需要的 counter代码片断。

保存后进行功能仿真

仿真结果

下载验证

在生成可用于下载的Bit流文件前,必须生成ucf约 束文件,否则生成的bit流文件将无法在硬件上正 常运行。 约束文件中可包含:时序约束,周期约束,偏移 约束,管脚约束等。其中管脚约束是必不可少的, 它将你设计文件中的I/O与实际硬件管脚进行关联。 管脚约束可调用ISE的PASE工具实现。 最后使用ISE IMPACT工具通过JTAG口下载bit流 至硬件。

管脚约束源文件的建立

管脚约束文件的建立

3.在此编辑窗口进行管脚约束编写 例如:net "ckout(3)" loc="k12"; net "ckout(2)" loc="p14"; net "ckout(1)" loc="l12"; net "ckout(0)" loc="n14"; net "clk" loc= "t9" ; net"direction" loc = "f12";

1.选中

2.双击 编写完成后保存

ISE使用教程(修改稿)

点击project菜单的New Source

设计输入

• 要完成这个计数器模块,可以在ISE自动生成的代 码框架基础上通过自己编写代码完成,也可使用 ISE的语言模板(ISE Language Template)工具 来完成。 • 选择Edit->Language Template或者通过点击工 具栏中最右端的灯泡按钮 来打开语言模板。 在语言模版(Language Template )窗口中,有 很多Xilinx提供的参考代码片断,找到需要的 counter代码片断。

4、为元件添加连线(add the wire )

注意:在元件端口拉出一小段线段为以后添加网线名称并 设置I/O管教做准备,否则可能添加不上 5、添加网线名(add the branch) 6、设置I/O管理 7、生成器件符号

8、调用项目生成的器件符号,进行系统设计 9、绘制总线 10、检查

谢谢大家!

ISE软件概述

ISE系列软件特点综述

• Xilinx作为当今世界上最大的FPGA/CPLD生产 商之一,长期以来一直推动着FPGA/CPLD技 术的发展。其开发的软件也不断升级换代,由 早期的Foundation系列逐步发展到目前的 ISE10.x系列。 • ISE是集成综合环境(Integrated Software Environment)的简称,是Xilinx提供的一套工 具集,其集成的工具可以完成FPGA/CPLD从 源码输入、仿真、综合到下板调试的整个开发 过程。

几点需要注意的地方

• 用 ModelSim 进行仿真,包括 行为仿真亦 即功能仿真和布局布线后的仿真亦即时序 仿真(详细可以去参考ModelSim教程)

用ISE自带的仿真工具仿真

• ISE仿真工具设置

【设计经验】3、ISE中烧录QSPIFlash以及配置mcs文件的加载速度与传输位宽

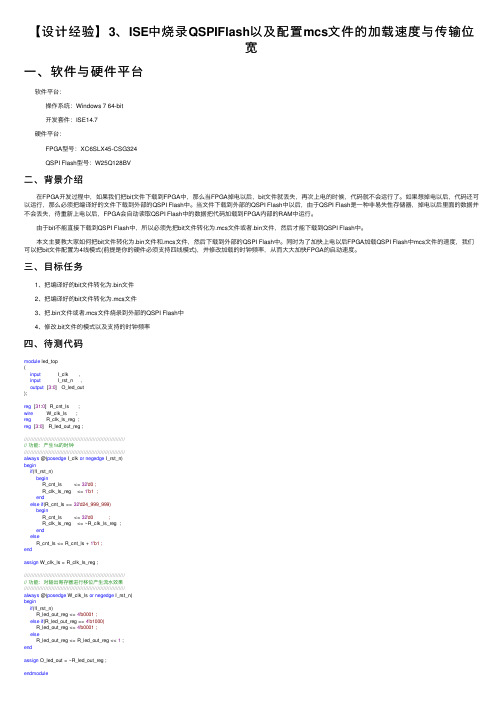

【设计经验】3、ISE中烧录QSPIFlash以及配置mcs⽂件的加载速度与传输位宽⼀、软件与硬件平台软件平台:操作系统:Windows 7 64-bit开发套件:ISE14.7硬件平台:FPGA型号:XC6SLX45-CSG324QSPI Flash型号:W25Q128BV⼆、背景介绍 在FPGA开发过程中,如果我们把bit⽂件下载到FPGA中,那么当FPGA掉电以后,bit⽂件就丢失,再次上电的时候,代码就不会运⾏了。

如果想掉电以后,代码还可以运⾏,那么必须把编译好的⽂件下载到外部的QSPI Flash中。

当⽂件下载到外部的QSPI Flash中以后,由于QSPI Flash是⼀种⾮易失性存储器,掉电以后⾥⾯的数据并不会丢失,待重新上电以后,FPGA会⾃动读取QSPI Flash中的数据把代码加载到FPGA内部的RAM中运⾏。

由于bit不能直接下载到QSPI Flash中,所以必须先把bit⽂件转化为.mcs⽂件或者.bin⽂件,然后才能下载到QSPI Flash中。

本⽂主要教⼤家如何把bit⽂件转化为.bin⽂件和.mcs⽂件,然后下载到外部的QSPI Flash中。

同时为了加快上电以后FPGA加载QSPI Flash中mcs⽂件的速度,我们可以把bit⽂件配置为4线模式(前提是你的硬件必须⽀持四线模式),并修改加载的时钟频率,从⽽⼤⼤加快FPGA的启动速度。

三、⽬标任务1、把编译好的bit⽂件转化为.bin⽂件2、把编译好的bit⽂件转化为.mcs⽂件3、把.bin⽂件或者.mcs⽂件烧录到外部的QSPI Flash中4、修改.bit⽂件的模式以及⽀持的时钟频率四、待测代码module led_top(input I_clk ,input I_rst_n ,output [3:0] O_led_out);reg [31:0] R_cnt_ls ;wire W_clk_ls ;reg R_clk_ls_reg ;reg [3:0] R_led_out_reg ;//////////////////////////////////////////////////////////////////// 功能:产⽣1s的时钟//////////////////////////////////////////////////////////////////always @(posedge I_clk or negedge I_rst_n)beginif(!I_rst_n)beginR_cnt_ls <= 32'd0 ;R_clk_ls_reg <= 1'b1 ;endelse if(R_cnt_ls == 32'd24_999_999)beginR_cnt_ls <= 32'd0 ;R_clk_ls_reg <= ~R_clk_ls_reg ;endelseR_cnt_ls <= R_cnt_ls + 1'b1 ;endassign W_clk_ls = R_clk_ls_reg ;//////////////////////////////////////////////////////////////////// 功能:对输出寄存器进⾏移位产⽣流⽔效果//////////////////////////////////////////////////////////////////always @(posedge W_clk_ls or negedge I_rst_n)beginif(!I_rst_n)R_led_out_reg <= 4'b0001 ;else if(R_led_out_reg == 4'b1000)R_led_out_reg <= 4'b0001 ;elseR_led_out_reg <= R_led_out_reg << 1 ;endassign O_led_out = ~R_led_out_reg ;endmodule 写好待测代码,并添加物理约束⽂件绑定好管脚,我的开发板上的约束⽂件如下NET I_clk LOC = V10 | TNM_NET = sys_clk_pin | IOSTANDARD = "LVCMOS33";TIMESPEC TS_sys_clk_pin = PERIOD sys_clk_pin 50000 kHz;NET I_rst_n LOC = N4 | IOSTANDARD = "LVCMOS15"; ## SW2 pushbuttonNET O_led_out<0> LOC = V5 | IOSTANDARD = "LVCMOS33"; ## LED1NET O_led_out<1> LOC = R3 | IOSTANDARD = "LVCMOS33"; ## LED2NET O_led_out<2> LOC = T3 | IOSTANDARD = "LVCMOS33"; ## LED3NET O_led_out<3> LOC = T4 | IOSTANDARD = "LVCMOS33"; ## LED4五、任务⼀、把.bit⽂件转化为.bin⽂件。

i se 14.7安装教程

i se 14.7安装教程安装前准备断开网络链接。

关闭PC的防护软件。

安装过程说明1.安装包文件说明。

不同的人的安装包文件可能有一定的区别,但大体上差不多。

双击应用程序setup。

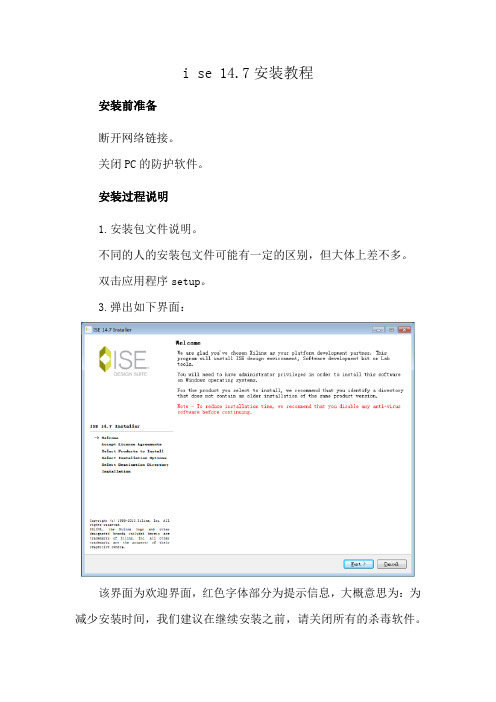

3.弹出如下界面:该界面为欢迎界面,红色字体部分为提示信息,大概意思为:为减少安装时间,我们建议在继续安装之前,请关闭所有的杀毒软件。

由于有些杀毒软件会误删系统文件,所以我们在安装时可以先把杀毒软件退出然后再安装,避免不必要的麻烦。

在一切准备就绪之后,点击下一步。

4.该界面显示的是软件的许可协议,总共两项,全部接受即可。

5.这个界面是选择需要安装的内容,大家安装时,选择自己需要的进行安装,这里勾选了ISE Design Suite System Edition。

在下面的详细介绍中,我们可以知道,这个选项中包含了ISE的逻辑编辑器,还有EDK和System Generator For DSP。

6.选择安装设置。

①第一个选项:使用多个CPU内核来加速安装速度②第二个选项:获取或管理许可证密钥。

③第三个选项:为以太网硬件协同仿真安装WinPCap。

④第四个选项:安装驱动。

⑤第五个选项:启用webtalk发软硬件的IP和设备使用情况,统计到XILINX。

这五项内容,大家根据自己需要进行勾选,这里我进行了全部选择。

7.选择安装路径。

在选择安装路径的时候,系统默认是安装在C 盘。

但是建议大家不要装在C盘,避免电脑卡顿。

如果大家要安装到其他盘。

只需要将C改为你想安装的盘即可,后面的路径不需要修改。

另外,安装时一定要确保安装路径里面没有中文。

8.这个界面显示了我们要安装的内容,直接点击INSTALL。

9.进入安装界面,等待安装即可。

10.点击NEXT。

11.继续点击Install。

12.界面提示,安装完成,点击Finish。

13.点击NEXT。

14.点击NEXT。

15.点击Finish。

16.安装WinPcap。

点击NEXT。

17.引导界面,点击NEXT。

ISE 14.7教程

Xilinx ISE Design Suite14.7开发流程

1、打开ISE Design Suite14.7

2、新建项目 File--New Project(一般新建一个文件夹来保存项目)

3、选择设备平台(我这里是basys2开发板的,所以我根据这款板子选择配置)

4、项目总览

5、项目创建完成

6、新建源文件

选择Verilog Module 填入File Name 然后next

端口可设置可不设置(这里我先设置了)

文件总览

7、编写硬件代码

8、编译文件,编译通过后可以查看RTl视图,或者添加ucf约束文件,也可以做仿真(参考ISim仿真)

9、添加ucf约束文件,跟建院文件一样,不过这里选择IMplementation Constraints File ,填写File name ,然后next,接着finish

10、编写约束文件

10、再次编译

11、配置目标设备

12、下载到板子上

边缘扫描

初始设备(有的同学可能扫描不到设备,这可能是驱动没装好)

选择文件

选完之后不选SPi or BPI PROM 选 no(一般测试不选,如果要固化就可以选择)

确定一下文件是否选对了

烧录在第一颗芯片右键,然后点Program

烧录成功

13、观察板子现象(如果不正常,可查一下自己的代码有没有问题或者ucf约束文件有没有绑定好,如果没问题,在重新编译一次)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Xilinx ISE Design Suite14.7开发流程

1、打开ISE Design Suite14.7

2、新建项目 File--New Project(一般新建一个文件夹来保存项目)

3、选择设备平台(我这里是basys2开发板的,所以我根据这款板子选择配置)

5、项目创建完成

选择Verilog Module 填入File Name 然后next

端口可设置可不设置(这里我先设置了)

文件总览

7、编写硬件代码

8、编译文件,编译通过后可以查看RTl视图,或者添加ucf约束文件,也可以做仿真(参考ISim仿真)

9、添加ucf约束文件,跟建院文件一样,不过这里选择IMplementation Constraints File ,填写File name ,然后next,接着finish

10、编写约束文件

10、再次编译

11、配置目标设备

12、下载到板子上边缘扫描

初始设备(有的同学可能扫描不到设备,这可能是驱动没装好)

选择文件

选完之后不选SPi or BPI PROM 选 no(一般测试不选,如果要固化就可以选择)

确定一下文件是否选对了

烧录在第一颗芯片右键,然后点Program

烧录成功

13、观察板子现象(如果不正常,可查一下自己的代码有没有问题或者ucf约束文件有没有绑定好,如果没问题,在重新编译一次)。