电子琴实验报告(基于乐曲《梁祝》)

简易电子琴实验报告

简易电子琴实验报告引言:本实验旨在设计和制作一台基于微控制器的简易电子琴,通过按下不同键盘上的按键产生不同音调,从而实现音乐的演奏。

电子琴采用的主要器件为微控制器、音频发声模块以及按键电路。

一、实验目的1.学习和理解数字音乐技术的基本原理;2.掌握微控制器的编程方法和音频发声的实现技术;3.熟悉电子琴的工作原理和设计过程。

二、实验器材1. 单片机:Arduino Uno;2.音频发声模块;3.面包板;4.按键;5.电阻、电容等元件;6.连线和连接器。

三、实验步骤1. 将Arduino Uno连接至音频发声模块,确保连接正确并稳定。

2.在面包板上连接按键电路,将按键与单片机的引脚相连。

3. 编写Arduino Uno的程序,实现按键按下时的音调发声。

4.上电,并测试按键是否能够产生正确的音调。

四、实验结果经过实验得到的结果如下:1.按下不同按键,电子琴会产生不同的音调。

2.通过改变程序中相应按键的频率值,可以调整音调的高低。

五、实验分析1.通过对单片机的编程,实现了按键按下时的音调发声,成功地实现了电子琴的基本功能。

2.实验中使用了音频发声模块,利用其内置的DAC(数字模拟转换器)实现了数字音频信号的模拟输出。

六、实验总结和心得体会通过本次实验,我对电子琴的工作原理和设计过程有了更深入的了解。

学习和掌握了单片机的编程方法和音频发声的实现技术,提高了我的实验能力和动手能力。

同时,也对数字音乐技术有了初步的认识。

在今后的学习和工作中,我将继续深入研究和应用这些知识,为电子音乐的发展做出自己的贡献。

EDA硬件乐曲演奏电路设计梁祝两只老虎

编号:EDA综合设计实验报告课题:硬件乐曲演奏电路设计专业:智能科学与技术学生姓名:黎良贵学号: 12008502112014 年11 月30 日一、概述:硬件乐曲演奏电路顶层模块图如图1-1所示,电路图由11个子模块组成,能够实现:(1)梁祝乐曲的自动演奏;(2)键盘弹奏歌曲;(3)ROM中能存两首歌曲,并能手动选歌。

二、实验原理:①音符的频率可以由图1-1中的SPKER获得。

这是一个数控分频器。

由其CLK端输入一具有较高频率(1MHz)的时钟,通过SPKER分频后,经由D触发器构成的分频电路,由SPK_KX口输出。

由于直接从分频器中出来的输出信号是脉宽极窄的信号,为了有利于驱动扬声器,需另加一个D触发器分频以均衡其占空比,但这时的频率将是原来的1/2。

SPKER对CLK输入信号的分频比由输入的11位预置数TN[10..0]决定。

SPK_KX的输出频率将决定每一音符的音调;这样,分频计数器的预置值TN[10..0] 与输出频率就有了对应关系,而输出的频率又与音乐音符的发声有对应关系,例如在F_CODE模块中若取TN[10..0]=11'H40C,将由SPK_KX发出音符为“3”音的信号频率。

②音符的持续时间需根据乐曲的速度及每个音符的节拍数来确定,图1-1中模块F_CODE的功能首先是为模块SPKER(11位分频器)提供决定所发音符的分频预置数,而此数在SPKER输入口停留的时间即为此音符的节拍周期。

模块F_CODE是乐曲简谱码对应的分频预置数查表电路,每一音符的停留时间则由音乐节拍和音调发生查表模块MUSIC中简谱码和工作时钟inclock的频率决定,在此为4Hz。

这4Hz频率来自分频模块FDIV,模块MUSIC是一个LPM_ROM。

它的输入频率来自锁相环PLL20的2kHz输出频率。

而模块F_CODE的14个值的输出由对应于MUSIC模块输出的q[3..0]及4位输入值INX[3..0]确定,而INX[3..0]最多有16种可选值。

梁祝电子琴和弦伴奏指法教学

梁祝电子琴和弦伴奏指法教学

梁祝是古典音乐的重要作品之一,也是中国音乐中最有代表性的民歌之一。

它的音乐特色使其成为电子琴演奏的经典曲目。

学习梁祝的琴谱,可以让演奏者体会到一种浓郁的中国传统文化气息,更可以学习到丰富的技巧和知识。

学习梁祝电子琴和弦伴奏指法,从最基本的指法开始,首先学习五线谱,然后进行乐曲的弹奏。

学习它拥有多义的和弦,比如半音阶,十二音阶,就近等,可以增强演奏的丰富性。

在学习弹奏技巧的同时,还应当多学习基本的琴技,比如加节奏、加音色等等的技巧,这些技巧可以使演奏更加丰富多彩。

此外,在学习梁祝电子琴和弦伴奏指法时,还应当注意演奏时使用的琴键及按键,准确掌握它们,能够更快更准确地演奏出梁祝。

在练习梁祝的琴谱时,也可以尝试改编不同的弹奏技巧,学习琴谱中的弦乐伴奏,以及如何灵活地使用不同的和弦来弹奏。

另外,梁祝的演奏不仅要讲究和弦的准确和技术,同时也要多考虑情感表现,让一首梁祝不再是一首乐曲,而是一种精神和情感上的艺术,打动每个人的心。

综上所述,梁祝电子琴和弦伴奏指法是一种传统和现代结合的音乐手法,它不仅仅提高了演奏者技术水平,更丰富了音乐表现力,让每个人都能从中体验到精彩的音乐。

- 1 -。

数字电子技术综合实验报告——简易电子琴

数字电子技术综合实验报告2012--2013学年第二学期姓名:学号:班级:实验时间:实验指导老师:目录一、设计任务 (2)二、设计方案 (2)三、系统框图 (3)四、方案实现 (3)1.乐曲演奏的原理 (3)2.总体方案 (4)五、实验结果 (6)六、方案优化 (7)七、心得体会 (7)附录 (7)1.VHDL源程序 (7)2.各层次原理图 (35)3.编译报告 (40)1题目: 简易电子琴设计摘要电子琴的设计大规模可编程逻辑器件(FPGA )作为系统的核心控制部分通过软件的设计编写然后进行软硬件的调试运行最终达到设计电路的乐器演奏、选歌及显示功能。

设计中采用计数原理控制演奏器发声,对音乐发生所必须确定的音符和节拍分别用程序语言实现。

可以用它来弹奏和播放乐曲。

特点是设计思路简单、清晰。

关键字:电子琴 CPLD一、设计任务1.基本要求(1)具有一般弹奏功能;(2)自动播放功能;(3)数码显示音符功能。

2.发挥部分(1)能通过选择键在多首歌曲中选择播放;(2)输出增加功率放大电路,增加歌曲容量;(3)增加音效或节拍可调;(4)无线弹奏。

二、设计方案采用大规模可编程逻辑器件(FPGA),利用quartusII,通过verilog代码实现简易电子琴演奏电路。

2三、系统框图四、方案实现1.乐曲演奏的原理:乐曲演奏的原理:组成乐曲的每个音符的频率值(音调)以及持续时间(音长)是乐曲能持续演奏所需的两个基本数据,因此只要控制输出到扬声器的激励信号的频率的高低和持续的时间,就可以使扬声器发出持续的乐曲声。

音调的控制频率的高低决定了音调的高低。

音乐的十二平均率规定:每两个八度音(如简谱中的中音1与高音1)之间的频率相差一倍。

在两个八度音之间,又可分为十二个半音,每半个音的频率比为。

另外,音名A(简谱中的低音6)的频率为440HZ,音名B到C之间,E到F之间为半音,其余为全音。

由此可以计算出简谱中从低音1至高音1之间的每个音名对应的频率如图所示:3所有不同频率均从同一基准频率分频得到。

电子琴实习报告

电子琴实习报告篇一:电子琴设计实习报告单片机原理与应用技术课程设计报告基于单片机的电子琴控制系统专业班级:* 姓名:*时间:~指导教师:*XX年 1月 10日基于单片机的电子琴控制系统课程设计任务书1.设计目的与要求设计出一个基于单片机的电子琴控制系统。

准确地理解有关要求,独立完成系统设计,要求所设计的电路具有以下功能:(1)实现基本的音符1-7的弹奏和数码显示。

(2)自动弹奏播放一首简单的歌曲。

(3)随机弹奏曲子时,可以实时记忆,并可复读(重复播放)。

(扩展功能,可选择设计)2.设计内容(1)画出电路原理图,正确使用逻辑关系;(2)确定元器件及元件参数;(3)进行电路模拟仿真;(4)SCH 文件生成与打印输出。

3.编写设计报告写出设计的全过程,附上有关资料和图纸,有心得体会。

4.答辩在规定时间内,完成叙述并回答问题。

基于单片机的电子琴控制系统班级:* 姓名:*摘要:电子琴是现代电子科技与音乐结合的产物,是一种新型的键盘乐器,采用半导体集成电路,对乐音信号进行放大,通过扬声器产生音响。

用户可以自己弹奏乐曲,也可以自动伴奏。

单片机具有强大的控制功能和灵活的编程实现特性,便于设计各种以单片机为核心的控制系统。

本课程设计是用AT89S51单片机为核心控制元件,用其他外围电路配合单片机组成一个简单的电子琴控制系统,能实现音乐弹奏,自动播放音乐等功能。

本系统功能由单片机控制实现,具有运行稳定,电路简单,软件功能完善,控制系统可靠等特点。

关键词:电子琴,单片机,外围电路,系统分析,汇编程序,仿真,PCB,调试1 引言本次设计的电子琴控制系统由单片机最小系统加上按键电路,数码显示电路,声音播放电路组成,通过单片机内烧写的汇编程序来输出控制信号控制外围电路的工作。

电子琴设计不同于其他设计,需要输出1到7七个不同音阶的声音,因此信号的输出有其特殊性,可以利用单片机定时计数器产生不同频率的方波信号来形成七个不同的音阶,不同音阶的组合就能输出我们想要的音乐了。

梁祝乐曲_乐曲硬件演奏电路的VHDL设计_eda课程设计

一、设计题目:乐曲硬件演奏电路的VHDL设计二、设计目标:了解一般乐曲演奏电路设计设计方法,学习VHDL语言,熟悉EDA设计软件QuartusII和MAX+plusⅡ,加强独立完成电子设计的能力。

(1)能够播放“梁祝”乐曲。

(2)能够通过LED显示音阶。

(3)(选作)具有“播放/停止”功能,并在此基础上实现“按键演奏”的电子琴功能。

主芯片型号为FLEX10K10LC84-4三、实验电路的工作原理:(演奏电路逻辑图)组成乐曲的每个音符的发音频率值及其持续的时间是乐曲能够连续演奏所需的两个基本要素,设计演奏电路的关键就是获得这两个要素所对应的数值以及通过纯硬件的手段来利用这些数值实现所希望乐曲的演奏效果。

演奏电路逻辑图有三部分:音乐节拍和音调发生器、简谱码对应的分频预置数查表电路、数控分频与演奏发生器。

演奏电路逻辑图:四、设计内容:1.完成程序的编辑工作。

2.将音乐数据制作成LMP_ROM文件.3.将程序加载到MAX+plusⅡ中进行编译、仿真,并保存仿真结果。

4.到实验室进行下载验证。

引脚进行锁定,然后下载到实验芯片中观察实验结果。

五、仿真结果:1.音乐节拍和音调发生器(NoteTabs.VHD)notetabs模块中设置了一个8位二进制计数器(计数最大值138),作为音符数据ROM的地址发生器。

这个计数器的计数频率选为4Hz,即每一个计数值的停留时间为0.25秒,恰为当全音符设为1秒时,四四拍的4分音符持续时间。

随着notetabs模块中的计数器按4Hz的时钟速率作为加法计数时,即随地址值递增时,音符数据ROM中的音符数据将从ROM中通过ToneIndex[3..0]端口输向ToneTaba模块,“梁祝”乐曲就开始连续自然的演奏起来了。

Notetabs模块仿真图:2.简谱码对应的分频预置数查表电路(ToneTaba.VHD)音符的持续时间需根据乐曲的速度及每个音符的节拍数来确定,tonetaba 模块的功能首先是为speakera提供决定所发音符的预置数,而此数在speakera 输入口停留的时间即为此音符的节拍值。

硬件电子琴---《梁祝》乐曲演奏的实现

硬件电子琴---《梁祝》乐曲演奏的实现一、实验目的1.了解蜂鸣器发声原理和硬件实现乐曲演奏的原理;2.了解数控分频器的工作原理;3.进一步熟习Verilog HDL的设计方法。

二、实验原理根据蜂鸣器输入信号频率的不同决定了其发声不同的原理,来设计一个由数控分频器控制蜂鸣器发声的简单实验。

数控分频器的预置数由乐曲的音调的值来决定,从而间接的控制蜂鸣器的发声频率。

我们知道,组成乐曲的每个音符的发音频率值及其持续的时间是乐曲能连续演奏所需的2个基本要素,首先让我们来了解音符与频率的关系。

乐曲的12平均率规定:每2个八度音(如简谱中的中音1与高音1)之间的频率相差1倍。

在2个八度音之间,又可分为12个半音,音符A(简谱中的低音6)的频率为440Hz,音符B到C之间,E到F之间为半音,其余为全音。

由此可以计算出简谱中从低音1至高音1之间每个音符的频率。

产生各音符所需的频率可用一分频器实现,由于各音符对应的频率多为非整数,而分频系数又不能为小数,故必须将计算得到的分频数四舍五入取整。

若分频器时钟频率过低,则由于分频系数过小,四舍五入取整后的误差较大;若时钟频率过高,虽然误差较小,但会增加分频器的分频级数。

实际的设计应综合考虑两方面的因素,在尽量减小频率误差的前提下取合适的时钟频率。

这里设计的乐曲发生器选取5MHz的基准频率。

即使基准频率有所改变,实际上,只要各个音符间的相对频率关系不变,演奏出的乐曲听起来都不会“走调”。

化蝶简谱中各音符对应得分频系数如下表所示。

音符分频系数音符分频系数低音3 7584 低音5 6378 低音6 5682 低音7 5062 中音1 4778 中音2 4257 中音3 3792 中音5 3189 中音6 2841 高音1 2391为了减小输出的偶次谐波分量,最后输出到扬声器的波形应为对称方波,因此在到达扬声器之前,有一个二分频的分频器。

所以表中的分频系数是从5MHz频率二分频得到的2.5MHz频率基础上计算得出的。

学士学位论文—-电子琴实验报告乐曲硬件演奏电路设计

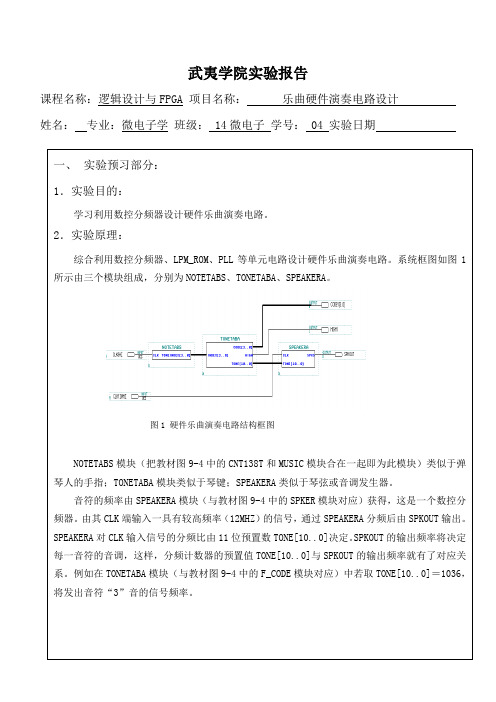

武夷学院实验报告课程名称:逻辑设计与FPGA 项目名称:乐曲硬件演奏电路设计姓名:专业:微电子学班级: 14微电子学号: 04 实验日期实验预习成绩(百分制)实验指导教师签字:二、 实验过程记录部分:1.实验过程记录:1.1 输入信号锁相环PLL0调节: 图2.1 锁相环 管脚clk_50m (设置为B12)接入FPGA 内部的50mhz 的时钟信号,C0口为得到数控分屏器模块的输入时钟750KHZ ,将分频比设置为1/67,即50000000HZ/67=74.6K约等于75K ;c1口为2KHZ (配合下级的500分频模块),设置为:c1=50000000HZ/25000=2KHZ 。

1.2 500分频模块count500(即500进制的计数器):图2.2 分频电路程序设计 如图2.2,因为梁祝歌曲只用低音和中音来演奏,为1/4拍,即四分之一拍,每个音符持续0.25秒的时间。

因为前级电路已经实现了从50MHZ 到2KHZ 的转换,要得到4HZ 的频率,则用500进制的计数器(0到499的计数)产生的进位信号对2KHZ 实现500分频(输出波形分析见后)。

1.3 乐曲长度控制计数器cnt138设计:图2.3 乐曲长度控制计数器程序及元件图经查阅《EDA技术实用教程(第五版)》可知,《梁祝》这首歌曲总共有139个音符,其中包含末尾的3个休止符。

如图2.3,因此为了产生这139音符,因此想到开发一个139进制的计数器(计数值:0到138),实现用139状态代表139个音符。

又因为要配合下一级音符谱码存储模块的输入(ROM的输入一般为偶数位),因此将原本用7路线就可以表示完成的输出端cnt8增加一位线宽。

注:在本程序中,输出端cnt8由于定义成integer整型,在Quartus中被自动分配成了7根;也可以定义成vector型,而此时需要注意配合下级电路的权位最好写成cnt8: out std_logic_vector(7 downto 0).1.4 音符谱码存储模块设计构建:1.4.1 ROM的设置:图2.4 音符谱码存储模块ROM音符谱码存储模的主体构想,是为了让前级模块所产生的139个状态与实际音符(Do Re Mi Fa So La Si)构成映射。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

武夷学院实验报告

课程名称:逻辑设计与FPGA 项目名称:乐曲硬件演奏电路设计姓名:朱文卓专业:微电子学班级: 14微电子学号: 04 实验日期

实验预习成绩(百分制)实验指导教师签字:

二、 实验过程记录部分:

1.实验过程记录:

1.1 输入信号锁相环PLL0调节: 图

2.1 锁相环 管脚clk_50m (设置为B12)接入FPGA 内部的50mhz 的时钟信号,C0口为得到数控分屏器

模块的输入时钟750KHZ ,将分频比设置为1/67,即50000000HZ/67=74.6K

约等于75K ;c1口为2KHZ (配合下级的500分频模块),设置为:c1=50000000HZ/25000=2KHZ 。

1.2 500分频模块count500(即500进制的计数器):

图2.2 分频电路程序设计 如图2.2,因为梁祝歌曲只用低音和中音来演奏,为1/4拍,即四分之一拍,每个音符持续0.25秒的时间。

因为前级电路已经实现了从50MHZ 到2KHZ 的转换,要得到4HZ 的频率,则用500进制的计数器(0到499的计数)产生的进位信号对2KHZ 实现500分频(输出波形分析见后)。

1.3 乐曲长度控制计数器cnt138设计:

图2.3 乐曲长度控制计数器程序及元件图

经查阅《EDA技术实用教程(第五版)》可知,《梁祝》这首歌曲总共有139个音符,其中包含末尾的3个休止符。

如图2.3,因此为了产生这139音符,因此想到开发一个139进制的计数器(计数值:0到138),实现用139状态代表139个音符。

又因为要配合下一级音符谱码存储模块的输入(ROM的输入一般为偶数位),因此将原本用7路线就可以表示完成的输出端cnt8增加一位线宽。

注:在本程序中,输出端cnt8由于定义成integer整型,在Quartus中被自动分配成了7根;也可以定义成vector型,而此时需要注意配合下级电路的权位最好写成cnt8: out std_logic_vector(7 downto 0).

1.4 音符谱码存储模块设计构建:

1.4.1 ROM的设置:

图2.4 音符谱码存储模块ROM

音符谱码存储模的主体构想,是为了让前级模块所产生的139个状态与实际音符(Do Re Mi Fa So La Si)构成映射。

因此需要构建一个包含《梁祝》乐谱的mif文件。

1.4.2构建《梁祝》乐谱.mif文件:

图2.5《梁祝》乐谱(部分截取)

因此综上所述,结合1.3的分析,音符谱码存储ROM,即输入为8位数据线,含256bit数据(实际只用了139bit);输出为4根线,这是由于《梁祝》这首歌曲只有低音的123567,以及中音的12356合高音部分的1,加上休止符一共13个状态,因此用4根数据线完全足够。

出于简化电路设计原则以及综合考虑电路测试的难易程度,我将高音部分的1当做中音的7来处理,将13个状态音符分为低音音符,中音音符和休止符;这样的好处是:在测试时候,只需用一个LED的亮灭并结合七段数码管来具体表示播放的音符,此时若灯亮且七段数码管显示为“7”,实际代表输出为高音的“Do”。

注:在以下的段落中,若出现“中音”,则用以表示“中音”的1235和“高音”的1.

1.5 分频预置查表电路f_code构建:

图2.6 f_code模块代码及原理图

由前级电路可知,从mscicsionROM模块的输出端q输出了13个音符(13个状态),而扬声器发出声音的实质是通过播放不同的声音频率实现的,而要实现将统一的频率分为不同的频率则必须引入实现分频功能的模块,由《数字电子技术基础(第五版)》的“时序电路章节”知识可知:普通的实现分频功能的计数器实现分频的原理是当计数值达到计数器最大模值N时,跳转到“预置数M”,因此可以实现“N-M+1”分频的功能;由此,我想到,如果将原本固定的“预置数”端,用一个模块代替,进而产生可以随需求变化而变化的预置数,这样就可以实现对不同音符频率的分频功能。

因此,本级模块最主要功能是将已有音符映射成对应的预置数。

因为下级模块“数控分频器”的最大计数值为11位2进制数,因此本级模块的输出TOO也为11位线宽。

因为下级模块数控分频器的最大计数值为2047,预置数为NT,计数模值为2047-NT+1=2048-NT, 如NT=912, 那么计数模值(分频系数)为2047-912=1135,因此将十进制的912改为十一位二进制的01110010000,赋值给TOO端(如图2.6),作为输出。

同时CODE端输出对应的音符(1到7),送至下级电路“谱码指示模块”;同时为了区别输出的音符为“低音”的(1到7)还是“中音”的(1到7),因此定义输出端口H,并接到FPGA 的一个LED,若灯不亮则表示为“低音”,若点亮则表示“高音”,再配合谱码指示模块中的“七段数码管”上显示的数值进而显示具体的音符。

1.6 数控分频器模块spker设计:

图2.7 数控分频器模块spker代码及原理图

如图2.7,该模块主要作用是将预置数通过计数器与对应音符的频率构成映射。

由于数控分频器所给的的输入时钟为750KHZ。

由之前的分析,数控分频器的最大计数值为11位2进制数,即2^11=2047,逢2047后预置NT, 为加法计数,输出为进位信号,进位信号总是取最大状态2047的译码。

不妨取1.5的假设,当NT=912时,计数模值:2047-912=1135,数控分频器输出频率为750KHZ/1135=660HZ,再由下级电路模块对数控分频输出进行2分频,则输出频率为660HZ/2=330HZ,对应为低音的2(Re)。

(其余见附录一)即,对应总公式:

fo =[750KHZ/(2048-TN)]/2

其中,f0为音符频率;TN即(TOO)为预置数。

1.7 谱码指示模块的设计:

1.7.1 七段数码管译码转换模块的设置:

图2.8 七段数码管译码转换模块代码及原理图

如图13所示T’触发器由D触发器加非门电路组成,构成一个二分频电路,由于直接从数控分频器出来的信号是脉宽极窄的信号,为了有利于驱动扬声器而添加此电路。

由1.5分析可知,f_code模块代的输出端CODE为4根线,而查阅PFGA开发板手册可知七段数码管的引脚有8个(包含一个小数点)。

因此,若想在数码管上显示对应的音符,必须开发一个模块,将4位二进制数(13个状态音符)用七位二进制数表示,对应7个输出端。

(因为本实验中用不到小数点,所以只考虑用数码管显示数值部分的7段LED)

1.7.2 七段数码管的设置:

图2.9 谱码指示模块总原理图

如图2.9,因为译码电路属于组合电路,属于异步,不受CLK控制,所以本级模块不设CLK 端。

结合(附录二)由于FPGA的七段数码管是共阳极接法,所以输出为0则点亮,例如音符“0001”,对应输出“1111001”。

1.8 二分频模块的设计:

图2.10 二分频模块原理图

由1.6可知,承接数控分频器模块的输出频率,为输出真正的音符频率,还需要一个二分频模块实现,直接调用D触发器,外接非门构成T’触发器,实现二分频功能。

此外由于从数控分频器输出的某些音符的频率的占空比很小,如果不加本模块,会出现音符出现的声音非常短暂的情况,因此,本模块还起到提高占空比50%,进而提升功率的作用。

2.实验现象及原始数据记录:

2.1 设计电路总图:

图2.11 总原理图

2.2 开发板管脚设置图:

图2.12 全体管脚映射图

实验操作成绩(百分制)__________ 实验指导教师签字:__________ 附录一

附录二

三、实验结果与讨论:

1.数据处理及实验结果分析:

1.1 实物图:

图3.1实物图

1.2 500分频模块波形仿真图:

图3.2 500分频模块波形

由图3.2可见,计数器计数值从0到499,到达计数最大模值499时进位输出pm端由低电平转入高电平,即500进制实现500分频。

1.3 cnt138模块波形仿真图:

图3.3 138模块波形

由图3.3,计数器从0计数到138,一共139个不同输出状态,从cnt8端输出。

2.实验改进、心得体会及思考题:

2.1 实验心得体会:

这次实验自己非常重视,花了很多时间,收获了很多。

自己对模块化设计电路有了更深,更直观的感受。

此外对用计数器来实现分频功能有了深刻的理解;在开发过程中也遇到了一系列的问题,例如在对“数控分频器”的VHDL代码编写中,开始不懂得signal和variable的区别,用前者时,信号在进程结束后才被改变,因此与所需音符状态无法及时对应;而后,我又发现如果在同一个进程中反复对variable所定义的变量进行赋值的话,软件只会把最后一次赋值的值赋给“变量”。

诸如此类的不再一一赘述,希望日后继续努力。

2.2 实验思考题:

1.教材图9-4中由D触发器INST1和非门INST2构成的2分频电路对扬声器发声有什么影响?

答:该电路模块实现对前级输出频率的二分频,让输出音符的频率全部处于人耳朵的听觉范围内。

同时还起到提高占空比至50%,进而提升功率的作用。

2.在电路上应该满足哪些条件,才能用数字器件直接输出的方波驱动扬声器发声?

答:(1):输出频率要在扬声器工作范围内;

(2):输出的电流要能驱动扬声器的正常工作。

实验报告成绩(百分制)实验指导教师签字:日期:。