2015-2016-01 存储器练习题 带参考答案分析

数据库原理习题(2015-2016-1)

数据库原理习题(2015-2016-1)第⼀、⼆、三章练习题⼀、单项选择题1、DBA是指( B )A、⾼级程序员B、数据库管理员C、数据库系统D、数据库管理系统2、在下列关于关系的陈述中,错误的是(B )A、表中任意两⾏的值不能相同B、表中任意两列的值不能相同C、⾏在表中的顺序⽆关紧要D、列在表中的顺序⽆关紧要3、数据库在磁盘上的基本组织形式是[ B]A.DB B.⽂件 C.⼆维表 D.系统⽬录4.在数据库中存储的是(C )。

A、数据B、数据模型C、数据以及数据之间的联系D、信息5.在关系数据库系统中,当合并两个关系时,⽤户程序可以不变。

这是( C )A、数据的物理独⽴性B、数据的位置独⽴性C、数据库的逻辑独⽴性D、数据库的存储独⽴性6.在下⾯的数据模型中,( D )是概念数据模型A、关系模型B、层次模型C、⽹状模型D、实体-联系模型7.关系数据库管理系统都是基于(A )理论。

A. Codd的数据关系模型B. 数据结构C. 计算机操纵系统D. 信息管理8.如果有9个不同的实体集,它们之间存在着12个不同的⼆元联系(⼆元联系是指两个实体集之间的联系),其中4个1:1联系,4个1:N联系,4个M:N 联系,那么根据ER模型转换成关系模型的规则,这个ER结构转换成的关系模式个数为[B ] A.9个 B.13个 C.17个 D.21个9.⼦模式DDL⽤来描述( B )A.数据库的总体逻辑结构B.数据库的局部逻辑结构C.数据库的物理存储结构D.数据库的概念结构10.关系笛卡尔积运算记号R×S中,(D )A. R为关系名,S为属性名B. R和S均为属性名C. R为属性名,S为关系名D. R和S均为关系名11.对单个⽤户使⽤的数据视图的描述称为(A)A.外模式B.概念模式C.内模式D.存储模式12.数据管理技术发展的3个阶段中,( A)阶段没有专门的软件对数据进⾏管理。

Ⅰ、⼈⼯管理阶段Ⅱ、⽂件管理阶段Ⅲ、数据库阶段A、只有ⅠB、只有ⅡC、Ⅰ和ⅡD、Ⅱ和Ⅲ13. 在数据库的三级模式间引⼊⼆级映象的主要作⽤是( A )A、提⾼数据与程序的独⽴性B、提⾼数据与程序的安全性C、保持数据与程序的⼀致性D、提⾼数据与程序的可移植性14.在关系模型中,同⼀个关系中的不同属性,其(C )。

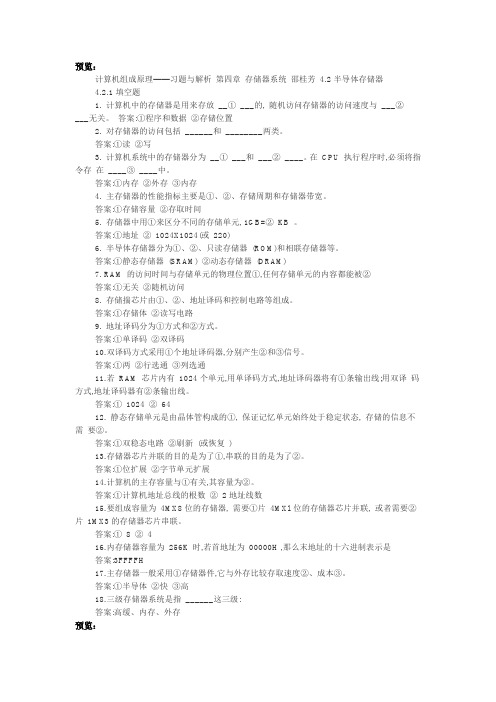

(完整版)存储器相关习题

预览:计算机组成原理——习题与解析第四章存储器系统邵桂芳 4.2半导体存储器4.2.1填空题1. 计算机中的存储器是用来存放__①___的, 随机访问存储器的访问速度与___②___无关。

答案:①程序和数据②存储位置2. 对存储器的访问包括______和________两类。

答案:①读②写3. 计算机系统中的存储器分为__①___和___②____。

在CPU 执行程序时,必须将指令存在____③____中。

答案:①内存②外存③内存4. 主存储器的性能指标主要是①、②、存储周期和存储器带宽。

答案:①存储容量②存取时间5. 存储器中用①来区分不同的存储单元, 1GB=②KB 。

答案:①地址②1024X1024(或220)6. 半导体存储器分为①、②、只读存储器(ROM)和相联存储器等。

答案:①静态存储器(SRAM) ②动态存储器(DRAM)7. RAM 的访问时间与存储单元的物理位置①,任何存储单元的内容都能被②答案:①无关②随机访问8. 存储揣芯片由①、②、地址译码和控制电路等组成。

答案:①存储体②读写电路9. 地址译码分为①方式和②方式。

答案:①单译码②双译码10.双译码方式采用①个地址译码器,分别产生②和③信号。

答案:①两②行选通③列选通11.若RAM 芯片内有1024个单元,用单译码方式,地址译码器将有①条输出线;用双译码方式,地址译码器有②条输出线。

答案:①1024 ②6412. 静态存储单元是由晶体管构成的①, 保证记忆单元始终处于稳定状态, 存储的信息不需要②。

答案:①双稳态电路②刷新(或恢复)13.存储器芯片并联的目的是为了①,串联的目的是为了②。

答案:①位扩展②字节单元扩展14.计算机的主存容量与①有关,其容量为②。

答案:①计算机地址总线的根数②2地址线数15.要组成容量为4MX8位的存储器, 需要①片4MXl 位的存储器芯片并联, 或者需要②片1MX3的存储器芯片串联。

答案:①8 ② 416.内存储器容量为256K 时,若首地址为00000H ,那么末地址的十六进制表示是答案:3FFFFH17.主存储器一般采用①存储器件,它与外存比较存取速度②、成本③。

第五章存储器习题(可编辑修改word版)

第五章存储器及其接口1.单项选择题(1)DRAM2164(64K╳1)外部引脚有()A.16 条地址线、2 条数据线B.8 条地址线、1 条数据线C.16 条地址线、1 条数据线 D.8 条地址线、2 条数据线(2)8086 能寻址内存贮器的最大地址范围为()A.64KBB.512KBC.1MBD.16KB(3)若用1K╳4b的组成2K╳8b的RAM,需要()。

A.2 片 B.16 片 C.4 片 D.8 片(4)某计算机的字长是否 2 位,它的存储容量是 64K 字节编址,它的寻址范围是()。

A.16K B.16KB C.32K D.64K(5)采用虚拟存储器的目的是()A.提高主存的速度 B.扩大外存的存储空间C.扩大存储器的寻址空间 D.提高外存的速度(6)RAM 存储器器中的信息是()A.可以读/写的 B.不会变动的C.可永久保留的D.便于携带的(7)用2164DRAM 芯片构成8086 的存储系统至少要()片A.16 B.32 C.64 D.8(8)8086 在进行存储器写操作时,引脚信号 M/IO 和 DT/R 应该是()A.00 B。

01 C。

10 D。

11(9)某SRAM 芯片上,有地址引脚线12 根,它内部的编址单元数量为()A.1024 B。

4096 C。

1200 D。

2K(11)Intel2167(16K╳1B)需要()条地址线寻址。

A.10 B.12 C.14 D.16(12)6116(2K╳8B)片子组成一个 64KB 的存贮器,可用来产生片选信号的地址线是()。

A.A0~A10B。

A~A15C。

A11~A15D。

A4~A19(13)计算一个存储器芯片容量的公式为()A.编址单元数╳数据线位数B。

编址单元数╳字节C.编址单元数╳字长D。

数据线位数╳字长(14)与 SRAM 相比,DRAM()A.存取速度快、容量大B。

存取速度慢、容量小C.存取速度快,容量小D。

存取速度慢,容量大(15)半导动态随机存储器大约需要每隔()对其刷新一次。

第三章存储系统练习题(含答案)

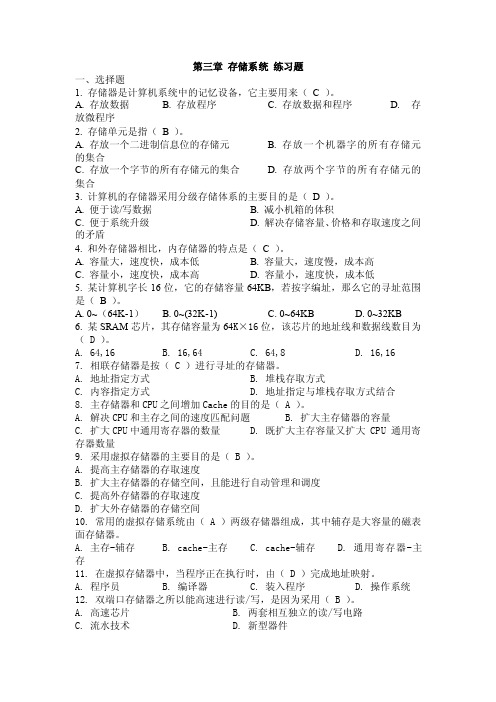

第三章存储系统练习题一、选择题1. 存储器是计算机系统中的记忆设备,它主要用来(C )。

A. 存放数据B. 存放程序C. 存放数据和程序D. 存放微程序2. 存储单元是指(B )。

A. 存放一个二进制信息位的存储元B. 存放一个机器字的所有存储元的集合C. 存放一个字节的所有存储元的集合D. 存放两个字节的所有存储元的集合3. 计算机的存储器采用分级存储体系的主要目的是(D )。

A. 便于读/写数据B. 减小机箱的体积C. 便于系统升级D. 解决存储容量、价格和存取速度之间的矛盾4. 和外存储器相比,内存储器的特点是(C )。

A. 容量大,速度快,成本低B. 容量大,速度慢,成本高C. 容量小,速度快,成本高D. 容量小,速度快,成本低5. 某计算机字长16位,它的存储容量64KB,若按字编址,那么它的寻址范围是( B )。

A. 0~(64K-1)B. 0~(32K-1)C. 0~64KBD. 0~32KB6. 某SRAM芯片,其存储容量为64K×16位,该芯片的地址线和数据线数目为( D )。

A. 64,16B. 16,64C. 64,8D. 16,167. 相联存储器是按( C )进行寻址的存储器。

A. 地址指定方式B. 堆栈存取方式C. 内容指定方式D. 地址指定与堆栈存取方式结合8. 主存储器和CPU之间增加Cache的目的是( A )。

A. 解决CPU和主存之间的速度匹配问题B. 扩大主存储器的容量C. 扩大CPU中通用寄存器的数量D. 既扩大主存容量又扩大CPU通用寄存器数量9. 采用虚拟存储器的主要目的是( B )。

A. 提高主存储器的存取速度B. 扩大主存储器的存储空间,且能进行自动管理和调度C. 提高外存储器的存取速度D. 扩大外存储器的存储空间10. 常用的虚拟存储系统由( A )两级存储器组成,其中辅存是大容量的磁表面存储器。

A. 主存-辅存B. cache-主存C. cache-辅存D. 通用寄存器-主存11. 在虚拟存储器中,当程序正在执行时,由( D )完成地址映射。

存储器习题解答

存储器习题解答1. ⽤下列芯⽚构成存储系统,各需要多少个RAM芯⽚?需要多少位地址作为⽚外地址译码?设系统为20位地址线,采⽤全译码⽅式。

(1)512×4位RAM构成16KB的存储系统;(2)1024×1位RAM构成128KB的存储系统;(3)2K×4位RAM构成64KB的存储系统;(4)64K×1位RAM构成256KB的存储系统。

解:(1) 需要16KB/512×4=64⽚,⽚外地址译码需20-log2512=11位地址线。

(2) 需要128KB/1K×1=1024⽚,⽚外地址译码需20-log21024=10位地址线。

(3) 需要64KB/2K×4=64⽚,⽚外地址译码需20-log2(1024×2)=9位地址线。

(4) 需要256KB/64K×1位=32⽚,⽚外地址译码需20-log2(1024×64)=4位地址线。

2. 现有⼀种存储芯⽚容量为512×4位,若要⽤它组成4KB的存储容量,需多少这样的存储芯⽚?每块芯⽚需多少寻址线?⽽4KB存储系统最少需多少寻址线?解: 4K×8bit /512×4bit= 16⽚,需要16⽚存储芯⽚;29 = 512,每⽚芯⽚需9条寻址线;212 = 4096,4KB存储系统最少需12条寻址线。

3. ⼀个具有8KB直接相联Cache的32位计算机系统,主存容量为32MB,假定该Cache中块的⼤⼩为4个32位字。

(1)求该主存地址中区号、块号和块内地址的位数。

(2)求主存地址为ABCDEF16的单元在Cache中的位置。

解: (1) 主存区数为32MB/8KB = 4096,212 = 4096,区号的位数为12;区内块数为8KB/4×4B = 512,29 = 512,块号的位数为9;块内单元数(字节编址)为4×32 / 8 = 16,24 = 16,块内地址的位数4。

存储器管理练习及参考答案

存储器管理练习及参考答案一、单项选择题:1、存储管理的目的是( C )。

A.方便用户B.提高主存空间的利用率C.方便用户和提高主存空间的利用率D.增加主存实际容量2、( A )存储管理不适合多道程序设计。

A.单一连续分区B.固定分区存储管理C.可变分区存储管理D.页式存储管理3、静态重定位是在作业的(B )进行的,动态重定位是在作业的( D )进行的。

A.编译过程中B.装入过程中C.修改过程中D.执行过程中4、提高主存利用率主要是通过( A )实现的。

A.内存分配B.内存保护C.地址映射D.内存扩充5、多道程序环境中,使每道程序能在不受干扰的环境下运行,主要是通过(C )功能实现的。

A.内存分配B.地址映射C.内存保护D.内存扩充6、最佳适应分配算法的空闲区是(B )。

A.按大小递减顺序排序B.按大小递增顺序排序C.按地址由小到大排列D.按地址由大到小排列7、地址重定位的对象是(B )。

A.源程序B.目标程序C.编译程序D.汇编程序8、采用可变分区存储管理方式管理主存时,使用移动技术可以(B )。

A.加快作业执行速度B.集中分散的空闲区C.扩大主存容量D.加快地址转换9、如下存储管理方式中,(A )一般采用静态重定位方式进行逻辑地址到物理地址的转换。

A.固定分区存储管理方式B.段式存储管理方式C.可变分区存储管理方式D.页式存储管理方式10、很好地解决了内存零头问题的存储管理方法是( A )。

A.页式存储管理B.段式存储管理C.多重分区管理D.可变式分区管理11、设基址寄存器的内容为1000,在采用动态重定位的系统中,当执行指令“Load A,2000”时,操作数的实际地址是( C )。

A.1000B.2000C.3000D.400012、对主存的研究可归纳为:主存的分配与回收、地址重定位、存储空间的共享与保护、( B )。

A.地址映射B.虚拟存储C.分区管理D.物理存储器的扩充13、地址转换或叫重定位的工作是将( C )A.绝对地址转换为逻辑地址B.逻辑地址转换为浮动地址C.逻辑地址转换为绝对地址D.绝对地址转换为浮动地址14、段式存储管理中,用于记录作业每个分段在主存中的起始地址和长度的是(B )。

2015-2016-01存储器练习题带参考答案讲解

存储器练习题参考答案一、选择题(75+7题)1、计算机系统中的存储器系统是指( D )。

A、RAM存储器B、ROM存储器C、主存储器D、主存储器和外存储器2、存储器是计算机系统中的记忆设备,它主要用来( C )。

A、存放数据B、存放程序C、存放数据和程序D、存放微程序3、存储单元是指( B )。

A、存放一个二进制信息位的存储元B、存放一个机器字的所有存储元集合C、存放一个字节的所有存储元集合D、存放两个字节的所有存储元集合4、计算机的存储器采用分级存储体系的主要目的是( D )。

A、便于读写数据B、减小机箱的体积C、便于系统升级D、解决存储容量、价格和存取速度之间的矛盾5、存储周期是指( C )。

A、存储器的读出时间B、存储器的写入时间C、存储器进行连续读和写操作所允许的最短时间间隔D、存储器进行连续写操作所允许的最短时间间隔6、和外存储器相比,内存储器的特点是( C )。

A、容量大,速度快,成本低B、容量大,速度慢,成本高C、容量小,速度快,成本高D、容量小,速度快,成本低7、某计算机字长16位,它的存储容量64K,若按字编址,那么它的寻址范围是( B )。

A、0~64KB、0~32KC、0~64KBD、0~32KB8、某SRAM芯片,其存储容量为64K×16位,该芯片的地址线和数据线数目为( D )。

A、64,16B、16,64C、64,8D、16,169、某DRAM芯片,其存储容量为512K×8位,该芯片的地址线和数据线数目为( D )。

A、8,512B、512,8C、18,8D、19,810、某机字长32位,存储容量1MB,若按字编址,它的寻址范围是( C )。

A、0~1MB、0~512KBC、0~256KD、0~256KB11、某计算机字长32位,其存储容量为4MB,若按字编址,它的寻址范围是( A )。

A、0~1MB、0~4MBC、0~4MD、0~1MB12、某计算机字长32位,其存储容量为4MB,若按半字编址,它的寻址范围( C )。

存储器作业答案

1、试使用62256,在8086最小系统中设计具有64KB的RAM,RAM地址从70000H开始。

要求:1)单片存储器RAM容量分别是多少?2)画出数据线、地址线和控制线的连线并注明符号名称;3)根据需要可以添加部分逻辑器件;4)要求线路清晰、准确,使用的符号标准规范。

1)单片存储器RAM容量:(芯片的存储容量=存储单元数×存储单元的位数=2M×NM:芯片的地址线根数、N:芯片的数据线根数)62256存储器芯片的地址线(A14~A0)15根,数据线(D7~D0)8根芯片的存储容量=215×8=16K×82)8086CPU16存储位系统设计①如下图所示:8086CPU16位存储系统采用奇、偶分体结构;A0通过或门连接偶片的CS,作为偶片选通的必要条件;BHE通过或门连接奇片的CS,作为奇片选通的必要条件;②数据线连接将数据总线的低8位D7~D0与偶体相连,高8位D15~D8与奇体相连③控制线连接控制信号线与8086系统工作模式有关,与存储单元有关控制信号线:MRD◆最大模式MWDC、C◆最小模式WR、RD、M/IO(IOM/用于控制存储芯片的片选信号)④地址线连接片内地址线(芯片地址线)数由芯片容量确定(如1k(210)容量,有10根地址线),通常连接从A1开始的19条地址线中的低位地址线;如:62256芯片的A14-A0连接地址总线的A15-A1⑤片选信号线的连接通常片选信号低电位有效,如62256芯片的片选信号CE=0芯片有效;芯片的片选信号受以下信号控制:✓奇偶芯片的选择信号;偶片用A0,奇片用BHE;✓最小模式的M/IO(访问存储器M/IO=1)控制信号;✓高位地址线的译码电路输出;(通常低电平有效)通常连接方法:➢M/IO为译码电路的输入➢A0通过或门与译码电路输出相或然后连接偶片的片选信号CE;BHE通过或门与译码电路输出相或然后连接奇片的CE;⑥地址译码电路的设计可以采用专用译码芯片(如:74LS138)和逻辑门电路⏹地址译码电路输入:➢地址总线的高位地址线(除用于连接芯片片内地址的低位地址线外,本题A19-A16)➢工作在最小模式时的M/IO⏹地址译码电路输出:输出低电位信号地址线的编码由芯片的地址决定;本题RAM地址从70000H开始;A19A18A17A16 A15 A14A13A12A11A10 A9A8A7 A6 A5 A4 A3 A2 A1A00 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0红色部分为片内地址;译码电路输入为A19A18A17A16G为高电位接M/IO;AG2为低电位接A19;G2、BA18A17A16分别接C、B、A,A18A17A16的编码为111,所以7Y有效(低电位),接或门。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

存储器练习题参考答案一、选择题(75+7题)1、计算机系统中的存储器系统是指( D )。

A、RAM存储器B、ROM存储器C、主存储器D、主存储器和外存储器2、存储器是计算机系统中的记忆设备,它主要用来( C )。

A、存放数据B、存放程序C、存放数据和程序D、存放微程序3、存储单元是指( B )。

A、存放一个二进制信息位的存储元B、存放一个机器字的所有存储元集合C、存放一个字节的所有存储元集合D、存放两个字节的所有存储元集合4、计算机的存储器采用分级存储体系的主要目的是( D )。

A、便于读写数据B、减小机箱的体积C、便于系统升级D、解决存储容量、价格和存取速度之间的矛盾5、存储周期是指( C )。

A、存储器的读出时间B、存储器的写入时间C、存储器进行连续读和写操作所允许的最短时间间隔D、存储器进行连续写操作所允许的最短时间间隔6、和外存储器相比,内存储器的特点是( C )。

A、容量大,速度快,成本低B、容量大,速度慢,成本高C、容量小,速度快,成本高D、容量小,速度快,成本低7、某计算机字长16位,它的存储容量64K,若按字编址,那么它的寻址范围是( B )。

A、0~64KB、0~32KC、0~64KBD、0~32KB8、某SRAM芯片,其存储容量为64K×16位,该芯片的地址线和数据线数目为( D )。

A、64,16B、16,64C、64,8D、16,169、某DRAM芯片,其存储容量为512K×8位,该芯片的地址线和数据线数目为( D )。

A、8,512B、512,8C、18,8D、19,810、某机字长32位,存储容量1MB,若按字编址,它的寻址范围是( C )。

A、0~1MB、0~512KBC、0~256KD、0~256KB11、某计算机字长32位,其存储容量为4MB,若按字编址,它的寻址范围是( A )。

A、0~1MB、0~4MBC、0~4MD、0~1MB12、某计算机字长32位,其存储容量为4MB,若按半字编址,它的寻址范围( C )。

A、0~4MBB、0~2MBC、0~2MD、0~1MB13、某计算机字长为32位,其存储容量为16MB,若按双字编址,它的寻址范围是( B )。

A、0~16MBB、0~8MC、0~8MBD、0~16MB14、某SRAM芯片,其容量为512×8位,加上电源端和接地端,该芯片引出线的最小数目应为( D )。

A、23B、25C、50D、1915、相联存储器是按( C )进行寻址的存储器。

A、地址指定方式B、堆栈存取方式C、内容指定方式D、地址指定与堆栈存取方式结合16、主存储器和CPU之间增加cache的目的是( A )。

A、解决CPU和主存之间的速度匹配问题B、扩大主存储器的容量C、扩大CPU中通用寄存器的数量D、既扩大主存容量又扩大CPU通用寄存器数量17、采用虚拟存储器的主要目的是( B )。

A、提高主存储器的存取速度B、扩大主存储器的存储空间,并能进行自动管理和调度C、提高外存储器的存取速度D、扩大外存储器的存储空间18、在虚拟存储器中,当程序在执行时,( D )完成地址映射。

A、程序员B、编译器C、装入程序D、操作系统19、下列说法中不正确的是( B )。

A、每个程序的虚地址空间可以大于实地址空间,也可以小于实地址空间B、多级存储体系由cache、主存和虚拟存储器构成C、cache和虚拟存储器这两种存储器管理策略都利用了程序的局部性原理D、当cache未命中时,CPU可以直接访问主存,而外存与CPU之间则没有直接通路20、在cache的地址映射中,若主存中的任意一块均可映射到cache内的任意一块的位置上,则这种方法称为( A )。

A、全相联映射B、直接映射C、组相联映射D、混合映射21、以下描述中基本概念正确的句子是( A )。

A、硬盘转速高,存取速度快B、软盘转速快,存取速度快C、硬盘是接触式读写D、软盘是浮动磁头读写22、组成2M*8bit的内存,可以使用( C )A、1M*8bit进行并联B、1M*4bit进行串联C、2M*4bit进行并联D、 2M*4bit进行串联23、若SRAM芯片容量为2M*8bit,则该芯片引脚中地址线和数据线的数目之和是( B )A.21B. 29C. 18D.不可估计24、若RAM中每个单元为16位,则下面所述正确的是( B )A.地址线也是16位B.地址线与16位无关C.地址线与16位有关D.地址线不得少于16位25、RAM芯片串联时可以( B )A.增加存储字长B.增加存储单元数量C.提高存储器的速度D.降低存储器的平均价格26、RAM芯片并联时可以( A )A.增加存储字长B. 增加存储单元数量C.提高存储器的速度D.降低存储器的平均价27、下面所叙述不正确的是( C )A.随机存储器可以随时存取信息,掉电后信息丢失B.访问随机存储器时,访问时间与单元的物理位置无关C.内存中存储的信息均是不可改变的D.随机存储器和制度存储器可以统一编址28、和外存相比,内存的特点是( C )A.容量大,速度快,成本低B.容量大,速度慢,成本高C.容量小,速度快,成本高D.容量小,速度快,成本低29、下列元件中存取最快的是()A.CacheB.寄存器C.内存D.外存30、RAM和ROM的主要区别是( B )A.断电后,ROM内保存的信息会丢失,RAM则可长期保存而不会丢失B.断电后,RAM内保存的信息会丢失,ROM则可长期保存而不会丢失C.ROM是外存,RAM是内存D.RAM是外存,ROM是内存31、某计算机字长16位,其存储容量为2MB,按半字编址,它的寻址范围是( C )A.0~8M-1B.0~4M-1C.0~2M-1D.0~1M-132、某计算机字长32位,其存储容量为8MB,按双字编址,它的寻址范围是( D )A.0~256K-1B.0~512K-1C.0~2M-1D.0~1M-133、计算机的存储器采用分级方式是为了( B )A.减少主机箱的体积B.解决容量、价格、速度三者之间的矛盾C.保存大量数据方便D.操作方便34、在主机和CPU之间增加cache的目的是( C )A.增加内存容量B.提高内存的可靠性C.解决CPU与内存之间的速度匹配问题D.增加内存容量,同时加快存取速度35、采用虚拟存储器的主要目的( B )A.提高主存的存取速度B.扩大存储器空间,并能进行自动管理C.提高外存的存取速度D.扩大外存储器空间36、程序访问的局部性是使用( B )的依据。

A.缓冲B.CacheC.虚拟内存D.进程37、有关高速缓冲存储器的说法正确的是( B )A.只能在CPU 以外B.CPU内外都可以设置C.只能在CPU以内D.若存在cache,CPU就不能再访问主存38、软盘驱动器在寻找数据时( C )A.盘片不动,磁头运动B.盘片运动,磁头不运动C.盘片运动,磁头运动D.盘片不动,磁头不运动39、磁盘存储器的记录方式一般采用( C )A.归零制B.不归零制C.改进的调频制D.调相制40、一张3.5英寸软盘的存储容量为(),每个扇区存储的固定数据是( A )。

A.1.44MB,512BB.1MB,1024BC.2MB,256BD.1.44MB,512KB41、磁盘的等待时间通常指( A )A.磁盘转半周所需的时间B.磁盘转2/3周所需的时间C.磁盘转1/3周所需的时间D.磁盘转一周所需的时间42、以下描述中基本概念正确的句子是( A )A.硬盘转速高、存取速度快B.软盘转速高、存取速度快C.硬盘是接触式读写D.软盘是浮动磁头读写43、若磁盘的转速提高一倍,则( D )A.平均存取时间减半B.平均寻道时间减半C.存储密度可以提高一倍D.平均定位时间不变44、活动头磁盘存储器的平均存取时间是指( C )A.最大找道时间加上最小找道时间B.平均找道时间C.平均找道时间加平均等待时间D.平均等待时间45、活动头磁盘存储器的找道时间是指( C )A.最大找道时间B.最小找道时间C.最大找道时间加上最小找道时间的平均值D.最大找道时间加上最小找道时间46、在下列几种存储器中,CPU可直接访问的是( A )。

A. 主存储器B. 磁盘C. 磁带D. 光盘47、在主存和CPU之间增加cache存储器的目的是( C )。

A. 增加内存容量B. 提高内存的可靠性C. 解决CPU与内存之间的速度匹配问题D.增加内存容量,同时加快存取速度48、SRAM芯片,存储容量为64K×16位,该芯片的地址线和数据线数目为( B )。

A.64,16 B.16,16 C.64,8 D.16,64。

49、以下四种类型的半导体存储器中,以传输同样多的字为比较条件,则读出数据传输率最高的是( C )。

A DRAMB SRAMC FLASH ROMD EPROM50、双端口存储器所以能进行高速读/写操作,是因为采用( D )。

A.高速芯片 B 新型器件 C 流水技术 D 两套相互独立的读写电路51、某单片机字长32位,其存储容量为4MB。

若按字编址,它的寻址范围是(A )。

A.1MB.4MBC.4MD.1MB52、 EEPROM是指(D )A.读写存储器 B 只读存储器 C 闪速存储器 D 电编程只读存储器53、一个Cache-主存系统,采用50MHz 的时钟,存储器以每一个时钟周期传输一个字的速率,连续传输8 个字,以支持块长为8 个字的Cache,每个字4 个字节。

假设读操作所花的时间是:1 个周期接受地址,3 个周期延迟,8 个传输周期传输8 个字;写操作所花的时间是:1 个周期接受地址,2 个周期延迟,8 个周期传输8 个字,3 个周期恢复和写入纠错码,则当系统以35%为读操作,65%为写操作的访问情况工作,则存储器最大带宽为( D )A.133.2MBps B.114.4MBps C.126MBps D.120.3MBps分析:时钟50MHZ,时钟周期为20ns.读操作的时间:Tr =(1+3+8)×20n s = 240ns写操作的时间:Tw = (1+2+8+3)×20ns = 280ns则综合加权的时间是:240ns×0.35 + 280ns×0.65 = 266ns带宽为(也就是266ns 可以传输8 个字,或者说传输32 字节):Bn = 32B/(266×10-9 s)≈ 120.3MBps54、在下列Cache 替换算法中,一般情况下,( D )性能最优。

A.随机法 B.先进先出法 C.后进先出法 D.近期最少使用法55、4 片16K×8 位的存储芯片可以设计成( D )容量的存储器。

Ⅰ. 64K×8 位Ⅱ. 32K×4 位Ⅲ. 32K×16 位Ⅳ. 16K×32 位A.Ⅰ、Ⅱ B.Ⅱ、Ⅲ C.Ⅰ、Ⅲ D.Ⅰ、Ⅲ、Ⅳ56、某机器字长16 位,主存容量为16MB,若按半字寻址,其寻址范围大小为( D )。