STM32F10x_USB_学习培训资料

STM32_深入浅出(新手必看)资料

STM32学前班教程之一:为什么是它经过几天的学习,基本掌握了STM32的调试环境和一些基本知识。

想拿出来与大家共享,笨教程本着最大限度简化删减STM32入门的过程的思想,会把我的整个入门前的工作推荐给大家。

就算是给网上的众多教程、笔记的一种补充吧,所以叫学前班教程。

其中涉及产品一律隐去来源和品牌,以防广告之嫌。

全部汉字内容为个人笔记。

所有相关参考资料也全部列出。

:lol教程会分几篇,因为太长啦。

今天先来说说为什么是它——我选择STM32的原因。

我对未来的规划是以功能性为主的,在功能和面积之间做以平衡是我的首要选择,而把运算放在第二位,这根我的专业有关系。

里面的运算其实并不复杂,在入门阶段想尽量减少所接触的东西。

不过说实话,对DSP的外设并和开发环境不满意,这是为什么STM32一出就转向的原因。

下面是我自己做过的两块DSP28的全功能最小系统板,在做这两块板子的过程中发现要想尽力缩小DSP的面积实在不容易(目前只能达到50mm×45mm,这还是没有其他器件的情况下),尤其是双电源的供电方式和1.9V的电源让人很头疼。

后来因为一个项目,接触了LPC2148并做了一块板子,发现小型的ARM7在外设够用的情况下其实很不错,于是开始搜集相关芯片资料,也同时对小面积的A VR和51都进行了大致的比较,这个时候发现了CortexM3的STM32,比2148拥有更丰富和灵活的外设,性能几乎是2148两倍(按照MIPS值计算)。

正好2148我还没上手,就直接转了这款STM32F103。

与2811相比较(核心1.8V供电情况下),135MHz×1MIPS。

现在用STM32F103,72MHz×1.25MIPS,性能是DSP的66%,STM32F103R型(64管脚)芯片面积只有2811的51%,STM32F103C型(48管脚)面积是2811的25%,最大功耗是DSP的20%,单片价格是DSP 的30%。

STM32USB学习笔记

基于STM32的USB学习总结第一章基础之简析USB协议1、USB包的分类USB包主要有以下几种:令牌包、数据包、握手包,其他包暂时用不到先不提。

1.1、令牌包顾名思义,这个类型的包是用来发布命令的,我们知道USB协议是典型的主从结构的协议,主设备就是用来发送令牌包,从设备是接收令牌后执行相应的命令的设备。

而令牌包下面又分了几种类型的令牌,他们分别带表了不同命令。

令牌包可分为SETUP包、IN包、OUT包、SOF包,其中SETUP包、IN包、OUT包结构构如下:其中同步域是用来同步主机和从机的,8位PID号分别代表了不同的包,其中低4位代表PID,高4位是用来取反的。

USB协议也是靠不同的PID来区别不同类型的包的。

我们先列下令牌包的几种包的PID以及各1.2、数据包用来代表这个包是用来装载用户传输的数据,包的长度大小和设备的属性有关,第一个数据包总是跟在令牌的后面,有了令牌包才会有数据包。

DAET0和DATE1都是用来传送数据,那为什么要2个不同的包呢?因为在USB协议里,每次成功传送一次数据后,都会进行数据类型的反转,即从DATE0到DATE1或者DATE1到DATE0。

举例说明:如果传送不成功主句不会收到ACK,那么他就会以原来的数据包PID进行发送数据,这样从机接收到新的PID和自己的是一样的,会保存数据;另外一种情况是,从机保存了数据并进行了数据类型反转,然后向主机发送了ACK,但主机没收到,主机也会按原来的PID数据包从新发送,当从机接收到了数据包后发现与将要接收的PID类型不一样,则不会保存数据。

1.3、握手包这种包是用来进行确认消息是否有效或者消息是否发送成功的,握手包可以分为ACK,NAK,STALL和ACK,NAK,STALL和NYET包的PID如下表:2、USB 事务USB 事务也可以称为USB 事件,每次事件的发生必定会存在3种包:令牌包---用来发送指令,数据包---用来传送数据,握手包-----用来确认操作。

STM32自定义USB设备开发详细流程讲解及全套资料源码下载

25

/******************** endpoint descriptor ********************/

26

/* 18 */

27

0x07,

/* endpoint descriptor length = 07H */

28

USB_ENDPOINT_DESCRIPTOR_TYPE, /* endpoint descriptor type = 05H */

03 {

04

CUSTOMHID_SIZ_STRING_LANGID,

05

USB_STRING_DESCRIPTOR_TYPE,

06

0x09,

07

0x04

08 }; /* LangID = 0x0409: U.S. English */

09 const uint8_t CustomHID_StringVendor[CUSTOMHID_SIZ_STRING_VENDOR] =

USB_ENDPOINT_DESCRIPTOR_TYPE, /* endpoint descriptor type = 05H */

41

0x82,

/* endpoint 2 IN */

42

0x02,

/* bulk transfer = 02H */

43

0x40,0x00, /* endpoint max packet size = 0040H */

22 uint8_t CustomHID_StringSerial[CUSTOMHID_SIZ_STRING_SERIAL] =

23 {

24

CUSTOMHID_SIZ_STRING_SERIAL,

MXCHIP STM32F10xxx USB 开发人员工具包 说明书

用户手册STM32F10xxx USB开发人员工具包介绍STM32F10xxx USB开发人员工具包是一个完整的固件和软件包,并且包括所有USB传输方式(控制,中断,块,同步的方式)的实例和范例,支持STM32F10xxx系列的所有微控制器。

STM32F10xxx USB开发人员工具包的目标是在每种USB传输方式都提供一个使用STM32F10xxx USB库的固件范例。

本文档是对STM32F10xxx USB开发人员工具包的所有组件的描述,包括以下内容:STM32F10xxx USB库,关于默认端点和标准请求的过程设备固件升级范例:控制传输方式操纵杆鼠标范例:中断传输方式大容量存储范例:批量传输方式虚拟COM端口:批量传输方式USB音频范例(USB扬声器):同步传输方式。

目录1 STM32F10xxx USB固件库 (5)1.1 USB应用层次 (5)1.2 USB库内核 (6)1.2.1 usb_type.h (6)1.2.2 Usb_reg (.c,.h) (7)1.2.3 usb_int (.c , .h) (14)1.2.4 usb_core (.c , .h) (14)1.3 应用接口 (19)1.3.1 usb_istr(.c) (20)1.3.2 usb_conf(.h) (20)1.3.3 usb_endp (.c) (20)1.3.4 usb_prop (.c , .h) (20)1.3.5 usb_pwr (.c , .h) (23)1.4 用STM32F10xxx USB 库实现USB应用 (23)1.4.1 实现无数据类专用请求 (23)1.4.2 如何管理非控制端点的数据传输 (26)2 操纵杆鼠标范例 (26)3 设备固件升级 (26)3.1 DFU扩展协议 (27)3.1.1 介绍 (27)3.1.2 阶段 (28)3.1.3 请求 (28)3.2 DFU 模式选择 (29)3.2.1 运行时描述集 (29)3.2.2 DFU模式描述符集 (30)3.3 重配置阶段 (36)3.4 传输阶段 (36)3.4.1 请求 (37)3.4.2 特殊指令/协议描述 (37)3.4.3 DFU 状态图 (38)3.4.4 下载和上传 (40)3.4.5 显示阶段 (41)3.5 STM32F10xxx DFU 实现 (41)3.5.1 支持的存储器 (41)3.5.2 DFU 模式进入机制 (41)3.5.3 STM32F10xxx的可用DFU 映像 (42)4 大容量存储范例 (42)4.1 大容量存储范例总论 (43)4.2 大容量存储协议 (43)4.2.1 仅块传输 (43)4.2.2 小型计算机系统接口 (SCSI) (46)4.3 大容量范例的实现 (48)4.3.1 硬件配置接口 (48)4.3.2 端点配置和数据管理 (49)4.3.3 类细节请求 (50)4.3.4 标准请求规需求 (52)4.3.5 BOT 状态机 (52)4.3.6 SCSI 协议实现 (53)4.4 如何定制大容量存储范例 (55)5 虚拟COM端口范例 (59)5.1 虚拟COM端口范例建议 (59)5.2 软件驱动安装 (60)5.3 实现 (61)5.3.1 硬件实现 (61)5.3.2 固件实现 (61)6 USB音频范例 (63)6.1 同步传输综述 (63)6.2 音频设备类综述 (64)6.3 STM32FF10xxx USB扬声器范例 (65)6.3.1 通用功能 (66)6.3.2 实现 (67)7 修改历史 (76)8 版权声明: (77)1STM32F10xxx USB固件库本章节介绍用于管理STM32F10xxx USB 2.0全速设备外设的固件接口(称之为USB库)。

芯达STM32入门系列教程之十四《STM32的USB下载调试》

STM32入门系列教程STM32的USB下载调试Revision 0.01( 2010-08-12)ST官方实际上提供了两种下载方式:串口ISP与USB下载。

之前讲述了串口ISP的下载调试(类似单片机一样),还有一种就是USB方式。

通俗地说,我们可以使用USB接口来下载和调试程序。

熟悉USB的朋友马上反应过来,USB 和串口一样,都是串行传送数据。

是的,这两种方式下载,数据的传输方式都是串行,因此速度不可能太快。

事实上,真正的开发,不可能靠ISP来调试。

都是使用JLINK + MDK或者IAR来调试的。

有条件的同学可以购买jlink仿真器。

说了很多闲话,下面开始进入正题。

要进行USB下载,我们需要事先准备的工作如下:1、DfuSe安装软件2、USB下载固件(hex文件)以上这两个均可在芯达stm32光盘中找到。

在光盘的软件工具目录下,可以找到DfuSe_Demo_V2.2.1_Setup.exe;该软件是为了进行USB下载提供一个操作的界面。

USB的固件HEX文件——STM32_USB.hex,可以在目录“芯达STM32出厂HEX文件”中找到。

1. Dfuse软件的安装安装的过程,建议大家不要看一下本教程的一个步骤,安装一下,再看一下教程,再安装。

如此效率比较低。

建议先把教程浏览一遍,人的瞬间记忆能力,在这里足够用了。

遇到没有印象的,再回过头来看教程。

OK,双击DfuSe_Demo_V2.2.1_Setup.exe图标,双击后,会进入如下界面:等待几秒钟,即可进入如下界面:点击下一步NEXT,进入下一界面:此时,选择是否接收协议授权等信息,可暂且不管,直接YES,进入下一界面:此界面最熟悉不过,一般软件都会有,直接Next,进入下一界面:这里需要做一个说明,笔者默认把该软件安装在C盘,如果你想安装在别的盘符,直接点击Browse…,跳出对话框选择即可。

建议默认放在C盘。

以防后续步骤出错。

然后Next。

Part3 -STM32F10x Technical Training_V0.3

April 07STM32F10x Technical TrainingMCD Application TeamCONTENTSObjectivesSTM32F10x DeviceBlock DiagramMemory mapping and boot modesSystem ArchitectureSTM32F10x PeripheralsMain featuresSTM32F10x USB Developer kitSTM32F10x Firmware LibraryPackage organizationCoding conventionsLibrary structureUsing the LibrarySTM32F10x Technical Training V0.3OBJECTIVESImprove your knowledge on STM32F10x peripheralsIntroduce the STM32F10x Firmware LibraryAt the end of the training you will be able toList the main features of the STM32F10x peripheralsList the main demos of the STM32F10x USB Developer kitConfigure the Firmware library environmentDevelop your applications using the STM32F10x Firmware Library STM32F10x Technical Training V0.3CONTENTSObjectivesSTM32F10x DeviceBlock DiagramMemory mapping and boot modesSystem ArchitectureSTM32F10x PeripheralsMain featuresSTM32F10x USB Developer kitSTM32F10x Firmware LibraryPackage organizationCoding conventionsLibrary structureUsing the LibrarySTM32F10x Technical Training V0.3STM32F10x Technical Training V0.3Up to 20kB SRAM 64kB to come e/o2007F l a s h I /F32kB-128kB Flash Memory 512kB to comee/o 2007CORTEXM3CPU 72 MHzJTAG/SW Debug Nested vect IT Ctrl 1x Systic Timer A R M L i t e H i -S p e e d B u s M a t r i x / A r b i t e r (m a x 72M H z )STM32F10x Series Block DiagramARM 32-bit Cortex-M3 CPUNested Vectored Interrupt Controller (NVIC) w/ 43 maskable IT + 16 prog. priority levels Embedded Memories :FLASH: up 128 Kbytes, 512kB to come e/o 2007SRAM: up 20 Kbytes, 64kB to come e/o 20077 Channels DMAPower Supply with internal regulator and low power modes :2V to 3V6 supply4 Low Power Modes with Auto Wake-upIntegrated Power On Reset (POR)/Power Down Reset (PDR) + Programmable voltage detector (PVD)Backup domain w/ 20B regUp to 72 MHz frequency managed & monitored by the Clock Control w/ Clock Security System Rich set of peripherals & IOsEmbedded low power RTC with V BAT capability Dual Watchdog Architecture5 Timers w/ advanced control features (including Cortex SysTick)9 communications InterfacesUp to 80 I/Os (100 pin package) w/ 16 external interrupts/eventUp to 2x12-bits 1Msps ADC w/ up to 16 channels and Embedded temperature sensor w/ +/-1.5°linearity with T °XTAL oscillators 32KHz + 4~16MHz Int. RC oscillators 32KHz + 8MHzPLL32/49/80 I/OsUp to 16 Ext. ITs2x I 2C1x SPI 2x USART/LIN Smartcard / IrDa Modem Control1x USB 2.0FS 1x bxCAN 2.0B 1x USART/LIN Smartcard/IrDa Modem-Ctrl1x SPI RTC / AWUPower Supply Reg 1.8V POR/PDR/PVDDMA 7 Channels2x 12-bit ADC 16 channels / 1Msps Temp SensorA R M P e r i p h e r a lB u s(m a x 72M H z )Bridge BridgeARM Peripheral Bus(max 36MHz)1x 16-bit PWMSynchronized ACTimer3x 16-bit Timer20B Backup Regs Independent WatchdogWindow Watchdog Reset Clock ControlSTM32F10x Technical Training V0.3Memory Mapping and Boot ModesBOOT Mode Selection Pins Boot Mode AliasingBOOT1BOOT0x0User FlashUser Flash is selected asboot space 01SystemMemory SystemMemory is selectedas boot space 11Embedded SRAMEmbedded SRAM is selected as boot spaceCODESRAMPeripherals0x0000 00000x2000 00000x4000 00000xE010 00000xFFFF FFFF ReservedReservedReservedBit-Band regionBoot modesDepending on the Boot configuration, Embedded Flash Memory, System Memory or Embedded SRAM Memory is aliased at @0x000x0800 00000x0801 FFFF0x1FFF F0000x1FFF F7FF FlashSystemMemoryReservedReservedOption Bytes 0x1FFF F8000x1FFF F9FF Addressable memory space of 4 GBytes RAM : up to 20 kBytes FLASH : up to 128 kBytesSystemMemory : contains the Bootloader used to re-program the FLASH through USART .Boot from SRAM :In the application initialization code you have to Relocate the Vector Table in SRAM using the NVIC Exception Table and Offset registerCortex-M3 internal peripherals0xE000 00000xE00F FFFF ReservedSTM32F10x Technical Training V0.3System ArchitectureMultiply possibilities of bus accesses to SRAM, Flash, Peripherals, DMABusMatrix added to Harvard architecture allows parallel accessEfficient DMA and Rapid data flowDirect path to SRAM through arbiter , guarantees alternating accessHarvard architecture + BusMatrix allows Flash execution in parallel with DMA transferIncrease Peripherals Speed for better performanceDual Advanced Peripheral buses (APB) architecture w/ High Speed APB (APB2) up to 72MHz and Low Speed APB (APB1) up to 36MHzAllows to optimize use of peripherals (18MHz SPI, 4.5Mbps USART , 72MHz PWM Timer , 18MHz toggling I/Os)Buses are not overloaded with data movement tasksBusMatrixSystemD-busI-busCORTEX-M3Master 1GP-DMA Master 2SRAM SlaveFLASHF L I T FAHB-APB2AHB-APB1AHBGPIOA,B,C,D,E -AFIO –USART1-SPI1 -ADC1,2 -TIM1 -EXTI BridgesAPB1APB2Arbiter USART2,3 -SPI2 -I2C1,2 –TIM2,3,4 -IWDG –WWDG –USB –CAN –BKP –PWR –CONTENTSObjectivesSTM32F10x DeviceBlock DiagramMemory mapping and boot modesSystem ArchitectureSTM32F10x PeripheralsMain featuresSTM32F10x USB Developer kitSTM32F10x Firmware LibraryPackage organizationCoding conventionsLibrary structureUsing the LibrarySTM32F10x Technical Training V0.3STM32F10x Technical Training V0.3STM32F10x Series Block DiagramClick on Periph to jump to the corresponding slideCORTEXM3CPU72 MHzUp to 20kB SRAM64kB to come e/o 2007A R M P e r i p h e r a lB u s(m a x 72M H z )2x 12-bit ADC16 channels / 1Msps2x I 2C1x SPI 2x USART/LINSmartcard / IrDa Modem Control32/49/80 I/OsUp to 16 Ext. ITs F l a s h I /F32kB-128kB Flash Memory512kB to come e/o2007Temp Sensor1x USB 2.0FS 1x bxCAN 2.0B 1x 16-bit PWMSynchronized AC TimerIndependent Watchdog 3x 16-bit TimerJTAG/SW Debug XTAL oscillators32KHz + 4~16MHzPower SupplyReg 1.8VPOR/PDR/PVD DMA7 ChannelsNested vect IT Ctrl 1x USART/LINSmartcard/IrDa Modem-Ctrl1x SPI Bridge Bridge1x Systic TimerA R M L i t e H i -S p e e dB u s M a t r i x / A r b i t e r (m a x 72M H z )Int. RC oscillators32KHz + 8MHzPLLReset Clock ControlRTC / AWUARM Peripheral Bus(max 36MHz)20B Backup Regs Window WatchdogEmbedded FLASH STM32F10x Technical Training V0.3Flash Features Overview Flash Features:Up to 128KBytes1 KByte Page sizeEndurance: 1000 cyclesMemory organization:Main memory blockInformation blockAccess time: 35nsWord(32-bit) program time: 20μsPage / Mass Erase Time: 20msFlash interface Features:Read Interface with pre-fetch bufferOption Byte loaderFlash program/Erase operationsTypes of Protection:Access ProtectionWrite ProtectionSTM32F10x Technical Training V0.3Flash OperationsThe Flash program and erase operations are handled by the Flash program and erase controller (FPEC)After reset the FPEC is protected, an unlocking sequence should be performed (write of 2 key values) to unlock the FlashThe Flash can be programmed with 16-bits at a timeFlash can be erased page-wise or completely: Mass EraseThe Read access can be performed with the following configuration: Latency: Number of wait state for a read operation programmable on the flyPrefetch buffer of 2x64bit: For faster CPU execution can be enabled and disabled on the flyHalf Cycle: Flash access can be made on a half cycle of the HCLK to reduce powerconsumption, enabled by softwareSTM32F10x Technical Training V0.3Information BlockThe Information Block consists of:2 KBytes for Big Information block (BIF): contains Bootloader512 Bytes for Small Information block (SIF): contains the user option bytes.6 option bytes (SIF Block) are available:4 for write protection1 for read protection1 for configuration:IWDG HW/SW modeReset when entering STANDBY modeReset when entering STOP modeAfter unlocking the FPEC, the user has to authorize the small info blockprogramming by writing 2 key values then he can program the Option bytesOn every reset, the option bytes loader performs a read of the information block and stores the data into the FPEC registers (when programmed the option bytes are taken into account only after reset).STM32F10x Technical Training V0.3Flash Protection(1/2)Two kind of protections are available:Write protection to avoid unwanted writingsReadout protection to avoid piracyActivated by setting option bytes in the Small Information Block (SIF)Readout protection:The following Flash access are not allowed: read data in Flash memory through DCODE bus (main and information blocks) from others memory, from debugger or from DMA.Pages 0-3 are automatically write protected, to avoid the reprogramming of the Reset Vector to make it jump to RAM to execute untrusted code.Unprotection:Erase the entire Small Information block (User part)The result of Readout protection code (RDP) will be 0xFF, the read protection will be still enableProgram the correct code 0xA5 of RDP to unprotect the memory, this operation will first force a MassErase of the main blockReset the device (System Reset) to re-load the options bytes (and the new RDP code), and disable theReadout protectionSTM32F10x Technical Training V0.3Flash Protection(2/2)Write ProtectionThe write protection is implemented with a choice of protecting 4 pages (4K) at a timeA total of 4 user Options bytes are used to protect all the 128K main FlashAny programming or erase of a protected page is discarded and the Flash will return protection error flag on FSR status registerUnprotection:Erase the entire Small Information block (User part)The result of Readout protection code (RDP) will be 0xFF , the readout protection is enabledProgram the correct code 0xA5 of RDP to disable read protectionReset the device (System Reset) to re-load the options bytes for disabling any write protectionSTM32F10x Technical Training V0.3Direct Memory Access (DMA) STM32F10x Technical Training V0.3DMA Features7 independently configurable channels: hardware requests or software triggeron each channelSoftware programmable priorities: Very high, High, Medium or Low. (Hardware priority in case of equality)Programmable and Independent source and destination transfer data size: Byte, Halfword or Word3 event flags for each channel: DMA Half Transfer, DMA Transfer complete andDMA Transfer ErrorMemory-to-memory, peripheral-to-memory and memory-to-peripheraltransfersFaulty channel is automatically hardware disabled in case of bus access error Programmable number of data to be transferred: up to 65536Support for circular buffer managementSTM32F10x Technical Training V0.3STM32F10x Technical Training V0.3DMA Request MappingD M ASW TRIGGER DMA REQUESTOR ADC1TIM2_CC3TIM4_CC1SW TRIGGER OR USART3_TX SW TRIGGER OR SW TRIGGER OR SW TRIGGER OR SW TRIGGER ORSW TRIGGERORHigh Priority RequestLow Priority RequestThe DMA controller provides access to 7 channelsChannel1Channel2Channel3Channel4Channel5Channel6Channel7TIM1_CC1TIM2_UPTIM3_CC3SPI1_RX USART3_RXTIM1_CC2SPI1_TXTIM3_CC4TIM3_UPSPI2_RXI2C2_TXTIM1_CC4USART1_TXTIM1_CCU TIM1_TRIGTIM4_CC2USART1_RX TIM1_UP SPI2_TX I2C2_RXTIM2_CC1TIM4_CC3USART2_RXTIM1_CC3TIM3_CC1I2C1_TXTIM3_TRIGUSART2_TXTIM2_CC2TIM2_CC4TIM4_UPI2C1_RXSTM32F10x Technical Training V0.3The latency between two DMA transferRequest1 sample & arbitration phaseBus access Address computation Acknowledgement phase1 cycle1 cycle 3 cycle 1 cycleRequest 16 cycles for each request (source and destination on AHB)Request2 sample & arbitration phaseRequest 2If source or destination is a peripheral on APB, Bus access will include more cycles due to the AHB/APB bridge latency depending on the AHB/APB ratio.STM32F10x Technical Training V0.3To improve the DMA performances, a new request can be served while the previous one isrunning : if a request is active and other ones are pending, the new request sample & arbitration phase is performed during AHB bus access of the current request. The winning request AHB bus access will start immediately after the end of the current request…s AHB Bus access.Request 1 sample & arbitration phaseAcknowledgephaseHCLKChannel 1Request 2 sample & arbitration phaseAddresscomputationRequest 1 sample & arbitration phaseAddresscomputationAddresscomputationChannel 2Bus accessBus accessBus accessAcknowledgephaseAcknowledgephaseSTM32F10x Technical Training V0.3DMA and Bus occupationRequest, arbitration and acknowledgement operations are done outside AHB system bus, so the bus is not occupied during those phasesOne DMA access takes 2 cycles: the system Bus can not be totally freeze by DMA as at least one cycle is left to the CPU between two consecutive transactions. So up to 66%of the total bus bandwith available for DMA accesses.Current DMA controller compared to others which permit burst transfer have nearly thesame system bus occupation rate. However , it doesn‟t freeze the bus for many cyclesconsecutively as it is the case with the burst mode: better performance with many small data transfer without blocking the busRead Write Read Write Read WriteRead WriteBus accessBus accessBus free for CPUAHB Control AHB DataQuizHow many DMA Channels are available in the STM32F10x ?____________List the peripherals which have a DMA interface?____________How many interrupts can be generated for each channel?____________Which Channel is able to perform Memory to Memory transfer?____________STM32F10x Technical Training V0.3Power Control (PWR) and Backup Domain (BKP) STM32F10x Technical Training V0.3STM32F10x Technical Training V0.3Power SupplyA/D converter Temp. sensor Reset block PLLV DDAdomainLSE crystal 32K osc BKP registersRCC BDCR register RTCBackup domainCoreMemories DigitalperipheralsV 18domainV DD domainSTANDBY circuitry (Wake-up logic,IWDG, RCC CSR reg)Voltage RegulatorI/O Rings V SS V DDV BAT V DDA V SSAV REF-V REF+Low Voltage DetectorPower Supply SchemesV DD = 2.0 to 3.6 V: External Power Supply for I/Os and the internal regulator .V DDA = 2.0 to 3.6 V: External Analog Power supplies for ADC, Reset blocks, RCs and PLL. ADC working only if V DDA ≥ 2.4 VV BAT = 2.0 to 3.6 V: For Backup domain when V DD is not present.Power pins connection:V DD and V DDA must be connected to the same power sourceV SS , V SSA and V REF-must be tight to ground 0V < V REF+≤ V DDAV REF+and V REF-available only in LQFP100 package, in other packages they are internally connected respectively to V DDA and V SSAPower On Reset (POR)/Power Down Reset (PDR)Integrated POR / PDR circuitry guarantees proper product reset when voltage is not in the product guaranteed voltage range (2V to 3.6V)No need for external reset circuitPOR and PDR have a typical hysteresis of 40mVVDDPORPDR40mv hysteresisResetVtrhVtrlTempo2msVtrl min 1.8V / Vtrh max 2VSTM32F10x Technical Training V0.3STM32F10x Technical Training V0.3Programmable Voltage Detector (PVD)Programmable Voltage DetectorEnabled by softwareMonitor the V DD power supply by comparing it to a thresholdThreshold configurable from 2.2V to 2.9V by step of 100mVGenerate interrupt through EXTI Line16 (if enabled) when VDD < Threshold and/or VDD < ThresholdCan be used to generate a warning message and/or put the MCU into a safe stateVDD100mv hysteresisPVD OutputPVD ThresholdBackup DomainBackup Domain containsRTC (Counter , Prescaler and Alarm mechanism)Separate 32KHz Osc (LSE) for RTC10 x 16-bits user backup registersRCC BDSR register: RTC source clock selection and enable + LSE configReset only by Backup domain RESETV BAT independent voltage supplyAutomatic switch-over to V BAT when V DD goes lower than PDR levelNo current sunk on V BAT when V DD presentT amper detection: resets all user backup registers Configurable level: low/highConfigurable interrupt generationBackup domain32KHz OSC(LSE)RTC10 x 16regANTI_TAMPV BATV DDRCC BDSRregpower switchSTM32F10x Technical Training V0.3STM32F10x Low Power modes: uses CortexM3 Sleep modesWFI, WFE, STOP and STANDBY modesThe reset circuitry, POR/PDR, is active in STANDBY and STOP modesFeature STM32F10x typConsumption in RUN mode w/ execute from Flash on10mAinternal RC and peripherals clock ON36mAConsumption in RUN mode w/ execute from Flash onPLL 72 MHz( internal RC) and peripherals clock ON32mAConsumption in RUN mode w/ execute from SRAM onPLL 72 MHz( internal RC) and peripherals clock ONSTOP w/ Voltage Regulator in low power7µASTANDBY (w/ RTC OFF)2µARTC on VBAT 1.5 µAThe mA/MHz is higher at low frequency because of some static consumption (regulator, oscillator, Flash) SRAM execution is low power than Flash executionSTM32F10x Technical Training V0.3WFI/WFE Modes : Core stopped, peripherals kept runningWFI (Wait For Interrupt)Entry: execute WFI instructionExit: any peripheral interrupt acknowledged by the Nested Vectored Interrupt Controller (NVIC) WFE (Wait For Event)An event can be an interrupt enabled in the peripheral control register but NOT in the NVIC or an EXTIline configured in event modeEntry: execute WFE instructionExit: as soon as the event occurs No time wasted in interrupt entry/exitTwo mechanisms to enter these modesSleep Now: MCU enters Sleep mode as soon as WFI/WFE instruction are executedSleep on Exit: MCU enters Sleep mode as soon as it exits the lowest priority ISR (WFI/WFE instructionsare written in the ISR)To further reduce power consumption you can save power of unused peripherals by gating their clockSTM32F10x Technical Training V0.3STOP Mode: all periph clocks, PLL, HSI and HSE are disabled, SRAM and register contents are preserved.If the RTC and IWDG are running they are not stopped in STOP (either as their clocksources)To further reduce power consumption the Voltage Regulator can be put in Low Power mode Wake-up sources:WFI was used for entry: any EXTI Line configured in Interrupt mode (the corresponding EXTI Interruptvector must be enabled in the NVIC)WFE was used for entry: any EXTI Line configured in event modeEXTI line source can be: one of the 16 external lines, PVD, RTC alarm, USB wake-upAfter resuming from STOP the clock configuration returns to its reset state (HSI used as system clock).STM32F10x typWake-up time from Stop mode on HSI RC at8MHzRegulator in run mode 4 µsRegulator in low power mode9 µsSTM32F10x Technical Training V0.3Low Power Modes (4/4)STANDBY Mode : Voltage Regulator off, the entire V18 domain is powered off.SRAM and register contents are lost except registers in the Backup domain and STANDBY circuitryRTC and IWDG are kept running in STANDBY (if enabled)In STANDBY mode all IO pins are high impedance exceptReset pad (still available)Anti-Tamper pin if configured for tamper or calibration outWKUP pin if enabledWake-up sources:WKUP pin rising edgeRTC alarmExternal reset in NRST pinIWDG resetAfter wake-up from STANDBY mode, program execution will restart in the same way as after a RESET.Wake-up time from STANDBY mode on HSI RC at8MHz STM32F10x typ35 µsSTM32F10x Technical Training V0.3QuizHow many power supply domains are available?____________What is the content of the BKP domain?____________What is the difference between “Sleep Now” and “Sleep on Exit” modes?____________What are the wake-up sources from STOP mode?____________STM32F10x Technical Training V0.3Reset and Clock Control (RCC) STM32F10x Technical Training V0.3RESET Sources System RESETResets all registers except someRCC registers and BKP domain SourcesLow level on the NRST pin (ExternalReset)WWDG end of count conditionIWDG end of count conditionA software reset (through NVIC)Low power management ResetFilterV DDR ONPULSEGENERATOR(min 20µs)SYSTEM NRESET NRSTWWDG RESETIWDG RESETSoftware RESETPOR/PDR RESETLow powermanagement RESET ExternalRESETPower RESETResets all registers except BKP domainSourcesPower On/Power down Reset (POR/PDR)The internal voltage regulator is powered offby the application (this occurs when theMCU enters STANDBY mode)Backup domain RESETResets all BKP domainSourcesSetting BDRST bit in RCC BDCR registerVDD or VBAT power on, if both supplieshave previously been powered off.STM32F10x Technical Training V0.3On Chip OscillatorsMultiple clock sources for full flexibility in RUN/Low Power modesHSE (High Speed External oscillator): 4MHz to 16MHz main osc which can be multiplied by the PLL to provide a wide range of frequencies→Can be bypassed with external clockHSI (High Speed Internal RC): factory trimmed internal RC oscillator 8MHz +/-1% over 0-70°C temp rangeFeeds System clock after reset or exit from STOP mode for fast startup (startup time : 2us max)Backup clock in case HSE osc is failingLSI (Low Speed Internal RC): 32KHz internal RC for IWDG and optionally for the RTCused for Auto Wake-Up (AWU) from STOP/STANDBY modeLSE (Low Speed External oscillator): 32.768kHz osc provides a precise time base with very low power consumption (max 1µA). Optionally drives the RTC for Auto Wake-Up(AWU) from STOP/STANDBY mode.→Can be bypassed with external clockSTM32F10x Technical Training V0.3STM32F10x Technical Training V0.3Clock SchemeSystem Clock (SYSCLK) sources✓HSI ✓HSE ✓PLL Configurable dividers provides AHB, APB1/2, ADC and TIM clocksRTC Clock (RTCCLK) sources✓LSE ✓LSI✓HSE clock divided by 128USB Clock (USBCLK) provided from the internal PLLClock Security System (CSS) to backup clock in case of HSE clock failure (HSI feeds the system clock)Enabled by SW w/ interrupt capability linked to Cortex NMIClock-out capability on the MCO pin (PA.08) / max 50MHzTIMxCLKAPB1 Prescaler /1,2,4,8,16AHB Prescaler /1,2 (512)TIM2,3,4 x1, 2 multPCLK1 up to 36MHz TIM1CLKAPB2 Prescaler /1,2,4,8,16TIM1 x1, 2 multPCLK2 up to 72MHzADC Prescaler /2,4,6,8ADCCLK HCLK up to 72MHzUSB Prescaler /1,1.5USBCLK 48MHzCSSHSE OscOSC_OUT OSC_IN4 -16 MHzup to 72MHzSYSCLK x2...x16 PLLPLLCLK HSI RC/2/28MHzSYSCLK HSIHSE PLLCLKMCO/2LSI RC32.768KHz/128LSE OScOSC32_IN OSC32_OUT~32KHzIWDGCLKRTCCLKQuizHow many types of Reset are available?____________What is the maximum AHB, APB1 and APB2 clock frequencies ?____________What are the clock sources that can feed the PLL input?____________What is the purpose of the CSS?____________STM32F10x Technical Training V0.3General Purpose and Alternate FunctionI/O (GPIO and AFIO)STM32F10x Technical Training V0.3GPIO Features80 multifunction bi-directional I/O ports available: 80% IO ratio80 Standard I/Os (5V tolerant, 20 mA drive)18 MHz TogglingConfigurable Output Speed up to 50 MHzUp to 16 Analog InputsAlternate Functions pins (like USARTx, TIMx, I2Cx, SPIx, CAN, USB…)All I/Os can be set-up as external interrupt (up to 16 lines at time)One I/O can be used as Wake-Up from STANDBY (PA.00)One I/O can be set-up as Tamper Pin (PC.13)All Standard I/Os are shared in 5 ports (GPIOA..GPIOE)Atomic Bit Set and Bit Reset using BSRR and BRR registersLocking mechanism to avoid spurious write in the IO registersWhen the LOCK sequence has been applied on a port bit, it is no longer possible to modify theconfiguration of the port bit until the next reset (no write access to the CRL and CRH registerscorresponding bit).STM32F10x Technical Training V0.3STM32F10x Technical Training V0.3GPIO Configuration ModesB i t S e t /R e s e t R e g i s t e r sI n p u t D a t a R e g i s t e rO u t p u t D a t a R e g i s t e rRead / WriteI /O p i nAnalog InputAlternate Function InputAlternate Function OutputTo On-chip PeripheralsFrom On-chip PeripheralsPush-Pull Open Drain TTL Schmitt TriggerOUTPUT CONTROLON VDD_IOVSSVDD_IOVSS ON/OFFON/OFFP u l l -U PP u l l -D o w nVDD_IO VSS OFFInput DriverOutput DriverReadConfiguration ModeCNF1CNF0MOD1MOD0Input Floating (Reset State)01Input Pull-Up 10Input Pull-Down10Output Push-Pull0000: Reserved 01: 10 MHz 10: 2 MHz 11: 50 MHzOutput Open-Drain01AF Push-Pull 10AFOpen-Drain11Analog Input 0000WriteDisabledAFIO FeaturesEvent Out signal generationPulse generation with SEV instruction: to wake-up an other MCU from low powermode through its Event In signalEach IO can be used as Event OutGPIO Software RemappingSome Alternate function can be remapped in two different pins allowing optimization of the pin outAll SWJ-DP I/O pins can be used as GPIOEXTI Lines ConfigurationEach EXTI line is shared with all GPIO ports: EXTI Linexx GPIO[A..E].xxSTM32F10x Technical Training V0.3QuizHow many ports are in the STM32F10x microcontroller ?____________List all the I/O configuration modes____________How many External interrupts and Wake-up pins, exist in the STM32F10x microcontroller?____________List some of the peripherals that have alternate function pins____________What is the purpose of the Event Out Signal____________STM32F10x Technical Training V0.3External Interrupt/Event Controller (EXTI) STM32F10x Technical Training V0.3STM32F10x Technical Training V0.3EXTI FeaturesUp to 19 Interrupt/Events requestsAll GPIO can be used as EXTI line(0..15)EXTI line 16 connected to PVD output EXTI line 17 connected to RTC Alarm eventEXTI line 18 connected to USB Wake-up from suspend eventIndependent trigger (rising, falling, rising & falling) and mask on each interrupt/event lineDedicated status bit for each interrupt lineGeneration of up to 19 software interrupt/event requestsMinimum Pulse Width : < 1*T PCLK2 (Fast APB)Two Configuration mode:Interrupt mode: generate interrupts with external lines edgesEvent mode: generate pulse to wake-up system from WFE and STOP modesEXTI mapped on High Speed APB (APB2) to save time entering in the External Interrupt routineE X T I [15:0]Interrupt MaskRegisterPending RequestRegisterSoftware Interrupt Event RegisterRising Trigger Selection RegisterTo NVICEdge Detect CircuitSynchro Stage FCLKPulse GeneratorFalling Trigger Selection RegisterEvent Mask Register。

STM32F10X的USB固件库说明

6)、usb_endp.c,本文件包含端点收、发送的处理函数,由用户根据不同的USB设备进行不同的定义。

USB的应用软件在这三层上,在不同的USB应用中,用户可能需要对USB固件库的上层部分文件配置进行修改(主要为usb_prop.c何usb_endp.c文件)。而中间层何底层封装的非常好,对

3)、usb_sil.c,本文件包含精简接口的初始化或向端点读写的操作函数。

上层

1)、usb_pwr.c,该文件中包含处理上电、掉电、挂起和恢复事件的函数。

2)、usb_istr.c,该文件中只有一个函数,即USB中断的USB_Istr函数,该函数对各类引起USB中断的事件做轮询处理。

3)、usb_desc.c,该文件包含一些与USB相关的设备描述符、配置描述符等,以数组形式存储,在USB主机请求的时候这些信息将发送给主机。

3)、usb_mem.c,本文件主要负责进行数据传输处理。它主要负责数据在用户区域(内存)或USB数据包缓冲c,本文件主要负责USB协议管理,如USB标准请求、各种端点0的控制信息处理。

2)、usb_init.c,本文件主要包含了USB初始化的函数。

这些文件用户是不需要进行改动的。

最底层

1)、usb_int.c,本文件包含两个中断服务函数CTR_LP()和CTR_HP(),在接收发送中断时使用这两个函数进行处理,这两个函数又调用各个USB端点处理函数,端点处理函数由用户自定义。

2)、usb_regs.c,本文件时硬件抽象层。它含有各种用于读取或设置USB寄存器的函数,相当于对寄存器操作方法的封装。

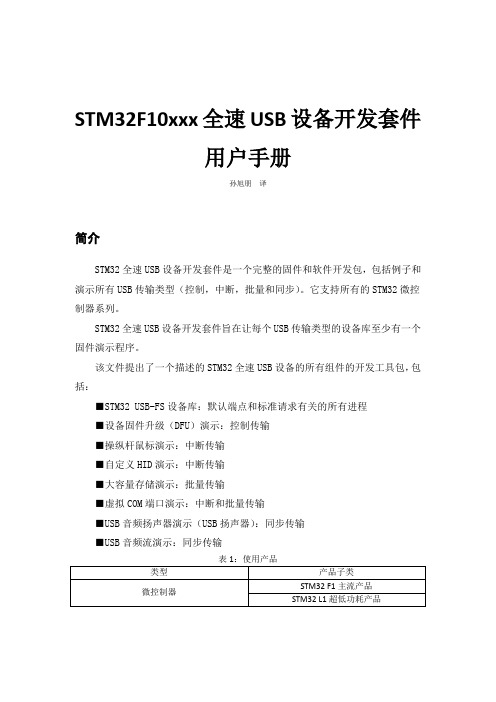

STM32F10xxx全速USB设备开发套件用户手册

STM32F10xxx全速USB设备开发套件用户手册孙旭朋译简介STM32全速USB设备开发套件是一个完整的固件和软件开发包,包括例子和演示所有USB传输类型(控制,中断,批量和同步)。

它支持所有的STM32微控制器系列。

STM32全速USB设备开发套件旨在让每个USB传输类型的设备库至少有一个固件演示程序。

该文件提出了一个描述的STM32全速USB设备的所有组件的开发工具包,包括:■STM32 USB-FS设备库:默认端点和标准请求有关的所有进程■设备固件升级(DFU)演示:控制传输■操纵杆鼠标演示:中断传输■自定义HID演示:中断传输■大容量存储演示:批量传输■虚拟COM端口演示:中断和批量传输■USB音频扬声器演示(USB扬声器):同步传输■USB音频流演示:同步传输表1:使用产品类型产品子类微控制器STM32 F1主流产品STM32 L1超低功耗产品目录简介 0目录 (1)1 STM32微控制器系列综述 (3)2 STM32 USB-FS-设备固件库 (3)2.1 USB应用层次 (4)2.2 USB-FS设备外围接口 (5)2.3 OTG-FS 设备外围接口 (10)2.4 USB-FS设备驱动程序介质层 (13)2.5应用程序接口 (17)2.6使用STM32 USB-FS-设备库实现USB-FS设备应用程序。

(21)3操纵杆鼠标例程 (23)3.1描述 (23)3.2 STM32在挂起模式下的低功耗管理 (24)3.3远程唤醒 (24)4自定义HID例程 (25)4.1描述 (25)4.2描述符的拓扑结构 (25)4.3自定义HID的实现 (26)5大容量存储例程 (27)5.1描述 (27)5.2大容量存储例程概述 (28)5.3大容量存储设备协议 (29)5.4大容量存储例程的实现 (32)5.5如何自定义大容量存储范例 (37)6 虚拟COM端口例程 (40)6.1描述 (40)6.2虚拟COM端口范例方案 (40)6.3软件驱动程序的安装 (41)6.4 实现 (42)7 USB音频扬声器例程 (43)7.1描述 (43)7.2同步传输综述 (43)7.3音频设备类综述 (44)7.4 STM32 USB扬声器范例 (45)8 USB音频流例程 (54)8.1概述 (54)8.2 STM32 USB音频流例程 (55)1 STM32微控制器系列综述在此文件中,STM32是指以下设备:■小容量设备:STM32F101xx,STM32F102xx和STM32F103xx微控制器,flash 大小在16-32KB之间。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Accept

Failed ACK TX (0->0) RX (1) TX (0->1)

Ignore

ACK RX (1) TX (1->0)

Accept

ACK RX (0)

MCU Group Shanghai

29

Packet 格式 (4)

SOP SYNC Packet Content EOP

Packet Identifier PID

8

USB 系统 (4)

主机 连接层 设备

客户端 应用程序 系统端 驱动程序 主机端 控制程序

应用层 应用程序 逻辑层 驱动程序 总线层 控制程序MCU Group Sha来自ghai主机端控制程序:

包括硬件和软件,使 USB设备能够被主机 识别。

9

USB 拓扑结构

高速

480Mbps

USB 2.0

主机

带宽 方向

端点号

错误处理

MCU Group Shanghai

最大包长度

13

USB 类 (1)

音频类 (Audio) 通信类-虚拟串口类 (CDC) 设备固件升级类 (DFU) 人机接口类 (HID) 大容量存储设备类 (Mass Storage)

/developers/devclass_docs#a pproved

Reject

NAK TX (0->0) RX (0) TX (0->1)

Accept

ACK RX (1)

MCU Group Shanghai

28

Packet 格式 (3) -- Data PID Toggle(3)

Data Toggle 用于数据的同步和重发

当ACK的传输被破坏

DATA0 TX (0) RX (0->1) TX (0) DATA0 RX (1) TX (1) DATA1 RX (1->0)

21

USB 信号 (3)

数据的编码 / 解码: 反向不归零码(NRZI)

Data NRZI

Idle 0 1 1 0 1 0 1 0 0 0 1 0 0 1 1 0

Idle K K K J J K K J K J J K J J J K

Bit 填充: 在数据进行NRZI编码前,每6个连续的1信号之后都会插 入1个0信号,以免丢失同步。

MCU Group Shanghai

实际的通信信道 逻辑上的信道

实现的核心区域

6

USB 系统 (2)

主机 连接层

应用程序:

应用程序运行于USB设 备所连接的主机上。 部分应用程序会由主机 的操作系统提供,大部 分的应用程序由USB设 备的供应商提供。

设备

客户端 应用程序 系统端 驱动程序 主机端 控制程序

MCU Group Shanghai

14

USB 类 (2)

智能卡接口设备类 (CCID) 图像类 (Image) IrDA桥接设备类 (IrDA Bridge) 监视设备类 (Monitor) 个人保健设备类 (Personal Health Care) 电源设备类 (Power Device) 物理接口设备类 (Physical Interface) 打印设备类 (Printer) 视频类 (Video) 测试测量类 (Test & Measurement)

挂起模式

高功耗设备的挂起模式:

在此模式下,耗电最多不能超过2.5mA。

低功耗设备的挂起模式:

在此模式下,耗电最多不能超过500uA。

MCU Group Shanghai

17

USB 连接器(1) – Standard / Mini

Standard A Plug Standard B Plug Mini B Plug

SOP (Start of Packet): 数据线从IDLE状态切换到K状态 EOP (End of Packet ): 持续2位时间的SE0信号,后跟随1位时间的J状态。 SYNC: 3个重复的KJ状态切换,后跟随2位时间的K状态,共 持续8位时间。 (低速/全速设备) Idle K J K J K J K K MCU Group Shanghai

Standard A Receptacle

Standard B Receptacle

MCU Group Shanghai

Mini B Receptacle

18

USB 连接器 (2) -- Micro

Micro A Plug

Micro B Plug

Micro AB Receptacle

Micro B Receptacle

地址

LSB

帧号

数据

MSB

CRC

MCU Group Shanghai

24

Packet 格式 (2)

SOP SYNC Packet Content EOP

PID

地址

帧号

数据

CRC

MCU Group Shanghai

25

Packet 格式 (3)

SOP SYNC Packet Content EOP

Packet Identifier PID

协同PC产业 协议易于实现和整合,并支持热插拔机制 低成本实现 低成本的电缆和连接插座,商品化的实现技术 易于升级 整体结构易于升级,能适应各类新生的应用。

MCU Group Shanghai

5

USB 系统 (1)

主机 连接层 设备

客户端 应用程序 系统端 驱动程序 主机端 控制程序

应用层 应用程序 逻辑层 驱动程序 总线层 控制程序

MCU Group Shanghai

19

USB 信号 (1)

电缆:

差分信号:

1: D+ > VOH (2.8V)and D- < VOL(0.3V) 0: D- > VOH and D+ < VOL Low Speed: Full Speed: Low Speed: Full Speed: Differential 0 Differential 1 Differential 1 Differential 0

MCU Group Shanghai

22

USB 数据格式

Transfer Transfer Transfer

Transaction

Transaction

Transaction

Packet

Packet

Packet

MCU Group Shanghai

23

Packet 格式 (1)

SOP SYNC Packet Content EOP

MCU Group Shanghai

26

Packet 格式 (3) -- Data PID Toggle(1)

Data Toggle 用于数据的同步和重发

正确的数据传输流程

DATA0 TX (0) RX (0->1) TX (1) DATA1 RX (1->0)

Accept

ACK TX (0->1) RX (1) TX (1->0)

MCU Group Shanghai

15

供电 (1)

USB设备按供电类别分:

主hub: 直接连接到USB主机控制器,与主机控制器使用同一供电电源,为下游

端口提供1个单位(100mA)-5个单位(500mA)的供电。

总线供电类hub: 从上游端口取电,为自身及其下游设备供电。 自供电hub: 从外部电源取电,为自身及其下游设备供电。 低功耗总线供电类设备: 所有的耗电都从上游总线获取,在任意时刻的

总线层 控制程序

MCU Group Shanghai

11

USB 逻辑部件 (1)

设备

接口 端点 接口: 接口用于描述特定的功能,每个接口都有一个端点集,用于实现接口 功能。 MCU Group Shanghai

12

USB 逻辑部件 (2)

主机 缓存 应用程序 缓存

设备

接口 端点

端点: 通信频率 传输类型

MCU Group Shanghai

3

技术背景(2)

应用范围 性能

低速:

交互式设备 10-100kbps

应用

键盘,鼠标 手写笔 游戏手柄 虚拟设备 外设 话音 宽带 音频 麦克风

特性

•极低的成本 •易于使用 •热插拔 •同时使用多个外设 •较低的成本 •易于使用 •热插拔 •同时使用多个外设 •可保证的带宽 •可保证的延迟 •低成本 •易于使用 •热插拔 •同时使用多个设备 •可保证的带宽 •可保证的延迟 •高带宽

全速:

电话,音频类 压缩的视频类 500kbps – 10Mbps

高速:

视频,大容量存储 25 – 400Mbps

视频 大容量存储 图像 宽带

MCU Group Shanghai

4

技术背景(3)

特性:

简单易用 使用统一制式的电缆和连接插座,支持热插拔。 应用广泛 支持从几kbps到几百Mbps的数据带宽,支持同步 和异步的传输,支持连接多达127个设备,并支持复合设备。 同步带宽 使用灵活 鲁棒性佳 提供保证的带宽和低延迟。 支持不同大小的数据包和各种传输速率。 多种的错误校验和恢复机制。

MCU Group Shanghai

J状态:

K状态:

20

USB 信号 (2)

SE0 (Single-ended0): SE1 (Single-ended1): D+ and D- < VOL D+ and D- > VSE1(0.8V)

复位 (Reset): 恢复 (Resume):