实验二编码器译码器及数码显示电路的设计与调试.ppt

译码器和编码器.ppt

优先编码器 优先编码器是数字系统中实现优先权管理的一个重要逻辑部件。 没有普通编码器的输入使用限制 编码群输出端

使能端 扩展端

权值由高到低

反 码 输 出

例7.7 由148构成16级不同中断请求的中断优先编码器

2

1

7.1.3 多路选择器和多路分配器 功能:完成对多路数据的选择与分配、在公共传输线上实现多路 数据的分时传送。

7.1.2 译码器和编码器

编码器:对输入信号按一定规律进行编排,使每组输出代码具 有一特定的含义. 译码器:对具有特定含义的输入代码进行“翻译”,将其转换 成相应的输出信号.

1、译码器

常见译码器:二进制译码器、二-十进制译码器和数字显示译 码器。

二进制译码器有n 个输入

如:74ls138、T4138等

典型计数器实例之1------T4193(4位二进制同步可逆计数器)

高电平有效清零端 低电平有效预制端

上升沿触发

异步清零

异步置数

同步计数 计数器的作用是不但可以用来计数,还可以构成分频器,一 个二进制计数器还可以用来构成任意进制的计数器

一、用193构成小于16进制的计数器

A、构成模10加法计数器 模10加法计数器的状态图如图

193有16个不同的计数状态,如何使其在第十个状态时 就回到初始状态

反馈清零法

B、构成模12减法计数器

初始状态为1111,如何构成电路?

反 馈 置 数 法

一、用193构成大于16进制的计数器

Q Q Q Q Q Q Q Q Q CC A B C D CB A B C DQ

典型计数器实例之2------74LS161(4位二进制同步计数器)

寄存器实例之一:T1194 见书P242

数字电子技术实验报告2

实验成绩实验日期指导教师批阅日期实验名称编码译码与显示1、实验目的掌握编码器、译码器与显示器的工作原理、测试方法以及应用。

2、实验原理编码器、译码器是数字系统中常用的逻辑部件,而且是一种组合逻辑电路。

1.编码器把状态或指令等转换为与其对应的二进制代码叫编码,例如可以用四位二进制所组成的编码表示十进制数0~9,把十进制数的0编成二进制数码0000,把十进制数的5编成二进制数码0101等。

完成编码工作的电路.通称为编码器。

2.译码器译码是编码的逆过程。

译码器的作用是将输入代码的原意“翻译”出来。

译码器的种类较多,如:最小项译码器(3线/8线、4线/16线译码器等)b、七段字形译码器等。

七段字形译码器,其作用是将输入的四位BCD码D、C、B、A翻译成与其对应的七段字形输出信号,用于显示字形。

常用的七段字形译码器有TTL的:T338(OC输出),74LS48、74LS248(内部带有上拉电阻)CMOS的:CD4511、MC14543、MC14547等。

3.显示器(1)发光二极管(LED)。

把电能转换成可见光(光能)的一种特殊半导体器件,其构造与普通PN 结二极管相同。

(2)LED显示器。

用LED构成数字显示器件时,需将若干个LED按照数字显示的要求集成- -个图案,就构成LED显示器(俗称“数码管”)。

3、实验步骤(1)按图连线,按表顺序给8线/3线优先编码器CD4532的信号输入端送入相应电平,将结果填入表中,与CD4532的功能表相对照,检查是否符合优先顺序以及编码结果是否正确。

注意:输入由逻辑开关给定。

输出连接逻辑电平指示。

(2)根据CD4532和CD4511的管脚图和功能表,自行设计连线,将编码器CD4532的输出端接到译码器CD4511的数据输入端,将CD4511的输出接七段显示数码管。

检查编码器与数字显示是否一致,若不一致,分析原因,检查故障并排除之,将结果填表。

(3)将十进制计数器/脉冲分配器CD4017接成八进制,用单次脉冲或1Hz脉冲信号检查CD4017的逻辑功能是否正常。

实验二编码器、译码器及数码显示电路的设计与调试

VCC Y0

74LS138 C 3 B 2 A 1 G2A G2B G1 4 5 6 GND 8

K1

K2

K3

K5

K6

K7

Âß¼¿ª¹Ø

74LS138 3-8 线译码器实验电 路

(2)8线-3线优先编码器逻辑功能验证

8线-3线编码器功能表

输入 E1

输出 QC QB QA GS E0

01234567 xxxxxxxx 11111111 xxxxxxx0 xxxxxx01 xxxxx011

三、实验原理(续)

2.译码器 译码器也是组合电路的一部分。所谓译码,就是把 代码的特定含义“翻译”出来的过程,而实现译码操作 的电路称为译码器。译码器分成三类: (1)二进制译码器:如中规模2-4线译码器 74LS139,3-8线译码器74LS138等。 (2)二-十进制译码器:实现各种代码之间的转换,如 BCD码-十进制译码器74LS145等。 (3)显示译码器:用来驱动各种数字显示器,如共阴 数码管译码驱动74LS48(或74LS248)共阳数码管 译码驱动74LS47(或74LS247)等。

S使能输入端, 低电平有效, 表示编码器正 常工作

YS I 0 I1 I 2 I 3 I 4 I 5 I 6 I 7 S

YEX =YS S

扩展输出端,代表电路工 作且有输入信号” 使能输出端,代表 电路工作但无输入 信号

芯片引脚图

2线---4线译码器

74LS138管脚功能及定义图

其工作原理如下:①当一个选 通端(E1)为高电平,另两个 选通端((/E2))和/(E3))为 低电平时,可将地址端①当一 个选通端(E1)为高电平,另 两个选通端((/E2))和/(E3)) 为低电平时,可将地址(A0、 A1、A2)的二进制编码在Y0 至Y7对应的输出端以低电平译 出。比如:A2A1A0=110时, 则Y6输出端输出低电平信号7接4位拨动开关 8 9

数电实验二

数电实验二实验二:组合逻辑电路(MSI和设计)一、实验目的:1、了解集成编码器74HC148、译码器74HC138、集成数据选择器74HC151、加法器74HC283、数值比较器74HC85的管脚排列和管脚功能、性能及使用方法;2、掌握用SSI小规模集成器件设计组合逻辑电路的方法,用实验验证所设计电路的功能;3、掌握用MSI中规模集成器件设计组合逻辑电路的方法,用实验验证所设计电路的功能。

二、知识点提示:1、组合逻辑电路的设计方法(1)首先根据给出的实际逻辑问题进行逻辑设计,将给定的因果关系进行逻辑抽象,列出逻辑真值表;(2)根据真值表写出相对应的逻辑表达式,并化成适合的形式; (3)选定集成器件类型;(应该根据电路的具体要求和器件的资源情况来决定) (4)再根据逻辑表达式,画出逻辑电路图;(5)在逻辑电路图上标出对应器件管脚号,然后进行接线,实验验证其设计功能。

2、中规模集成器件电路特点中规模集成器件多数是专用的功能器件,具有某种特定的逻辑功能,可以使用这些功能器件实现组合逻辑函数,方法是逻辑函数对比法。

具体设计方法见教材。

三、实验原理:1、MSI中规模集成电路的管脚图和功能表,及使用说明。

①译码器(74HC138)一个n变量的译码器的输出包含了n变量的所有最小项。

例如,3线/8线译码器(74HCl38)8个输出包含了3个变量的全部最小项的译码。

用n变量译码器加上输出与非门电路,就能获得任何形式的输入变量不大于n的组合逻辑电路。

74LSl38是3-8线译码器,其外引脚排列如图2-1所示。

74HCl38译码器有3个使能端S1、S2、S3,当S1=l、S2=0、S3=0时允许译码,否则禁止译码,且A2、A1、A0为3个地址输入端,Y0、Y1、Y2、Y3、Y4、Y5、Y6、Y7为8个输出端。

注:74HCl38的功能表见教材P176。

图2-1 74HC138引脚排列图1②优先编码器(74HC148)74HC148是8-3线优先编码器,其外引线排列如图2-2所示。

器件译码器编码器及数码管显示实验报告

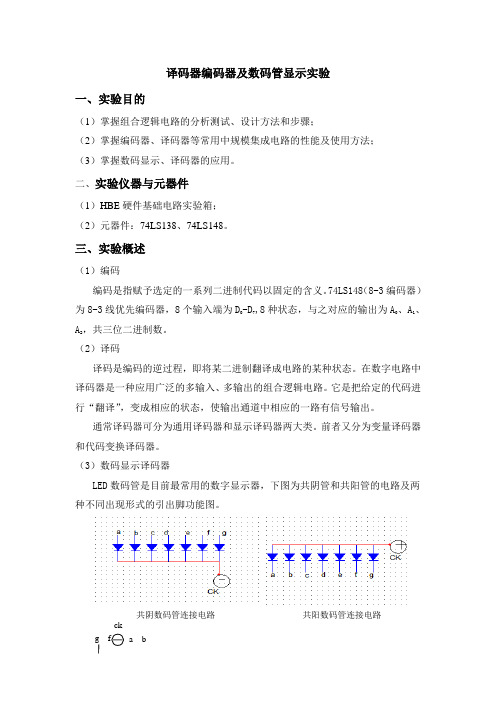

ck a b g f 译码器编码器及数码管显示实验一、实验目的(1)掌握组合逻辑电路的分析测试、设计方法和步骤;(2)掌握编码器、译码器等常用中规模集成电路的性能及使用方法; (3)掌握数码显示、译码器的应用。

二、实验仪器与元器件 (1)HBE 硬件基础电路实验箱; (2)元器件:74LS138、74LS148。

三、实验概述(1)编码编码是指赋予选定的一系列二进制代码以固定的含义。

74LS148(8-3编码器)为8-3线优先编码器,8个输入端为D 0-D 7,8种状态,与之对应的输出为A 0、A 1、A 2,共三位二进制数。

(2)译码译码是编码的逆过程,即将某二进制翻译成电路的某种状态。

在数字电路中译码器是一种应用广泛的多输入、多输出的组合逻辑电路。

它是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

通常译码器可分为通用译码器和显示译码器两大类。

前者又分为变量译码器和代码变换译码器。

(3)数码显示译码器LED 数码管是目前最常用的数字显示器,下图为共阴管和共阳管的电路及两种不同出现形式的引出脚功能图。

共阴数码管连接电路 共阳数码管连接电路a b e d c h cka b g f a b e d c hckck共阴极符号及引脚功能 共阳极符号及引脚功能四、实验内容1.测试变量译码器的逻辑功能(1)根据74LS138的逻辑,写出各输出端的逻辑表达式,列出真值表,根据真值表对逻辑电路进行测试,验证其功能。

由图2-6-3可知逻辑表达式:Y 0=ABC ,Y 1=ABC ,Y 2=ABC ,Y 3=ABC ,Y 4=ABC ,Y 5=ABC ,Y 6=ABC ,Y 7=ABC 。

真值表: A B C Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7 0 0 0 0 1 1 1 1 1 1 1 0 0 1 1 1 1 1 0 1 1 1 0 1 0 1 1 0 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 11111111a b gchdef a bgch def1 0 1 1 1 1 1 1 0 1 11 1 0 1 1 1 0 1 1 1 11 1 1 1 1 1 1 1 1 1 0分析:由于A、B、C之间是与、非的关系,对于不同的A、B、C的值,只会有一种情况是0。

译码器及其应用实验 ppt课件

译码器及其应用实验

2、功能测试 ➢ 将地址和使能端与逻辑开关连接,输出端与电平

指示连接。按上表逐项测试74LS138的逻辑功能。

译码器及其应用实验

Y0G1G2AG2BA2A1A0 A2A1A0 m 0

二、实验仪器及元器件 1、数电实验箱 3、元器件 :

74LS138(译码器)

2、数字万用表

74LS20(四输入端双与非门)

74LS153(双4选1数据选择器)

译码器及其应用实验

三、实验内容

(一)74LS138功能测试

1、简介 ➢ 74LS138为双列直插16脚3-8

线译码器,引脚及功能表见右 。 ➢ 使能端:G1=1,使能;G1=0,

译码器及其应用实验

Y0G1G2AG2BA2A1A0 A2A1A0 m 0

3、应用电路 ➢ (1)产生逻辑函数 用1片74LS138和基本逻辑门产生函数(电路自拟

L1ACAB CABC

L3ABABCA译BC 码器及其应用实验

四、实验报告 1.写出电路设计过程,画出实验内容3、4的

接线图。 2.设计出对应电路,对实验结果进行分析、

(3).分析上述实验结果并总结数据选择器作用。

译码器及其应用实验

4-16译码器参考电路

2.实现组合逻辑电路 例4.2.1 试用译码器和门电路实现逻辑函数:

LA BB CAC

解:将逻辑函数转换成最小项表达式,

L

再转换成与非—与非形式。

&

LA B C A B CAC B ABC

=m3+m5+m6+m7

编码、译码显示电路的设计与安装实验报告

《编码、译码显示电路设计与安装》实验报告姓名欧阳志刚学号20101138班级通信101专业通信技术指导教师林梅实验时间第8周电子信息工程系2011-2012学年第一学期实验目的及原理:1.了解编码译码器的功能和特点。

2.掌握编码译码器的工作原理。

3.掌握集成编码译码器的逻辑功能。

4.掌握集成编码译码器的级联方法。

实验一 编码器一、实验目的和任务:⑴验证编码器的逻辑功能。

(2)掌握中规模集成电路构成组合逻辑电路的方法。

二、实验设备与器材:TTL 集成编码器芯片74LS148等74LS148编码器I0~I7是8个输入端,Y1~Y3是3个输出端,EI 是使能输入端,EO 是使能输出端,GS 是优先标志输出端。

按下表逐项测试74LS148的逻辑功能。

74LS148管脚排列图:14131210161534567128911V CC GND74LS1484I 5I 6I 7I I E 2Y 1Y 0Y 0I 1I 3I 2I SG O E 4I 5I 6I 7I IE 2Y 1Y 0Y 0I 1I 2I 3I S G O E74LS148的功能表:输入输出S ’’I0”I1’’I2’’I3’’I4’’I5’’I6’’I7’’Y0" Y1" Y2" Ys’’Y EX’’1 X X X X X X X X 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 0 1 0 X X X X X X X 0 0 0 0 1 0 0 X X X X X X 0 1 0 0 1 1 0 0 X X X X X 0 1 1 0 1 0 1 0 0 X X X X 0 1 1 1 0 1 1 1 00 X X X 0 1 1 1 1 1 0 0 1 0 0 X X 0 1 1 1 1 1 1 0 1 1 0 0 X 1 1 1 1 1 1 1 1 1 1 1 0 0 0 1 1 1 1 1 1 1 1 1 1 1 0三、实验步骤及内容:(1)74LS148编码器I0~I7是8个输入端,Y1~Y3是3个输出端,EI 是使能输入端,EO是使能输出端,GS是优先标志输出端。

译码器与编码器的设计与仿真实验报告

译码器与编码器的设计与仿真一、实验内容1、参照芯片74LS138的电路结构,用逻辑图与VHDL语言设计3—8译码器。

2、参照芯片74LS148的电路结构,用逻辑图与VHDL语言设计8—3优先编码器。

3、应用MaxplusII软件对译码器与编码器进行编译、仿真和模拟。

4、能更加熟练的掌握应用MaxplusII软件,从而更形象更深层次的理解译码器与编码器。

二、实验平台及实验方法用VHDL语言编写编码器与译码器的程序,运用MaxplusII 软件进行仿真,再结合FPGA(即对实验箱的芯片进行编译)进行验证。

也可以用原理图进行文本设计,波形设计。

三、实验过程1.启动MaxplusII软件;2.新建一个文本编辑文件,输入全加器的VHDL语言;3.编译。

点击file→save as,保存文件名为V74x148名称,扩展名为vhd,选择芯片类型为EPF10K20TI144-4,保存并进行编译,若编译结果出现0 error,0 warnings则说明编译通过。

4.仿真波形。

点Max+plus II→Waveform editor,出现波形图的设置界面,然后点Node→Enter Nodes from SNF→list,将输入输出端添加到界面,并设置其周期和输入波形,保存后,点Max+plusII→Simulator,即可仿真出输出的波形。

5.配置芯片。

点Max+plus II→Floorplan editor,将Unassigned Nodes & 栏中,电路的输入输出节点标号直接用鼠标“拖到” 想分配的引脚上,Max+plusII→programmer→configuer,然后就可以操作试验箱,观察全加器的工作情况。

四、实验结果实验步骤:1、用VHDL语言编写编码器的程序2、将上述程序保存为文件名为V74x148的文件,点击Maxplus里的compiler进行编译,点击start,如果出现0 error,0 warnings,则编译成功。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(3)优先编码器:如8-3线优先编码器74LS148等

三、实验原理(续)

2.译码器 译码器也是组合电路的一部分。所谓译码,就是把

代码的特定含义“翻译”出来的过程,而实现译码操作 的电路称为译码器。译码器分成三类: (1)二进制译码器:如中规模2-4线译码器 74LS139,3-8线译码器74LS138等。 (2)二-十进制译码器:实现各种代码之间的转换,如 BCD码-十进制译码器74LS145等。 (3)显示译码器:用来驱动各种数字显示器,如共阴 数码管译码驱动74LS48(或74LS248)共阳数码管 译码驱动74LS47(或74LS247)等。

(1)将二进制2-4线译码器74LS139插入IC空插座中, 管脚排列图见上图。输入端G、A、B接逻辑开关,输出端 Y0、Y1、Y2、Y3 接LED发光二极管,接通电源,按表输 入各逻辑电平,观察输出结果并填入表中。

(2)将共阴极BCD7七段 译码器/驱动器 74LS48(74LS248)和共阴 极数码管LC501111(547R)插入IC空插座中, 按图接线,接通电源后,观 察LED发光二极管,看显示 的结果是否与拨码开关指示 的数据一致。

译码显示电路

0 11111111

0 xxxxxxx0

0 xxxxxx01

0 xxxxx011

0 xxxx0111

0 xxx01111

0 xx011111

0 x0111111

0 01111111

2、译码器逻辑功能验证

表 74LS139 2-4线3

1xx 000 001 010 011

图 10线-4线优先编码器实验原理图

表 十进制--BCD优先编码器功能表

输入

123456789

111111111 xxxxxxxx0 xxxxxxx01 xxxxxx011 xxxxx0111 xxxx01111 xxx011111 xx0111111 x01111111

输出

QD QC QB QA 1111

(2)将8线-3线优先 编码器74LS148集成 片插入IC空插座中,按 上述同样方法进行实 验论证。管脚排列图 见图。按表输入各逻 辑电平,观察输出结果 并填入表中。

8线-3线编码器功能表

输入

输出

E1 0 1 2 3 4 5 6 7 QC QB QA GS E0 1 xxxxxxxx 1 1 1 1 1

1.编码器实验

编码器也是组合电路的一部分。编码器就是实现

编码操作的电路,编码实际上是译码相反的过程。按照

被编码信号的不同特点和要求,编码器分成三类:

(1)二进制编码器:如用门电路构成的4-2线,8-3线 编码器等。

(2)二--十进制编码器:将十进制的0 ~ 9编成BCD 码,如:10线十进制-4线BCD码编码器74LS147等。

编码器、译码器及数码显示电路的设计与调试

一、实验目的

1、验证编码器、译码器的逻辑功能 2、掌握常用编码器、译码器的典型应用

二、实验仪器和设备

数字实验箱

芯片

74LS248 74LS147 74LS148等

74LS248芯片引脚图

芯片引脚图

芯片引脚图

芯片引脚图

芯片引脚图

三、实验原理

四、实验内容

1、优先编码器逻辑功能验证 2、译码器逻辑功能验证

1、优先编码器逻辑功能验证

(1)将10线-4线(十进制 -BCD码)优先编码器 74LS147集成电路芯片插 入IC空插座中。按图接线, 其中输入端1~9通过逻辑 电平开关接高低电平(设开 关打开为1、关闭为0), 输出端QD、QC、QB、QA接 逻辑电平显示。接通电源后, 按表输入各个逻辑电平,观 察输出结果并填入表中。