组成原理课程第六章

计算机组成原理第六章课件白中英版

66MHz的Pentium,基本非流水线总线周期

64÷2×66×106 bps=264 MB/S

66MHz的Pentium,2-1-1-1猝发读周期

32÷5×66×106 B/S=422.4 MB/S

【例1】(1)某总线在一个总线周期中并行传送4个字 节的数据,假设一个总线周期等于一个总线时钟周期, 总线时钟频率为33MHz,则总线带宽是多少?

STROBE*(选通)信号

•输出低有效,才能使打印机接收数据

ACK*(响应)信号

•打印机接收数据结束回送负脉冲响应信号

BUSY(忙状态)信号

•打印机忙于处理接收到的数据,不能接收新的数据

6.3.3 总线数据传送模式

读数据传送:数据由从设备到主设备 写数据传送:数据由主设备到从设备 猝发传送(数据块传送)

演示

每个数据位都需要单独一条传输线。二进制数 “0”或“1”在不同的线上同时进行传送

串行通信

串行通信:将数据分解成二进制位用一条信号 线,一位一位顺序传送的方式

串行通信的优势:用于通信的线路少,因而在 远距离通信时可以极大地降低成本

通信协议(通信规程):收发双方共同遵守

解决传送速率、信息格式、位同步、字符同步、 数据校验等问题

发送8位数据:59H=01011001B,偶校验、两个停止位

6.3.1 总线的仲裁

主设备(Master):控制总线完成数据传输 从设备(Slave):被动实现数据交换 总线仲裁:决定当前控制总线的主设备

•集中仲裁:中央仲裁器负责 •分布仲裁:比较各个主设备仲裁号决定

某一时刻,只能有一个主设备控制总线, 其它设备此时可以作为从设备

计算机组成原理第六章第3讲总线的仲裁

(4)由于参加竞争的各设备速度不一致,这个比较过程反 复(自动)进行,才有最后稳定的结果。竞争期的时间要

13 足够,保证最慢的设备也能参与竞争。

7

6.3 总线的仲裁

8

6.3 总线的仲裁

➢ 工作方式:

在独立请求方式中,每一个共享总线的设备均 有一对总线请求线BRi和总线授权线BGi。当设 备要求使用总线时,便发出该设备的请求信号。 总线仲裁器中有一个排队电路,它根据一定的 优先次序决定首先响应哪个设备的请求,给设 备以授权信号BGi。

独立请求方式的优点是响应时间快 对优先次序的控制相当灵活

➢ 优点:线路可靠性高(个别仲裁故障不会影响整 个系统)

➢ 缺点:设计复杂

12

6.3 总线的仲裁

(1)所有参与本次竞争的各主设备将设备竞争号CN取反后 打到仲裁总线AB上,以实现“线或”逻辑。AB线低电平 时表示至少有一个主设备的CNi为1,AB线高电平时表示 所有主设备的CNi为0。

(2)竞争时CN与AB逐位比较,从最高位(b7)至最低位 (b0)以一维菊花链方式进行,只有上一位竞争得胜者 Wi+1位为1。当CN i=1,或CNi=0且ABi为高电平时,才 使Wi位为1。若Wi=0时,将一直向下传递,使其竞争号后 面的低位不能送上AB线。

每次计数可以从“0”开始,也可以从中止点开发始。如 果从“0”开始,各设备的优先次序与链式查询法相同, 优先级的顺序是固定的。如果从中止点开始,则每个 设备使用总线的优级相等。

6

6.3 总线的仲裁

➢ 优点

计数器的初值也可用程序来设置,这可以方便 地改变优先次序。

计算机组成原理第六章答案

1. 写出下列各数的原码、反码、补码、移码(用8位二进制表示),其中MSB是最高位(符号位),LSB是最低位。

如果是小数,则小数点在MSB之后;如果是整数,则小数点在LSB之后。

(1)-59/64 (2)27/128 (3)-127/128(4)用小数表示-1(5)用整数表示-1 (6)-127 (7)35 (8)-1282. 设[x]补=x0.x1x2x3x4,其中x i取0或1,若要使x>-0.5,则x0、x1、x2、x3、x4的取值应满足什么条件?3. 若32位定点小数的最高位为符号位,用补码表示,则所能表示的最大正数为,最小正数为,最大负数为,最小负数为;若32位定点整数的最高位为符号位,用原码表示,则所能表示的最大正数为,最小正数为,最大负数为,最小负数为。

4. 若机器字长为32位,在浮点数据表示时阶符占1位,阶码值占7位,数符占1位,尾数值占23位,阶码用移码表示,尾数用原码表示,则该浮点数格式所能表示的最大正数为,最小正数为,最大负数为,最小负数为。

5. 某机浮点数字长为18位,格式如图2.35所示,已知阶码(含阶符)用补码表示,尾数(含数符)用原码表示。

(1)将(-1027)10表示成规格化浮点数;(2)浮点数(0EF43)16是否是规格化浮点数?它所表示的真值是多少?图2.35 浮点数的表示格式6. 有一个字长为32位的浮点数,格式如图2.36所示,已知数符占1位;阶码占8位,用移码表示;尾数值占23位,尾数用补码表示。

图2.36 浮点数的表示格式请写出:(1)所能表示的最大正数;(2)所能表示的最小负数;(3)规格化数所能表示的数的范围。

7. 若浮点数x的IEEE754标准的32位存储格式为(8FEFC000)16,求其浮点数的十进制数值。

8. 将数(-7.28125)10转换成IEEE754标准的32位浮点数的二进制存储格式。

9. 已知x=-0.x1x2…x n,求证:[x]补=+0.00…01。

计算机组成原理第6章 习题

第六章复习题1.若浮点数用补码表示,则判断运算结果是否为规格化数的方法是______。

A 阶符与数符相同为规格化数B 阶符与数符相异为规格化数C 数符与尾数小数点后第一位数字相异为规格化数D数符与尾数小数点后第一位数字相同为规格化数2.下面浮点运算器的描述中正确的句子是:______。

A. 浮点运算器可用阶码部件和尾数部件实现B. 阶码部件可实现加、减、乘、除四种运算C. 阶码部件只进行阶码相加、相减操作D. 尾数部件只进行乘法和减法运算3.IEEE754标准规定的32位浮点数中,符号位为1位,阶码为8位,则它所能表示的最大规格化正数为______。

A.+(2 – 2-23)×2+127B.+(1 – 2-23)×2+127C.+(2 – 2-23)×2+255D.2+127 + 2274.如果浮点数用补码表示,则判断下列哪一项的运算结果是规格化数______。

A 1.11000B 0.01110C 1.00010D0.010105.______表示法主要用于表示浮点数中的阶码。

A.原码B.补码C.反码D.移码6.(√)移码表示法主要用于表示浮点数的阶码E,以利于比较两个指数的大小和对阶操作。

7.(×)浮点运算器阶码部件可实现加、减、乘、除四种运算。

8.(√)浮点运算器阶码部件可实现加、减和比较操作。

9.(√)按IEEE754标准,一个浮点数由符号位S,阶码E,尾数m三部分组成。

10.(×)按IEEE754标准,阶码E的值等于指数的基值E加上一个固定偏移量128。

1.有一个字长为32位的浮点数,符号位1位,阶码8位,用移码表示;尾数23位,用补码表示;基数为2。

请写出:(1)最大数的二进制表示;(2)最小数的二进制表示;(3)规格化数所能表示的数的范围;(4)最接近于零的正规格化数与负规格化数。

解:•最大正数值是由尾数的最大正数值与阶码的最大正数值组合而成的;•最小正数值是由尾数的最小正数值与阶码的最小负数值组合而成的。

计算机组成原理第六章-第5讲-HOST总线和PCI总线复习课程

本章小结

➢ 当代流行的标准总线追求与结构、CPU、技术无关的开发标准。 其总线内部结构包含: ①数据传送总线(由地址线、数据线、控制线组成); ②仲裁总线; ③中断和同步总线; ④公用线(电源、地线、时钟、复位等信号线)。

在异步定时中,总线周期的长度是可变的。当代的 总线标准大都能支持以下数据传送模式:①读/写操 作;②块传送操作;③写后读、读修改写操作;④ 广播、广集操作。

返回

16

本章小结

➢ PCI总线是当前实用的总线,是一个高带宽且 与处理器无关的标准总线,又是重要的层次总 线。它采用同步定时协议和集中式仲裁策略, 并具有自动配置能力。PCI适合于低成本的小 系统,因此在微型机系统中得到了广泛的应用。

返回

15

本章小结

➢ 总线定时是总线系统的又一核心问题之一。为 了同步主方、从方的操作,必须制订定时协议, 通常采用同步定时与异步定时两种方式

在同步定时协议中,事件出现在总线上的时刻由总 线时钟信号来确定,总线周期的长度是固定的。

在异步定时协议中,后一事件出现在总线上的时刻 取决于前一事件的出现,即建立在应答式或互锁机 制基础上,不需要统一的公共时钟信号。

6.5 HOST总线和PCI总线

五、总线仲裁 ➢ PCI总线采用集中式仲裁方式,每个PCI主

设备都有独立的REQ#(总线请求)和 GNT#(总线授权)两条信号线与中央仲裁 器相连。由中央仲裁器根据一定的算法对 各主设备的申请进行仲裁,决定把总线使 用权授予谁。但PCI标准并没有规定仲裁算 法。

10

➢ 总线仲裁是总线系统的核心问题之一。为了解决多个主设备同 时竞争总线控制权的问题,必须具有总线仲裁部件。它通过采 用优先级策略或公平策略,选择其中一个主设备作为总线的下 一次主方,接管总线控制权。按照总线仲裁电路的位置不同: 集中式仲裁:仲裁方式必有一个中央仲裁器,它受理所有功 能模块的总线请求,按优先原则或公平原则。 分布式仲裁。分布式仲裁不需要中央仲裁器,每个功能模 块都有自己的仲裁号和仲裁器。

计算机组成原理(蒋本珊)第六章

第六章1.控制器有哪几种控制方式?各有何特点?解:控制器的控制方式可以分为3种:同步控制方式、异步控制方式和联合控制方式。

同步控制方式的各项操作都由统一的时序信号控制,在每个机器周期中产生统一数目的节拍电位和工作脉冲。

这种控制方式设计简单,容易实现;但是对于许多简单指令来说会有较多的空闲时间,造成较大数量的时间浪费,从而影响了指令的执行速度。

异步控制方式的各项操作不采用统一的时序信号控制,而根据指令或部件的具体情况决定,需要多少时间,就占用多少时间。

异步控制方式没有时间上的浪费,因而提高了机器的效率,但是控制比较复杂。

联合控制方式是同步控制和异步控制相结合的方式。

2.什么是三级时序系统?解:三级时序系统是指机器周期、节拍和工作脉冲。

计算机中每个指令周期划分为若干个机器周期,每个机器周期划分为若干个节拍,每个节拍中设置一个或几个工作脉冲。

3.控制器有哪些基本功能?它可分为哪几类?分类的依据是什么?解:控制器的基本功能有:(1)从主存中取出一条指令,并指出下一条指令在主存中的位置。

(2)对指令进行译码或测试,产生相应的操作控制信号,以便启动规定的动作。

(3)指挥并控制CPU 、主存和输入输出设备之间的数据流动。

控制器可分为组合逻辑型、存储逻辑型、组合逻辑与存储逻辑结合型3类,分类的依据在于控制器的核心———微操作信号发生器(控制单元CU)的实现方法不同。

4.中央处理器有哪些功能?它由哪些基本部件所组成?解:从程序运行的角度来看,CPU 的基本功能就是对指令流和数据流在时间与空间上实施正确的控制。

对于冯·诺依曼结构的计算机而言,数据流是根据指令流的操作而形成的,也就是说数据流是由指令流来驱动的。

中央处理器由运算器和控制器组成。

5.中央处理器中有哪几个主要寄存器?试说明它们的结构和功能。

解:CPU 中的寄存器是用来暂时保存运算和控制过程中的中间结果、最终结果及控制、状态信息的,它可分为通用寄存器和专用寄存器两大类。

6计算机组成原理第6章流水线原理

结果

6.1 先行控制技术

• 先行控制(look-ahead)技术最早在IBM公司研制的 STRETCH机器中采用。目前,许多处理机中都已经采 用了这种技术,包括超流水处理机和超标量处理机等。

6.4 线性流水线性能分析

衡量流水线的主要指标有吞吐率,加速比和效率。

6.4.1 吞吐率TP

吞吐率(TP ── ThroughPut)指流水线在单位时间内执行的任务数, 可以用输入任务数或输出任务数表示。

TP n Tk

其中k表示流水线划分的段数。

当满足 ti 条t 件时,有 Tk (n k 1) t。

第6章 流水线原理及其 §1 重叠方式

通常提高指令执行速度的途径有如下三种: 1. 提高处理机的工作主频。 2. 采用更好的算法和设计更好的功能部件。 3. 多条指令并行执行,称为指令级并行技术。

• 可以从两个方面来开发处理机内部的并行性:

– 空间并行性:即在一个处理机内设置多个独 立的操作部件,并让这些操作部件并行工作, 这种处理机称为多操作部件处理机或超标量 处理机;

• 超长指令字技术VLIW:指让一条指令包含多个独立的操 作字段,并且分别控制多个功能部件并行工作的技术。

一.重叠解释方式

1.一条指令的几个过程段

1)取指令:根据PC(指令计数器)从M(存储器)取 出指令送到IR(指令寄存器)

2)译码分析:译出指令的操作性质,准备好所需数 据

3)执行:将准备好的数按译出性质进行处理,主要 涉及ALU(算术逻辑运算部件)

计算机组成原理第六章答案

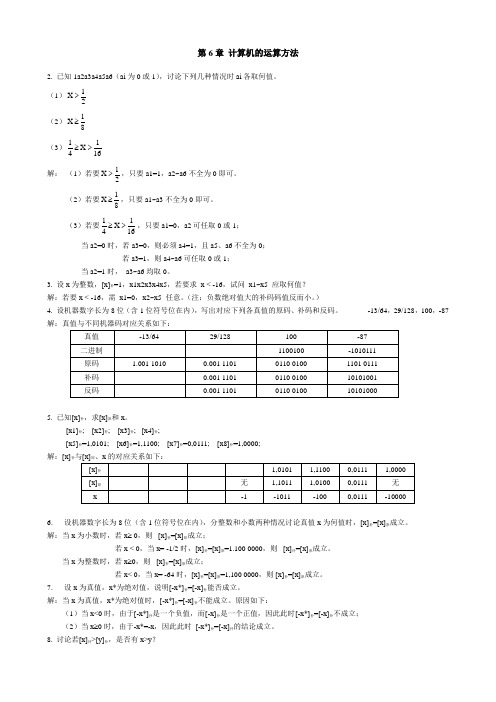

第6章 计算机的运算方法2. 已知1a2a3a4a5a6(ai 为0或1),讨论下列几种情况时ai 各取何值。

(1)21X > (2)81X ≥ (3)161X 41>≥ 解: (1)若要21X >,只要a1=1,a2~a6不全为0即可。

(2)若要81X ≥,只要a1~a3不全为0即可。

(3)若要161X 41>≥,只要a1=0,a2可任取0或1; 当a2=0时,若a3=0,则必须a4=1,且a5、a6不全为0;若a3=1,则a4~a6可任取0或1;当a2=1时, a3~a6均取0。

3. 设x 为整数,[x]补=1,x1x2x3x4x5,若要求 x < -16,试问 x1~x5 应取何值? 解:若要x < -16,需 x1=0,x2~x5 任意。

(注:负数绝对值大的补码码值反而小。

)4. 设机器数字长为8位(含1位符号位在内),写出对应下列各真值的原码、补码和反码。

-13/64,29/128,100,-87 解:真值与不同机器码对应关系如下:5. 已知[x]补,求[x]原和x 。

[x1]补; [x2]补; [x3]补; [x4]补;[x5]补=1,0101; [x6]补=1,1100; [x7]补=0,0111; [x8]补=1,0000; 解:[x]补与[x]原、x 的对应关系如下:6.设机器数字长为8位(含1位符号位在内),分整数和小数两种情况讨论真值x 为何值时,[x]补=[x]原成立。

解:当x 为小数时,若x ≥ 0,则 [x]补=[x]原成立;若x < 0,当x= -1/2时,[x]补=[x]原=1.100 0000,则 [x]补=[x]原成立。

当x 为整数时,若x ≥0,则 [x]补=[x]原成立;若x< 0,当x= -64时,[x]补=[x]原=1,100 0000,则 [x]补=[x]原成立。

7.设x 为真值,x*为绝对值,说明[-x*]补=[-x]补能否成立。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

中央处理器

计算机组成原理

本章知识点

6.1 CPU的功能和基本结构 CPU的基本功能和常见的CPU基本结构 6.2 指令执行的过程 1)数据通路的概念及组成 2)指令周期流程图 6.3时序与控制器 6.4微程序控制器的工作原理 1)微程序控制的基本概念 2)微程序控制器的组成原理 3)微指令的编码方法 4)微程序设计举例 6.5硬布线控制器的工作原理 1)硬布线控制器的模型 2)硬布线控制器的基本原理与设计方法

( 5 、 7、 9 )

图中相容性的微操作有: 1 、 2 、3 (4、6、8) 与 (5、7、9)两组中各取一个任意组合

32

计算机组成原理 2.微程序控制器的组成原理

1)控制存储器: 存放用来实现全部指令的所有微程序,是一种只读存储器,微程序固化 在其中,其容量取决于机器指令和每条指令微程序的长度,字长取决于

1)用( )表示读取寄存器或主存地址的内容,如(PC)表示读取PC寄

存器中的内容; 2)用[ ]表示主存单元地址或寄存器堆中寄存器的编号,则:

M[6]表示主存6号单元,(M[6])表示读取主存6号单元的数据;

R[6]表示寄存器堆中6号寄存器,(R[6])表示读取寄存器堆中6号 寄存器的数据; M[(R[6])]表示寄存器堆中6寄存器内容所指主存单元;(M[(R[6])]) 表示读取寄存器堆中6寄存器内容所指主存单元的内容。为简化对主 存单元的表示和访问,将它们分别简化成M[R[6]]和(M[R[6]])。 3)用“AB”表示数据传送,其中B为数据源,A为目的端;

•完成顺序控制的功能 •转移指令直接修改PC值

计算机组成原理 2)控制器中各主要功能部件的作用:指令寄存器IR

•保存当前正执行的指令

•指令的操作码字段和寻址方式送译码

7

计算机组成原理 3)控制器中各主要功能部件的作用:指令译码器ID

•对指令的OP字段和寻址方式译码,指出指令的操作方式

•译码的结果是找到与该指令相关的微程序的入口

•保存与主存之间交换的数据

11

计算机组成原理 7)控制器中各主要功能部件的作用:地址寄存器AR

•存放CPU将要访问的主存单元地址

12

计算机组成原理 6.2 指令执行的过程 1.数据通路的概念及组成

数据通路:数据在功能部件之间传送的路径; 数据在数据通路中的传送操作是在控制信号的控制下进行的; 数据通路的建立可用总线或专用通路两种方法来构建; 不同功能的指令及同一指令在执行的不同阶段的数据通路可不同; 数据通路的结构直接影响CPU内各种信息的传送路径、指令执行流程、 所需要的微操作控制信号及其时序安排和控制器的设计;

17

计算机组成原理 4.指令操作流程:基于单总线结构的处理器

18

计算机组成原理

根据指令周期的概念,任何指令第一个CPU周期都是取指周期,取 指周期中CPU要完成以下三件事: (1)根据PC的内容取出指令并送指令寄存器IR中保存(本书假定程序 首地址已存放在PC中); (2)修改PC的值;(这里假定计算机字长8位,采用单字长指令,主 存按字节编址); (3)对指令的操作码进行译码或测试,以确定指令在执行阶段将要 具体进行何种操作。

(a)取指CPU周期用到两条数据通路:

PC → MAR → MEM → MDR → IR

PC → X → ALU → Z → PC

(b)执行阶段用到的数据通路: IRA → MAR → MEM → MDR→ R0

20

计算机组成原理

(1) LOAD 指令周期流程

R[0] (M[6]): 将主存6号单元内容送R0, RS型指令

8

计算机组成原理

4)控制器中各主要功能部件的作用:操作控制器OC

•产生指令执行过程中所需要的控制信号

•实现指令的操作控制功能

9

计算机组成原理

5)控制器中各主要功能部件的作用:时序产生器

•对操作控制信号进行同步

•实现控制器的时间控制功能

计算机组成原理 6)控制器中各主要功能部件的作用:数据缓冲寄存器DR

28

计算机组成原理 微指令

程序

微程序

29

计算机组成原理

1)微命令和微操作 •控制部件与执行部件之间的联系

控制线

控制部件

反馈线 •微命令

执行部件

控制部件通过控制线向执行部件发出的各种控制信号(打开和关闭控制门)

•微操作 执行部件接受微命令后所进行的操作

•反馈线的作用

向控制部件反馈执行的状态信息,以便控制部件进行状态测试

执行阶段的操作 MAR (IRA) MDR (M[MAR]) R[0] (MDR)

各操作对应的控制信号 IRout=ARin=1 Read=DREin=1 DRIout=R0in=1

执行阶段用到的数据通路: IRA → MAR → MEM → MDR→ R0

21

计算机组成原理

(4)异常和中断处理:

处理运算中的异常及处理外部设备的中断服务请求等。 (5) 数据加工处理:

对数据进行算术、逻辑运算,或将数据在相关部件之间传送。

3

计算机组成原理 2.CPU的基本结构

4

计算机组成原理

5

计算机组成原理 1)控制器中各主要功能部件的作用:程序计数器PC

•给出并指示下一条指令的地址 •内容在取指完成后即可改变

2

计算机组成原理

6.1 CPU的功能和基本结构

1.CPU的基本功能

(1)指令执行顺序的控制: 控制程序中的指令按事先规定的顺序自动地执行。 (2)指令的操作控制: 产生指令执行过程中所需要的信号,以控制执行部件按指令规定 的操作运行。 (3)时间控制: 对各控制信号进行定时,以便按规定的时间顺序启动各操作。

13

计算机组成原理 2.指令周期流程

1)程序控制的过程,本质上是由控制器根据程序所包含的指令序列, 逐条执行指令的过程。 2)指令周期

一条指令从取出到执行完成所需时间 3)指令周期划分 (1)取指令周期: 根据PC的值取去主存储取指令; 如何形成后续指令地址。

(a)顺序执行指令时,将PC内容加当

微指令的字长,也与容量有一定关系(!)。要求控制存储器快速。

33

计算机组成原理

2)微指令寄存器(IR) •存放从控存中读出的微指令 •是图中的哪部分? 3)微地址寄存器(AR) 存储访问CM的微地址

34

计算机组成原理

4)微地址产生逻辑

用于产生后续微指令地址。能作为后继微指令地址的有下列形式:

对转移指令还需在执行周期内计算机 移地址。

(4)写回

将运算结果写到结果寄存器或存储器。 写回存储器时间较长,一般需要多个时 钟周期。

16

计算机组成原理 3.寄存器级传送语言RTL(Register Transfer Language)

为统一表示指令执行流程,采用寄存器描述语言表示指令执行过程中 的操作,使用RTL的规则如下:

下地址字段给出的地址是下条微指令地址,最终是否按照该 地址执行下一条微指令与是否进行条件测试及测试条件是否 成立等有关。

30

计算机组成原理

2)微操作的分类

微操作是计算机中最基本的操作,由于数据通路、逻辑功 能的关系,微操作可以分为相容性的和相斥性的微操作: •相容性的微操作 能同时并行执行的微操作 •相斥性的微操作 不能同时并行执行的微操作

31

计算机组成原理

图中相斥性的微操作有:

(

+ 、 – 、

M )

( 4 、 6、 8 )

R0out=DRIin=1 M[R[2]](MDR) DREout=Write=1

执行CPU周期用到的数据通路:

R2 → MAR 传送地址; 往主存存数据。

24

R0 → MDR → MEM

计算机组成原理

(5) JMP 指令周期流程

PC (IRA) : 将1000送入PC,实现无条件转移

前指令所占用的主存单元数 (b)当出现转移时,根据寻址方式、 转移条件、转移的目标地址等内容计算 得到。

14

计算机组成原理

(2)译码/取操作数周期 对指令寄存器中的操作码字段进行译 码并识别指令类型 根据指令地址码和寻址方式,从寄存 器或存储器中读取操作数。 不同的寻址方式可能具有不同的取操 作数周期。

19

计算机组成原理

(1) LOAD 指令周期流程

R[0] (M[6]): 将主存6号单元内容送R0, RS型指令

取指阶段的操作 MAR (PC) X (PC) Z ALU PC (Z) MDR (M[MAR]) IR ( MDR) 各操作对应的控制信号 PCout =ARin=1 Xin=1 +1 Zout=PCin=1 Read=DREin=1 DRIout=IRin=1

执行阶段的操作 PC (IRA)

对应的控制信号 IRout=PCin=1

执行CPU周期用到的数据通路:

IRA → PC

25

计算机组成原理 6.3时序与控制器

1.中央处理器的时序

过去的计算机采用主状态周期、节拍电位和节拍脉冲三级时序体制 来对操作控制信号进行定时控制.

主状态周期:一般对应指令的执行时间 节拍电位:对应指令执行的不同周期,如取指周期,以主存的工作周期为基础 节拍脉冲:完成一次微操作所需要的时间

算术运算类指令大都要求双操作数, 因此,取操作数流程要经历两次,第 一次取源操作数,操作流程由源寻址 方式字段确定,第二次取目的操作数, 操作流程由目的寻址字段确定。

15

计算机组成原理

(3)执行周期

控制器向算术逻辑运算单元及数据通 路中的其它相关部件发送操作控制命 令,完成由指令操作码规定的动作, 包括传送结果及记录状态信息。 操作结果送到哪里由寻址方式确定; 状态信息(如溢出)记录在PSW中;