F2812主要功能简介-事件管理器

F2812寄存器速查手册介绍

11

T1CTRIPE

当 EXTCON=0 时该位保留。 0 禁 止 T1CTRIP , T1CTPIR 不 影 响 定 时 器 1 的 比 较 输 出 、 GPTCDN(4) 或 PDPINTA(EVIFRA(0))标志。 1 使能 T1CTRIP,定时器 1 变为高阻状态,GPTCON ( 4 )变为 0, PDPINTA(EVIFRA(0)) 标志置 1。 10~ 9 8~7 T2TOADC 定时器 2 事件启动 ADC 00 不启动 ADC 01 下溢中断启动 ADC 10 周期中断启动 ADC 11 比较中断启动 ADC 定时器 1 事件启动 ADC 00 不启动 ADC 01 下溢中断启动 ADC 10 周期中断启动 ADC 11 比较中断启动 ADC 比较输出使能位,禁止或使能定时器比较输出。只有当 EXTCON ( 0 ) =1 时才激活 该位,当 EXTCON(0)=0 时该位保留。当 PDPIN/T1CTRIP 为低电平且 EVIMRA(0) =1 时激活该位,它会变为 0 0 定时器比较输出 T1/2PWM_T1/2CMPR 为高阻: 1 定时器比较输出 T 1/2PWM_T1/2CMPR 由各自的定时器比较逻辑驱动。 定时器 2 比较输出使能位,使能或禁止定时器 2 的比较输出 T2PWM_T2CMP。 EXTCON(0)=1 时激活该位, EXTCON(0)=0 时该位保留。 如果 T2CMPOE 有效, T2CTRIP 为低电平且被使能,则 T2CMPOE 变为 0 0 定时器 2 比较输出 T2PWM_T2CMP 为高阻。 1 定时器 2 比较输出 T2PWM_T2CMP 由定时器 2 比较逻辑驱动 定时器 1 比较输出使能位,使能或禁止定时器 1 的比较输出 T1PWM_T1CMP。 EXTCON(0)=1 时激活该位, EXTCON(0)=0 时该位保留。 如果 T1CMPOE 有效, T1CTRIP 为低电平且被使能,则 T1CMPOE 变为 0 0 定时器 2 比较输出 T1PWM_T1CMP 为高阻。 1 定时器 2 比较输出 T1PWM_T1CMP 由定时器 1 比较逻辑驱动 定时器 2 比较输出极性。 00 强制低 01 低有效 01 高有效 11 强制高 定时器 2 比较输出极性。 00 强制低 01 低有效 01 高有效 11 强制高

第6章_F2812事件管理器及其应用2

A

EVA/B PDPINTA CMP1/2/3INT CAPINT1/2/3n T1CINT,T1PINT A T1UFINT,T1OFINT T2CINT,T2PINT T2UFINT,T2OFINT B PDPINTB CMP4/5/6INT CAPINT4/5/6n B T3CINT,T3PINT T3UFINT,T3OFINT T4CINT,T4PINT T4UFINT,T4OFINT

2

第5.1节 事件管理器(EV)

一、通用定时器 二、脉宽调制电路PWM 三、捕获单元 四、事件管理器模块的中断 五、应用事件管理器产生PWM

第5.1节 事件管理器(EV)

F2812提供了两个结构和功能相同的事件管理器EVA和

EVB模块,具有强大的控制功能,特别在运动控制和电机控

制领域。 ▲ 通用定时器

1

第5章 TMS320F2812片内外设模块

一、事件管理器 EV 二、串行通信接口 SCI 三、串行外设接口 SPI 四、eCAN 总线模块 五、多通道缓冲串行 McBSP 六、模数转换器 ADC

一、看门狗定时器 WD 二、数字输入输出 I/O 三、事件管理器 EV 四、模数转换器 ADC 五、串行通信接口 SCI 六、异步串行口 SPI 七、CAN控制器

R/W-0

D5

R/W-0

D4

R/W-0

D3

R/W-0

D2

D1

R/W-0

D0

T1TOADC TCMPOE T2CMPOE T1CMPOE

通用定时器A控制寄存器

T2PIN

T1PIN

D15

R-0

D14

R-1

D13

R-1

D12

R/W-1

TMS320F2812芯片介绍

TMS320F2812芯片介绍1 TMS320F2812芯片的特点 (1)2 F2812内核组成 (4)3 F2812外设介绍 (5)①事件管理器 (6)②模数转换模块 (6)③SPI和SCI通信接口 (6)④CAN总线通信模块 (7)⑤看门狗 (7)⑥通用目的数字量I/O (7)⑦PLL时钟模块 (7)⑧多通道缓冲串口 (7)⑨外部中断接口 (8)⑩JTAG (8)1 TMS320F2812芯片的特点TMS320F2812是TI公司推出的低价钱、高性能的32位定点DSP数字信号处置器,是到目前为止用于数字控制领域性能最好的DSP芯片。

它是在TMS320C28x为内核的基础上扩展了相应的存储器并集成了大量的片内外设而成的新一代适用于工业控制的DSP芯片。

图9为F2812控制器方框图。

图9 F2812控制器方框图TMS320F2812 系统组成包括:150MHz、150MIPS的低电压3.3VCPU、片内存储器、中断管理模块、事件管理器模块、片内集成外围设备。

TMS320F2812的体系结构采用4级流水线技术,加速程序的执行。

32位的CPU 内核提供了壮大的数据处置能力, 最高速度可达150MIPS,能够在单个指令周期内完成32*32位的乘累加运算。

TMS320F2812采用增强的哈佛结构,芯片内部具有6 条32位总线, 程序存储器总线和数据存储器总线彼此独立, 支持并行的程序和操作数寻址, 因此CPU的读/写可在同一周期内进行。

这种高速运算能力使各类复杂控制算法得以实现。

芯片本身具有128KB的Flash,外部RAM 能够按照需要进行扩充。

另外,它还具有高性能的12位模/数转换能力,改良的通信接口和1MB的线性地址空间。

外设模块丰硕且功能壮大,其中包括:事件管理器EV A和EVB,包括16个PWM输出,10个16位比较器和4个通用按时器;快速灵活的12位,16通道ADC,12.5MPS数据吞吐率;及其它丰硕的片内集成外设:2通道的SCI模块、SPI模块、eCAN2.0B模块、McBSP模块等。

TMS320F2812 DSP用正弦函数表与事件管理器EVAB产生6路PWM波详解

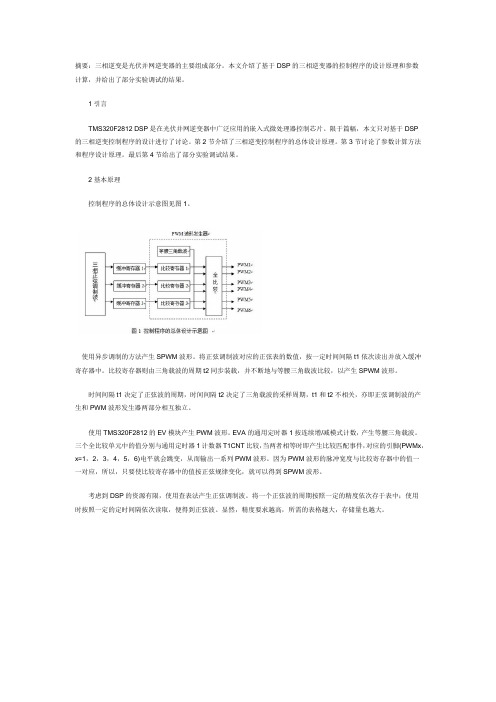

摘要:三相逆变是光伏并网逆变器的主要组成部分。

本文介绍了基于DSP的三相逆变器的控制程序的设计原理和参数计算,并给出了部分实验调试的结果。

1引言TMS320F2812 DSP是在光伏并网逆变器中广泛应用的嵌入式微处理器控制芯片。

限于篇幅,本文只对基于DSP的三相逆变控制程序的设计进行了讨论。

第2节介绍了三相逆变控制程序的总体设计原理。

第3节讨论了参数计算方法和程序设计原理。

最后第4节给出了部分实验调试结果。

2基本原理控制程序的总体设计示意图见图1。

使用异步调制的方法产生SPWM波形。

将正弦调制波对应的正弦表的数值,按一定时间间隔t1依次读出并放入缓冲寄存器中。

比较寄存器则由三角载波的周期t2同步装载,并不断地与等腰三角载波比较,以产生SPWM波形。

时间间隔t1决定了正弦波的周期,时间间隔t2决定了三角载波的采样周期,t1和t2不相关,亦即正弦调制波的产生和PWM波形发生器两部分相互独立。

使用TMS320F2812的EV模块产生PWM波形。

EVA的通用定时器1按连续增/减模式计数,产生等腰三角载波。

三个全比较单元中的值分别与通用定时器1计数器T1CNT比较,当两者相等时即产生比较匹配事件,对应的引脚(PWMx,x=1,2,3,4,5,6)电平就会跳变,从而输出一系列PWM波形。

因为PWM波形的脉冲宽度与比较寄存器中的值一一对应,所以,只要使比较寄存器中的值按正弦规律变化,就可以得到SPWM波形。

考虑到DSP的资源有限,使用查表法产生正弦调制波。

将一个正弦波的周期按照一定的精度依次存于表中;使用时按照一定的定时间隔依次读取,便得到正弦波。

显然,精度要求越高,所需的表格越大,存储量也越大。

一个周期的正弦表的相位是,对应表的长度的1/3。

为了产生三相对称正弦波,将正弦表长度取为3n,n为整数。

当A相从第0个数开始取值时,则B相从第n个数处开始取值,C相从第2n个数处开始取值。

事实上,因为使用了异步调制,所以只要正弦表的长度足够大,不是3的整数倍也不会对输出波形产生太大影响。

DSP 相关知识及TMS320F2812性能介绍

第一章 DSP 相关知识及TMS320F2812性能介绍数字信号处理(DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

在通常的实时信号处理中,它具有可程控、可预见性、精度高、稳定性好、可靠性和可重复性好、易于实现自适应算法、大规模集成等优点,这都是模拟系统所不及的。

1.1 DSP系统构成数字信号处理器是利用计算机或专用处理设备,在模拟信号变换成数字信号以后,以数字形式对信号进行采集、变换、滤波、估值、增强、压缩、识别等高速实时处理的专用处理器,其处理速度比最快的CPU还快10~50倍。

一个典型的DSP系统,输入信号首先进行带限滤波和抽样,然后进行A/D变换将信号变换成数字比特流。

DSP芯片的输入是A/D变换后得到的以抽样形式表示的数字信号,DSP芯片对输入的数字信号进行某种形式的处理,如进行一系列的乘累加操作(MAC)。

最后,经过处理后的数字样值再经D/A变换转换为模拟样值,之后再进行内插和平滑滤波就可得到连续的模拟波形。

必须指出的是,上面给出的DSP系统模型是一个典型模型,但并不是所有的DSP系统都必须具有模型中的所有部件。

1.2 DSP系统的特点数字信号处理系统是以数字信号处理为基础,因此具有数字处理的全部优点:(1)接口和编程方便。

DSP系统与其他以现代数字技术为基础的系统或设备都是相互兼容的,与这样的系统接口以实现某种功能要比模拟系统与这些系统接口容易得多;另外,DSP系统中的可编程DSP芯片可使设计人员在开发过程中灵活方便地对软件进行修改和升级。

(2)稳定性和可重复性好。

DSP系统以数字处理为基础,受环境温度、湿度、噪声、电磁场的干扰和影响较小,可靠性高;数字系统的性能基本不受元器件参数性能变化的影响,因此数字系统便于测试、调试和大规模生产。

(3)精度高。

16位数字系统可以达到10-5的精度。

(4)特殊应用。

有些应用只有数字系统才能实现,例如信息无失真压缩、V 型滤波器、线性相位滤波器等等。

DSP 相关知识及TMS320F2812性能介绍(word文档良心出品)

第一章 DSP 相关知识及TMS320F2812性能介绍数字信号处理(DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

在通常的实时信号处理中,它具有可程控、可预见性、精度高、稳定性好、可靠性和可重复性好、易于实现自适应算法、大规模集成等优点,这都是模拟系统所不及的。

1.1 DSP系统构成数字信号处理器是利用计算机或专用处理设备,在模拟信号变换成数字信号以后,以数字形式对信号进行采集、变换、滤波、估值、增强、压缩、识别等高速实时处理的专用处理器,其处理速度比最快的CPU还快10~50倍。

一个典型的DSP系统,输入信号首先进行带限滤波和抽样,然后进行A/D变换将信号变换成数字比特流。

DSP芯片的输入是A/D变换后得到的以抽样形式表示的数字信号,DSP芯片对输入的数字信号进行某种形式的处理,如进行一系列的乘累加操作(MAC)。

最后,经过处理后的数字样值再经D/A变换转换为模拟样值,之后再进行内插和平滑滤波就可得到连续的模拟波形。

必须指出的是,上面给出的DSP系统模型是一个典型模型,但并不是所有的DSP系统都必须具有模型中的所有部件。

1.2 DSP系统的特点数字信号处理系统是以数字信号处理为基础,因此具有数字处理的全部优点:(1)接口和编程方便。

DSP系统与其他以现代数字技术为基础的系统或设备都是相互兼容的,与这样的系统接口以实现某种功能要比模拟系统与这些系统接口容易得多;另外,DSP系统中的可编程DSP芯片可使设计人员在开发过程中灵活方便地对软件进行修改和升级。

(2)稳定性和可重复性好。

DSP系统以数字处理为基础,受环境温度、湿度、噪声、电磁场的干扰和影响较小,可靠性高;数字系统的性能基本不受元器件参数性能变化的影响,因此数字系统便于测试、调试和大规模生产。

(3)精度高。

16位数字系统可以达到10-5的精度。

(4)特殊应用。

有些应用只有数字系统才能实现,例如信息无失真压缩、V 型滤波器、线性相位滤波器等等。

F2812主要功能简介-事件管理器

tactive (2 TxPR-TxCMPRup -TxCMPRdn )T定标输入时钟周期

TxCMPRup=0,TxCMPRdn≠0

tactive (2 TxPR-TxCMPRdn )T定标输入时钟周期

TxCMPRup=0,TxCMPRdn=0

tactive 2 TxPR T定标输入时钟周期

TxCMPRup﹥TxPR,TxCMPRdn﹥TxPR

tactive 0

35

GP Timer 复位状态

任何RESET事件发生时,都产生下列结果

计数方向位 = 1 其它所有定时器寄存器的位 = 0,定时器被禁止 所有中断标志位 = 0 功率保护中断屏蔽位 = 1,开放 其它所有中断屏蔽位 = 0 定时器比较输出被置高阻

内部/外部时钟输入,可编程分频,方向可引脚控制

4种可屏蔽中断:上溢、下溢、比较、周期

全比较单元 Full-Compare Units

3 x 2 个独立的比较单元,每个有6个比较输出

配合可编程死区发生器,产生PWM波形

可编程死区发生器 Programmable Deadband

Generation

为什么要设计6个PWM输出?

3个4位计数器,1个16位比较寄存器,死区值可编程

PWM波形发生器 PWM Waveform Generation

共可产生8个PWM波形输出

捕获单元 Capture Units

EVA:CAP1/2/3,EVB:CAP4/5/6,上/下边沿触发

3个16位 2-level-deep FIFO堆栈

不变

高 低 低 高 立即高 立即低

31

PWM输出逻辑

TMS320F28122810第四章(共七章)

另外还有 GPTCONA/B,用法见后。 每个通用定时器都可以独立使用,也可以两个定时器同步使用。每个通用定时器的比较 寄存器可用于比较功能,产生 PWM 波形。当定时器工作在增/减模式时,有 3 种连续工作 方式。每个定时器都可以使用可预定标的内部或外部输入时钟。通用定时器还为别的事件管 理器子模块提供时钟基准:通用定时器 1 为比较单元和 PWM 电路提供时钟基准,通用定时 器 2/1 为捕获单元和正交编码电路提供时钟基准。周期寄存器和比较寄存器有双缓冲,允许 用户根据需要改变定时器周期和 PWM 脉冲宽度。

图 4.3 通用定时器框图(x=2 或 4) [当 x=2 时 y=1,n=2,当 x=4 时 y=3,n=4]

100

4.2.2 通用定时器的输入输出

通用定时器的输入包括: z 内部高速时钟(HSPCLK); z 外部时钟 TCLKINA/B,最高频率不超过 CPU 时钟的 1/4; z 方向输入 TDIRA/B,控制定时器增/减计数的方向; z 复位信号 RESET。

97

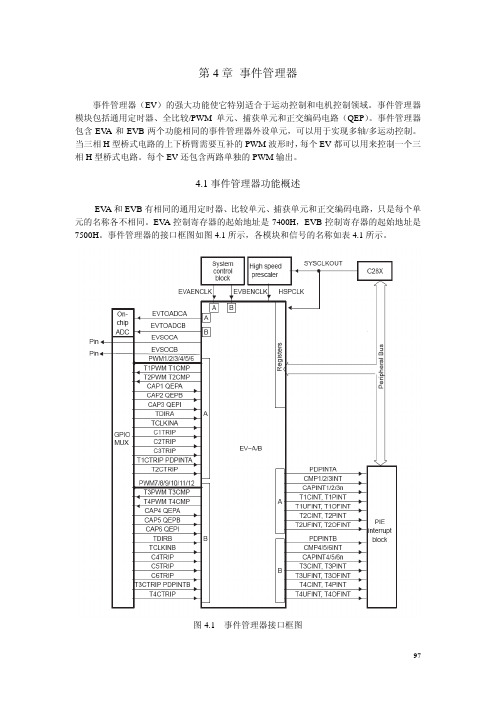

事件管理器模块

通用定时器

比较单元

捕获单元

正交编码电路

外部定时器输入

用于控制比较器 的外部触发输入 用于定时器比较 的外部触发输入 功率模块保护中

断输入 ADC 启动外部

触发输入

EVA

模块

信号

通用定时器 1 通用定时器 2 比较单元 1 比较单元 2 比较单元 3 捕获单元 1 捕获单元 2 捕获单元 3

模块

EVB

信号

通用定时器 3 通用定时器 4 比较单元 4 比较单元 5 比较单元 6 捕获单元 4 捕获单元 5 捕获单元 6

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

GP Timer Input & Output

Input:

内部高速外设时钟,HSPCLK 外部时钟TCLKINA/B,最高频率≤1/4 CPU时钟 方向输入引脚,TDIRA/B 复位信号,RESET

Output:

比较输出,TxCMP ADC启动转换信号 上溢、下溢、比较匹配、周期匹配 计数方向指示位

比较寄存器,TxCMPR

存放比较常数,不断与计数器比较,匹配时: 根据GPTCONA/B设置,比较输出引脚发生跳变 对应设置中断标志 中断未屏蔽,产生中断请求

周期寄存器,TxPR

存放周期值,决定定时器周期 与计数器值相等时,根据计数方式确定复位为0或转为减计数

16

GP Timer Registers 2

GPTCONA/B中的位反映计数方向 TDIRA/B引脚决定计数方向

1 增计数 0 减计数

17

GP Timer Clock

可采用内部时钟或外部时钟TCLKINA/B引脚输入 外部时钟频率≤1/4 CPU时钟 定向增/减计数模式:

T2、T4为QEP电路使用 QEP电路为定时器提供时钟、方向输入

内部/外部时钟输入,可编程分频,方向可引脚控制

4种可屏蔽中断:上溢、下溢、比较、周期

全比较单元 Full-Compare Units

3 x 2 个独立的比较单元,每个有6个比较输出

配合可编程死区发生器,产生PWM波形

可编程死区发生器 Programmable Deadband

Generation

13

GP Timer Functional Block

每个GP Timer 包括:

一个16位增/减计数器,TxCNT,RW,当前计数值 一个16位比较寄存器,TxCMPR,RW,双缓冲 一个16位周期寄存器,TxPR,EW,双缓冲 一个16位控制寄存器,TxCON,RW 内部/外部时钟输入,可定标 四个可屏蔽中断控制逻辑 一个增/减方向控制引脚,TDIRx 一个比较输出引脚,TxCMP 全局控制寄存器,GPTCONA/B

7

EVA Registers (1)

8

EVA Registers (2)

9

问题

一一对应EVA寄存器, 说出EVB寄存器的名称?

10

3 F2812主要功能简介 3-3 事件管理器 2 通用定时器

11

问题

还有其它定时器吗? 有几个? TI 如此设计的意图是什么?

12

GP Timers Block Diagram

3个4位计数器,1个16位比较寄存器,死区值可编程

PWM波形发生器 PWM Waveform Generation

共可产生8个PWM波形输出

捕获单元 Capture Units

EVA:CAP1/2/3,EVB:CAP4/5/6,上/下边沿触发

3个16位 2-level-deep FIFO堆栈

比较和周期寄存器的双缓冲

任何时候都可写入新值,但不立即加载 周期寄存器:当计数器计数到0时重新加载 比较寄存器:立即加载 / 下溢时加载 / 下溢或周期匹配时加载

比较输出

高/低电平有效、强制高/低电平 高/低电平有效:比较输出有效时转变电平 强制高/低电平:立即转变电平

计数方向

2

Event Manager Module & Signal

3

EV Device Interfaces

4

EV A Functional Block Diagram

5

Event Manager Functions 1

通用定时器 General-Purpose (GP) Timers

16位定时器,EVA:T1/2;EVB:T3/4,独立/同步工作

基于QEP电路的时钟输入

QEPCLK为T1的时钟输入

预标定阐述≡1

计数器在上升/下降沿均计数 QEP产生的时钟频率是每个QEP输入通道的4倍 QEP时钟频率应≤1/4 CPU时钟

18

GP Timer的同步

配置T2CON使T2与T1同步:

将T2CON的T2SWT1置1,T2用T1的使能位TENABLE启动 启动前,T1、T2用不同值初始化计数器 将T2CON的SELT1PR置1,T2用T1的周期

15

GP Timer Registers 1

控制寄存器,பைடு நூலகம்xCON

选择四种计数模式之一

选择内/外时钟

重新装载条件

时钟预定标

定时器使能/禁止

确定T2、T4使用的周期寄存器是 本比身较还操是作T1使、能T3/禁止

全局控制寄存器,GPTCONA/B

根据定时器的任务确定采取的操作方式 控制计数方向

功率驱动保护中断 Power Drive Protection Interrupt

为系统安全操作提供保护,如过压、过流、超速等

EV寄存器 EV Registers

EVA Registers:0x7400 – 0x7431 EVA Registers:0x7500 – 0x7531

EV中断 EV Interrupts

6

Event Manager Functions 2

正交编码脉冲电路 Quadrature-Encode Pulse

(QEP)

CAP1/2,CAP4/5作为QEP完全同步输入 脉冲序列方向、边沿自动检测

A/D转换器外部启动 External ADC Start-of-

Conversion EVASOC、EVBSOC

3 F2812主要功能简介 3-3 事件管理器

1 事件管理器功能概述 2 通用定时器 3 比较单元 4 PWM电路 5 空间矢量PWM

6 捕获单元 7 正交编码脉冲QEP电路 8 事件管理器的中断 9 事件管理器的寄存器 10 使用实例

1

3 F2812主要功能简介 3-3 事件管理器

1 事件管理器功能概述

T1、T2都从自己的当前值开始计数

问题 定时器同步有什么用处?

如何使用T4与T3的同步?

19

GP Timer启动ADC

GPTCONA/B中设置ADC的启动信号由哪个定时器

提供:

下溢中断 周期中断 比较中断