74HC165功能说明

74HC165 概述

74HC165 概述74HC165是一款高速CMOS器件,74HC165遵循JEDEC标准no.7A。

74HC165引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC165是8位并行读取或串行输入移位寄存器,可在末级得到互斥的串行输出(Q7和Q7),当并行读取(PL)输入为低时,从D0到D7口输入的并行数据将被异步地读取进寄存器内。

而当PL为高时,数据将从DS输入端串行进入寄存器,在每个时钟脉冲的上升沿向右移动一位(Q0 → Q1 → Q2,等等)。

利用这种特性,只要把Q7输出绑定到下一级的DS输入,即可实现并转串扩展。

74HC165的时钟输入是一个“门控或”结构,允许其中一个输入端作为低有效时钟使能(CE)输入。

CP和CE的引脚分配是独立的并且在必要时,为了布线的方便可以互换。

只有在CP为高时,才允许CE由低转高。

在PL上升沿来临之前,不论是CP还是CE,都应当置高,以防止数据在PL的活动状态发生位移。

74HC165 特性异步8位并行读取同步串行输入兼容JEDEC标准no.7AESD保护HBM EIA/JESD22-A114E超过2000 VMM EIA/JESD22-A115-A超过200 V温度范围-40~+85 ℃-40~+125 ℃74HC165 参数74HC165 基本参数电压 2.0~6.0V驱动电流+/-5.2 mA传输延迟16 ns@5V74HC165 其他特性最高频率56 MHz逻辑电平CMOS功耗考量低功耗或电池供电应用74HC165 封装与引脚SO16, SSOP16, DIP16, TSSOP168 位移位寄存器(并行输入,互补串行输出)简要说明当移位/置入控制端(SH/LD)为低电平时,并行数据(A-H)被置入寄存器,而时钟(CLK,CLK INH)及串行数据(SER)均无关。

当SH/LD为高电平时,并行置数功能被禁止。

CLK和CLK INK在功能上是等价的,可以交换使用。

74HC165中文资料_数据手册_参数

4 4

PQD

74HC_HCT165

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 4 — 28 December 2015

© Nexperia B.V. 2017. All rights reserved

SOT338-1

Nexperia

74HC165; 74HCT165

8-bit parallel-in/serial out shift register

Table 1. Ordering information …continued

Type number Package

Temperature range Name

Table 4. Limiting values In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V)

Rev. 4 — 28 December 2015

© Nexperia B.V. 2017. All rights reserved

4 of 21

Nexperia

74HC165; 74HCT165

8-bit parallel-in/serial out shift register

8. Limiting values

Description

Version

plastic small outline package; 16 leads; body width 3.9 mm SOT109-1

74HC165功能说明

74HC165功能说明

1.并行输入:74HC165具有8个并行输入引脚(A-H),可以同时读取8个输入信号。

这些输入信号可以是数字信号,也可以是模拟信号。

2.串行输出:74HC165具有串行输出引脚(QH),它可以将输入信号转换为串行输出信号。

输出信号的顺序与输入信号的读取顺序相同。

3.移位操作:74HC165可以通过移位操作来读取并且存储输入信号。

移位操作可以由一个时钟信号(SH/LD)和一个时钟使能信号(CLKINH)来控制。

当时钟使能信号为高电平时,移位操作生效;当时钟使能信号为低电平时,移位操作被禁止。

4.并行加载:除了移位操作之外,74HC165还可以通过并行加载操作来读取并存储输入信号。

并行加载操作可以通过时钟使能引脚(CLKINH)和并行加载引脚(PL)来控制。

当时钟使能引脚为高电平时,同时并行加载引脚为高电平,即可进行并行加载操作。

5.级联操作:多个74HC165芯片可以级联在一起,以扩展输入信号的数量。

级联操作可以通过级联引脚(SERA/B)和级联输出引脚(QH)来实现。

级联引脚可以将一个74HC165的输出连接到另一个74HC165的输入,以实现数据的串行传输。

总结起来,74HC165是一种用于将8个并行输入信号转换为串行输出信号的移位寄存器芯片。

它通过移位操作和并行加载操作来读取并存储输入信号,并且可以通过级联操作扩展输入信号的数量。

这种芯片在数字电路控制和数据采集等应用中非常常见,具有广泛的用途。

74hc165 电平标准

74hc165 电平标准740HC165是一种8位移位寄存器,它常用于电子设备中的数据输入和输出。

在设计和使用电子电路中,了解和理解其电平标准是非常重要的。

首先,让我们来了解一下何为电平标准。

在电子领域中,电平标准用来定义不同电压值所代表的逻辑状态,例如高电平表示1,低电平表示0。

电平标准是为了保证不同设备和电路之间的互操作性以及通信的可靠性。

740HC165的电平标准和逻辑电平定义如下:1.电源电压:740HC165的工作电压范围通常为2V至6V。

这意味着电路在这个电压范围内工作时,可以正常执行其功能。

2.逻辑高电平:对于输入信号而言,当输入电压高于特定阈值电压(通常称为ViH)时,电路将识别为逻辑高电平。

在740HC165中,典型的ViH电平为0.7VCC,其中VCC是电路的电源电压。

也就是说,如果输入电压高于0.7VCC,电路将被视为处于逻辑高电平。

3.逻辑低电平:对于输入信号而言,当输入电压低于特定阈值电压(通常称为ViL)时,电路将识别为逻辑低电平。

在740HC165中,典型的ViL电平为0.3VCC,其中VCC是电路的电源电压。

也就是说,如果输入电压低于0.3VCC,电路将被视为处于逻辑低电平。

4.输出电平:对于输出信号而言,当输出电压高于特定阈值电压(通常称为VOH)时,电路将输出逻辑高电平。

在740HC165中,典型的VOH电平为0.9VCC,其中VCC是电路的电源电压。

相反,当输出电压低于特定阈值电压(通常称为VOL)时,电路将输出逻辑低电平。

在740HC165中,典型的VOL电平为0.1VCC,其中VCC是电路的电源电压。

总结一下,740HC165的电平标准意味着输入电压高于0.7倍的电源电压将被视为逻辑高电平,低于0.3倍的电源电压将被视为逻辑低电平。

对于输出电平而言,高于0.9倍的电源电压将输出逻辑高电平,低于0.1倍的电源电压将输出逻辑低电平。

了解电平标准对于正确设计和使用电子电路至关重要。

(31条消息)74HC165级联电路篇(三)

(31条消息)74HC165级联电路篇(三)

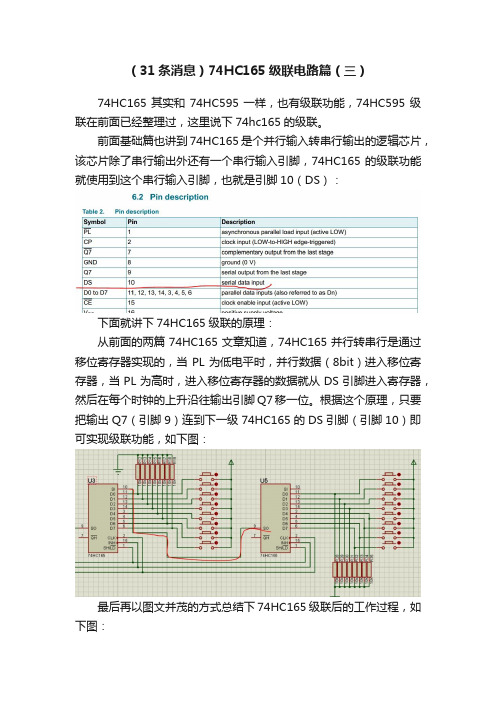

74HC165其实和74HC595一样,也有级联功能,74HC595级联在前面已经整理过,这里说下74hc165的级联。

前面基础篇也讲到74HC165是个并行输入转串行输出的逻辑芯片,该芯片除了串行输出外还有一个串行输入引脚,74HC165的级联功能就使用到这个串行输入引脚,也就是引脚10(DS):

下面就讲下74HC165级联的原理:

从前面的两篇74HC165文章知道,74HC165并行转串行是通过移位寄存器实现的,当PL为低电平时,并行数据(8bit)进入移位寄存器,当PL为高时,进入移位寄存器的数据就从DS引脚进入寄存器,然后在每个时钟的上升沿往输出引脚Q7移一位。

根据这个原理,只要把输出Q7(引脚9)连到下一级74HC165的DS引脚(引脚10)即可实现级联功能,如下图:

最后再以图文并茂的方式总结下74HC165级联后的工作过程,如下图:

74HC165的级联电路就整理到这里,下一篇是级联的编程,总结下如何读取74HC165级联的数据。

常用元器件使用方法6:并

常用元器件使用方法6:并

介绍:

74HC165是并-串转换芯片,单芯片可以将8路并行信号转换为1路串行信号,并可以进行芯片级联,以完成多路并行信号输入单片机的操作。

芯片特性:

1、异步8位并读取;

2、同步串行输入;

3、温度范围-40~85。

芯片引脚:

内部结构图:

引脚功能说明:

使用说明:

SH/LD用于并行装载数据,当其引脚为低时,将外部数据并行装入移位寄存器,当其引脚为高时,阻断外部输入与内部寄存器。

在SH/LD为低的条件下,进行移位操作,需保证CLK INH与CLK引脚一个引脚为底(实际上CLK INH与CLK引脚的功能是相同的),另一个引脚上升沿即进行数据移位。

时序图:

典型电路图:

原创性文章,转载请注明出处CSDN:/qingwufeiyang12346。

AiP74HC165中文使用说明书

-

0

0.1

-

0.1

V

-

0

0.1

-

0.1

V

-

0.15

0.26

-

0.33

V

-

0.16

0.26

-

0.33

V

i-core 输入

漏电流

II

VI =VCC或GND;

VCC=6.0 V

-

-

VI = VCC 或

电源电流

ICC

GND; IO=0A;

-

-

VCC = 6.0 V

输入电容

CI

-

3.5

3.3.2 交流参数 (除非另有规定,CL = 50 pF)

单位 V V V

°C

参数名称 高电平 输入电压 低电平 输入电压

高电平 输出电压

符号 VIH VIL

VOH

测试条件

VCC=2.0V VCC=4.5V VCC=6.0V VCC=2.0V VCC=4.5V VCC=6.0V VI=VIH 或 VIL IO = -20uA; VCC = 2.0 V IO = -20uA; VCC = 4.5 V IO = -20uA; VCC = 6.0 V

3.3、电气特性 3.3.1 直流参数

Ptot

Tamb Tstg TL

-40~+85°C

10 秒

符号

VCC Vቤተ መጻሕፍቲ ባይዱ VO Tamb

最小 2.0 0 0 -40

DIP16

SOP16 SSOP16

DIP SOP

典型 5.0 -

750

500

mW

500

-40~+85

第4节:“鸿哥三宝”之74HC165(按键扫描篇)

}

else if(key_lock4==0)

{

++ delay_cnt4;

if(delay_cnt4> cnt_delay_cnt1) //延时计数去抖动

hc165_pl_dr=0;

asm("nop");

asm("nop");

hc165_pl_dr=1;

asm("nop");

asm("nop");

for(j=0;j<16;j++)

{

hc165_cp_dr=0;

beep_dr=0; //关蜂鸣器,上电初始化IO

while(1) { Nhomakorabea CLRWDT(); //喂看门狗,大家不用过度关注此行

key_service(); //按键服务

asm("nop");

asm("nop");

} //以上一小段代码是通过驱动2个74HC165来获取16个按键的电平状态

//key_status

//以下代码通过解析每一位电平状态来确定哪个按键被触发

if((key_status &0x0001)==0x0001)

(4)源码适合的单片机:PIC18f4520,晶振为22.1184MHz

(5)源代码讲解如下:

#include<pic18.h> //包含芯片相关头文件

//补充说明:吴坚鸿程序风格是这样的,凡是输出IO后缀都是_dr,凡是输入的//IO后缀都//是_sr

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

74hc165编程说明

接触单片机,嵌入式有好长一段时间了,一直想找个机会把自己总结得东西拿出来晒晒太阳(其实没有什么,高手可能早已经了解),在这里我只想分享给与我一样奋斗在单片机一线得广大童鞋么一点小小得甚至卑微得经验.我们都知道通信从大得方面有两种:串行与并行。

串行得最大优点就是占用总线少,但就是传输速率低;并行恰恰相反,占用总线多,传输速率高.市面上有很多这样得芯片,有串入并出得(通俗讲就就是一个一个进,最后一块出来),有并入串出得(相对前者而言)。

具体用哪种类型要根据我们得实际情况。

比如利用单片机显示数码管单纯得显示一个数码管如果仅仅就是为了显示那么动用单片机一个端口(如P0或P1/P2/P3)那没有什么,当然这里我说得数码管就是8段得(如果利用BCD类型16进制数码管那么只需四个即可)就拿51类型得单片机来说,总共32个I/O口,一般如果不就是做太大得工程就是完全够用得,但有些时候您会恨单片机怎么不多长几条“腿",怎么省还就是不够用。

别急集成串行芯片来帮忙哈哈

客套话就不多说了言归正传,今天我介绍一下几个在数码管显示或键盘处理中经常用到得移位寄存器芯片,首先登场得就是74HC165:

74HC165/74LS165就是典型并入串出芯片,用它来读取外界键盘信息再好不过了,前提我们得了解它,我们先了解其引脚:

引出端符号ﻫCLK,CLK INH 时钟输入端(上升沿有效)

A-H 并行数据输入端

SER 串行数据输入端

QH 输出端ﻫQHn 互补输出端

SH/LD移位控制/置入控制(低电平有效)

真值表

时序图

其实瞧一个芯片就是如何使用得,不只就是瞧引脚功能,更重要得就是要瞧时序图与真值表,从其中我们可以详细得了解到它就是如何使用得,然后转化成程序代码即可.

从上面我们得真值表与时序图中我们要特别注意几个端口得变化,真值表中SH/LD只有在高电平得时候方才有效;CLK,CLK INH只有当其中一个为低电平得时候,另一个时钟才能正确得输入,这就是非常重要得(一般得我们在使用时,可以将其中得一个直接接地,另一个做时钟输入端口使用).但就是我们做事要细心,要一丝不苟,从时序图中我们瞧到SH/LD有一个负脉冲这就是什么缘故呢?在程序设计中如果忽略了此处,那么注定结果就是悲剧得。

从SH/LD得全称就是:SHIFT/LOAD这说明它有两种功能(SHIFT英文意思就是移位,LOAD就是装载),故美其名曰:移位控制(高电平有效)/置入控制端口(低电平有效)。

在单片机接收数据前,必须将该引脚拉低,目得就是为了将并行数据A-—H上得数据装载到内部寄存器中,这里体现得时LOAD功能;接下来在接收数据得过程中必须将该引脚拉高,目得就是为了使寄存器中得数据可以移动,从而从QH或QN'中移入单片机.这里体现得就是SHIFT功能.74hc165中最重要得一个引脚就就是该引脚至于说时钟电路就显得逊色多了。

我们只需将单品机得某一个端口拉低或抬高即可,这样数据就一步一步得被接收了.请务必记得上升沿有效.

分析了74hc165得引脚及其时序我想大家对其使用明白多了,接下来我们用51单品机来编写一段程序代码:

#include〈reg51、h〉ﻫ#include〈intrins、h>

#defineuint unsigned int

#define uchar unsigned char

sbit CLK=P3^6;//时钟位定义ﻫsbit Lock=P3^7; //转载/移位位定义

sbit Data=P3^5;//接收位定义

/************************165接收程序***********************/

//---—-—-——--——----------—--—----———-——---————-——--——--—-—-—-—-ﻫ

uchar series_165()

{

uchari;ﻫuchar BYTE=0;//最终接收到得字符Lock=0;//将165外部端口数据装入内部寄存器ﻫ_nop_();ﻫLock=1;//抬高为移位准备

for(i=0;i<8;i++)

{ ﻫBYTE〈<=1;//1ﻫCLK=0;//时钟低

_nop_();ﻫBYTE|=Data;//先接收高位ﻫCLK =1; //时钟高,上升沿下一个数据移出ﻫ_nop_();

// 5ﻫ

}ﻫreturn BYTE;//返回接收字符ﻫ}

void main()ﻫ{ﻫCLK=0;ﻫwhile(1)

P2=series_165();//显示

}

运行过这个程序没有任何问题,显示如下

但就是我们在实验得过程中,出现了一种情况我们将上述程序得1语句换到了5得位置,就出现了下面得显示结果:

注意别被“1"迷惑了那只就是165外部数据,就是单片机要读得数据,而P2口才就是真正要显示接收得数据,为什么差别如此之大呢?其实在编程得过程中这种情况太常见了,今天仔细分析了一下发现问题得所在:单片机接收一个字节得数据需要移位8次,每次接收前先移位就是为了给接下来接收得数据腾开位置,这样每个数据都可以正确接收; 但就是分析下面得程序您会发现如果接收得数据就是0,那么不会有任何问题,但就是当接收1时,上次得数据就会被接下来得这个1覆盖掉,这正就是问题得所在,试试瞧。

因此我们在利用单片机引脚模拟有些通信时要特别注意什么时候移位,移动几次。

很有可能有时因为多移一次、少移一次或诸如上面得问题而导致接收不正确。

本打算用一篇日志将74hc165、74hc595、74hc164介绍一下瞧来篇幅太长了,下次再叙.如有兴趣请密切关注:

今后本人写日志将更趋向于专业知识,请见谅。