lvds接口定义及原理知识

LVDS原理及设计指南

LVDS原理及设计指南LVDS全称为低压差分信号(Low Voltage Differential Signaling),是一种高速串行接口技术,广泛应用于电子设备中进行高速数据传输。

LVDS主要通过两对差分信号进行数据传输,其中一对信号传输高电平信号,另一对信号传输低电平信号,通过差分运算来提高抗干扰能力和抗噪声能力,以实现高质量的数据传输。

LVDS的工作原理如下:1.发送端:将输入信号通过电流驱动压缩成低压差分信号,并通过双绞线传输给接收端。

2.传输线路:使用双绞线进行数据传输,利用差分运算来抵消传输线上的共模噪声和反射噪声。

3.接收端:对接收到的低压差分信号进行解码,还原成原始的输入信号。

设计LVDS接口时需要注意以下几点:1.信号线路的设计:为了保证信号的完整性和稳定性,需要控制信号线的阻抗匹配,减小信号线的长度和延迟,并避免信号线与高频噪声信号线的交叉和平行布线。

2.布线和PCB设计:保持信号线的长度均匀,并尽量使用同一层或相邻层进行差分信号线布线,以减小信号线之间的不平衡和串扰。

3.电源和接地:为了提供噪声的抑制和信号的稳定性,需要使用低噪声电源和低阻抗接地。

4.EMI抑制:由于LVDS接口传输速率高,会引起较大的电磁辐射干扰,因此需要在设计中加入适当的EMI抑制措施,如电磁屏蔽、地线设计和滤波器等。

5.信号匹配:为了保证所发送信号的完整性和稳定性,需要将发送端与接收端之间的差分阻抗匹配,以最大限度地减小信号反射和串扰。

总之,LVDS是一种高速串行接口技术,通过差分运算进行数据传输,具有抗噪声和抗干扰能力强的特点。

在设计LVDS接口时需注意信号线路的设计、布线和PCB设计、电源和接地、EMI抑制以及信号匹配等方面,以保证高质量的数据传输。

LVDS屏接口定义解析

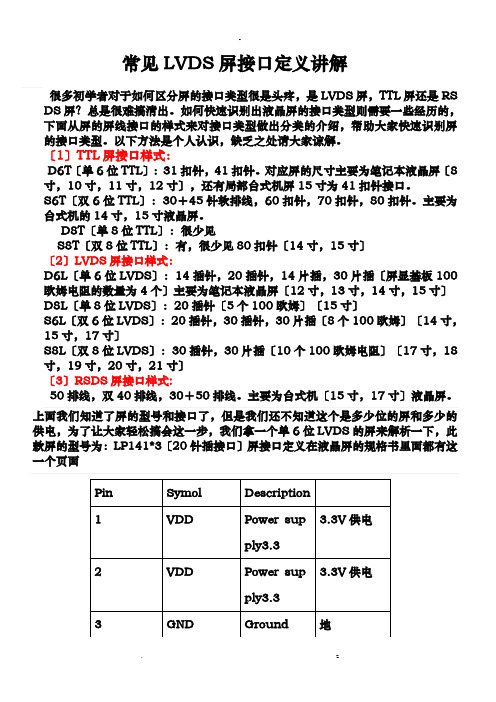

常见LVDS 屏接口定义讲解很多初学者对于如何区分屏的接口类型很是头疼,是LVDS 屏,TTL 屏还是RS DS 屏?总是很难搞清出。

如何快速识别出液晶屏的接口类型则需要一些经历的,下面从屏的屏线接口的样式来对接口类型做出分类的介绍,帮助大家快速识别屏的接口类型。

以下方法是个人认识,缺乏之处请大家谅解。

〔1〕TTL 屏接口样式:D6T 〔单6位TTL 〕:31扣针,41扣针。

对应屏的尺寸主要为笔记本液晶屏〔8寸,10寸,11寸,12寸〕,还有局部台式机屏15寸为41扣针接口。

S6T 〔双6位TTL 〕:30+45针软排线,60扣针,70扣针,80扣针。

主要为台式机的14寸,15寸液晶屏。

D8T 〔单8位TTL 〕:很少见S8T 〔双8位TTL 〕:有,很少见80扣针〔14寸,15寸〕 〔2〕LVDS 屏接口样式:D6L 〔单6位LVDS 〕:14插针,20插针,14片插,30片插〔屏显基板100欧姆电阻的数量为4个〕主要为笔记本液晶屏〔12寸,13寸,14寸,15寸〕 D8L 〔单8位LVDS 〕:20插针〔5个100欧姆〕〔15寸〕S6L 〔双6位LVDS 〕:20插针,30插针,30片插〔8个100欧姆〕〔14寸,15寸,17寸〕S8L 〔双8位LVDS 〕:30插针,30片插〔10个100欧姆电阻〕〔17寸,18寸,19寸,20寸,21寸〕 〔3〕RSDS 屏接口样式:50排线,双40排线,30+50排线。

主要为台式机〔15寸,17寸〕液晶屏。

上面我们知道了屏的型号和接口了,但是我们还不知道这个是多少位的屏和多少的供电,为了让大家轻松搞会这一步,我们拿一个单6位LVDS 的屏来解析一下,此款屏的型号为:LP141*3〔20针插接口〕屏接口定义在液晶屏的规格书里面都有这一个页面在屏的接口定义中我们看出液晶屏的供电为3.3这里面出现了两组数据每组中都有一对时钟信号,这个屏我们就能看出这是一个30针双8位屏,屏的供电为5V。

完整版)LVDS接口详解

完整版)LVDS接口详解LVDS输出接口是一种数字视频信号传输方式,它利用低压差分信号技术接口,在两条PCB走线或一对平衡电缆上通过差分进行数据的传输。

相比于TTL接口,LVDS输出接口具有高速率、低噪声、远距离、高准确度等优点,因此在17in及以上液晶显示器中得到了广泛的应用。

LVDS接口电路由驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)组成。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过柔性电缆传送到液晶面板侧的LVDS接收器。

LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

在数据传输过程中,LVDS接口采用差分信号对的形式进行传输,每个数据传输通道或时钟传输通道的输出都为两个信号(正输出端和负输出端)。

这种方式不仅可以提高数据传输速率,还可以减少电磁干扰和功耗,使得LVDS输出接口更加稳定可靠。

不同种类的液晶显示器的驱动板上的LVDS发送器并不相同。

有些LVDS发送器是一片或两片独立的芯片,例如DS90C383;而有些则是集成在主控芯片中,例如主控芯片gm5221内部集成了LVDS发送器。

LVDS输出接口也分为四种类型,其中第一种是单路6位LVDS输出接口。

这种接口电路采用单路方式传输,每个基色信号(即RGB三色中的其中任何一种颜色)采用6位数据(XOUT0+、TXOUT0-,TXOUT1+、TXOUT1-,TXOUT2+、TXOUT2-),共18位RGB(6bit X 3(RGB3色))数据,因此也被称为18位或18bit LVDS接口。

第二种是双路6位LVDS输出接口。

在这种接口电路中,两个基色信号(例如红色和绿色)共用一条传输线,而蓝色信号则使用另一条传输线,每个基色信号采用6位数据,因此也被称为双路18位或18bit LVDS接口。

LVDS屏接口定义解析

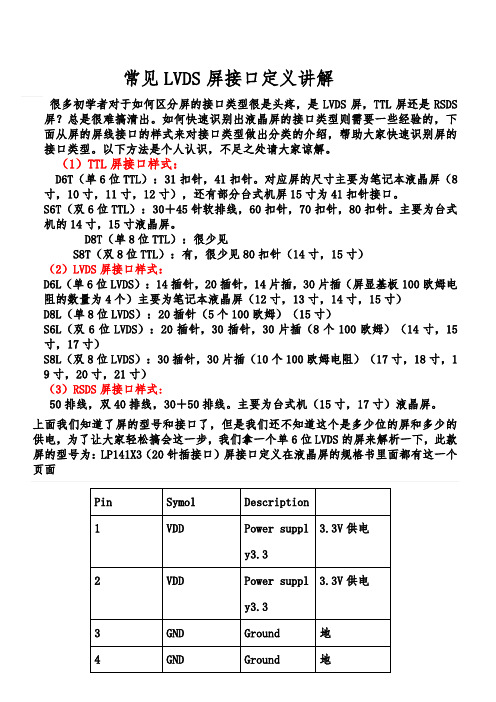

常见LVDS屏接口定义讲解很多初学者对于如何区分屏的接口类型很是头疼,是LVDS屏,TTL屏还是RSDS 屏?总是很难搞清出。

如何快速识别出液晶屏的接口类型则需要一些经验的,下面从屏的屏线接口的样式来对接口类型做出分类的介绍,帮助大家快速识别屏的接口类型。

以下方法是个人认识,不足之处请大家谅解。

(1)TTL屏接口样式:D6T(单6位TTL):31扣针,41扣针。

对应屏的尺寸主要为笔记本液晶屏(8寸,10寸,11寸,12寸),还有部分台式机屏15寸为41扣针接口。

S6T(双6位TTL):30+45针软排线,60扣针,70扣针,80扣针。

主要为台式机的14寸,15寸液晶屏。

D8T(单8位TTL):很少见S8T(双8位TTL):有,很少见80扣针(14寸,15寸)(2)LVDS屏接口样式:D6L(单6位LVDS):14插针,20插针,14片插,30片插(屏显基板100欧姆电阻的数量为4个)主要为笔记本液晶屏(12寸,13寸,14寸,15寸)D8L(单8位LVDS):20插针(5个100欧姆)(15寸)S6L(双6位LVDS):20插针,30插针,30片插(8个100欧姆)(14寸,15寸,17寸)S8L(双8位LVDS):30插针,30片插(10个100欧姆电阻)(17寸,18寸,1 9寸,20寸,21寸)(3)RSDS屏接口样式:50排线,双40排线,30+50排线。

主要为台式机(15寸,17寸)液晶屏。

上面我们知道了屏的型号和接口了,但是我们还不知道这个是多少位的屏和多少的供电,为了让大家轻松搞会这一步,我们拿一个单6位LVDS的屏来解析一下,此款屏的型号为:LP141X3(20针插接口)屏接口定义在液晶屏的规格书里面都有这一个页面这里面出现了两组数据每组中都有一对时钟信号,这个屏我们就能看出这是一个30针双8位屏,屏的供电为5V。

常见的LVDS接口定义20PIN单6定义:1:电源2:电源3:地4:地5:R0- 6:R0+ 7:地8:R1- 9:R1+ 10:地11:R2- 12:R2+ 13:地14:CLK- 15:CLK+ 16空17空18空19空20空每组信号线之间电阻为(数字表100欧左右)指针表20-100欧左右(4组相同阻值)20PIN双6定义:1:电源2:电源3:地4:地5:R0- 6:R0+ 7:R1- 8:R1+ 9:R2- 10:R2+ 11:CLK- 12:CLK+ 13:RO1- 14:RO1+ 15:RO2- 16:RO2+ 17:RO3-18:RO3+19:CLK1- 20:CLK1+知识点:TTL接口的屏线明显比LVDS的屏线多常见31扣41扣30+50 60扣7 0扣80扣TTL的屏也有单组数据和双组数据之分以此类推就可以了常见TTL屏线D6T(单6位TTL):31扣针,41扣针。

LVDS接口定义

LVDS接口又称RS-644总线接口,是20世纪90年代才出现的一种数据传输和接口技术。

LVDS即低电压差分信号,这种技术的核心是采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点,其传输介质可以是铜质的PCB连线,也可以是平衡电缆。

LVDS在对信号完整性、低抖动及共模特性要求较高的系统中得到了越来越广泛的应用。

目前,流行的LVDS技术规范有两个标准:一个是TIA/EIA(电讯工业联盟/电子工业联盟)的ANSI/TIA/EIA-644标准,另一个是IEEE 1596.3标准。

如上图,就是一块单六位LVDS 30针接口的液晶屏,其中1脚GND就是地,2脚、3脚VCC就是电压,4、6、7脚为存储IC(一般为24C之类的芯片)的读写信号脚,就是我们常换DELL机器的屏所说的码片,这里面存储了屏的一些信息,如型号、生产日期等,DELL 之类的少类的机器就往屏上这个IC里写入了自家的识别信号。

8脚R0-、9脚R0+为第一组LVDS信号,依次类推,每往下一组信号中间都空一脚,共三组R-及R+信号,一直到接口的17脚CLKIN-、18脚CLKIN+,这两脚很重要,断开一根线,屏就无法显示,R-+的信号,少了一根两根还可以点亮屏,当然会显示不正常!这四对信号用数字表量阻值表现为100欧--120欧(不同屏)。

像我以前装液晶显示器的时候,这个单六位LVDS,只要对应单六位,再对应屏的分辨率(分辨率很重要)写个程序,屏线只用十根线,几乎就可以点亮这类的屏!这类屏我们常称为单六,当然液晶显示器的屏还有单八,单八的就多了对R3-和R3+,别小看这多出的一对信号,液晶屏的色彩就会多很多~单八位的己经过时了,以前15寸的液晶显示器的屏很多都是单八位的。

当然,还有双八的~现在的市面上的液晶显示器都是双八位的接口啦~这里,我可以大胆的说:笔记本上用的都是单六,和双六的~现在液晶显示器上用的都是双八位了,早期的还有TTL、TMDS、TCON接口的,这类接口的我们修本的完全不必了解。

lvds液晶屏幕接口详解

1.LVDS输出接口概述之答禄夫天创作液晶显示器驱动板输出的数字信号中,除了包含RGB数据信号外,还包含行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超出28MHz。

采取TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB数据造成一定的影响;另外,TTL多路数据信号采取排线的方式来传送,整个排线数量达几十路,不单连接方便,而且不适合超薄化的趋势。

采取LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

那么,什么是LVDS输出接口呢?LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采取LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采取低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

2.LVDS接口电路的组成在液晶显示器中,LVDS接口电路包含两部分,即驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

图1所示为LVDS接口电路的组成示意图。

LVDS(低电压差分信号)原理简介

LVDS(低电压差分信号)原理简介1 、LVDS信号介绍LVDS:Low Voltage Differential Signaling,低电压差分信号。

LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

IEEE在两个标准中对LVDS信号进行了定义。

ANSI/TIA/EIA-644中,推荐最大速率为655Mbps,理论极限速率为1.923Mbps。

1.1 LVDS信号传输组成图1 LVDS信号传输组成图LVDS信号传输一般由三部分组成:差分信号发送器,差分信号互联器,差分信号接收器。

差分信号发送器:将非平衡传输的TTL信号转换成平衡传输的LVDS信号。

通常由一个IC来完成,如:DS90C031差分信号接收器:将平衡传输的LVDS信号转换成非平衡传输的TTL信号。

通常由一个IC来完成,如:DS90C032差分信号互联器:包括联接线(电缆或者PCB走线),终端匹配电阻。

按照IEEE 规定,电阻为100欧。

我们通常选择为100,120欧。

1.2 LVDS信号电平特性LVDS物理接口使用1.2V偏置电压作为基准,提供大约400mV 摆幅。

LVDS驱动器由一个驱动差分线对的电流源组成(通常电流为3.5mA),LVDS接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Ω的匹配电阻,并在接收器的输入端产生大约350mV 的电压。

电流源为恒流特性,终端电阻在100――120欧姆之间,则电压摆动幅度为:3.5mA * 100 = 350mV ;3.5mA * 120 = 420mV 。

下图为LVDS与PECL(光收发器使用的电平)电平变化。

图2 LVDS与PECL电平图示由逻辑“0”电平变化到逻辑“1”电平是需要时间的。

由于LVDS信号物理电平变化在0。

lvds液晶屏幕接口详解

1.LVDS输出接口概述液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。

采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB数据造成一定的影响;另外,TTL多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

那么,什么是LVDS输出接口呢?LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

2.LVDS接口电路的组成在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

图1所示为LVDS接口电路的组成示意图。

图1 LVDS接口电路的组成示意图在数据传输过程中,还必须有时钟信号的参与,LVDS接口无论传输数据还是传输时钟,都采用差分信号对的形式进行传输。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

lvds接口定义及原理知识LVDS接口定义作者:bechade 更新时间:2007-9-22 7:31:10 文章录入:chfygl--------------------------------------------------------------------------------20PIN单6定义:1:电源2:电源3:地4:地5:R0-6:R0+ 7:地8:R1-9:R1+ 10:地11:R2-12:R2+ 13:地14:CLK-15:CLK+ 16空17空18空19 空20空每组信号线之间电阻为(数字表120欧左右)20PIN双6定义:1:电源2:电源3:地4:地5:R0-6:R0+ 7:R1-8:R1+ 9:R2-10:R2+ 11:CLK-12:CLK+ 13:RO1-14:RO1+ 15:RO2-16:RO2+ 17:RO3-18:RO3+19:CLK1-20:CLK1+每组信号线之间电阻为(数字表120欧左右)20PIN单8定义:1:电源2:电源3:地4:地5:R0-6:R0+ 7:地8:R1-9:R1+ 10:地11:R2-12:R2+ 13:地14:CLK-15:CLK+ 16:R3-17:R3+每组信号线之间电阻为(数字表120欧左右)30PIN单6定义:1:空2:电源3:电源4:空5:空6:空7:空8:R0-9:R0+ 10:地11:R1-12:R1+ 13:地14:R2-15:R2+ 16:地17:CLK-18:CLK+ 19:地20:空-21:空22:空23:空24:空25:空26:空27:空28空29空30空每组信号线之间电阻为(数字表120欧左右)30PIN单8定义:1:空2:电源3:电源4:空5:空6:空7:空8:R0-9:R0+ 10:地11:R1-12:R1+ 13:地14:R2-15:R2+ 16:地17:CLK-18:CLK+ 19:地20:R3-21:R3+ 22:地23:空24:空25:空26:空27:空28空29空30空每组信号线之间电阻为(数字表120欧左右)30PIN双6定义:1:电源2:电源3:地4:地5:R0-6:R0+ 7:地8:R1-9:R1+ 10:地11:R2-12:R2+ 13:地14:CLK-15:CLK+ 16:地17:RS0-18:RS0+ 19:地20:RS1-21:RS1+ 22:地23:RS2-24:RS2+ 25:地26:CLK2-27:CLK2+每组信号线之间电阻为(数字表120欧左右)30PIN双8定义:1:电源2:电源3:电源4:空5:空6:空7:地8:R0-9:R0+ 10:R1-11:R1+ 12:R2-13:R2+ 14:地15:CLK-16:CLK+ 17:地18:R3-19:R3+ 20:RB0-21:RB0+ 22:RB1-23:RB1+ 24:地25:RB2-26:RB2+ 27:CLK2- 28:CLK2+ 29:RB3-30:RB3+每组信号线之间电阻为(数字表120欧左右)一般14PIN、20PIN、30PIN为LVDS接口。

什么是LVDS?现在的液晶显示屏普遍采用LVDS接口,那么什么是LVDS呢?LVDS(Low Voltage Differential Signaling)即低压差分信号传输,是一种满足当今高性能数据传输应用的新型技术。

由于其可使系统供电电压低至2V,因此它还能满足未来应用的需要。

此技术基于ANSI/TIA/EIA-644 LVDS 接口标准。

LVDS 技术拥有330mV 的低压差分信号(250mV MIN and 450mV MAX) 和快速过渡时间。

这可以让产品达到自100 Mbps 至超过1 Gbps 的高数据速率。

此外,这种低压摆幅可以降低功耗消散,同时具备差分传输的优点。

LVDS 技术用于简单的线路驱动器和接收器物理层器件以及比较复杂的接口通信芯片组。

通道链路芯片组多路复用和解多路复用慢速TTL 信号线路以提供窄式高速低功耗LVDS 接口。

这些芯片组可以大幅节省系统的电缆和连接器成本,并且可以减少连接器所占面积所需的物理空间。

LVDS 解决方案为设计人员解决高速I/O 接口问题提供了新选择。

LVDS 为当今和未来的高带宽数据传输应用提供毫瓦每千兆位的方案。

更先进的总线LVDS (BLVDS)是在LVDS 基础上面发展起来的,总线LVDS (BLVDS) 是基于LVDS 技术的总线接口电路的一个新系列,专门用于实现多点电缆或背板应用。

它不同于标准的LVDS,提供增强的驱动电流,以处理多点应用中所需的双重传输。

BLVDS 具备大约250mV 的低压差分信号以及快速的过渡时间。

这可以让产品达到自100 Mbps 至超过1Gbps 的高数据传输速率。

此外,低电压摆幅可以降低功耗和噪声至最小化。

差分数据传输配置提供有源总线的+/-1V 共模范围和热插拔器件。

BLVDS 产品有两种类型,可以为所有总线配置提供最优化的接口器件。

两个系列分别是:线路驱动器和接收器和串行器/解串器芯片组。

总线LVDS 可以解决高速总线设计中面临的许多挑战。

BLVDS 无需特殊的终端上拉轨。

它无需有源终端器件,利用常见的供电轨(3.3V 或5V),采用简单的终端配置,使接口器件的功耗最小化,产生很少的噪声,支持业务卡热插拔和以100 Mbps 的速率驱动重载多点总线。

总线LVDS 产品为设计人员解决高速多点总线接口问题提供了一个新选择。

附件:摘要:介绍了LVDS(低电压差分信号)技术的原理和应用,并讨论了在单板和系统设计中应用LVDS时的布线技巧。

关键词:LVDS PCB设计1 LVDS介绍LVDS(Low Voltage Differential Signaling)是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

几十年来,5V供电的使用简化了不同技术和厂商逻辑电路之间的接口。

然而,随着集成电路的发展和对更高数据速率的要求,低压供电成为急需。

降低供电电压不仅减少了高密度集成电路的功率消耗,而且减少了芯片内部的散热,有助于提高集成度。

减少供电电压和逻辑电压摆幅的一个极好例子是低压差分信号(LVDS)。

LVDS物理接口使用1.2V 偏置提供400mV摆幅的信号(使用差分信号的原因是噪声以共模的方式在一对差分线上耦合出现,并在接收器中相减从而可消除噪声)。

LVDS驱动和接收器不依赖于特定的供电电压,因此它很容易迁移到低压供电的系统中去,而性能不变。

作为比较,ECL和PECL技术依赖于供电电压,ECL要求负的供电电压,PECL参考正的供电电压总线上电压值(Vcc)而定。

而GLVDS是一种发展中的标准尚未确定的新技术,使用500mV的供电电压可提供250mV 的信号摆幅。

不同低压逻辑信号的差分电压摆幅示于图1。

LVDS在两个标准中定义。

IEEE P1596.3(1996年3月通过),主要面向SCI(Scalable Coherent Interface),定义了LVDS的电特性,还定义了SCI协议中包交换时的编码;ANSI/EIA/EIA-644(1995年11月通过),主要定义了LVDS的电特性,并建议了655Mbps的最大速率和1.823Gbps的无失真媒质上的理论极限速率。

在两个标准中都指定了与物理媒质无关的特性,这意味着只要媒质在指定的噪声边缘和歪斜容忍范围内发送信号到接收器,接口都能正常工作。

LVDS具有许多优点:①终端适配容易;②功耗低;③具有fail-safe特性确保可靠性;④低成本;⑤高速传送。

这些特性使得LVDS在计算机、通信设备、消费电子等方面得到了广泛应用。

图2给出了典型的LVDS接口,这是一种单工方式,必要时也可使用半双工、多点配置方式,但一般在噪声较小、距离较短的情况下才适用。

每个点到点连接的差分对由一个驱动器、互连器和接收器组成。

驱动器和接收器主要完成TTL信号和LVDS信号之间的转换。

互连器包含电缆、PCB上差分导线对以及匹配电阻。

LVDS驱动器由一个驱动差分线对的电流源组成通常电流为3.5mA),LVDS接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Ω的匹配电阻,并在接收器的输入端产生大约350mA 的电压。

当驱动器翻转时,它改变流经电阻的电流方向,因此产生有效的逻辑〃1〃和逻辑〃0〃状态。

低摆幅驱动信号实现了高速操作并减小了功率消耗,差分信号提供了适当噪声边缘和功率消耗大幅减少的低压摆幅。

功率的大幅降低允许在单个集成电路上集成多个接口驱动器和接收器。

这提高了PCB板的效能,减少了成本。

不管使用的LVDS传输媒质是PCB线对还是电缆,都必须采取措施防止信号在媒质终端发生反射,同时减少电磁干扰。

LVDS要求使用一个与媒质相匹配的终端电阻(100±20Ω),该电阻终止了环流信号,应该将它尽可能靠近接收器输入端放置。

LVDS驱动器能以超过155.5Mbps的速度驱动双绞线对,距离超过10m。

对速度的实际限制是:①送到驱动器的TTL数据的速度;②媒质的带宽性能。

通常在驱动器侧使用复用器、在接收器侧使用解复用器来实现多个TTL信道和一个LVDS信道的复用转换,以提高信号速率,降低功耗。

并减少传输媒质和接口数,降低设备复杂性。

LVDS接收器可以承受至少±1V的驱动器与接收器之间的地的电压变化。

由于LVDS驱动器典型的偏置电压为+1.2V,地的电压变化、驱动器偏置电压以及轻度耦合到的噪声之和,在接收器的输入端相对于接收器的地是共模电压。

这个共模范围是:+0.2V~+2.2V。

建议接收器的输入电压范围为:0V~+ 2.4V。

2 LVDS系统的设计LVDS系统的设计要求设计者应具备超高速单板设计的经验并了解差分信号的理论。

设计高速差分板并不很困难,下面将简要介绍一下各注意点。

2.1 PCB板(A)至少使用4层PCB板(从顶层到底层):LVDS信号层、地层、电源层、TTL信号层;(B)使TTL信号和LVDS信号相互隔离,否则TTL可能会耦合到LVDS线上,最好将TTL和LVDS信号放在由电源/地层隔离的不同层上;(C)使LVDS驱动器和接收器尽可能地靠近连接器的LVDS 端;(D)使用分布式的多个电容来旁路LVDS设备,表面贴电容靠近电源/地层管脚放置;(E)电源层和地层应使用粗线,不(F)保持PCB地线层返回路径宽而短;(G)要使用50Ω布线规则;应该使用利用地层返回铜线(gu9ound return wire)的电缆连接两个系统的地层;(H)使用多过孔(至少两个)连接到电源层(线)和地层(线),表面贴电容可以直接焊接到过孔焊盘以减少线头。