数字电路习题

数字电路考试题

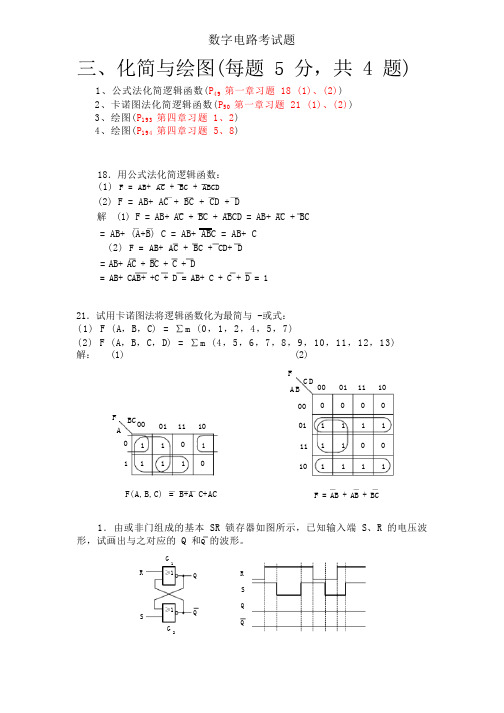

三、化简与绘图(每题 5 分,共 4 题)1、公式法化简逻辑函数(P 49 第一章习题 18 (1)、(2))2、卡诺图法化简逻辑函数(P 50 第一章习题 21 (1)、(2))3、绘图(P 193 第四章习题 1、2)4、绘图(P 194 第四章习题5、8)18.用公式法化简逻辑函数: (1) F = AB+ AC + BC + ABCD (2) F = AB+ AC + BC + CD + D解 (1) F = AB+ AC + BC + ABCD = AB+ AC + BC = AB+ (A+B) C = AB+ ABC = AB+ C (2) F = AB+ AC + BC + CD+ D= AB+ AC + BC + C + D= AB+ CAB+ +C + D = AB+ C + C + D = 121.试用卡诺图法将逻辑函数化为最简与 -或式: (1) F (A ,B ,C ) = ∑m (0,1,2,4,5,7)(2) F (A ,B ,C ,D ) = ∑m (4,5,6,7,8,9,10,11,12,13) 解: (1) (2)F(A,B,C) = B+A C+ACF C D A B 000111 10F = AB + AB + BC1.由或非门组成的基本 SR 锁存器如图所示,已知输入端 S 、R 的电压波 形,试画出与之对应的 Q 和Q 的波形。

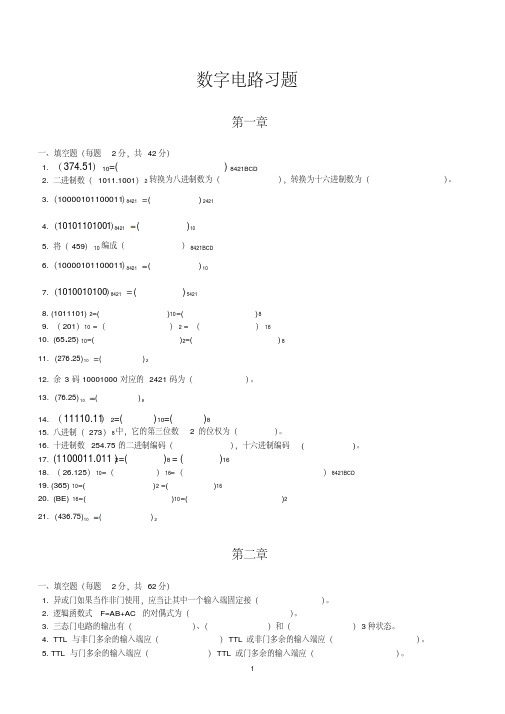

G 1≥1≥1SQGF BC00 A 0 1 1 101 1 111 0 110 1 001 0 1 1 1000 1 1 111 0 1 0 110 0 1 0 1R SQ QQR 2RSQQ2.由与非门组成的基本 SR 锁存器如图 P4.2 所示,已知输入端S 、R 的电压波形,试画出与之对应的G1&&RG2Q 和Q 的波形。

SRQQ解:SRQQ5.钟控 SR 锁存器符号如图 P4.5 (a)所示,设初始状态为0,假如给定CP、S、R 的波形如图 P4.5 (b)所示,试画出相应的输出 Q 波形。

数字电路习题资料

1 数字电路习题第一章一、填空题(每题2分,共42分)1. (374.51)10=( ) 8421BCD2. 二进制数(1011.1001)2转换为八进制数为(),转换为十六进制数为()。

3. 24218421)(00111000010110)(4.108421)(11010110100)(5. 将(459)10编成()8421BCD6. 108421)(00111000010110)(7. 54218421)(1010010100)(8. (1011101) 2=( )10=( )89. (201)10 =()2 = ()1610.(65.25) 10=( )2=( )811. 210)()25.276(12. 余3码10001000对应的2421码为()。

13. 810)()25.76(14. (11110.11)2=( )10=( )815. 八进制(273)8中,它的第三位数 2 的位权为()。

16. 十进制数254.75的二进制编码(),十六进制编码( )。

17.(1100011.011 )2=( )8 = ( )1618. (26.125)10=()16=()8421BCD19. (365) 10=( )2 =( )1620.(BE) 16=( )10=( )221. 210)()75.436(第二章一、填空题(每题2分,共62分)1. 异或门如果当作非门使用,应当让其中一个输入端固定接()。

2. 逻辑函数式F=AB+AC 的对偶式为()。

3. 三态门电路的输出有()、()和()3种状态。

4.TTL 与非门多余的输入端应()TTL 或非门多余的输入端应()。

5. TTL 与门多余的输入端应()TTL 或门多余的输入端应()。

聊城大学《数字电路》期末复习题及参考答案

《数字电路》练习题及参考答案一、逻辑函数化简1.用卡诺图法将逻辑函数化简为最简与一一或表达式Y=ABC+ABD+CD'+AB C+A'CD'+ACDY=A+D2.用卡诺图法将逻辑函数化简为最简与一一或表达式Y=AB,+B,C+ΛD二、简答题1.时序逻辑电路在逻辑功能和电路结构上各有什么特点?答:逻辑功能上:任意时刻的输出不仅取决于这一时刻的输入,还与电路的历史状态有关。

电路结构上:①包含存储电路和组合电路;②存储器状态和输入变量共同决定输出。

3.简述触发器电路必须具备的两个基本特点。

答:1.有两个可以自行保持的状态;2.可以根据不同的输入置成。

或1状态三、设计题1.用4选1数字选择器(74HC153/2)产生逻辑函数:Z=AβC+A t C+BC(数据选择器输出方程为Y=D0(AAi)+D i(A i A0)+D2(A i A n)+D y(A i A ii))已知输出方程为:Y=(AA)Qo+(AA)S+(AA)Qf(AA)A将给定逻辑函数化为与输出方程对应的形式为:Y=Aβ,C+A BI+ABC+ABC另数据选择器输入接成:Al=A;Ao=8;D 0=D 2=C ,;D 1=1;D 3=C2 .用3线一8线译码器74HC138和门电路产生如下多输出逻辑函数。

Y 1=ACY 2=A ,B ,C+AffC ,+BCY i =B'C+ABCY i =AC=ΛffC+ΛBC=nι5+m 7=(m 5,m 7y=(Y 5,Y 7y<Y 2≈A ,B ,C+AffC ,+BC=A'B ,C+A;BC+AB ,C+ABC≈m i +m 3+fn i +m 7≈(m,,m 3,m 4'm ιy=(Y l 'Y i ,Y 4,Y 7y X=B'C+46C=A'B'C+A&C+ABC=,/+,%+%=(/'%6')'=(可匕工)画出电路为:则:Y=Z接电路为:3¾%J %41IΛβ与。

数字电路练习题

选择1、有八个触发器的二进制计数器,它们最多有( C )种计数状态。

A 、8;B 、16;C 、256;D 、642、下列触发器中上升沿触发的是( D )。

A 、主从RS 触发器;B 、JK 触发器;C 、T 触发器;D 、D 触发器3、下式中与非门表达式为( D ),或门表达式为( A )。

A 、Y=A+B ;B 、Y=AB ;C 、Y=B A +;D 、Y=AB4、十二进制加法计数器需要( C )个触发器构成。

A 、8;B 、16;C 、4;D 、35、逻辑电路如右图,函数式为(A )。

A 、F=AB +C ; B 、F=AB +C ;C 、F=C AB +;D 、F=A+BC6、逻辑函数F=AB+BC 的最小项表达式为( C )A 、F=m 2+m 3+m 6B 、F=m 2+m 3+m 7C 、F=m 3+m 6+m 7D 、F=m 3+m 4+m 77、74LS138译码器有( A ),74LS148编码器有( C )A 、三个输入端,三个输出端;B 、八个输入端,八个输出端;C 、三个输入端,八个输出端;D 、八个输入端,三个输出端。

8、单稳态触发器的输出状态有( A )A 、一个稳态、一个暂态B 、两个稳态C 、只有一个稳态D 、没有稳态1、对于MOS 门电路,多余端不允许( A )A 、悬空B 、与有用端并联C 、接电源D 、接低电平2、右图①表示( A )电路,②图表示( B )电路A、与门 B、或门C、非门 D、与非门3、卡诺图③、④表示的逻辑函数最简式分别为( C )和( B )A 、F=B +DB 、F=B+DC 、F=BD+B DD 、F=BD+BD4、逻辑电路如图⑤,函数式为( A )A 、 F=AB +CB 、 F =A B +CC 、 F=AB +CD 、F=A+B C5、一位8421B C D 码计数器至少需要 B 个触发器。

A.3B.4C.5D.106、下列逻辑函数表达式中与F=A B +A B 功能相同的是( A )A 、B A ⊕ B 、B A ⊕C 、B A ⊕D 、B A ⊕7、施密特触发器常用于( A )A 、脉冲整形与变换B 、定时、延时C 、计数D 、寄存8、施密特触发器的输出状态有 BA 、一个稳态、一个暂态B 、两个稳态C 、只有一个稳态D 、没有稳态1、对于MOS 门电路,多余端不允许 AA 、悬空B 、与有用端并联C 、接电源D 、接低电平2、一个8选1多路选择器,输入地址有 ,16选1多路选择器输入地址有 。

数字电路课堂练习题——第4章

第 1 页/共 3 页1. 按照电路图,画Q 的波形。

2. 上图当D S =D R =0时,1n Q +=?1n Q +=?当D S 和D R 同时恢复到“1”时,保持的是什么状态?A : 当D S =D R =0时,1n Q +=1,1n Q +=1;当D S 和D R 同时恢复到“1”时,保持状态不决定。

3. 上图想要1n Q +=0,D S 和D R 加什么触发?经过几个t pd 后1n Q +=0?A : 想要1n Q +=0,D S 和D R 加“置0”触发,D S =1,D R =0;经过2个t pd 后1n Q +=0。

4. 上图想要1n Q +=1,D S 和D R 加什么触发?要经过几个t pd 后1n Q +=1?A : 想要1n Q +=1,D S 和D R 加“置1”触发,D S =0,D R =1;经过1个t pd 后1n Q +=1。

5. 当D S =D R =0时,1n Q +=1,1n Q +=?随后D S =0、D R =1时,1n Q +=?。

A : 当D S =D R =0时,1n Q +=1,1n Q +=1; 随后D S =01n Q +=1。

R D S D & &Q Q R D S D Q1. 有两个触发器如下,当CP 和D 有如下波形时,画Q 1、Q 2波形。

2. 用边沿D 触发器实现将CP 频率下降1/2和1/4的电路。

A : 触发器特征方程为 1n n Q D Q +==每来一个时钟升高沿,Q 翻转一次,Q 1输出为2分频,Q 2输出为4分频。

T 1和T 2。

A : T 2≥T su4. 当同步RS 触发器要想Q n+1=1时,RS 应加什么触发信号?写出特征方程。

求CP QQ T →=?A : 应加R=0、S=1时,Q n+1=1特征方程 约束条件:0S R ⋅=CP QQ T →=3t pd 5. 当同步RS 触发器R=S=1时,1n Q +=?1n Q +=?随后R=S=0,问1n Q +=?倘若R=S=1之后R=1、S=0,1n Q +=?A : R=S=1时,1n Q +=1,1n Q +=1随后R=S=0, 1n Q +=为不定状态 倘若R=S=1之后R=1、S=0,1n Q +=0D 1 Q 1 D 2 Q 2Q 2D Q 1 CP第3页/共3页。

数字电路习题库

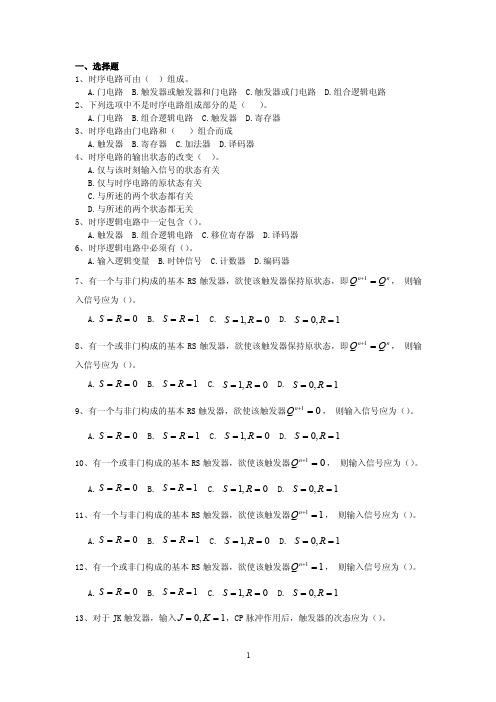

一、选择题1、时序电路可由( )组成。

A.门电路B.触发器或触发器和门电路C.触发器或门电路D.组合逻辑电路 2、下列选项中不是时序电路组成部分的是( )。

A.门电路 B.组合逻辑电路 C.触发器 D.寄存器 3、时序电路由门电路和( )组合而成A.触发器B.寄存器C.加法器D.译码器 4、时序电路的输出状态的改变( )。

A.仅与该时刻输入信号的状态有关 B.仅与时序电路的原状态有关 C.与所述的两个状态都有关 D.与所述的两个状态都无关5、时序逻辑电路中一定包含()。

A.触发器B.组合逻辑电路C.移位寄存器D.译码器 6、时序逻辑电路中必须有()。

A.输入逻辑变量B.时钟信号C.计数器D.编码器7、有一个与非门构成的基本RS 触发器,欲使该触发器保持原状态,即n n Q Q =+1, 则输入信号应为()。

A.0==R SB. 1==R SC. 0,1==R SD. 1,0==R S8、有一个或非门构成的基本RS 触发器,欲使该触发器保持原状态,即n n Q Q =+1, 则输入信号应为()。

A.0==R SB. 1==R SC. 0,1==R SD. 1,0==R S9、有一个与非门构成的基本RS 触发器,欲使该触发器01=+n Q , 则输入信号应为()。

A.0==R S B. 1==R S C. 0,1==R S D. 1,0==R S10、有一个或非门构成的基本RS 触发器,欲使该触发器01=+n Q , 则输入信号应为()。

A.0==R S B. 1==R S C. 0,1==R S D. 1,0==R S11、有一个与非门构成的基本RS 触发器,欲使该触发器11=+n Q , 则输入信号应为()。

A.0==R S B. 1==R S C. 0,1==R S D. 1,0==R S 12、有一个或非门构成的基本RS 触发器,欲使该触发器11=+n Q, 则输入信号应为()。

A.0==R S B. 1==R S C. 0,1==R S D. 1,0==R S13、对于JK 触发器,输入1,0==K J ,CP 脉冲作用后,触发器的次态应为()。

数字电路习题1

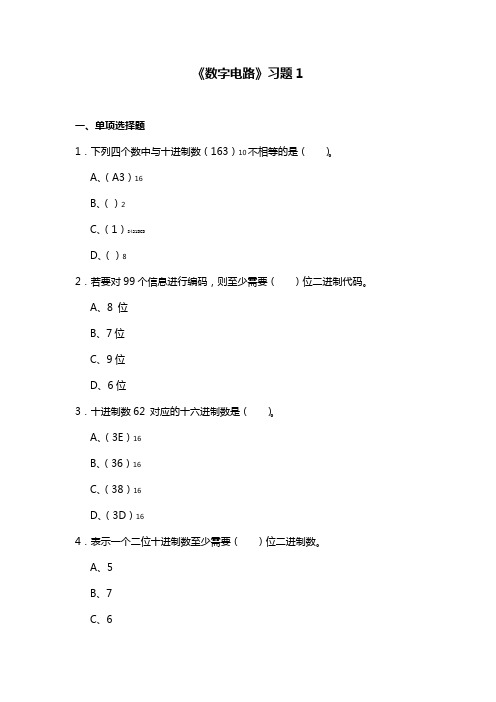

《数字电路》习题1一、单项选择题1.下列四个数中与十进制数(163)10不相等的是()。

A、(A3)16B、()2C、(1)8421BCDD、()82.若要对99个信息进行编码,则至少需要()位二进制代码。

A、8 位B、7位C、9位D、6位3.十进制数62 对应的十六进制数是()。

A、(3E)16B、(36)16C、(38)16D、(3D)164.表示一个二位十进制数至少需要()位二进制数。

A、5B、7C、6D、85.以下说法中,()是正确的。

A、一个逻辑函数全部最小项之和恒等于1B、一个逻辑函数全部最大项之和恒等于0C、一个逻辑函数全部最小项之积恒等于1D、一个逻辑函数全部最大项之积恒等于16.对TTL与非门多余输入端的处理,不能将它们()。

A、与有用端连在一起B、悬空C、接高电平D、接地7.下列几种说法中与BCD码的性质不符的是()。

A、一组4 位二进制数组成的码只能表示一位十进制数B、BCD码是一种人为选定的0~9十个数字的代码C、BCD码是一组4位二进制数,能表示十六以内的任何一个十进制数D、BCD码有多种8.一个基本RS触发器能记忆()位二进制数。

A、2B、1C、3D、49.存在()组取值使最小项ABCD的值为0。

A、1B、7C、15D、310.在数字电路中实现从一组输入数据中选择出某一个来输出,这种电路称为()。

A、编码器B、译码器C、数据选择器D、加法器11.若两逻辑式相等,则它们的对偶式也相等,这就是()。

A、对偶定理B、代入定理C、反演定理D、摩根定理二、多项选择题1.欲使JK触发器按Qn+1=0工作,可使JK触发器的输入端()。

A、J=K=1B、J=Q,K=QC、J=Q,K=1D、J=0,K=12.逻辑变量的取值1和0可以表示()。

A、开关的闭合、断开B、电位的高、低C、真与假D、电流的有、无3.逻辑函数的表示方法中具有唯一性的有哪些?()A、真值表B、表达式C、逻辑图D、卡诺图4.常用的BCD码有()。

数字电子基础练习题答案

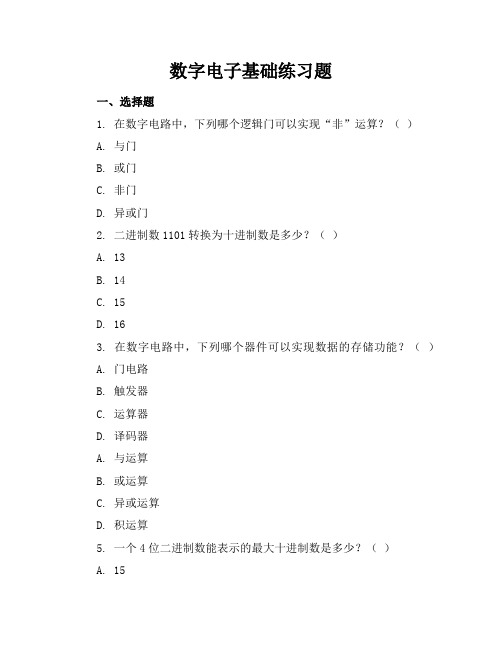

数字电子基础练习题一、选择题1. 在数字电路中,下列哪个逻辑门可以实现“非”运算?()A. 与门B. 或门C. 非门D. 异或门2. 二进制数1101转换为十进制数是多少?()A. 13B. 14C. 15D. 163. 在数字电路中,下列哪个器件可以实现数据的存储功能?()A. 门电路B. 触发器C. 运算器D. 译码器A. 与运算B. 或运算C. 异或运算D. 积运算5. 一个4位二进制数能表示的最大十进制数是多少?()A. 15B. 16C. 17D. 18二、填空题1. 在数字电路中,逻辑“0”和逻辑“1”分别代表______和______电平。

2. 二进制数1110转换为八进制数是______。

3. 一个触发器可以存储______位二进制信息。

4. 在数字电路中,实现算术运算的电路称为______。

5. n位二进制数可以表示的不同状态有______个。

三、判断题1. 在数字电路中,正逻辑和负逻辑的电压范围是相同的。

()2. 两个二进制数相加,和的位数一定比被加数和加数的位数多。

()3. 触发器是数字电路中的基本存储单元。

()4. 逻辑门电路的输出与输入之间存在线性关系。

()5. 二进制数和十六进制数之间的转换需要通过十进制数进行。

()四、简答题1. 请简述数字电路与模拟电路的区别。

2. 什么是逻辑门?请举例说明常见的逻辑门及其功能。

3. 请解释半加器和全加器的区别。

4. 简述二进制数与八进制数之间的转换方法。

5. 请列举至少三种常见的数字电路器件,并说明其功能。

五、综合题1. 给定一个4位二进制数1011,请将其转换为十进制数。

2. 设计一个简单的38译码器电路,并说明其工作原理。

5. 请简述触发器在数字电路中的作用,并以D触发器为例,说明其工作原理。

六、计算题a) 101011b) 11011101c) 111100001a) 25b) 63c) 128a) 1101 + 1011b) 11101 + 10111c) 1001101 + 110111a) 1010 110b) 111100 10101c) 10011011 11011a) 10101111b) 110011001c) 111100001111七、分析题2. 给定一个4位二进制计数器,说明其工作原理,并计算计数器的最大计数值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字电路习题第一章一、填空题(每题2分,共42分)1. (374.51)10=( ) 8421BCD2. 二进制数(1011.1001)2转换为八进制数为( ),转换为十六进制数为( )。

3. 24218421)(00111000010110=)(4. 108421)(11010110100=)(5. 将(459)10编成( )8421BCD6. 108421)(00111000010110=)(7. 54218421)(1010010100=)(8. (1011101) 2=( )10=( )89. (201)10 =( )2 = ( )1610. (65.25) 10=( )2=( )811. 210)()25.276(=12. 余3码10001000对应的2421码为( )。

13. 810)()25.76(=14. (11110.11)2=( )10=( )815. 八进制(273)8中,它的第三位数2 的位权为( )。

16. 十进制数254.75的二进制编码( ),十六进制编码 ( )。

17. (1100011.011 )2=( )8 = ( )1618. (26.125)10=( )16=( )8421BCD19. (365) 10=( )2 =( )1620. (BE) 16=( )10=( )221. 210)()75.436(=第二章一、填空题(每题2分,共62分)1. 异或门如果当作非门使用,应当让其中一个输入端固定接( )。

2. 逻辑函数式F=AB+AC 的对偶式为( )。

3. 三态门电路的输出有( )、( )和( )3种状态。

4. TTL 与非门多余的输入端应( )TTL 或非门多余的输入端应()。

5. TTL 与门多余的输入端应( )TTL 或门多余的输入端应( )。

6. 逻辑函数 F=BC B A +⋅的最小项之和表达式为( )。

7. Y=(A+B+C )A B C 对偶式为Y /=( )。

8. 已知Y=D AC BC B A ++,则Y =( )。

9. 任何逻辑函数都可以表示成最小项的( )及最大项的( )10. Y= ABC+AD+C 对偶式为Y /=( )。

11. Y=AB+CDE+0 的反函数式为( )。

12. 逻辑函数式F=AB+AC 的最小项表达式为( )。

13. 函数1F AB BC =+的反演式1F =( )。

14. F =AB+BC+CA 的“与非”逻辑式为( )。

15. 有一数码10010011,作为自然二进制数时,它相当于十进制数( ),作为8421BCD 码时,它相当于十进制数( )。

16. 用与非门实现逻辑函数F=AB+CD ,逻辑函数应该改成F=( )。

17. 逻辑函数F=)(B A A ⊕⊕=( )。

18. 已知A B A B B A Y +++=,化简后结果是( )。

19. OC 门能实现( )逻辑运算的电路连接,采用总线结构,分时传输数据时,应选用( )。

20. 二进制数111011.101转化成十进制数为( )转化成八进制数为( )。

21. 已知某函数⎪⎭⎫ ⎝⎛+⎪⎭⎫ ⎝⎛++=D C AB D C A B F ,该函数的反函数F =( )。

22. C A AB Y +=,Y 的最简与或式为( )。

23. 函数)(D C A AB A Y +++=,其对偶式为( )。

24. 逻辑函数F=BDE AC C B B A ++的最简与或式为( )。

25. 1F =AB C AB C B A C B A +++,2F =)(C A B B A ⊕+, 它们之间的关系是( )。

26. 逻辑函数Y A B C =+的两种标准形式分别为( )、( )。

27. 函数)(D C A AB A Y +++=,其反函数为( )。

28. 已知逻辑函数F =A ⊕B ,它的或与非表达式为( )。

29. 在函数F=AB+CD 的真值表中,F=1的状态有( )个。

30. Y=AB+C+AD 的反函数式为( )。

31. F=A BCD+A B C+AB C +ABC=Σm ( )。

二、函数化简题(每题5分,共200分)1. 化简逻辑函数)14,10,6,4,2,0(),,,(m D C B A Y ∑=2. 化简逻辑函数3. 化简逻辑函数F AB AD BD BCE =+++4. 化简逻辑函数C A D AC C B A F ++=5. 化简逻辑函数C B C B C A C A Y +++=6. 化简逻辑函数Z=C B A C B A B A ∙∙+∙∙+BC=07. 化简逻辑函数C AB C B BC A AC F +++=8. 化简逻辑函数F ( A,B,C,D )=∑m (0,1,2,4,5,9)+∑d (7,8,10,11,12,13)9. 化简逻辑函数(1,3,4,9,11,12,14,15)(5,6,7,13)m d Y =∑+∑10. 化简逻辑函数(,,,)(0,2,5,7,8,10,13,15)L A B C D m =∑11. 化简逻辑函数F= ∑m (1,3,8,9,10,11,14,15)12. 化简逻辑函数)15,14,7,6,3,2(),,(m C B A Y ∑=13. 化简逻辑函数L AB AB AB AB =+++14. F= ∑m(0,2,3,4,8,10,11)15. 化简逻辑函数)15,14,13,12,10,9,8,7,5,1,0(),,,(m D C B A L ∑=16. 化简逻辑函数F(A,B,C,D)=∑m (0,6,9,10,12,15)+∑d (2,7,8,11,13,14)17. 化简逻辑函数D C B A C B A D C B A C AB D C B A Y +⋅+⋅⋅+=),,,(,且A ,B ,C ,D 不可能同时为0。

18. 化简逻辑函数()()()∑∑15125214137431,,,+,,,,,=,,,d m D C B A F 19. 化简逻辑函数()()∑131********,,,,,,,=,,,m D C B A F 20. 化简逻辑函数)10,9,8,6,5,4,2,1,0(),,,(m D C B A L ∑=21. 化简逻辑函数ABC C ABC B ABC A Y ∙∙=22. 化简逻辑函数F (A 、B 、C 、D )=Σm (0,2,8,9,10,11,13,15)23. 化简逻辑函数Y BCD BC ACD ABD =+++24. 化简逻辑函数25. 用卡诺图把下逻辑函数化简成最简与或式。

D C B A D C B A D C A Y ++++=给定约束条件为0=+++++ABCD D ABC D C AB D C AB CD B A D C B A26. 化简逻辑函数)14,11,10,6,3,2()12,9,4,1,0(),,,(d m D C B A Y ∑+∑=27. 化简逻辑函数)15,11,5,3,2()13,9,6,4,1,0(),,,(d m D C B A Y ∑+∑=28. 逻辑函数Y (A ,B ,C ,D )=∑)9,6,5,4,2,1(约束条件为AB+AC=029. 化简逻辑函数BC DE C B BD A BD C A F +++++=)())((30. 化简逻辑函数()()()()DC B AD C B A D C B A D C B ++++++++++++=A F ()D A +31. 用公式化简逻辑函数:C B C A B A D B BC D C A Y ⋅+++++⋅=32. 化简逻辑函数()D C A C B A B A D C Y ⋅++⊕=,给定约束条件为AB +CD =0。

33. 已知 ,试证明 = 。

34. 化简逻辑函数F= A(B+C ) +A (B +C)+ BCDE+B C (D+E)F35. 化简逻辑函数DE B A D BC A C B A D C D B C B AC Y +++++++=)(36. 化简逻辑函数D C A CD B A Y ⊕++⋅+=37. 化简逻辑函数()()()()()C B D B C A B A C A F +++++=38. 化简逻辑函数()()∑15,141311109765410,,,,,,,,,,=,,,m D C B A F 39. 化简逻辑函数()()BC AD C B A B A F ++∙+=C B A40. 化简逻辑函数D C A C B A D C D C A ABD ABC Y ++⋅+++= 第四章一、填空题(每题2分,共4分)1. 2004 个1进行异或运算的结果为( )。

2. 74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为( )。

二、综合分析题(每题15分,共15分)1. 试分析如图所示的组合逻辑电路。

1. 写出输出逻辑表达式;2. 化为最简与或式;3. 列出真值表;4. 说明逻辑功能。

三、综合设计题(每题15分,共300分)1. 某汽车驾驶员培训班结业考试,有三名评判员,其中A 为主评判员,B 、C 为副评判员,评判时,按照少数服从多数原则,但若主评判员认为合格也可以通过。

试用74LS138和与非门实现此功能的逻辑电路。

2. 试用一片四位加法器将5421BCD 码转换为2421BCD 码。

请完成设计并画出接线图。

3. 试用一片3—8译码器74LS138及与非门实现如下逻辑函数。

AC BC AB C B A C B A C B A F F++=⊕⊕=),,(),,(21 4. 用一片双4选一数据选择器及与非门实现如下逻辑函数。

AC BC AB C B A C B A C B A F F ++=⊕⊕=),,(),,(215. 试用一片四位加法器及最少的门电路将8421BCD 码转换为2421BCD 码。

请完成设计并画出接线图6. 用一片3—8译码器74LS138及与非门实现如下逻辑函数。

+=⊕⊕=AB C B A C B A C B A F F ),,(),,(217. 某雷达站有3部雷达A 、B 、C ,其中A 和B 功率消耗相等,C 的功率是A 的2倍。

这些雷达由两台发电器X 和Y 供电,发电机X 的最大输出功率等于雷达A 的功率消耗,发电机Y 的最大输出功率是X 的3倍。

要求设计一个逻辑电路,能够根据各雷达的启动和关闭信号,以最节约电能的方式启、停发电机。

8. 设计“一位十进制数”的四舍五入电路(采用8421BCD 码)。

要求只设定一个输出,并画出用最少“与非门”实现的逻辑电路图。