07-锁相环时钟的抖动

时钟抖动的4大根本原因及3种查看途径

时钟抖动的4大根本原因及3种查看途径时钟接口阈值区间附近的抖动会破坏ADC的时序。

例如,抖动会导致ADC在错误的时间采样,造成对模拟输入的误采样,并且降低器件的信噪比(SNR)。

降低抖动有很多不同的方法,但是,在get降低抖动的方法前我们必须找到抖动的根本原因!时钟抖动,why?时钟抖动的根本原因就是时钟和ADC之间的电路噪声。

随机抖动由随机噪声引起,主要随机噪声源包括· 热噪声(约翰逊或奈奎斯特噪声),由载流子的布朗运动引起。

· 散粒噪声,与流经势垒的直流电流有关,该势垒不连续平滑,由载流子的单独流动引起的电流脉冲所造成。

· 闪烁噪声,出现在直流电流流动时。

该噪声由携带载流子的半导体中的陷阱引起,这些载流子在释放前通常会形成持续时间较短的直流电流。

· 爆裂噪声,也称爆米花噪声,由硅表面的污染或晶格错位造成,会随机采集或释放载流子。

查看时钟信号噪声,how?确定性抖动由干扰引起,会通过某些方式使阈值发生偏移,通常受器件本身特性限制。

查看时钟信号噪声通常有三种途径:时域、频域、相位域。

咳咳,敲黑板划重点,以上三种途径的具体方法如下↓↓↓时域图图1. 抖动的时域图时钟抖动是编码时钟的样本(不同周期)间的变化,包括外部和内部抖动。

抖动引起的满量程信噪比由以下公式得出举个栗子,频率为1 Ghz,抖动为100 FS均方根值时,信噪比为64 dB。

在时域中查看时,x轴方向的编码边沿变化会导致y轴误差,幅度取决于边沿的上升时间。

孔径抖动会在ADC输出产生误差,如图2所示。

抖动可能产生于内部的ADC、外部的采样时钟或接口电路。

图2. 孔径抖动和采样时钟抖动的影响图3显示抖动对信噪比的影响。

图中显示了5条线,分别代表不同的抖动值。

x轴是满量程模拟输入频率,y轴是由抖动引起的信噪比,有别于ADC总信噪比。

图3. 时钟抖动随模拟信号增大而提升信噪比由抖动引起的信噪比和有效位数(ENOB)的关系由以下公式定义:SNR = 6.02 N + 1.76 dB其中N =有效位数。

时钟生成电路中锁相环的作用

时钟生成电路中锁相环的作用锁相环(Phase-Locked Loop,简称PLL)是一种常用于时钟生成电路中的重要电路,它的作用是使输出时钟信号与输入参考信号保持相位一致。

在现代电子设备中,时钟信号的稳定性对于保证系统性能至关重要,而锁相环正是通过自身的反馈控制机制,实现了高精度和稳定的时钟生成。

锁相环的作用可以从多个方面来解释。

首先,锁相环可以将输入的不稳定时钟信号进行整形和稳定化处理,产生一个相位准确、频率稳定的输出时钟信号。

其原理是通过比较输入时钟信号和反馈信号的相位差,并根据相位差的大小来调整输出时钟信号的频率和相位,使其逐渐与输入参考信号保持一致。

因此,锁相环可以有效消除输入时钟信号的抖动和漂移,提供稳定可靠的时钟信号给后续的电路模块使用。

锁相环还可以实现时钟信号的倍频或分频功能。

通过调整锁相环中的除数和乘法器的参数,可以实现将输入时钟信号的频率放大或缩小到需要的范围。

这对于不同模块之间的时钟频率转换非常有用,可以提高系统的灵活性和兼容性。

锁相环还可以实现时钟信号的相位同步。

在一些需要多个时钟信号同步工作的系统中,锁相环可以将不同模块的时钟信号进行相位调整,使它们在某个特定的相位关系下工作。

这对于实现数据的准确采样和处理非常重要,可以避免因时钟相位不一致而引起的数据错误和时序问题。

除了以上的基本功能,锁相环在实际应用中还有许多衍生和扩展的功能。

例如,锁相环可以通过引入额外的相位调整电路,实现对输入信号相位的连续调节,从而达到相位延迟或相位提前的效果。

这在一些需要实时调整相位的应用中非常有用,如通信系统中的相位调制和解调。

锁相环还可以通过引入滤波器和自适应控制算法,提高系统对噪声和干扰的抑制能力,进一步提高时钟信号的稳定性和抗干扰能力。

这对于提高系统的抗干扰性和抗噪声性能非常重要,尤其是在高速通信和精密测量等领域。

锁相环在时钟生成电路中的作用是非常重要的。

它可以实现时钟信号的整形、稳定化和倍频分频,实现时钟信号的相位同步,并具备一定的相位调节和抗干扰能力。

pll计算抖动时频率范围

PLL(锁相环)在计算抖动时,需要考虑的频率范围通常包括以下几个主要部分:

1. 输入信号频率:这是PLL输入的信号频率,通常在数兆赫兹(MHz)或更高。

2. VCO(压控振荡器)频率范围:VCO是PLL的一个重要组成部分,其频率范围决定了PLL的输出频率范围。

通常,VCO 的频率范围可以达到数十兆赫兹至数百兆赫兹。

3. 分频器(Divider)设置:分频器用于将VCO的输出频率分频,以匹配输入信号频率。

分频器的设置会影响PLL的频率范围。

4. 抖动频率范围:抖动是由于PLL内部噪声和非理想特性导致的输出信号频率的微小变化。

抖动频率范围通常在数赫兹至数兆赫兹之间,取决于PLL的具体实现和应用。

总之,在计算PLL抖动时,需要考虑的频率范围包括输入信号频率、VCO频率范围、分频器设置和抖动频率范围。

这些因素共同决定了PLL在特定应用中的性能和稳定性。

正确理解锁相环Jitter

Application Report

ZHCA492 – JAN 2013

正确理解时钟器件的抖动性能

Steven Shi China Telecom Application Team

摘

要

在选择时钟器件时,抖动指标是最重要的关键参数之一。但不同的时钟器件,对抖动的描述不尽相同,如不带 锁相环的时钟驱动器有附加抖动指标要求,而带锁相环实现零延时的时钟驱动器则有周期抖动和周期间抖动指。同 时,不同厂家对相关时钟器件的抖动指标定义条件也不一样,如在时钟合成器条件下测试,还是在抖动滤除条件下 测试等。 为了正确理解时钟相关器件的抖动指标规格,同时选择抖动性能适合系统应用的时钟解决方案,本文详细介绍 了如何理解两种类型时钟驱动器的抖动参数,以及从锁相环输出噪声特性理解时钟器件作为合成器、抖动滤除功能 时的噪声特性。

2 时钟抖动和锁相环噪声模型

对时钟器件而言,抖动和锁相环是两个最基本的概念。

2.1 抖动

如图 1 所示,时钟抖动可分为三种抖动类型:时间间隔误差 TIE(Time Interval Error)、周期抖动 PJ (Period Jitter)和相邻周期间抖动 CCJ(Cycle to Cycle Jitter)。周期抖动是多个周期内对时钟周期的变化 进行统计与测量的结果,相邻周期间抖动是时钟相邻周期的周期差值进行统计与测量的结果,由于这两种 抖动是单个周期或相邻周期的偏差,表征的是短期抖动行为。时间间隔误差又称为相位抖动( Phase Jitter),是指信号在电平转换时,其边沿与理想时间位置的偏移量,通常表征的是长期抖动行为。

锁相环指标 -回复

锁相环指标-回复什么是锁相环指标?锁相环指标是指用来衡量锁相环(Phase-Locked Loop,PLL)性能的各种参数和指标。

PLL是一种电路系统,通过对输入信号的相位进行比较,并根据比较结果调整本身输出信号的相位,从而使输出信号保持与输入信号的相位同步。

在各种通信、控制和测量领域,PLL已经广泛应用。

而锁相环指标则是评估PLL工作性能和稳定度的重要依据。

有哪些常见的锁相环指标?实际上,锁相环的指标非常多,并且根据具体应用的不同可能略有差异。

下面列举几个常见的锁相环指标:1. 锁定时间(Lock time):指PLL从失锁状态转变为锁定状态所需要的时间。

锁定时间短是衡量PLL性能和适用性的重要指标之一。

2. 锁定范围(Lock range):指PLL在输入信号频率范围内能够保持稳定锁定的能力。

通常用频率范围或相位范围来表示。

3. 噪声性能(Noise performance):指PLL对输入信号中的噪声和扰动的抵抗能力。

好的锁相环应该能够在抑制噪声的同时保持输出信号的稳定性。

4. 抖动(Jitter):指信号在时间上的不稳定性,可以通过锁相环来降低抖动。

抖动越小,表明锁相环性能越好。

5. 相位噪声(Phase noise):指锁相环输出信号相位随时间的变化情况。

相位噪声小的锁相环输出信号更加稳定。

6. 频率稳定度(Frequency stability):指锁相环输出信号频率的变化程度。

频率稳定度好的锁相环输出信号与输入信号的频率差距很小。

以上仅为锁相环指标中的几个常见要素,根据不同应用的需求,可能还会有其他更具体的指标。

锁相环指标如何优化?优化锁相环指标是实际应用中非常重要的任务,因为合理的指标设计和优化可以提高PLL的性能,提高系统的可靠性和稳定性。

1. 设计合适的环路带宽:适当选择环路带宽可以平衡相位噪声和锁定时间的要求。

过高的带宽容易引入噪声,过低的带宽又会增加锁定时间。

2. 添加滤波器:通过添加滤波器来抑制输入信号中的噪声和频率扰动,从而提高锁相环的噪声性能和稳定性。

微电子电路中的时钟信号抖动分析与优化方法研究

微电子电路中的时钟信号抖动分析与优化方法研究引言:时钟信号在微电子电路中起着至关重要的作用,它是整个系统的节拍,负责同步各个模块的工作。

然而,由于各种因素的干扰,时钟信号会产生抖动,导致系统性能下降。

因此,对时钟信号的抖动进行分析和优化成为微电子电路设计中的重要课题。

一、时钟信号抖动的来源时钟信号抖动是指时钟信号的周期性变化,主要有以下几个来源:1. 环境干扰:温度变化、电磁辐射等环境因素会对时钟信号产生影响,导致抖动。

2. 电源噪声:电源的不稳定性会引起时钟信号的抖动。

3. 器件非线性:微电子器件的非线性特性会对时钟信号产生影响,引起抖动。

4. 时钟信号传输线路:传输线路的噪声、阻抗不匹配等因素也会导致时钟信号的抖动。

二、时钟信号抖动的影响时钟信号抖动对微电子电路的性能有着重要的影响,主要体现在以下几个方面:1. 时序错误:时钟信号抖动会导致时序错误,使得电路无法按照设计要求正常工作。

2. 时钟偏移:时钟信号抖动会引起时钟频率的偏移,导致电路的时钟周期不稳定。

3. 噪声干扰:时钟信号抖动会引入噪声,影响电路的信号完整性和稳定性。

4. 能耗增加:时钟信号抖动会导致电路频繁切换,增加功耗。

三、时钟信号抖动分析方法为了准确分析时钟信号的抖动情况,可以采用以下几种方法:1. 时钟抖动测量仪器:使用专门的时钟抖动测量仪器,通过测量时钟信号的抖动参数,如峰峰值、均方根值等,来评估抖动情况。

2. 时钟抖动仿真工具:利用电路仿真软件,对时钟信号进行仿真分析,得到时钟信号的波形和频谱,进而分析抖动情况。

3. 时钟抖动模型:建立时钟信号的抖动模型,通过数学方法进行分析,得到时钟信号的抖动特性。

四、时钟信号抖动优化方法为了降低时钟信号的抖动,可以采用以下几种优化方法:1. 电源和地线设计:合理设计电源和地线,减小电源噪声对时钟信号的影响。

2. 环境隔离:采用屏蔽罩、隔离层等措施,减少环境因素对时钟信号的干扰。

3. 时钟信号传输线路设计:采用匹配阻抗、减小传输线路长度等措施,降低传输线路对时钟信号的影响。

锁相环指标 -回复

锁相环指标-回复什么是锁相环指标?锁相环(PLL)是一种电子反馈系统,用于调节信号的频率和相位。

锁相环指标是用来描述锁相环性能的量化指标。

锁相环指标通常包括锁定时间、锁定范围、抖动、输入偏置等。

锁相环指标的详细解释如下:1. 锁定时间:锁相环的锁定时间是指从输入信号发生变化到锁相环稳定在新的输出状态所需要的时间。

锁定时间越短,锁相环的响应速度越快。

2. 锁定范围:锁相环的锁定范围是指锁相环能够跟踪的输入信号的频率范围。

锁定范围越广,锁相环适应不同频率的输入信号能力越强。

3. 抖动:锁相环的抖动是指输出信号在稳定锁定状态下的频率和相位误差。

抖动越小,锁相环的稳定性和精度越高。

4. 输入偏置:锁相环的输入偏置是指输入信号与锁相环内部参考信号之间的相位差。

输入偏置越小,锁相环的跟踪效果越好。

为何需要锁相环指标?锁相环指标对于电子系统设计和应用至关重要。

它们是评估锁相环性能和判断锁相环是否满足系统需求的依据。

锁相环指标的合理选择可以确保系统的稳定性、精度和实时性。

以移动通信系统为例,锁相环指标的好坏直接影响信号的传输、检测和处理。

在无线通信中,移动信号的频率、相位和稳定性要求非常高,锁相环用于调整持续变化的信号以保持稳定性。

如果锁相环指标不达标,信号将可能失真、丢失或传输不及时。

如何评估锁相环指标?评估锁相环指标需要进行一系列测试和分析。

常见的锁相环指标测试方法有以下几种:1. 测试锁定时间:在输入信号变化时,观察输出信号的响应时间。

多次测试并取平均值以获得可靠的结果。

2. 测试锁定范围:逐渐改变输入信号的频率,观察锁相环的跟踪能力和输出信号的稳定性。

一般使用频谱仪或示波器进行测试。

3. 测试抖动:使用高精度的频率计或相位计对输出信号进行测量,计算其频率和相位误差。

抖动可以通过信号处理和滤波来减小。

4. 测试输入偏置:输入一个稳定的参考信号和待测试信号,测量两者的相位差。

使用示波器或均衡器等仪器进行测量。

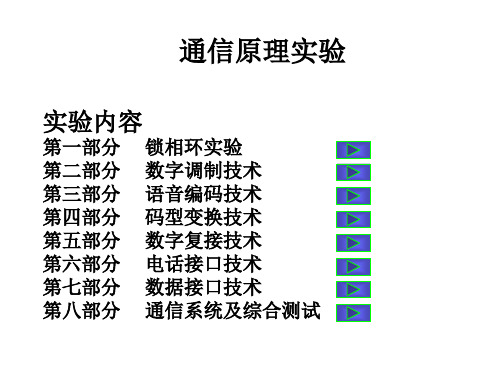

通信原理实验

VCO自由振荡频率测量

测量TPP04点的VCO输出振荡频率为549.4KHZ 到549.6KHZ

△f/ f0 ≈ 0.2/549.5=3.6 ×10-4

返回

锁定状态测量

不存在相差

存在一定的相差

返回

锁定频率测量和分频比计算

这一部分的具体点频率测量请学生自己完成, 并可将测得的各点频率与学生用书上的图2.1.1参考来 对比.

1. 将J007接地,把函数信号发生器方式设置为计数,

闸门时间放在100ms或1s,测量TPP04点的VCO输出振荡频

率f0 .记录闸门每次闪动的频率读数(其读数不太稳定). 2. 求VCO在频率512KHZ时的短期频率稳定度△f/ f0 .

返回

锁定状态测量

实验步骤:

1. 用函数信号发生器从测试信号输入端口 J007 送入 一个256 KHz的TTL方波信号。测量TPP03、TPP05 的相位关系。环路锁定该两信号将不存在相差。 2.将KP01设置在1_2位置,重复上述测量步骤。

返回

VCO压控灵敏度测量

根据测量可得出V1=0.56v,V2=0.08v. 则压控灵敏度=40KHZ/(0.56-0.08) =83.33KHZ/V

返回

实验二 数字锁相环模块

实验目的

1.了解数字锁相环的基本 概念

实验内容

1.数字锁相环锁定状态测量

2.熟悉数字锁相环与模拟 锁相环的指标

3.掌握全数字锁相环的设 计

2.数字锁相环的相位抖动特性 测量 3.数字锁相环锁定频率测量和 分频比计算

4.数字锁相环锁定过程观测

5.数字锁相环同步带测量 6.数字锁相环捕捉带测量

返回

7.调整信号脉冲观测

数字锁相环锁定状态测量

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

锁相环时钟的抖动2008年11月22日

什么是抖动?如下图所示,抖动是信号和此刻信号理想位置相比短时间的变化。

这种输出信号从理想位置的偏离会给数据传输质量带来负面影响。

在很多情况下,其他的信号偏离,如信号偏差(signal skew),噪声耦合一起组合起来称作抖动。

偏离(用±ps来表示)可能发生在信号的上升沿或者下降沿。

时钟信号可能会由不同的源导致或者耦合而来,并且在不同频率也不一样。

抖动过大会不正确的传输数据流,增加通讯信号的误码率(BER)。

抖动会导致超过时序裕量,让电路不能正确工作。

为了确保系统的可靠性,精确测量抖动很有必要。

1. 抖动源

通常的抖动源包括:

锁相环的内部电路

晶振的随机热噪声

其他振荡器

晶振振荡的随机机械噪声

信号传输器

走线和电缆

接口

接收器

除了这些源,端接依赖,串扰,反射,趋肤效应,电源塌陷,地弹和临近设备的电磁串扰也会增加抖动量。

如果存在临近的同步同相,反射和串扰都会被放大。

除了电源和地导致的噪声,电路阻抗的变化是数据通讯电路中大部分抖动的来源。

2. 抖动的组成

抖动的2个主要组成部分是随机抖动(random jitter)和确定性抖动(deterministic jitter)

1) 随机抖动

随机抖动是由于电路内部内在的噪声造成的,典型的是呈现出高斯分布。

随机抖动(RJ)是由于随机源,如衬底和电源。

电源噪声影响信号的上升速率在切换点产生时序问题。

随机抖动是平方的和,呈现钟形曲线。

由于随机噪声没有边界,所以它的特性通过标准偏差来表示

2) 确定性抖动

确定性抖动依赖于数据样式(data pattern),来源于独立的源。

源通常和设备传输介质有关,但是也有可能由电源噪声,串扰和信号调制有关。

确定性抖动时线性的相加,它通常有特别的源。

确定性抖动没有按高斯随机分布,并且幅度有边界。

确定性抖动(DJ)的特性通过它的边界,峰峰值来表示。

3. 抖动的种类

抖动的种类有很多。

周期性抖动,周期间抖动,半周期间抖动将在下文具体描述。

1) 周期性抖动

周期性抖动是时钟输出转变时期(典型的是上升沿)和理想位置相比的变化。

周期性抖动用时间或者频率测量和表达。

周期性抖动测量用来计算系统中的时间裕量,如tSU和tCO。

2) 周期间抖动

周期间抖动是从一个时钟周期到下一个时钟周期之间的差别。

周期间抖动很难测量,通常要用时间间隔分析器。

如下图所示,J1和J2是测量的抖动值。

在多次测量中的最大值称作最大的周期间抖动。

3) 半周期间抖动

半周期抖动是测量是在一个周期到下半个周期时钟转变过程和理想位置对比的最大的改变。

图3所示为半周期间抖动。

4. 抖动的指标

锁相环的特性测量需要一些参数。

通常有3个指标来表示锁相环的特性,抖动生产,抖动容限,抖动传输。

1) 抖动生产

抖动生产是测量锁相环内在的抖动,在锁相环的输出测量。

抖动生产是通过一个没有抖动的信号作为参考,来测量输出的抖动。

抖动生产通常为周期抖动的峰值。

2) 抖动容限

抖动容限是测量在相对于基准频率情况下加入抖动情况下锁相环能正确运行的能力(例如,在不同频率的不同程度的抖动的情况下是否能保持锁定)。

抖动容限通常为输入抖动的掩码。

3) 抖动传输

抖动传输和抖动衰减基于输入不同的抖动时,输出的不同程度的抖动。

输入不同幅度和频率的抖动,输出用不同设置的带宽来测量。

因为内在抖动始终存在,低频抖动会比高频抖动的衰减低。

抖动传输典型为一个带宽图表。