时钟抖动分析

时钟抖动的4大根本原因及3种查看途径

时钟抖动的4大根本原因及3种查看途径时钟接口阈值区间附近的抖动会破坏ADC的时序。

例如,抖动会导致ADC在错误的时间采样,造成对模拟输入的误采样,并且降低器件的信噪比(SNR)。

降低抖动有很多不同的方法,但是,在get降低抖动的方法前我们必须找到抖动的根本原因!时钟抖动,why?时钟抖动的根本原因就是时钟和ADC之间的电路噪声。

随机抖动由随机噪声引起,主要随机噪声源包括· 热噪声(约翰逊或奈奎斯特噪声),由载流子的布朗运动引起。

· 散粒噪声,与流经势垒的直流电流有关,该势垒不连续平滑,由载流子的单独流动引起的电流脉冲所造成。

· 闪烁噪声,出现在直流电流流动时。

该噪声由携带载流子的半导体中的陷阱引起,这些载流子在释放前通常会形成持续时间较短的直流电流。

· 爆裂噪声,也称爆米花噪声,由硅表面的污染或晶格错位造成,会随机采集或释放载流子。

查看时钟信号噪声,how?确定性抖动由干扰引起,会通过某些方式使阈值发生偏移,通常受器件本身特性限制。

查看时钟信号噪声通常有三种途径:时域、频域、相位域。

咳咳,敲黑板划重点,以上三种途径的具体方法如下↓↓↓时域图图1. 抖动的时域图时钟抖动是编码时钟的样本(不同周期)间的变化,包括外部和内部抖动。

抖动引起的满量程信噪比由以下公式得出举个栗子,频率为1 Ghz,抖动为100 FS均方根值时,信噪比为64 dB。

在时域中查看时,x轴方向的编码边沿变化会导致y轴误差,幅度取决于边沿的上升时间。

孔径抖动会在ADC输出产生误差,如图2所示。

抖动可能产生于内部的ADC、外部的采样时钟或接口电路。

图2. 孔径抖动和采样时钟抖动的影响图3显示抖动对信噪比的影响。

图中显示了5条线,分别代表不同的抖动值。

x轴是满量程模拟输入频率,y轴是由抖动引起的信噪比,有别于ADC总信噪比。

图3. 时钟抖动随模拟信号增大而提升信噪比由抖动引起的信噪比和有效位数(ENOB)的关系由以下公式定义:SNR = 6.02 N + 1.76 dB其中N =有效位数。

数字系统时钟抖动

数字系统时钟抖动数字系统时钟抖动是指当数字系统的时钟信号存在不稳定性或噪声时,导致时钟信号产生微小的偏移或抖动现象。

时钟信号在数字系统中起着至关重要的作用,它用于同步各个模块的操作,确保数据的准确传输和处理。

然而,时钟抖动会对系统的性能和可靠性产生负面影响。

本文将探讨数字系统时钟抖动的原因、后果以及应对措施。

一、时钟抖动的原因1. 元器件误差:元器件的制造和使用过程中会存在一定的误差,例如晶体振荡器的频率精度、时钟发生器的稳定性等。

这些误差在时钟信号传输过程中会放大,导致时钟抖动。

2. 环境干扰:数字系统所处的环境中存在各种干扰源,如电磁波干扰、温度变化、电源波动等。

这些干扰会对时钟信号的传输和接收产生影响,进而引起时钟抖动。

3. 信号串扰:在复杂的数字系统中,各个信号线之间会存在串扰现象,即一个信号线上的电磁场对其他信号线产生影响。

当时钟信号受到其他信号线的串扰时,也会导致时钟抖动。

二、时钟抖动的后果1. 时序错误:时钟抖动可能导致时钟信号的上升沿或下降沿不准确,进而造成时序错误。

这会导致数据传输出错、计时错误等问题,严重时可能导致整个系统的崩溃。

2. 数据稳定性下降:时钟抖动会导致数据的采样和恢复不准确,使得数据的稳定性下降。

在高速数据传输中,时钟抖动可能导致数据丢失或数据错误,影响系统的可靠性和性能。

3. 时钟频率偏移:时钟抖动可能导致时钟信号的频率产生微小的偏移,进而影响系统的时钟同步和数据处理速度。

这会给系统的运行带来一定的难度和不确定性。

三、应对时钟抖动的措施1. 选择高质量的元器件:在设计和选择数字系统的元器件时,应注重其频率精度、稳定性和抗干扰能力。

采用高质量的晶体振荡器、时钟发生器等元器件,能够减小时钟抖动的概率。

2. 优化时钟布线:合理设计时钟信号的布线路径,避免与其他信号线的干扰。

尽可能使用短而直接的时钟线路,减少串扰的可能性。

3. 电磁屏蔽和滤波:对数字系统中的时钟信号进行电磁屏蔽和滤波处理,减少来自外界的干扰。

抖动测量与分析

抖动的测量与分析一、时钟抖动时钟是广泛用于计算机、通讯、消费电子产品的元器件,包括晶体振荡器和锁相环,主要用于系统收发数据的同步和锁存。

如果时钟信号到达接收端时抖动较大,可能出现:并行总线中数据信号的建立和保持时间余量不够、串行信号接收端误码率高、系统不稳定等现象,因此时钟抖动的测量与分析非常重要。

1、时钟抖动的分类时钟抖动通常分为时间间隔误差(Time Interval Error,简称TIE),周期抖动(Period Jitter)和相邻周期抖动(cycle to cycle jitter)三种抖动。

TIE又称为phase jitter,是信号在电平转换时,其边沿与理想时间位置的偏移量。

理想时间位置可以从待测试时钟中恢复,或来自于其他参考时钟。

Period Jitter是多个周期内对时钟周期的变化进行统计与测量的结果。

Cycle to cycle jitter是时钟相邻周期的周期差值进行统计与测量的结果。

2、时钟抖动的测量对于每一种时钟抖动进行统计和测量,可以得到其抖动的峰峰值和RMS值(有效值),峰峰值是所有样本中的抖动的最大值减去最小值,而RMS值是所有样本统计后的标准偏差。

3种时钟抖动可以调用示波器的抖动包中的TIE、Period和Cycle to cycle函数进行测试。

3、时钟抖动的应用范围在三种时钟抖动中,在不同的应用范围需要重点测量与分析某类时钟抖动。

TIE抖动是最常用的抖动指标,在很多芯片的数据手册上通常都规定了时钟TIE抖动的要求。

对于串行收发器的参考时钟,通常测量其TIE抖动。

在并行总线系统中,通常重点关注Period Jitter和Cycle to cycle jitter。

4、时钟抖动的分析在时钟抖动测量时,可以在三个域分析抖动,即在时域分析抖动追踪(jitter track/trend)、在频域观察抖动的频谱、在统计域分析抖动的直方图。

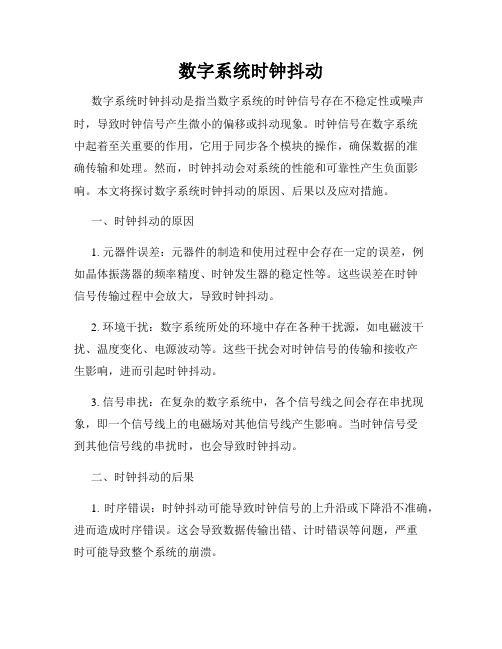

二、串行数据抖动1、数据抖动的分类和来源业界通常把串行数据的抖动分解为:在力科SDA系列示波器中使用了‘normalized Q-scale method’(简称NQ-Scale方法)来求解Tj。

时间抖动(jitter)的概念及其分析方法

时间抖动(jitter)的概念及其分析方法随着通信系统中的时钟速率迈入GH z级,抖动这个在模拟设计中十分关键的因素,也开始在数字设计领域中日益得到人们的重视。

在高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。

不仅如此,它还会导致通信链路的误码率增大,甚至限制A/D转换器的动态范围。

有资料表明在3GH z以上的系统中,时间抖动(jitter)会导致码间干扰(ISI),造成传输误码率上升。

在此趋势下,高速数字设备的设计师们也开始更多地关注时序因素。

本文向数字设计师们介绍了抖动的基本概念,分析了它对系统性能的影响,并给出了能够将相位抖动降至最低的常用电路技术。

本文介绍了时间抖动(jitter)的概念及其分析方法。

在数字通信系统,特别是同步系统中,随着系统时钟频率的不断提高,时间抖动成为影响通信质量的关键因素。

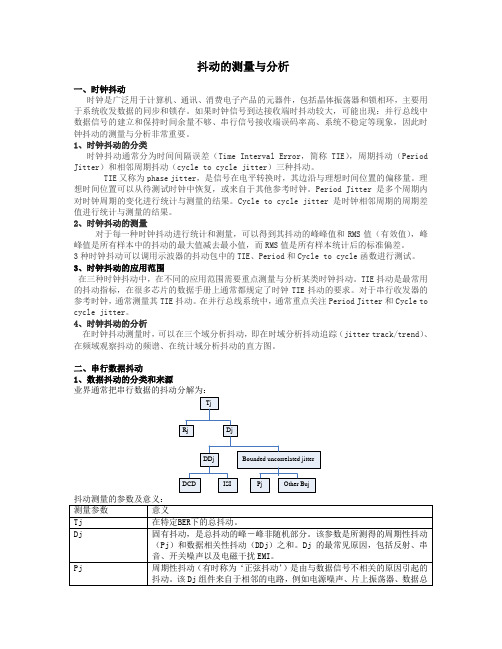

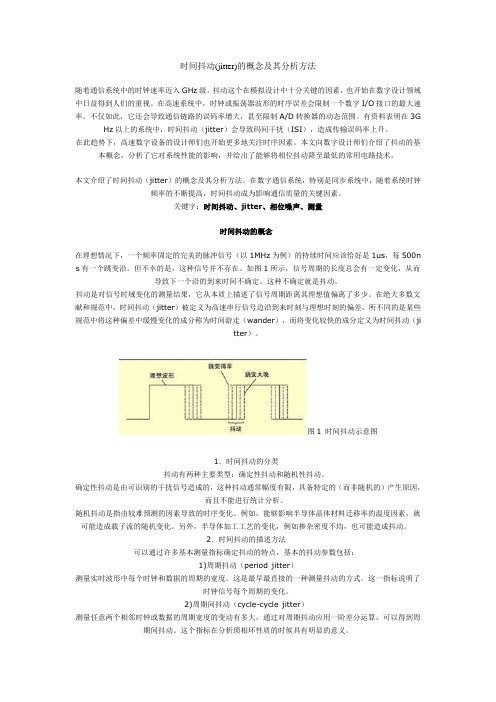

关键字:时间抖动、jitter、相位噪声、测量时间抖动的概念在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500ns 有一个跳变沿。

但不幸的是,这种信号并不存在。

如图1所示,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。

这种不确定就是抖动。

抖动是对信号时域变化的测量结果,它从本质上描述了信号周期距离其理想值偏离了多少。

在绝大多数文献和规范中,时间抖动(jitter)被定义为高速串行信号边沿到来时刻与理想时刻的偏差,所不同的是某些规范中将这种偏差中缓慢变化的成分称为时间游走(wander),而将变化较快的成分定义为时间抖动(jitter)。

图1 时间抖动示意图1.时间抖动的分类抖动有两种主要类型:确定性抖动和随机性抖动。

时间抖动(jitter)的概念及其分析方法

时间抖动(jitter)的概念及其分析方法随着通信系统中的时钟速率迈入GHz级,抖动这个在模拟设计中十分关键的因素,也开始在数字设计领域中日益得到人们的重视。

在高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。

不仅如此,它还会导致通信链路的误码率增大,甚至限制A/D转换器的动态范围。

有资料表明在3G Hz以上的系统中,时间抖动(jitter)会导致码间干扰(ISI),造成传输误码率上升。

在此趋势下,高速数字设备的设计师们也开始更多地关注时序因素。

本文向数字设计师们介绍了抖动的基本概念,分析了它对系统性能的影响,并给出了能够将相位抖动降至最低的常用电路技术。

本文介绍了时间抖动(jitter)的概念及其分析方法。

在数字通信系统,特别是同步系统中,随着系统时钟频率的不断提高,时间抖动成为影响通信质量的关键因素。

关键字:时间抖动、jitter、相位噪声、测量时间抖动的概念在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500n s有一个跳变沿。

但不幸的是,这种信号并不存在。

如图1所示,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。

这种不确定就是抖动。

抖动是对信号时域变化的测量结果,它从本质上描述了信号周期距离其理想值偏离了多少。

在绝大多数文献和规范中,时间抖动(jitter)被定义为高速串行信号边沿到来时刻与理想时刻的偏差,所不同的是某些规范中将这种偏差中缓慢变化的成分称为时间游走(wander),而将变化较快的成分定义为时间抖动(jitter)。

图1 时间抖动示意图1.时间抖动的分类抖动有两种主要类型:确定性抖动和随机性抖动。

确定性抖动是由可识别的干扰信号造成的,这种抖动通常幅度有限,具备特定的(而非随机的)产生原因,而且不能进行统计分析。

随机抖动是指由较难预测的因素导致的时序变化。

例如,能够影响半导体晶体材料迁移率的温度因素,就可能造成载子流的随机变化。

微电子电路中的时钟信号抖动分析与优化方法研究

微电子电路中的时钟信号抖动分析与优化方法研究引言:时钟信号在微电子电路中起着至关重要的作用,它是整个系统的节拍,负责同步各个模块的工作。

然而,由于各种因素的干扰,时钟信号会产生抖动,导致系统性能下降。

因此,对时钟信号的抖动进行分析和优化成为微电子电路设计中的重要课题。

一、时钟信号抖动的来源时钟信号抖动是指时钟信号的周期性变化,主要有以下几个来源:1. 环境干扰:温度变化、电磁辐射等环境因素会对时钟信号产生影响,导致抖动。

2. 电源噪声:电源的不稳定性会引起时钟信号的抖动。

3. 器件非线性:微电子器件的非线性特性会对时钟信号产生影响,引起抖动。

4. 时钟信号传输线路:传输线路的噪声、阻抗不匹配等因素也会导致时钟信号的抖动。

二、时钟信号抖动的影响时钟信号抖动对微电子电路的性能有着重要的影响,主要体现在以下几个方面:1. 时序错误:时钟信号抖动会导致时序错误,使得电路无法按照设计要求正常工作。

2. 时钟偏移:时钟信号抖动会引起时钟频率的偏移,导致电路的时钟周期不稳定。

3. 噪声干扰:时钟信号抖动会引入噪声,影响电路的信号完整性和稳定性。

4. 能耗增加:时钟信号抖动会导致电路频繁切换,增加功耗。

三、时钟信号抖动分析方法为了准确分析时钟信号的抖动情况,可以采用以下几种方法:1. 时钟抖动测量仪器:使用专门的时钟抖动测量仪器,通过测量时钟信号的抖动参数,如峰峰值、均方根值等,来评估抖动情况。

2. 时钟抖动仿真工具:利用电路仿真软件,对时钟信号进行仿真分析,得到时钟信号的波形和频谱,进而分析抖动情况。

3. 时钟抖动模型:建立时钟信号的抖动模型,通过数学方法进行分析,得到时钟信号的抖动特性。

四、时钟信号抖动优化方法为了降低时钟信号的抖动,可以采用以下几种优化方法:1. 电源和地线设计:合理设计电源和地线,减小电源噪声对时钟信号的影响。

2. 环境隔离:采用屏蔽罩、隔离层等措施,减少环境因素对时钟信号的干扰。

3. 时钟信号传输线路设计:采用匹配阻抗、减小传输线路长度等措施,降低传输线路对时钟信号的影响。

规范-时钟抖动的分析与测量(试行)_Rev 1.0

时钟抖动的分析与测量编制:审核:批准:文件维护日志目录第一章抖动的分析 (4)1.1抖动的定义 (4)1.2抖动的分类,峰峰值与有效值 (4)1.3时钟抖动的分解 (7)第二章抖动的测量 (8)2.1用TDSJIT3测量抖动 (9)2.1.1 Wizard向导测试 (9)测试步骤: (9)2.1.2 TDSJIT3手动测抖动 (12)测试步骤: (12)2.2用DPOJET测量抖动 (17)2.2.1 One Touch 向导测试 (17)测试步骤: (18)2.2.2 手动测试 (19)测试步骤: (19)第三章参考 (22)前言文章结构:第一章抖动的分析第二章抖动的测量第一章抖动的分析1.1抖动的定义一个信号在跳变时相对其理想时间位置的偏移量1.2抖动的分类,峰峰值与有效值抖动通常分为三类:●时钟抖动:period jitter,cycle-cycle jitter,N-cycle jitter,long-term jitter等●并行总线中数据与时钟相关的抖动:setup-hold time jitter等●高速串行数据的抖动测试:TIE(time interval error)等抖动定义分析对比及示例:TIE :又称为phase jitter,是信号在电平转换时,其边沿与理想时间位置的偏移量。

理想时间位置可以从待测试时钟中恢复,或来自于其他参考时钟。

如图 2 所示TIE抖动的示意图:I1、I2、I3、In-1、In 是时钟第一个到第n 个上升沿与理想时间位置的偏差,将I1、I2 到In 进行数理统计,在所有样本的找出最大值和最小值,两者相减可以得到TIE 抖动的峰峰值,即:假设N为测量的样本总数,抖动的平均值可表示为:抖动的有效值(即RMS 值)为所有样本的1 个Sigma 值,即:PJ:周期抖动(Period Jitter)是多个周期内对时钟周期的变化进行统计与测量的结果,主要用于时钟等固定周期的信号。

时钟抖动测试方法

时钟抖动测试方法

时钟抖动测试是一种用于测试时钟稳定性的方法。

时钟抖动是指时钟

信号在短时间内发生的微小波动,这种波动可能会导致系统出现错误。

因此,时钟抖动测试对于保证系统的稳定性和可靠性非常重要。

时钟抖动测试的方法有很多种,下面介绍一种常用的方法:

1. 准备测试设备:需要一台高精度的频率计和一台信号发生器。

2. 设置信号发生器:将信号发生器的频率设置为需要测试的时钟频率,并将输出信号连接到频率计上。

3. 测量时钟频率:使用频率计测量时钟的频率,并记录下来。

4. 生成测试信号:使用信号发生器生成一个频率为1Hz的正弦波信号,并将其连接到示波器上。

5. 观察示波器波形:在示波器上观察正弦波信号的波形,如果波形出

现了明显的抖动,则说明时钟存在抖动问题。

6. 分析测试结果:根据示波器上观察到的波形,可以分析出时钟的抖

动情况。

如果抖动很小,则说明时钟稳定性较好;如果抖动较大,则需要进一步调整时钟频率或者更换时钟源。

需要注意的是,时钟抖动测试需要在实验室等稳定的环境下进行,避免外界干扰对测试结果的影响。

此外,测试时钟的频率应该尽量接近实际使用时钟的频率,以保证测试结果的准确性。

总之,时钟抖动测试是一项非常重要的测试工作,可以帮助我们保证系统的稳定性和可靠性。

通过上述方法进行测试,可以有效地检测时钟抖动问题,并及时采取措施进行调整,从而提高系统的性能和可靠性。

时钟的抖动测量与分析

时钟的抖动测量与分析和分解时钟的抖动可以分为随机抖动(Random Jitter,简称Rj)和固有抖动(Deterministic jitter),随机抖动的来源为热噪声、Shot Noise 和FlickNoise,与电子器件和半导体器件的电子和空穴特性有关,比如ECL 工艺的PLL 比TTL 和CMOS 工艺的PLL 有更小的随机抖动;固定抖动的来源为:开关电源噪声、串扰、电磁干扰等等,与电路的设计有关,可以通过优化设计来改善,比如选择合适的电源滤波方案、合理的PCB 布局和布线。

和串行数据的抖动分解很相似,时钟的抖动可以分为Dj 和Rj。

但不同的是,时钟的固有抖动中通常只有周期性抖动(Pj),不包括码间干扰(ISI)。

当时钟的上下边沿都用来锁存数据时占空比时钟(DCD)计入固有抖动,否则不算固有抖动。

时钟抖动测量方法在上个世纪90 年代,抖动的测量方法非常简单,示波器触发到时钟的一个上升沿,使用余辉模式,测量下一个上升沿余辉在判定电平上(通常为幅度的50%)的水平宽度。

测量水平宽度有两种方法。

第一种使用游标测量波形边沿余辉的宽度,如下图4 所示。

由于像素偏差或屏幕分辨率(量化误差) 会降低精度,而且引入了触发抖动,所以这种方法误差较大。

第二种使用直方图,对边沿余辉的水平方向进行直方图统计,如下图5 所示。

测量直方图的最左边到最右边的间距即为抖动的峰峰值(168 皮秒)。

这种方法的缺点是:引入了示波器的触发抖动;一次只测量一个周期,测试效率低,某些出现频率低的抖动在短时间内不能测量到。

随着测试仪器技术的发展与进步,目前,示波器的抖动分析软件不再是测量一两个周期波形后分析抖动,而是一次测量多个连续比特位,计算与统计所有比特位的抖动,测量的数据量非常大、效率非常高。

如下图6 所示为某50MHz时钟的Period 抖动测试,示波器的抖动测试软件可以一次测量所有周期的周期值,计算出抖动的峰峰值与有效值。

时钟抖动定义与测量方法

时钟抖动定义与测量方法引言以5G无线技术、电动汽车和先进移动设备为代表的应用大趋势正影响着全球社会,并将重塑未来的各个产业。

这些大趋势为电子产品,尤其是传感器和MEMS,提供了巨大的商机。

SiTime作为MEMS时钟解决方案的领先供应商,已经出货超过20亿颗MEMS时钟器件,拥有超过90%的MEMS时钟器件市场份额.。

SiTime的使命是为5G通讯、移动物联网、汽车和工业市场的客户解决最具挑战的时钟问题。

1、抖动的定义今天我们就来聊聊时钟抖动的定义与测量方法抖动是时钟信号边沿事件的时间点集合相对于其理想值的离散时序变量。

时钟信号中的抖动通常是由系统中的噪声或其他干扰导致的。

具体因素包括热噪声、电源变化、负载条件、器件噪声以及相邻电路耦合的干扰等。

2、抖动类型时钟信号抖动定义有多种主要如下:周期抖动(Period Jitter)相邻周期抖动(Cycle to Cycle Period Jitter)长期抖动 (Long Term Jitter)相位抖动 (Phase Jitter)时间间隔误差 (Time Interval Error or TIE)2.1 周期抖动周期抖动是时钟信号的周期时间相对于一定数量、随机选定的理想时钟信号周期的偏差。

如果我们能对一定数量的时钟周期进行测量,就可以计算出这一段时间测量窗口内的平均时钟周期以及其标准偏差与峰峰值。

我们通常将标准偏差和峰峰值分别称作RMS 值和Pk-Pk 周期抖动。

许多已发表的文献中往往将周期抖动定义为测得的时钟周期与理想周期之间的差异,但在实际应用中,想要量化理想周期往往有困难。

如果用示波器观察设定频率为 100 MHz 的振荡器的输出,测得的平均周期可能是9.998 ns,而非理想周期的10 ns。

因此,在实际测量中可将测量时间窗口内的平均周期视为理想周期。

2.1.1 周期抖动应用周期抖动在数字系统中的时序冗余度计算方面非常实用。

例如,在一个基于微处理器的系统中,处理器在时钟上升之前需要 1 ns的数据建立时间。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

A = 10 log10(A1 + A2 + A3 + A4) RMS PHASE JITTER (radians) ≈ PHASE NOISE (dBc/Hz) A/10 2• 10 A/10 2•10 2 π fC

RMS JITTER (seconds) fC = CLOCK FREQUENCY

A/10 2•10

The World Leader in High-Performance Signal Processing Solutions

Performance Clocks: Demystifying Jitter

Low Jitter Clocks – a Review

The first ADI Web Seminar on Low Jitter Clocks was titled:

Time Jitter on clock results in higher Bit Error Rate (BER), poor call quality Spurious signals on clock result in Adjacent Channel Interference (ACI), dropped calls Signal Path Clock

For an oscillator

Fundamental power decreases As phase noise increases

fc

17

f

foffset

Calculating Time Jitter from Phase Noise

A= AREA = INTEGRATED PHASE NOISE POWER (dBc)

Random Time Jitter is characterized by a statistical distribution. Usually the distribution is assumed to be Gaussian (Normal).

distribution of many error samples

Time Jitter on clock degrades ability to make accurate measurements Time Jitter on clock degrades image in medical equipment

Wireless Infrastructure Radios

200 MHz

INTEGRATE OVER BW OF INTEREST –155 dBc

A

10k

100k

1M

10M

100M

1G

foffset

FREQUENCY OFFSET (Hz) = –155 + 83 = –72 dBc = 355 • 10–6 radians = 565 fs

A = –155 + 10 log10 2⋅ 108 – 0.01⋅ 106 RMS PHASE JITTER (radians) ≈ RMS JITTER (seconds) =

dV

error voltage

encode dt

13

“Low Jitter” refers to Jitter < 1 picosecond RMS

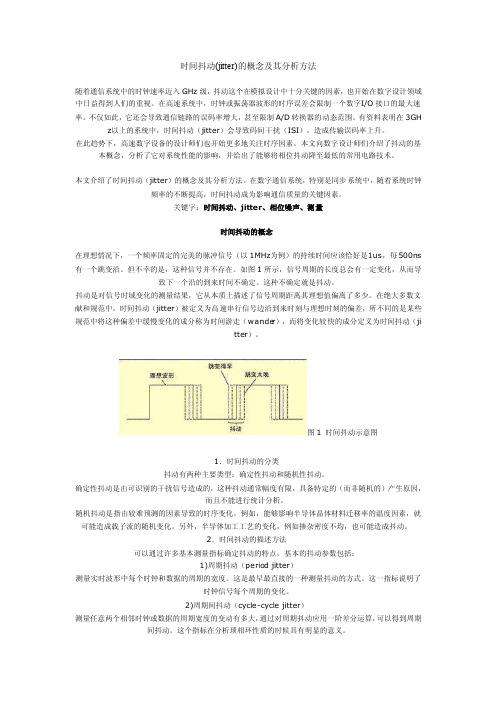

130 120 110 100 SNR in dB 90 80 70 60 50 40 30 1 10 100 1000 ADC Analog Input Frequency in MHz

10

Peak-to-Peak: A statistical reminder

mean

1σ 1σ 6σ

6.18σ bounds 99.9% of measurements

11

What effect does Time Jitter have on Data Converters?

FA

Digital Input

DAC

Analog Output (after LPF)

FA

FC

Sampling Clock

SNR

ADC

Analog Input

Digital Output SNR

For data converter applications, the answer is directly related to analog frequency FA. The actual clock rate FC is not as important!

actual edges occur at different times than expected

ideal signal

actual signal

7

edges should be here if occuring evenly in time

Time Jitter is Statistical

15

Phase Noise Power Spectrum of an Oscillator

Close-in Phase Noise

dBc/Hz

1 Hz BW

Broad-Band Phase Noise

fc

16

foffset

f

Phase Noise Power Spectrum of an Oscillator

14

16 bits 14 bits 12 bits 10 bits

FA 70-300MHz, SNR 60-80dB

Learning to speak a new language…

There is another phenomenon that many engineers are perhaps more familiar with than Time Jitter. Phase Noise Phase Noise is the Frequency Domain effect of Time Jitter. Time Jitter is the Time Domain effect of Phase Noise.

2 Outputs PLL Core DDS/DAC 48 LFCSP

/clocks

3

Low Time Jitter (Low Phase Noise) Clocks are Critical to Signal Processing Applications

Instrumentation

12

FC

ter and SNR

Clock jitter is the sample to sample variation in the encode clock Fullscale SNR (signal to noise ratio) is jitter limited by:

Broadband Infrastructure

Phase Noise on clocks result in data errors, lower throughput

4

AD9510 Clock Distribution IC

ADC

AD9510 provides clocks with sub-picosecond jitter to critical signal path components.

ideal signal

actual signal

edges should be here, but usually aren’t

8

RMS Jitter 1σ (one sigma – a standard deviation) is the same as the RMS

value for a Gaussian (or Normal) distribution

2

ADI’s Low Jitter / Low Phase Noise Clock Products

Clock Distribution

Clock Generation

8 Outputs PLL Core 64 LFCSP

5 Outputs PLL Core 48 LFCSP

5 Outputs 2 Inputs 48 LFCSP

≈

A1

INTEGRATE OVER BW OF INTEREST

A2 A3 A4

10k

100k

1M

10M

100M

1G

foffset

18

FREQUENCY OFFSET (Hz)

Calculating Time Jitter from Broadband Phase Noise

PHASE NOISE (dBc/Hz) fc = 100 MHz CLOCK FREQUENCY

Clock to A-D Converters

ADC ADC ADC

Reference Clock

AD9510 Clock Distribution IC

Clock to Digital Chips

DDC or ASIC DUC or FPGA DAC

ADC, Analog-to-Digital Converters DAC, Digital-to-Analog Converters DDC, Digital Down Converters DUC, Digital Up Converters

Using Low Jitter Clocks to Enhance Converter Performance

(available at /onlineseminars) That seminar introduced the ADI low jitter clock family of ICs. The uses and advantages of these clock chips were presented. These clock chips address application spaces which require better than (less than)1ps of time jitter.