时钟的稳定性和抖动(2)

数字系统时钟抖动

数字系统时钟抖动数字系统时钟抖动是指当数字系统的时钟信号存在不稳定性或噪声时,导致时钟信号产生微小的偏移或抖动现象。

时钟信号在数字系统中起着至关重要的作用,它用于同步各个模块的操作,确保数据的准确传输和处理。

然而,时钟抖动会对系统的性能和可靠性产生负面影响。

本文将探讨数字系统时钟抖动的原因、后果以及应对措施。

一、时钟抖动的原因1. 元器件误差:元器件的制造和使用过程中会存在一定的误差,例如晶体振荡器的频率精度、时钟发生器的稳定性等。

这些误差在时钟信号传输过程中会放大,导致时钟抖动。

2. 环境干扰:数字系统所处的环境中存在各种干扰源,如电磁波干扰、温度变化、电源波动等。

这些干扰会对时钟信号的传输和接收产生影响,进而引起时钟抖动。

3. 信号串扰:在复杂的数字系统中,各个信号线之间会存在串扰现象,即一个信号线上的电磁场对其他信号线产生影响。

当时钟信号受到其他信号线的串扰时,也会导致时钟抖动。

二、时钟抖动的后果1. 时序错误:时钟抖动可能导致时钟信号的上升沿或下降沿不准确,进而造成时序错误。

这会导致数据传输出错、计时错误等问题,严重时可能导致整个系统的崩溃。

2. 数据稳定性下降:时钟抖动会导致数据的采样和恢复不准确,使得数据的稳定性下降。

在高速数据传输中,时钟抖动可能导致数据丢失或数据错误,影响系统的可靠性和性能。

3. 时钟频率偏移:时钟抖动可能导致时钟信号的频率产生微小的偏移,进而影响系统的时钟同步和数据处理速度。

这会给系统的运行带来一定的难度和不确定性。

三、应对时钟抖动的措施1. 选择高质量的元器件:在设计和选择数字系统的元器件时,应注重其频率精度、稳定性和抗干扰能力。

采用高质量的晶体振荡器、时钟发生器等元器件,能够减小时钟抖动的概率。

2. 优化时钟布线:合理设计时钟信号的布线路径,避免与其他信号线的干扰。

尽可能使用短而直接的时钟线路,减少串扰的可能性。

3. 电磁屏蔽和滤波:对数字系统中的时钟信号进行电磁屏蔽和滤波处理,减少来自外界的干扰。

07-锁相环时钟的抖动

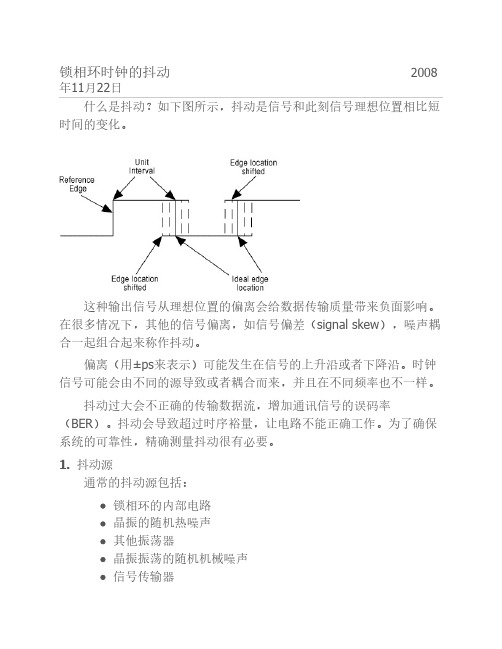

锁相环时钟的抖动2008年11月22日什么是抖动?如下图所示,抖动是信号和此刻信号理想位置相比短时间的变化。

这种输出信号从理想位置的偏离会给数据传输质量带来负面影响。

在很多情况下,其他的信号偏离,如信号偏差(signal skew),噪声耦合一起组合起来称作抖动。

偏离(用±ps来表示)可能发生在信号的上升沿或者下降沿。

时钟信号可能会由不同的源导致或者耦合而来,并且在不同频率也不一样。

抖动过大会不正确的传输数据流,增加通讯信号的误码率(BER)。

抖动会导致超过时序裕量,让电路不能正确工作。

为了确保系统的可靠性,精确测量抖动很有必要。

1. 抖动源通常的抖动源包括:锁相环的内部电路晶振的随机热噪声其他振荡器晶振振荡的随机机械噪声信号传输器走线和电缆接口接收器除了这些源,端接依赖,串扰,反射,趋肤效应,电源塌陷,地弹和临近设备的电磁串扰也会增加抖动量。

如果存在临近的同步同相,反射和串扰都会被放大。

除了电源和地导致的噪声,电路阻抗的变化是数据通讯电路中大部分抖动的来源。

2. 抖动的组成抖动的2个主要组成部分是随机抖动(random jitter)和确定性抖动(deterministic jitter)1) 随机抖动随机抖动是由于电路内部内在的噪声造成的,典型的是呈现出高斯分布。

随机抖动(RJ)是由于随机源,如衬底和电源。

电源噪声影响信号的上升速率在切换点产生时序问题。

随机抖动是平方的和,呈现钟形曲线。

由于随机噪声没有边界,所以它的特性通过标准偏差来表示2) 确定性抖动确定性抖动依赖于数据样式(data pattern),来源于独立的源。

源通常和设备传输介质有关,但是也有可能由电源噪声,串扰和信号调制有关。

确定性抖动时线性的相加,它通常有特别的源。

确定性抖动没有按高斯随机分布,并且幅度有边界。

确定性抖动(DJ)的特性通过它的边界,峰峰值来表示。

3. 抖动的种类抖动的种类有很多。

周期性抖动,周期间抖动,半周期间抖动将在下文具体描述。

电子工程师岗位面试题及答案(经典版)

电子工程师岗位面试题及答案一、基础知识与技能1.请介绍一下您的电子工程背景和相关经验。

答案:我获得了电子工程学士学位,并在过去的五年中在一家半导体公司工作,专注于集成电路设计和测试。

我参与了多个项目,包括XXX芯片的设计和优化,以及YYY传感器的嵌入式系统开发。

2.解释一下功率放大器的工作原理。

答案:功率放大器是将输入信号的能量放大到足够大的输出信号的装置。

它包括一个放大元件,如晶体管,以及适当的电源和电路来确保线性放大。

例如,类AB功率放大器通过结合类A和类B的特点,实现了较高的效率和较低的失真。

3.什么是噪声?在电子电路中如何处理噪声?答案:噪声是电子电路中不期望的随机信号。

它可以影响信号质量和精确度。

处理噪声的方法包括使用滤波器、接地技巧、差分信号传输和合适的屏蔽方法,以最小化噪声对信号的干扰。

4.请解释什么是嵌入式系统,并提供一个实际应用示例。

答案:嵌入式系统是集成在其他设备中,用于执行特定任务的计算机系统。

例如,汽车中的发动机控制单元(ECU)是一个嵌入式系统,负责监控和控制引擎操作,以优化燃油效率和性能。

5.您在硬件描述语言(HDL)方面有经验吗?请描述一下您在HDL 项目中的角色。

答案:是的,我熟悉VerilogHDL,并在以前的项目中使用过。

例如,在一个数字信号处理器的设计中,我负责编写Verilog代码,描述其算法和控制逻辑,并与团队进行协调,确保功能正确实现。

二、电路设计与分析6.请解释什么是电压分压器,并说明其在电路中的应用。

答案:电压分压器是由两个电阻构成的电路,用于将电压分成更小的部分。

在电路中,它常用于将高电压信号降低到适合其他电路部分的范围,如模拟信号输入到模数转换器(ADC)。

7.如何设计一个低通滤波器?请描述设计流程。

答案:低通滤波器用于通过低频信号并削弱高频信号。

设计过程包括选择滤波器类型(如巴特沃斯、切比雪夫等)、截止频率,然后根据滤波器的传递函数计算电阻和电容值。

时钟和定时芯片降低抖动提高精度

时钟和定时芯片降低抖动提高精度时钟和定时芯片降低抖动提高精度时钟和定时芯片是现代电子产品中不可或缺的组成部分。

它们在各种应用中都具有重要的作用,如通信设备、计算机、汽车电子以及工业自动化等领域。

然而,由于各种因素的干扰,时钟和定时芯片在实际应用中可能会出现抖动问题,从而降低了精度。

本文将讨论抖动的原因以及如何通过各种方法来降低抖动,以提高时钟和定时芯片的精度。

一、抖动的原因抖动是指时钟或定时芯片在其理想频率周围产生的随机时间偏差。

其主要原因包括以下几个方面:1. 外部干扰:时钟和定时芯片可能会受到来自电源波动、信号干扰、温度变化等外部因素的干扰,从而导致抖动。

2. 设计缺陷:在时钟和定时芯片的设计中,可能存在电路设计不合理、布局问题或者材料质量等方面的缺陷,这些都可能对抖动产生影响。

3. 阻尼问题:时钟和定时芯片内部的振荡器可能存在阻尼不足的问题,从而导致抖动的产生。

4. 时钟信号传输问题:当时钟信号被传输到其他电路或系统时,可能会受到传输线路质量、噪声等因素的影响,从而引起抖动。

二、降低抖动的方法为了提高时钟和定时芯片的精度,需要采取相应的措施来降低抖动。

以下是几种常见的方法:1. 选择合适的振荡器:振荡器是时钟和定时芯片的关键组件,选择合适的振荡器对降低抖动至关重要。

一般而言,TCXO(温度补偿型晶体振荡器)和OCXO(精确温度补偿型晶体振荡器)具有较高的精度和稳定性,可用于要求较高精度的领域。

2. 优化电路设计:在时钟和定时芯片的设计过程中,需要注意电路的布局、功耗管理以及环境干扰等因素,优化电路设计可以有效减少抖动问题的发生。

3. 降低干扰影响:通过合理的防护措施,例如添加滤波电容、隔离干扰源等,可以有效降低外部干扰对时钟和定时芯片的抖动影响。

4. 传输线路优化:对于需要传输时钟信号的场景,应注意优化传输线路的设计,减少噪声干扰和信号失真,从而避免抖动问题的产生。

5. 使用校准技术:校准技术可以通过对时钟和定时芯片的输出进行实时校准,从而提高其精度和稳定性。

时钟的抖动测量与分析

行信号接收端误码率高、系统不稳定等现象,因此时钟抖动的测量与分析非常重要。

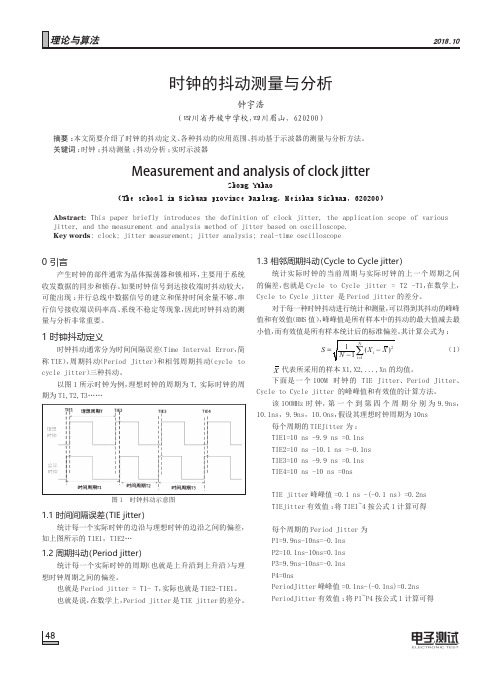

1 时钟抖动定义时钟抖动通常分为时间间隔误差(Time Interval Error,简称TIE),周期抖动(Period Jitter)和相邻周期抖动(cycle to cycle jitter)三种抖动。

以图1所示时钟为例,理想时钟的周期为T,实际时钟的周期为T1,T2,T3……图1 时钟抖动示意图1.1 时间间隔误差(TIE jitter)统计每一个实际时钟的边沿与理想时钟的边沿之间的偏差,如上图所示的TIE1,TIE2…1.2 周期抖动(Period jitter)统计每一个实际时钟的周期(也就是上升沿到上升沿)与理想时钟周期之间的偏差。

也就是Period jitter = T1- T,实际也就是TIE2-TIE1。

也就是说,在数学上,Period jitter 是TIE jitter 的差分。

对于每一种时钟抖动进行统计和测量,可以得到其抖动的峰峰值和有效值(RMS 值),峰峰值是所有样本中的抖动的最大值减去最小值,而有效值是所有样本统计后的标准偏差。

其计算公式为:S =(1)X 代表所采用的样本X1,X2,...,Xn 的均值。

下面是一个100M 时钟的 TIE Jitter、Period Jitter、Cycle to Cycle jitter 的峰峰值和有效值的计算方法。

该1OOMHz 时钟,第一个到第四个周期分别为9.9ns,10.1ns,9.9ns,10.Ons,假设其理想时钟周期为10ns每个周期的TIEJitter 为:TIE1=10 ns -9�9 ns =0�1ns TIE2=10 ns -10�1 ns =-0�1ns TIE3=10 ns -9�9 ns =0�1ns TIE4=10 ns -10 ns =0nsTIE jitter 峰峰值=0.1 ns -(-0.1 ns)=0.2ns TIEjitter 有效值:将TIE1~4按公式1计算可得每个周期的Period Jitter 为P1=9�9ns-10ns=-0�1ns P2=10�1ns-10ns=0�1ns P3=9�9ns-10ns=-0�1ns P4=0nsPeriodJitter 峰峰值=0.1ns-(-0.1ns)=0.2ns PeriodJitter 有效值:将P1~P4按公式1计算可得49(通常为幅度的 50%)的水平宽度。

时间抖动(jitter)的概念及其分析方法

时间抖动(jitter)的概念及其分析方法随着通信系统中的时钟速率迈入GH z级,抖动这个在模拟设计中十分关键的因素,也开始在数字设计领域中日益得到人们的重视。

在高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。

不仅如此,它还会导致通信链路的误码率增大,甚至限制A/D转换器的动态范围。

有资料表明在3GH z以上的系统中,时间抖动(jitter)会导致码间干扰(ISI),造成传输误码率上升。

在此趋势下,高速数字设备的设计师们也开始更多地关注时序因素。

本文向数字设计师们介绍了抖动的基本概念,分析了它对系统性能的影响,并给出了能够将相位抖动降至最低的常用电路技术。

本文介绍了时间抖动(jitter)的概念及其分析方法。

在数字通信系统,特别是同步系统中,随着系统时钟频率的不断提高,时间抖动成为影响通信质量的关键因素。

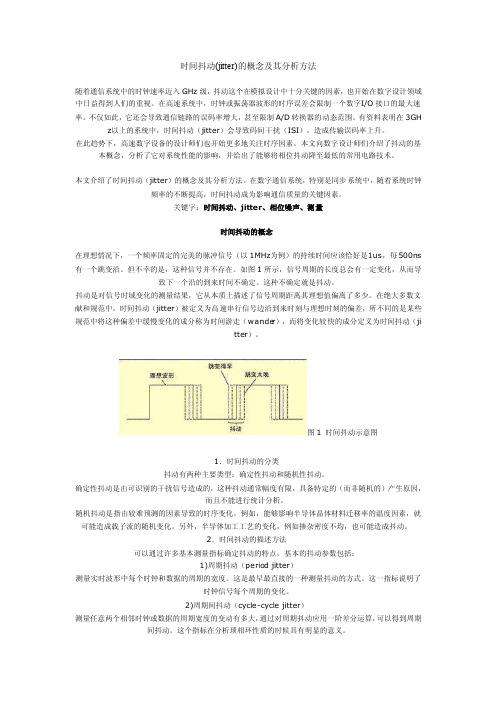

关键字:时间抖动、jitter、相位噪声、测量时间抖动的概念在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500ns 有一个跳变沿。

但不幸的是,这种信号并不存在。

如图1所示,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。

这种不确定就是抖动。

抖动是对信号时域变化的测量结果,它从本质上描述了信号周期距离其理想值偏离了多少。

在绝大多数文献和规范中,时间抖动(jitter)被定义为高速串行信号边沿到来时刻与理想时刻的偏差,所不同的是某些规范中将这种偏差中缓慢变化的成分称为时间游走(wander),而将变化较快的成分定义为时间抖动(jitter)。

图1 时间抖动示意图1.时间抖动的分类抖动有两种主要类型:确定性抖动和随机性抖动。

时钟抖动的定义与测量方式

译自: SiT-AN10007 Rev 1.2 January 2014Clock Jitter Definitions and Measurement Methods时钟抖动的定义与测量方式[译]懒兔子1 简介抖动是实际信号的一组边沿与理想信号之间的偏差(兔子:说白了,抖动就是实际情况和理想情况不一样,差别越大抖动越大)。

时钟信号的抖动通常由系统中的噪声或其他干扰因素引起。

影响因素包括热噪声、电源变化(波动)、负载的状况(负载也可以反过来影响时钟信号)、设备噪声和临近电路耦合进来的干扰。

2 抖动的分类抖动可以通过许多方式测量(不同方式测量到的抖动被分别加以定义),以下是主要的抖动分类:1. 周期抖动(Period Jitter)2. 相邻周期间的抖动(Cycle to Cycle Period Jitter)3. 长时间抖动(Long Term Jitter)4. 相位抖动(Phase Jitter)5. 单位时间间隔抖动(TIE,Time Interval Error)2.1 周期抖动周期抖动是时钟信号的实际周期长度与理想周期长度之间的偏差,测量样本为数目不定(随机)的一组周期。

如果给定一定数目的单个时钟周期,我们就可以通过测量每个周期的长度并计算平均的周期长度,以及这些时钟周期的标准差和峰峰值(peak-to-peak value)。

这里所说的标准差和峰峰值也分别被称为RMS抖动和Pk-Pk周期抖动。

许多文献将周期抖动直接定义为被测时钟周期与理想周期之间的误差。

但是真实情况下很难对理想周期进行量化。

如果我们用示波器观察一个标称100MHz的晶振,测得的平均时钟周期却可能是9.998ns,而不是理想的10ns。

所以退而求其次,通常将平均周期作为理想周期看待(兔子:因为实际周期都是在理想值周围按照一定规律分布的,如果测量时间足够长,得到的平均值就可以非常接近理想值)。

2.1.1 周期抖动的应用周期抖动对于计算数字系统的时序裕量十分有用。

时钟抖动(ClockJitter)和时钟偏斜(ClockSkew)

时钟抖动(ClockJitter)和时钟偏斜(ClockSkew)系统时序设计中对时钟信号的要求是⾮常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。

但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

所谓抖动(jitter),就是指两个时钟周期之间存在的差值,这个误差是在时钟发⽣器内部产⽣的,和晶振或者PLL内部电路有关,布线对其没有影响。

如下图所⽰:除此之外,还有⼀种由于周期内信号的占空⽐发⽣变化⽽引起的抖动,称之为半周期抖动。

总的来说,jitter可以认为在时钟信号本⾝在传输过程中的⼀些偶然和不定的变化之总和。

时钟偏斜(skew)是指同样的时钟产⽣的多个⼦时钟信号之间的延时差异。

它表现的形式是多种多样的,既包含了时钟驱动器的多个输出之间的偏移,也包含了由于PCB⾛线误差造成的接收端和驱动端时钟信号之间的偏移。

时钟偏斜指的是同⼀个时钟信号到达两个不同寄存器之间的时间差值,时钟偏斜永远存在,到⼀定程度就会严重影响电路的时序。

如下图所⽰:信号完整性对时序的影响,⽐如串扰会影响微带线传播延迟;反射会造成数据信号在逻辑门限附近波动,从⽽影响最⼤/最⼩飞⾏时间;时钟⾛线的⼲扰会造成⼀定的时钟偏移。

有些误差或不确定因素是仿真中⽆法预见的,设计者只有通过周密的思考和实际经验的积累来逐步提⾼系统设计的⽔平。

Clock skew 和Clock jitter 是影响时钟信号稳定性的主要因素。

很多书⾥都从不同⾓度⾥对它们进⾏了解释。

其中“透视”⼀书给出的解释最为本质:Clock Skew: The spatial variation in arrival time of a clock transition on an integrated circuit;Clock jitter: The temporal vatiation of the clock period at a given point on the chip;简⾔之,skew通常是时钟相位上的不确定,⽽jitter是指时钟频率上的不确定(uncertainty)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

深圳奥康迪科技有限公司

时钟的稳定性和抖动(2)

造成时钟不稳定的原因是什么?开关在开通和关断时会产生高频噪声,这些噪声通过不同引脚进入国产IC ,并且难以滤除和抑制,最终只能通过降低MOSFET 的关断速度来减少噪声的产生。

对于大多数开关,开通需要一定的延时,或降低开通的速度,使输出/钳位二极管在MOSFET 开通前彻底恢复阻断能力。

否则,开关开通时将有非常大的反向恢复尖峰电流流过二极管和MOSFET ,使效率严重降低。

但许多工程师凭直觉认为“开通应慢一些,关断应尽可能的快”这种观点是错误的,因为有时时钟也因此变得完全不稳定。

可能瞬间导致开关损坏。

因此,在优化变换器的整体性能之前的故障诊断过程中,首先应采用较大的栅极开通和关断电阻。

开关电源设计的首要目标是使电源可靠的开关,随后确保限流电路、占空比限制、电压前馈等功能全部恢复正常,最后才考虑如何提高效率,即确定挑食过程中的优先顺序。

应特别注意,开关的损坏对检查电源的问题毫无帮助,只会使生产人缘失去耐心。

你能做的一件事是设法提高电路或控制IC 的噪声容限。

本文由奥康迪科技有限公司发布。