计组实验报告3

计组实验报告范文-3存储器和IO扩展实验

计组实验报告范文-3存储器和IO扩展实验综合实验报告(2022--2022年度第一学期)名称:计算机组成原理综合实验题目:存储器和I/O扩展实验院系:计算机系班级:学号:学生姓名:指导教师:设计周数:一周成绩:日期年月一、目的与要求实验目的:(1)熟悉ROM芯片和RAM芯片在功能和使用方法等方面的相同和差异之处;学习用编程器设备向EEPROM芯片内写入一批数据的过程和方法。

(2)理解并熟悉通过字、位扩展技术实现扩展存储器系统容量的方案;(3)了解静态存储器系统使用的各种控制信号之间正常的时序关系;(4)了解如何通过读、写存储器的指令实现对58C65ROM芯片的读、写操作;(5)加深理解存储器部件在计算机整机系统中的作用;(6)学习串行口的正确设置和使用。

实验要求:(1)实验之前认真预习,明确实验目的和具体内容,设计好扩展8K字存储器容量的线路图,标明数据线和控制信号的连接关系,做好实验之前的必要准备;(2)想好实验步骤,明确通过实验到底可以学习哪些知识,想想怎么样有意识的提高教学实验的真正效果;(3)在教学实验过程中,要爱护教学实验设备和用到的辅助仪表,记录实验步骤中的数据和运算结果,仔细分析遇到的现象与问题,找出解决问题的办法,有意识的提高自己的创新思维能力;(4)实验之后认真写出实验报告,总结自己再实验过程中的收获,善于总结和发现问题。

二、实验正文1.主存储器实验内容1.1实验的教学计算机的存储器部件设计(说明只读存储器的容量、随机读写器的容量,各选用了什么型号及规格的芯片、以及地址空间的分布)答:ROM存储区选用4片长度8位、容量8KB的58C65芯片实现,RAM存储区选用2片长度8位、容量2KB的6116芯片实现,每2个8位的芯片合成一组用于组成16位长度的内存字,6个芯片被分成3组,其地址空间分配关系是:0-1777h用于第一组ROM,固化监控程序,2000-2777h用于RAM,保存用户程序和用户数据,其高端的一些单元作为监控程序的数据区,第二组ROM的地址范围可以由用户选择,主要用于完成扩展内存容量(存储器的字、位扩展)的教学实验1.2扩展8K字的存储空间,需要多少片58C65芯片,58C65芯片进行读写时的特殊要求答:第一,要扩展8K字的存储空间,需要使用2片(每一片有8KB容量,即芯片内由8192个单元、每个单元由8个二进制位组成)存储器芯片实现。

小组计算机实验报告三

实验报告课程名称:计算机在材料科学中的应用指导教师:付江盛班级:10粉体小组成员姓名与学号:何树斌2010260103李蓓2010260143实验名称:正交实验设计与数据分析一、实验目的1、掌握正交实验设计方法2、会用相关软件或自编程序正交实验的数据进行分析二、实验原理1、全面实验法三因素三水平全面实验法的实验安排根据A、B、C的不同组合共有33=27次实验。

其优点是对各因素与实验指标(即实验结果)之间的关系剖析得比较清楚;其缺点是:(1)实验次数太多、费时、费事,当因素水平比较多时。

实验无法完成;(2)不做重复实验无法估计误差;(3)无法区分因素主次。

2、简单比较法简单比较法是变化一个因素而固定其他因素,如首先固定B、C于B1、C1,使A变化,如果得出结果A3最好,则固定A于A3,C还是C1,使B变化,如果得出B2最好,则固定B于B2,A于A3,使C变化,如果实验结果以C2最好,于是得出最佳工艺条件为A3B2C2。

其优点是实验次数少;缺点是:(1)实验点不具有代表性;(2)考察的因素水平仅限于局部区域,不能全面地反映因素的实际情况;(3)无法分清因素的主次。

如果不进行重复实验,实验误差就估计不出来,因此无法确定最佳分析条件的精度;(4)很难利用数理统计方法对实验结果进行分析。

3、正交实验法考虑兼顾全面实验法和简单比较法的优点,利用依据数学原理制作好的规格化表——正交表来设计实验不失为一种上策。

用正交表来安排实验及分析实验结果,这种方法叫做正交实验法。

事实上,正交实验法的优点不仅表现在实验的设计上,更表现在对实验结果的处理上。

正交实验法的优点有:(1)实验点代表性强,实验次数少;(2)不需做重复实验就可以估计实验误差;(3)可以分清因素的主次;(4)可以使用数理统计的方法处理实验结果。

(1)正交表符号正交表安排实验需要考虑的结果称为实验指标(简称指标),可以直接用数量表示的叫定量指标,不能用数量表示的叫定性指标。

《计算机组成原理》实验报告3

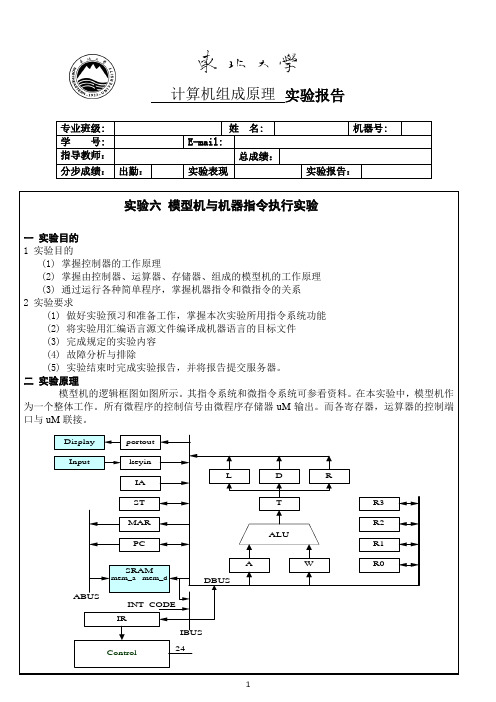

《计算机组成》实验报告实验名称:数据通路组成实验一、实验目的1、掌握时序产生器的组成原理。

2、掌握微程序控制器的组词原理。

3、掌握微指令格式的化简和归并。

二、实验内容(1)按实验要求,连接实验台的数码开关K0—K15 、控制开关、按钮开关、时钟信号源和微程序控制器。

注意:本次实验只做微程序控制器本身的实验,故微程序控制器输出的微命令信号与执行部件(数据通路)的连线暂不连接。

连线完成后应仔细检查一遍,然后才可加上电源。

(2)观察时序信号用双踪示波器观测时序产生器的输入输出信号:MF,W1—W4,T1—T4。

比较相位关系,画出其波形,并标注测量所得的脉冲宽度。

观察时须将TJ1 接低电平,DB,DZ,DP开关均置0状态,然后按QD按钮,则连续产生T1,T2,T3,T4,W1,W2,W3,W4。

了解启停控制信号的功能,并熟练地使用连接这些控制信号的按钮或开关。

(3)熟习微指令格式的定义,按此定义将控制台指令微程序地8条微指令按十六进制编码,SWA A三个二进制开关地状态来指列于下表。

三种控制台指令地功能由SWC,SWB,SW定(KRD=001B,KWE=010B,PR=010B)。

此表必须在预习时完成。

微指令地址微指令编码微指令地址微指令编码00H 3CH 07H 17H 27H 3FH 3DH 3EH 单拍(DP)方式执行控制台微程序,读出上述八条微指令,用P字段和微地址指示灯跟踪微指令执行情况,并与上表数据对照。

用连续方式执行KWE和KRD(将TJ1接地),画出uA0(28C64的地址A0)信号波形,作出解释。

SWA A的状态组合,观察验证三种控制台指令KWE和KRD,PD (4)用P3 和SWC,SWB,SW微地址转移逻辑功能地实现。

(5)熟习05H,10H两条微指令的功能和P2测试的状态(IR4—IR7),用二进制开关设置IR7—IR4的不同状态,观察ADD至STP九条机器指令微地址转移逻辑功能的实现。

计组第三次实验报告总结

34

35

36

37

W=21H

A=0DFH

AND A,#55H

02

03

5C 55

累加器A逻辑与立即数55H

C7FFEF

FFFE93

CBFFFF

03

04

5C

5D

5E

W=55H

A=55H

OR A,02H

04

05

68 02

累加器A逻辑或存储器02单元的内容

C77FFF

D7BFEF

FFFE92

CBFFFF

05

汇编指令

程序地址

机器码

指令说明

微程序

PC

uPC

运行时寄存器或存储器的值

MOVA,#12

00

01

7C 12

立即数12H送到累加器A

C7FFF7

CBFFFF

01

02

7C

7D

A=12H

MOV A,R0

02

70

寄存器R0送到累加器A

FFF7F7

CBFFFF

03

70

71

A=00H

MOV A,@R0

03

74

R0间址的存储器内容送到累加器A

汇编指令

程序地址

机器码

指令说明

微程序

PC

uPC

运行时寄存器或存储器的值

MOV A,#55H

00

01

7C 55

把立即数55H放入A中

C7FFF7

CBFFFF

01

02

7C

7D

A=55H

RRA

02

D0

把A中数逻辑右移

FFFCB7

计组存储器实验实验报告(3篇)

第1篇一、实验目的1. 理解存储器的基本组成和工作原理;2. 掌握存储器的读写操作过程;3. 熟悉存储器芯片的引脚功能及连接方式;4. 了解存储器与CPU的交互过程。

二、实验环境1. 实验设备:TD-CMA计算机组成原理实验箱、计算机;2. 实验软件:无。

三、实验原理1. 存储器由地址线、数据线、控制线、存储单元等组成;2. 地址线用于指定存储单元的位置,数据线用于传输数据,控制线用于控制读写操作;3. 存储器芯片的引脚功能:地址线、数据线、片选线、读线、写线等;4. 存储器与CPU的交互过程:CPU通过地址线访问存储器,通过控制线控制读写操作,通过数据线进行数据传输。

四、实验内容1. 连线:按照实验原理图连接实验箱中的存储器芯片、地址线、数据线、控制线等;2. 写入操作:将数据从输入单元IN输入到地址寄存器AR中,然后通过控制线将数据写入存储器的指定单元;3. 读取操作:通过地址线指定存储单元,通过控制线读取数据,然后通过数据线将数据输出到输出单元OUT;4. 实验步骤:a. 连接实验一(输入、输出实验)的全部连线;b. 按实验逻辑原理图连接两根信号低电平有效信号线;c. 连接A7-A0 8根地址线;d. 连接13-AR正脉冲有效信号线;e. 在输入数据开关上拨一个地址数据(如00000001,即16进制数01H),拨下开关,把地址数据送总线;f. 拨动一下B-AR开关,实现0-1-0”,产生一个正脉冲,把地址数据送地址寄存器AR保存;g. 在输入数据开关上拨一个实验数据(如10000000,即16进制数80H),拨下控制开关,把实验数据送到总线;h. 拨动控制开关,即实现1-0-1”,产生一个负脉冲,把实验数据存入存储器的01H号单元;i. 按表2-11所示的地址数据和实验数据,重复上述步骤。

五、实验结果与分析1. 通过实验,成功实现了存储器的读写操作;2. 观察到地址线、数据线、控制线在读写操作中的协同作用;3. 理解了存储器芯片的引脚功能及连接方式;4. 掌握了存储器与CPU的交互过程。

计组实验报告(共10篇)

计组实验报告(共10篇)计组实验报告计算机组成原理实验报告一一、算术逻辑运算器1. 实验目的与要求:目的:①掌握算术逻辑运算器单元ALU(74LS181)的工作原理。

②掌握简单运算器的数据传输通道。

③验算由74LS181等组合逻辑电路组成的运输功能发生器运输功能。

④能够按给定数据,完成实验指定的算术/逻辑运算。

要求:完成实验接线和所有练习题操作。

实验前,要求做好实验预习,掌握运算器的数据传送通道和ALU 的特性,并熟悉本实验中所用的模拟开关的作用和使用方法。

实验过程中,要认真进行实验操作,仔细思考实验有关的内容,把自己想得不太明白的问题通过实验去理解清楚,争取得到最好的实验结果,达到预期的实验教学目的。

实验完成后,要求每个学生写出实验报告。

2. 实验方案:1.两片74LS181(每片4位)以并/串联形式构成字长为8为的运算器。

2.8为运算器的输出经过一个输入双向三态门(74LS245)与数据总线相连,运算器的两个数据输入端分别与两个8位寄存器(74LS273)DR1和DR2的输出端相连,DR1和DR2寄存器是用于保存参加运算的数据和运算的结果。

寄存器的输入端于数据总线相连。

3.8位数据D7~D0(在“INPUT DEVICE”中)用来产生参与运算的数据,并经过一个输出三态门(74LS245)与数据总线相连。

数据显示灯(BUS UNIT)已与数据总线相连,用来显示数据总线上所内容。

4.S3、S2、S1、S0是运算选择控制端,由它们决定运算器执行哪一种运算(16种算术运算或16种逻辑运算)。

5.M是算术/逻辑运算选择,M=0时,执行算术运算,M=1时,执行逻辑运算。

6.Cn是算术运算的进位控制端,Cn=0(低电平),表示有进位,运算时相当于在最低位上加进位1,Cn=1(高电平),表示无进位。

逻辑运算与进位无关。

7.ALU-B是输出三态门的控制端,控制运算器的运算结果是否送到数据总线BUS上。

低电平有效。

华工计组实验报告

实验名称:计算机组成原理实验实验目的:1. 理解计算机组成原理的基本概念和原理。

2. 掌握计算机各个组成部件的功能和相互关系。

3. 通过实验加深对计算机组成原理的理解和应用。

实验时间:2023年X月X日实验地点:计算机实验室实验器材:1. 计算机组成原理实验箱2. 计算机组成原理实验指导书3. 计算器4. 计算机组成原理实验数据记录表实验内容:一、实验一:计算机硬件系统结构1. 实验目的:了解计算机硬件系统的基本结构,包括中央处理器(CPU)、存储器、输入输出设备等。

2. 实验步骤:(1)观察实验箱的硬件组成,识别各个硬件部件。

(2)了解各个硬件部件的功能和相互关系。

(3)记录实验数据。

3. 实验结果与分析:实验结果显示,计算机硬件系统主要由CPU、存储器、输入输出设备等组成。

CPU负责处理数据,存储器负责存储数据,输入输出设备负责与用户进行交互。

二、实验二:CPU工作原理1. 实验目的:了解CPU的工作原理,包括指令周期、时钟周期、数据通路等。

2. 实验步骤:(1)观察实验箱的CPU模块,识别各个部件。

(2)了解CPU各个部件的功能和相互关系。

(3)进行指令周期和时钟周期的实验,记录实验数据。

3. 实验结果与分析:实验结果显示,CPU的工作原理包括指令周期和时钟周期。

指令周期是指执行一条指令所需的时间,时钟周期是指CPU中时钟信号的周期。

实验数据表明,CPU通过数据通路进行指令的执行,完成数据处理。

三、实验三:存储器工作原理1. 实验目的:了解存储器的工作原理,包括随机存储器(RAM)、只读存储器(ROM)等。

2. 实验步骤:(1)观察实验箱的存储器模块,识别各个存储器。

(2)了解存储器的功能和特点。

(3)进行存储器读写实验,记录实验数据。

3. 实验结果与分析:实验结果显示,存储器包括RAM和ROM。

RAM具有读写功能,而ROM只能读。

实验数据表明,存储器通过地址译码器进行寻址,实现数据的读写。

计算机组成原理实验三报告

管理学院信息管理与信息系统专业 3 班______组、学号姓名协作者教师评定_____________实验题目_微程序控制器实验__________________1.实验目的与要求:实验目的:(1).理解时序产生器的原理,了解时钟和时序信号的波形。

(2).掌握微程序控制器的功能、组成知识。

(3).掌握微指令格式和各字段功能。

(4).掌握微程序的编制、写入、观察微程序的运行,学习基本指令的执行流程。

实验要求:(1).按练习一要求完成测量波形的操作,画出TS1、TS2、TS3、TS4的波形,并测出所用的脉冲Φ的周期。

(2).按练习二的要求输入微指令的二进制代码表,并单步运行五条机器指令。

(3).实验时,结合读、写微指令流程图,选择存储器地址和数据不断对RAM写入数据,执行时为循环重复执行微指令,直到有P2(CLR)清零信号作用时才停止。

(4)结合实验内容,将数据00H-002H存入存储器6116的00H-002H 单元,,写出实验步骤,并在实验中加以验证。

2.实验方案:(1)按要求在实验仪上接好线,仔细检查正确与否,无误后才接通电源,每次实验都要接一些线,先接线,后打开电源,养成不带电接线的习惯,这样可以避免烧坏实验仪器。

(2)编程写入E2PROM28161)将编程开关(MJ20)置为PROM(编程)状态;2)将STATE UNIT中的STEP置为“STEP”状态,STOP置为“RUN”状态;3)在UA5-UA0开关上置要写的某个微地址(八进制);4)在MK24-MK1开关上置要写的微地址相应的24位微代码,24位开关对应24位显示灯,开关量为“1”灯亮,为“0”灯灭;5)启动时序电路(按动启动按钮START),即将微代码写入到E2PROM2816的相应地址对应的单元中;6)重复(3)~(5)步骤将每一条微指令写入E2PROM2816。

(3)校验1)将编程开关置为READ状态;2)将STEP开关置为“STEP”状态,STOP开关置为“RUN”状态;3)在开关UA5~UA0上置好要读的某个微地址;4)按动START键,启动时序电路,观察显示灯MD24-MD1的状态,检查读出的微代码是否已写入的相同。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

case(F_LED_SW)

3'b000:LED[7:0] = F[7:0];

3'b001:LED[7:0] = F[15:8];

3'b010:LED[7:0] = F[23:16];

3'b011:LED[7:0] = F[31:24];

3'b111: begin LED[7] = ZF; LED[0] = OF; LED[6:1] = 6'b0; end

#100;

ALU_OP = 101;

AB_SW = 101;

F_LED_SW = 000;

#100;

ALU_OP = 110;

AB_SW = 110;

F_LED_SW = 000;

#100;

ALU_OP = 111;

AB_SW = 111;

F_LED_SW = 000;

end

endmodule

二、仿真波形

output OF;

always@(*)

bБайду номын сангаасgin

case(AB_SW)

3'b000: begin A=32'h0000_0000; B=32'h0000_0000; end

3'b001: begin A=32'h0000_0003; B=32'h0000_0607; end

3'b010: begin A=32'h8000_0000; B=32'h8000_0000; end

default: begin LED[7] = ZF; LED[0] = OF; LED[6:1] = 6'b0; end

endcase

end

endmodule

仿真测试

module ALUTest;

// Inputs

reg [2:0] ALU_OP;

reg [2:0] AB_SW;

reg [2:0] F_LED_SW;

NET "LED[3]"LOC = "V15";

NET "LED[4]"LOC = "M11";

NET "LED[5]"LOC = "N11";

NET "LED[6]"LOC = "R11";

NET "LED[7]"LOC = "T11";

五、调试

1刚开始不知道怎么去设计,后来查书发现使用always (*)可以把这个搞定

2做运算的时候灯不亮,看了下源代码才发现忘记给LED灯赋值了,然后在选择这一个

这个程序的复杂度比之前的2个难了好多,不管是复杂度还是在设计上的难度,不过最后模块化设计以后还是比较好做,但是也花了很长时间的查错和调试,毕竟接触的时间不是很长,很多错误都要调试半天才能够解决,但是最后通.F(F),

.LED(LED),

.ZF(ZF),

.OF(OF)

);

initial begin

// Initialize Inputs

ALU_OP = 0;

AB_SW = 0;

F_LED_SW = 0;

// Wait 100 ns for global reset to finish

#100;

ALU_OP = 000;

NET "F_LED_SW[0]"LOC = "T10";

NET "F_LED_SW[1]"LOC = "T9";

NET "F_LED_SW[2]"LOC = "C4";

NET "LED[0]"LOC = "U16";

NET "LED[1]"LOC = "V16";

NET "LED[2]"LOC = "U15";

AB_SW = 001;

F_LED_SW = 000;

#100;

ALU_OP = 001;

AB_SW = 001;

F_LED_SW = 000;

#100;

ALU_OP = 010;

AB_SW = 010;

F_LED_SW = 000;

#100;

ALU_OP = 100;

AB_SW = 100;

F_LED_SW = 000;

3'b110: begin A=32'hFFFF_FFFF; B=32'h8000_0000; end

3'b111: begin A=32'h1234_5678; B=32'h3333_2222; end

default: begin A=32'h9ABC_DEF0; B=32'h1111_2222; end

实验报告

成绩:

姓名

黄涛

卢玉琦

学号

13084220

13084225

班级

13080211

专业

信息安全

课程名称

《计算机组成原理》

任课老师

戴钧

指导老师

戴钧

机位号

实验序号

1

实验名称

多功能ALU的设计

实验时间

2015.9.8

实验地点

1教235

实验设备号

一、实验程序源代码

module ALU(ALU_OP, AB_SW, F_LED_SW, F, LED, ZF, OF);

// Outputs

wire [31:0]F;

wire [7:0]LED;

wire ZF;

wire OF;

// Instantiate the Unit Under Test (UUT)

ALU uut (

.ALU_OP(ALU_OP),

.AB_SW(AB_SW),

.F_LED_SW(F_LED_SW),

3'b111:begin F<=B<<A; end

default: F<=32'h0000_0000;

endcase

end

always@(*)

begin

if(F===32'h0000_0000)

ZF<=1;

else

ZF<=0;

end

assign OF=A[31]^B[31]^F[31]^C32;

always@(*)

reg[31:0]A;

reg[31:0]B;

input[2:0]ALU_OP;

input[2:0]AB_SW;

input[2:0]F_LED_SW;

reg[31:0]F;

reg[7:0]LED;

reg ZF;

wire OF;

reg C32;

output F;

output LED;

output ZF;

3'b011: begin A=32'h7FFF_FFFF; B=32'h7FFF_FFFF; end

3'b100: begin A=32'hFFFF_FFFF; B=32'hFFFF_FFFF; end

3'b101: begin A=32'h8000_0000; B=32'hFFFF_FFFF; end

三、电路图

四、引脚配置(约束文件)

NET "ALU_OP[0]"LOC = "U8";

NET "ALU_OP[1]"LOC = "V8";

NET "ALU_OP[2]"LOC = "T5";

NET "AB_SW[0]"LOC = "V9";

NET "AB_SW[1]"LOC = "M8";

NET "AB_SW[2]"LOC = "N8";

endcase

end

always@(*)

begin

case(ALU_OP)

3'b000:F<=A&B;

3'b001:F<=A|B;

3'b010:F<=A^B;

3'b011:F<=A~^B;

3'b100:{C32,F}<=A+B;

3'b101:{C32,F}<=A-B;

3'b110:begin if(A<B) F<=32'h0000_0001; else F<=32'h0000_0000; end