ADI实验室电路-带抗混叠滤波器的宽带接收机

ADI电路实验室电路说明书-AD7685

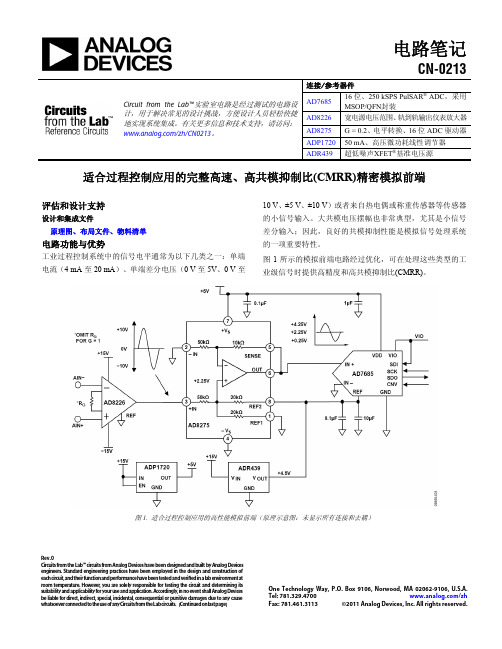

Rev.0Circuits from the Lab™ circuits from Analog Devices have been designed and built by Analog Devices engineers. Standard engineering practices have been employed in the design and construction of each circuit, and their function and performance have been tested and verified in a lab environment atroom temperature. However, you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly, in no event shall Analog Devices be liable for direct, indirect, special, incidental, consequential or punitive damages due to any cause One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: /zh电路笔记CN-0213连接/参考器件16位、250 kSPS PulSAR® ADC,采用MSOP/QFN封装AD7685Circuit from the Lab™实验室电路是经过测试的电路设计,用于解决常见的设计挑战,方便设计人员轻松快捷地实现系统集成。

ADI推出8通道超声模拟前端(AFE) AD9675

ADI 推出8 通道超声模拟前端(AFE)AD9675

北京2013 年2 月27 日-- Analog Devices,Inc. (NASDAQ:ADI),全球领先的高性能信号处理解决方案供应商,最近推出了8 通道超声模拟前端(AFE)AD9675,该器件内置片内RF 抽取器和JESD204B 串行接口,针对中高端便携式和手推式医用及工业超声系统而设计。

该器件集成了八通道的

低噪声放大器、可变增益放大器、抗混叠滤波器以及14 位模数转换器,具有

业界最高的采样速率(125 MSPS)和最佳的信噪比(75 dB SNR)性能,超声成像质量更佳。

片内RF 抽取器使ADC 可以过采样,在保持低数据I/O 速

率的同时提供增强的SNR,以实现更优画质。

5 Gbps JESD204B 串行接口与其它数据接口标准相比,可减少多达80%的超声系统I/O 数据路由。

该特性

简化了超声电路板的设计,同时更好地满足了工业上对于更高数据速率、更

多通道数以及更高图像分辨率的要求。

第二个型号AD9674 具有相同的基本

功能,但是采用了标准LVDS 接口。

AD9675 和AD9674 是ADI 公司屡获殊

荣的八通道超声接收器产品组合的最新产品。

ADI 推出低成本八通道超声接收器AD9675-AD9674

AD9675 和AD9674 均采用节约空间的144 引脚、10 mm x 10 mm BGA 封装,与AD9670/AD9671 引脚兼容,让需要降低成本和数字化功能有限的设

计能够轻松升级。

一种Sigma-DeltaADC中抽取滤波器的研究

重庆大学硕士学位论文ABSTRACTThis thesis focuses on the study and design a digital decimation filter in the Sigma-Delta ADC which used in the high-end audio device. Because of the merits, such as high-linearity, high-resolution and easy integratoin with digital circuit, it is widely used in the area of audio process, wireless communication and precision measurement. As the advance of the technology, Sigma-Delta ADC will be used in the wideband field, such as the digital video process. The Sigma-Delta ADC has two main parts, the frontend modulator and backend digital decimation filter. The modulator has two functions, the first is oversampling the input, the second is moving the qualitazation noise to higher frequency which called noiseshaping. The backend decimation filter downsamples the signal to the Nyquist Rate,at the same time,filters out the out-of-band quantization noise which be shaped by the modulator. So,the SNR in the baseband rises.The followings are the main content done in this thesis.Firstly, the whole design adopt a Top-down approach. Base on the specification that system must meet, the stucture and type of the filter need to be choosen in the beginning. The filter is implement with multistage multirate stucture. The CIC filter is choosen to be the first stage, followed by two stage of halfband filter and one CIC compensation filter. After comparing and analysis, the CIC compensation filter locates between the two halfband filters is the best choice for calculation efficient. At the same time, for further increase the calculation efficient, the last three stage use a two-phase structure which let the operation of the filter at the downsampled rate.Secondly, the filter is designed in the Matlab with FDAtool toolbox and Fdesign toolbox. The stopband attenuation of the filter is 120dB, passband ripple less than 0.01dB. Also the filter supports 24/20/16 bits output wordwidth, 96/48 kHz output frequency. After the coefficients of the flilter is calculated, they need to be coded into CSD. Due to the wordlength of the coefficient and the output have the effect on the resolution of the filter, after analysis, this design adopt 24 bit coefficient quantization and the most 24 bit output wordlength for meeting the design specifications.Thirdly, the design and testbench are written by Verilog HDL. Using Simulink which embeded in the Matlab and Sdtoolbox to build the model of the Sigma-Delta modulator. Thismodel is used to generate the dataflow of output of the modulator which is used to simulate and validate the function of the filter in the Modelsim.Finally, after validation the code, the next step of the design is synthesis the Verilog HDL by Design Compiler to get the netlist. Then the layout of the design can be achieved by the Auto-Place-and-Route tool, Astro. The technology library in my design is 0.18 um standard cell library. The area of the chip is 1.7mm*1.7mm. As such design adopts the top-down design method, it has good capability of duplication and transplantation. The operation of digital filter is a pure DSP process, so it is suitable for the use of FPGA to implement the filter. At last, Quartus, a FPGA software, is used to simulate the implement of the filter in the FPGA.Keywords: Sigma-Delta ADC, CSD, Decimation filter, CIC filter1 绪论1.1 引言根据“国际半导体技术路线”(International Technology Roadmap for Semiconductor, ITRS)的报告,CMOS工艺的特征尺寸会在未来至少十年当中继续降低,到2013年将会达到32nm。

CN-0242 高性能、高IF、75 MHz 带宽、14 位、250 MSPS 接收机前端说明书

ADI 中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI 不对翻译中存在的差异或由此产生的错误负责。

如需确认任何词语的准确性,请参考ADI 提供的最新英文版数据手册。

CN-0242Circuits from the Lab™ reference circuits are engineered and tested for quick and easy system integration to help solve today’s analog, mixed-signal, and RF design challenges. For more information and/or support, visit /CN0242AD9643 14位双通道ADC ,采样速率为250 MSPS ADL5202宽动态范围、高速、数字控制VGA具有带通抗混叠滤波器的高性能、高IF 、75 MHz 带宽、14位、250 MSPS 接收机前端Rev. 0Circuits from the Lab™ circuits from Analog Devices have been designed and built by Analog Devices engineers. Standard engineering practices have been employed in the design and construction of each circuit, and their function and performance have been tested and veri ed in a lab environment at room temperature. However , you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly , in no event shall Analog Devices be liable for direct, indirect, special, incidental, consequential or punitive damages due to any cause whatsoever connected to the use of any Circuits from the Lab circuits. (Continued on last page)One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113©2012 Analog Devices, Inc. All rights reserved. 0.1µF0.1µF0.1µF0.1µF0.1µF0.1µF 1µH 1µH+5V+5V300Ω150nH150nH180nH180nH140nH162Ω162ΩV CM3.3pF 12pF12pF20Ω20ΩINPUTZ = 50ΩANALOG INPUT –13.0dBm FS AT 182.5MHz4.1dB GAIN20dB GAINFILTER2.3dB LOSS1:3 Z145Ω293Ω100ΩINTERNAL INPUT Z3k Ω2.2pFAD964314-BIT 250MSPS ADC +5V~Z IN =150ΩFS = 1.75V p-p DIFF+1.8VADL5202VGA SET FOR 20dB GAIN10156-00175Ω75Ω图1. 四通道IF 接收机前端的单通道(原理示意图:未显示所有连接和去耦)增益、损耗和信号电平10 MHz 下测得值电路笔记连接/参考器件评估和设计支持设计和集成文件原理图、布局文件、物料清单电路功能与优势图1所示电路是基于ADL5202宽动态范围、高速、数字控制可变增益放大器(VGA)和14位、250 MSPS AD9643双通道模数转换器(ADC)的75 MHz 宽带接收机前端。

基于AD9680的宽带高动态全数字雷达接收机设计

基于AD9680的宽带高动态全数字雷达接收机设计肖丹丹;宿绍莹;李涛【摘要】针对某宽带雷达数字接收机对带宽、动态、处理速度、多通道等指标的需求,设计了一种基于新型ADC器件AD9680的宽带高动态全数字雷达接收机验证平台.文中首先在搭建的平台上对AD9680进行全带宽模式和数字下变频模式的性能验证与结果分析,根据分析结果提出改善AD9680动态性能的方案;其次,对AD9680两个通道之间的同步性做了验证,并提出了一种针对双通道时间偏差的优化方法.各项结果表明,AD9680能满足某宽带雷达的应用需求.【期刊名称】《电子科技》【年(卷),期】2015(028)010【总页数】4页(P141-144)【关键词】AD9680;宽带雷达数字接收机;JESD204B;数字下变频;双通道同步【作者】肖丹丹;宿绍莹;李涛【作者单位】国防科学技术大学电子科学与工程学院,湖南长沙410073;国防科学技术大学电子科学与工程学院,湖南长沙410073;国防科学技术大学电子科学与工程学院,湖南长沙410073【正文语种】中文【中图分类】TN957现代雷达数字接收机的特点是环境化、模块化[1],日益复杂的电磁环境要求宽带数字接收机必须具备以下功能:大瞬时带宽、实时信号接收、大动态范围、高灵敏度和频率分辨能力[2]。

基于软件无线电的宽带雷达数字接收机射频前端通过专用ADC(Analog-to-Digital Converter)芯片对射频信号直接采样,增加了射频前端的灵活性,减少了模拟环节[3]。

某雷达升级改进要求系统的量化位数达到14 位,采样率为1 GSample·s-1,能从水平与垂直两个极化通道采集频段为1.2 ~1.4 GHz的射频信号。

文献[4]实现了等效采样速率可达10 GSample·s-1的4 通道数字式脉冲超宽带雷达信号接收;文献[5]实现了基于拼接采样技术的宽带数字接收机,能对带宽1.2 GHz 的模拟信号以采样率3.2 GSample·s-1采样;但其的量化位数均只有10 位,能满足该雷达需求的数字接收机未见报道。

模块时代之ADI实验室电路 45页 7.2M 超清书签版

第三章 实战篇 资深工程师教你玩转ADI 实验室电路

3.1 ADI实验室电路DIY项目指南:

tyw藏书

作者:EEWORLD坛友chunyang ADI实验室电路品种繁多,涉及面很广,如何选择合适的DIY项目可能是件容易令人困扰的事,但深究起来,其实可玩

性是很大的,从今天开始,我将陆续放出近日研究ADI实验电路的一些心得和DIY项目建议。

决客户问题的售后中心。“

——网名:fsyicheng

“有了ADI实验室电路,工程师可以从细节中解放出来,重点关注自己的应用。”

——网名:lrz123

3

tyw藏书

第一章 概念篇

包括: 电路文档 测试数据 原理图 物料清单 布局文件 器件驱动 低成本评估

当今电子设计工作中,具有着前所未有的挑战,主要包括:

¾ 产品上市压力前所未有,设计团队规模更小

¾ 工程师必须运用更多技术

◆ 需要学习的东西增多

◆ 用于学习的时间减少

¾ 更多应用集成模拟和混合信号技术,难度增大

而作为设计主体的电子工程师,则面临着越来越大的挑战:

tyw藏书

“虽然技术不断进步,但最大的改变是开发周期越来越短。”——设计工程师 “我面对的混合技术设计越来越多,涉及单电路板系统集成模拟、数字和RF处理。”——PCB设计师

最后,我们也要感谢SOSO的辛勤整理,能够让ADI实验室电路如此系统、完整地呈现在大家面前。

EEWORLD执行总编:

2

推荐者说

tyw藏书

“半导体厂商越来越倾向于提供一揽子的解决方案,用以帮助客户以最快的速度和最低的研发成本推出新产品,一个典型的例子 就是“山寨手机”,但手机毕竟是高度集成的数字化产品,那么模拟电路的应用是否也可以走同样的路呢?看来已经有厂家在这么做 了,ADI实验室电路的推出就是解决模拟电路/模拟-数字混合电路应用的一揽子解决方案。”

抗混叠滤波器.

摘要文章是对抗混叠滤波器的设计研究,提出了一种过采样系统设计方案。

通过多次反复地对信号进行采样,然后通过将数字滤波和模拟滤波技术有机结合,充分发挥各自滤波器的特点来解决数据采集系统的抗混叠问题。

抗混叠滤波器的设计重点在数字滤波器部分,而FIR数字滤波器以其良好的线性特性、系统稳定等诸多优点,得到了广泛应用,也十分适合用于信号采集中的抗混叠滤波。

关键词:抗混叠滤波器;过采样;数字滤波器;目录摘要 (I)目录 (II)第1章绪论 (1)1.1课题研究背景和意义 (1)1.2课题研究现状 (1)1.3课题的目标与任务 (2)第2章抗混叠滤波器系统的构建 (3)2.1抗混叠滤波器设计的基本思路 (3)2.2数字滤波器的选择 (3)2.3过采样系统 (4)2.3.1过采样技术 (4)2.3.2过采样系统设计方案 (4)第3章抗混叠滤波器系统的仿真 (6)3.1FIR低通滤波器的设计 (6)3.1.1FIR数字滤波器的设计步骤 (6)3.1.2窗函数的选择 (6)3.1.3MATLAB相关函数的使用 (7)3.2过采样系统的构建与仿真 (8)结论 (11)参考文献 (12)致谢..................................................................................................错误!未定义书签。

附录. (13)第1章绪论1.1课题研究背景和意义现如今需要滤波器的领域十分多。

例如,采样视频系统中的信号混叠现象,当超出视频频段范围的高频信号通过数模转换器的采样过程混叠回视频频段时,就会产生混叠现象;随着电力电子技术的不断发展,电力电子装置广泛投入运行因而有大量的高次谐波注入电网,产生了严重的谐波污染,对于工农业生产造成了严重的影响;在当代煤矿的电网中,由于大量大功率和非线性设备的应用,致使部分煤矿电网中的谐波含量已经远远超出国家标准;在自动控制、测控系统的数据采集过程中,不可避免地会有高频干扰信号混杂在有用信号当中,当这些信号的数据采集频率超过采样定理所规定的范围时,就会采集到一些不确定的信号并对有用信号造成干扰,即频率混叠。

自组网无线动态应变检测节点设计

自组网无线动态应变检测节点设计乔卿阳;王竞;张婷【摘要】本文设计了高精度自组网无线动态应变采集电路.设计采用TI公司的ZIGBEE解决方案进行无线自组网网络建立,采用恒流式电桥提高传感器的抗干扰能力和精度,并进行ADC驱动电路的分析设计,并进行现场实验.实验表明该方案具有较好的环境适应性、可维护性并具有优异的采集精度,可以满足大型复杂结构的分布式疲劳测试.【期刊名称】《船电技术》【年(卷),期】2014(034)009【总页数】5页(P61-65)【关键词】自组网;态应变;恒流式电桥【作者】乔卿阳;王竞;张婷【作者单位】武汉船用电力推进装置研究所,武汉430064;武汉船用电力推进装置研究所,武汉430064;武汉船用电力推进装置研究所,武汉430064【正文语种】中文【中图分类】TN7100 引言现代产品竞争要求产品在同样的结构下具有更好的效率、寿命、可维护性和可制造性。

静态结构和疲劳测试可以很好的为以上问题提供解决方法。

生产周期和成本控制要求急需新的测试方法来缩短测试周期和测试成本。

现代测试方法面临的挑战主要包括以下几个方面:测试点的增加、合理的测试点布局和识别、减小测试的不确定性、复杂结构测试的线缆布置和测试装置的灵活性[1]。

本文设计的高精度无线动态应变采集节点采用TI的ZIGBEE硬件解决方案进行自组网无线局域网络的组建,采用高精度Δ-Σ模数转换器辅以精密信号调理电路进行数据转换,具有自组网络、体积小、安装灵活、采集精度高的特点,能够有效解决传统采集方式的以上问题,适用于对复杂结构件进行疲劳测试的场合。

1 数据采集电路本文设计的无线动态应变采集节点包括数据采集电路和无线发射电路。

由于ZiGBEE的传输速率限制,在数据采集电路和无线发射电路之间设计数据缓冲电路进行数据的缓冲存储。

数据采集电路由电桥电路、ADC驱动电路、基准源电路和数据转换器构成。

本设计采用日本AKM 公司的 24位高性能Δ-Σ数据转换器AK5393vs进行采集电路设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ADI 实验室电路:带抗混叠滤波器的宽带接收机电路功能与优势

图1 所示电路是一款基于超低噪声差分放大器驱动器ADL5562 和16 位、250 MSPS 模数转换器AD9467 的宽带接收机前端。

三阶巴特沃兹抗混叠滤波器根据放大器和ADC 的性能与接口要求进行优化。

滤波器网络和其它组件引起的总插入损耗仅有1.8 dB。

电路整体的1 dB 通带平坦度为152 MHz,。

120 MHz 模拟输入下测得的SNR 和SFDR 分别为72.6 dBFS 和82.2 dBc。

图1. 16 位、250 MSPS 宽带接收机前端(原理示意图:未显示去耦和所有连接),增益、损耗和信号电平在10 MHz 下测量

电路描述。