第六章电子封装中至关重要的膜材料与膜技术

《薄膜物理与技术》课程教学大纲

《薄膜物理与技术》课程教学大纲课程代码:ABCL0527课程中文名称: 薄膜物理与技术课程英文名称:Thin film physics and technology课程性质:选修课程学分数:1.5课程学时数:24授课对象:新能源材料与器件专业本课程的前导课程:《材料表面与界面》、《近代物理概论》、《材料科学基础》、《固体物理》、《材料物理性能》一、课程简介本课程主要论述薄膜的制造技术与薄膜物理的基础内容。

其中系统介绍了各种成膜技术的基本原理与方法,包括蒸发镀膜、溅射镀膜、离子镀、化学气相沉积、溶液制膜技术以及膜厚的测量与监控等。

同时介绍了薄膜的形成,薄膜的结构与缺陷,薄膜的电学性质、力学性质、半导体特性、磁学性质以及超导性质等。

通过本课程的讲授,使学生在薄膜物理基础部分,懂得薄膜形成物理过程及其特征,薄膜的电磁学、光学、力学、化学等性质。

在薄膜技术部分初步掌握各种成膜技术的基本内容以及薄膜性能的检测。

二、教学基本内容和要求掌握物理、化学气相沉积法制膜技术,了解其它一些成膜技术。

学会对不同需求的薄膜,应选用不同的制膜技术。

了解各种薄膜形成的过程及其物理特性。

理解并能运用热力学界面能理论及原子聚集理论解释薄膜形成过程中的一些现象,了解薄膜结构及分析方法,理解薄膜材料的一些基本特性,为薄膜的应用打下良好的基础。

以下分章节介绍:第一章真空技术基础课程教学内容:真空的基础知识及真空的获得和测量。

课程重点、难点:真空获得的一些手段及常用的测量方法。

课程教学要求:掌握真空、平均自由程的概念,真空各种单位的换算,平均自由程、碰撞频率、碰撞频率的长度分布率的公式,高真空镀膜机的系统结构及抽气的基本过程。

理解蒸汽、理想气体的概念,余弦散射率,真空中气体的来源,机械泵、扩散泵、分子泵以及热偶真空计和电离真空计的工作原理。

了解真空的划分,气体的流动状态的划分,气体分子的速度分布,超高真空泵的工作原理。

第二章真空蒸发镀膜法课程教学内容:真空蒸发原理,蒸发源的蒸发特性及膜厚分布,蒸发源的类型,合金及化合物的蒸发,膜厚和淀积速率的测量与监控。

《薄膜材料》PPT课件

浆料印刷法形成的膜层——厚膜,前者膜厚多,厚~ 200微米

薄膜的真空沉积法优点

可以得到各种材料的膜层 镀料气化方式很多(如电子束蒸发、溅射、气体源等),控 制气氛还可以进行反应沉积

通过基板、镀料、反应气氛、沉积条件的选择,可以对界面结 构、结晶状态、膜厚等进行控制,还可制取多层膜、复合膜及 特殊界面结构的膜层等。由于膜层表面精细光洁,故便于通过 光刻制取电路图形

特别是可直接印刷电路图形。

典型的成膜方法

电镀和化学镀成膜

是依靠电场反应,使金属从金属盐溶液中析出成 膜的方法

电镀 促进电场析出的还原能量由外部电源提供

化学镀 需添加还原剂,利用自分解而成膜

电镀或化学镀成膜的特点 可对大尺寸基板大批量成膜,与其他成膜方法 相比,设备投资低 需要考虑环境保护问题

为保证金属—半导体间连接为欧姆接触,要求: 金属与半导体的结合部位不形成势垒 对于n型半导体,金属的功函数要比半导体的功函数小 对于p型半导体,与上述相反 金属与半导体结合部的空间电荷层的宽度要尽量窄,电子 直接从金属与半导体间向外迁移受到限制等

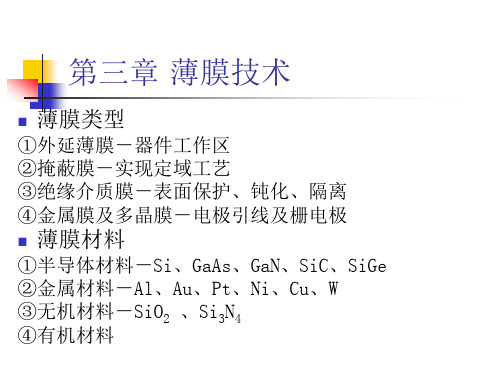

2、薄膜材料

导体薄膜材料 电阻薄膜材料 介质薄膜材料 功能薄膜材料

2、薄膜材料 导体薄膜材料

材料的种类及性质 实际情形

单一种导体不可能满足上述所有要求 构成电子电路往往需要多种导体膜的组合

2、薄膜材料 导体薄膜材料

而且 相互连接及电极中往往也不是采用单一金属,而是多种导体膜积 层化,以达到上述各种要求

多层金属组合的实例

2、薄膜材料 导体薄膜材料

从道理上讲,这种方法ຫໍສະໝຸດ 以在任何基板上沉积任何物 质的薄膜,但一般多用于氧化物、氮化物等绝缘材料 及合金材料的成膜

典型的成膜方法 CVD法

微电子封装中的薄膜技术

外围元件 互联线

Die attach

一.电子封装工程中至关重要的 膜材料及膜技术

薄膜与厚膜 膜及膜电路的功能 薄膜材料 薄膜成膜方法 厚膜材料 厚成膜方法 电路图形的成型方法

1.薄膜与厚膜

相对于三维块体材料,从一般意义上讲,所谓膜, 由于其厚度尺寸很小,可以看做是物质的二维形 态。

劣化模式是上述各种机制的组合,平均故障时间 MTF(mean time to failure)与微观的结构因子数 相关,特别是导体的长度和宽度、平均粒径与粒径 的分布、晶体学取向、晶界特性等影响很大。

导体膜劣化及可靠性

为了增加MTF,在条件允许的情况下应尽量采取

如下措施:

① 减少导体长度; ② 增加导体膜的宽度和厚度; ③ 增加膜层的平均粒度等。扩散系数 大很多。膜层中大量存在有晶界,晶界中离子的活动性与各 个晶粒的晶体的晶体学取向有关,特别是当许多晶粒的晶体 学取向不一致时,易于离子迁移。

其二,晶粒取向与外加电场之间的角度,因场所不同而 异。

其三,当传导电子从大晶粒一侧向小晶粒一侧移动时, 由于界面处也发生离子的迁移,因而引起小晶粒一侧空位的 积蓄等。

以Ti为底层的Ti-Au系,对于所有种类的基板都显 示出相当高的附着力,但在250~350℃不太高的温 度下即形成化合物,使Ti膜的特性变差,由此造成 电阻值增加。往往在Au与Ti之间加入Pt阻挡层。

导体膜劣化及可靠性

成膜后造成膜异常的主要原因有两个:

① 由于严重的热适配,存在过剩应力状态,膜层从通常的 基板或者Si、 SiO2 膜表面剥离,造成电路断线;

按膜厚对膜的经典分类认为,小于1μm的为薄膜 大于1μm的为厚膜。

按制作方法分类,由块体材料制作的,例如经轧 制、锤打、碾压等,为厚膜;而由膜的构成物

【2024版】微电子工艺之薄膜技术

二、外延掺杂及杂质再分布

3.杂质再分布

再分布:外延层中的杂质向衬底扩散;

衬底中的杂质向外延层扩散。

总杂质浓度分布:各自扩散的共同结果。

①衬底杂质的再分布(图3-21)

初始条件:N2(x,0)=Nsub,x<0; N2(x,0)=0,x>0; 边界条件一:衬底深处杂质浓度均匀,即

当vt» D1t 时,有

N1x,t

Nf 2

erfc

2

x D1t

二、外延掺杂及杂质再分布

当vt»2 D1t 时,有

N1(x,t)≈Nf

③总的杂质分布(图3-24)

N(x,t)=N1(x,t)± N2(x,t) “+”: 同一导电类型;

“-”:相反导电类型;

三、自掺杂(非故意掺杂)

1.定义

N 2 x

x 0

二、外延掺杂及杂质再分布

边Jd界条D件2 二Nx:2 在xx外f 延J层b 表J s面 (h2x=vxfN)2 ,扩x f 散,t 流密度Jd为

解得:

N2x,t

N sub 2

erfc

2

x D2 t

v h2 2h2

v

ex

p

D2

vt

x erfc

2vt x 2 D2t

①当hG» ks,则 NGS≈NG0,V= ks(NT/ NSi) Y,是表面反 应控制。

②当ks» hG,则 NGS ≈0, V= hG(NT/ NSi) Y,是质量转 移控制。

二、外延掺杂及杂质再分布

1. 掺杂原理-以SiH4-H2-PH3为例

薄厚膜技术

➢薄膜技术

薄膜技术是一种减法技术,在整个基板上覆几层金属

膜,一些不需要的部分被光刻掉。用光刻工艺形成的 图形比厚膜工艺能够形成的线条更窄、边缘更清晰。 这个特性促进了薄膜技术在高密度和高频领域的应用 薄膜技术利用热蒸镀、电子束蒸镀、溅镀、化学气相 沉积等薄膜镀着技术配合微影成像与蚀刻等技术在基 板上制成导线电路与各种电阻、电容等元件。

➢厚膜技术

厚膜技术是采用丝网印刷和烧结等工艺,将传统无

源元件(电阻、电容)及导线电路形成于散热良好 的陶瓷绝缘基板表面。 厚膜技术的基本内容是印刷和烧结。 网印是使用刮刀将导体浆料、电阻浆料和介质浆料 等刷过镂刻有电路图形的网板或金属板,以在陶瓷 基板表面形成所需的电路、电阻、电容图形,再经 过烧结或聚合完成膜与基板的粘接。 烧结技术也包括陶瓷基板的制作。

✓ 电容材料 氧化钽(Ta2O5)、氮化硅(Si3N4)

✓ 绝缘层材料 氧化硅、聚亚醯胺

光刻

在光刻工艺中,基板上涂一层光敏材料,紫外线透过在玻璃 上形成的图案对光敏材料进行曝光。不需要的材料,即没有 被光刻胶保护的部分,可以通过“湿法”(化学)刻蚀来去 除,也可以通过“干法”(溅散)刻蚀去除。

化学刻蚀仍然是薄膜刻蚀的最常用的方法,但许多制造商 用采用溅射刻蚀。在这项技术中,基板覆盖上光刻胶,与化 学刻蚀完全一样的方法露出图形。接着将基板放置于等离子 体内,加上电位。实际上,在溅散刻蚀过程中基板起靶的作 用,气体离子轰击薄膜的暴露部分除去不需要的材料。光刻 胶膜比溅散的薄膜厚很多,故它是不受影响的。

先用丝绸、尼龙或不锈钢丝编织成的网绷紧在框架上 ,再将刻有导体或电阻图形的有机膜或金属箔(称掩模 )贴到丝网上。

印刷时,将基板放在丝网下面,而将浆料放在丝网上 面,然后用橡胶或塑料制成的刮板以一定的速度和压力 在丝网上移动,使它通过掩模上的开孔图形而漏印到基 板上,于是在基板上便得到该浆料印出的所需图形。

电子工艺全部知识点总结

电子工艺全部知识点总结一、电子工艺材料与工艺工程1. 半导体材料:包括硅、砷化镓、碳化硅等。

半导体材料的选择对于半导体器件的性能有着重要的影响,工艺工程师需要根据具体的应用选择合适的半导体材料。

2. 半导体材料制备:包括晶体生长、材料加工等技术。

晶体生长技术有单晶生长、多晶生长等方法,工艺工程师需要了解各种方法的优缺点,以及应用范围。

3. 薄膜技术:包括化学气相沉积、物理气相沉积、溅射等技术。

薄膜技术在半导体器件的制备中具有重要作用,工艺工程师需要了解各种薄膜技术的原理和应用。

4. 化学成膜技术:包括电化学沉积、化学气相沉积等技术。

化学成膜技术在电子器件的制备中有着广泛的应用,工艺工程师需要了解各种化学成膜技术的工艺参数和控制方法。

5. 包装材料:包括封装树脂、封装胶粘剂等。

包装材料的选择对于电子元器件的性能和可靠性有着重要的影响,工艺工程师需要了解各种包装材料的特性和应用。

6. 其他工艺材料:包括金属材料、陶瓷材料、高分子材料等。

这些材料在电子工艺中都有着重要的应用,工艺工程师需要了解各种材料的特性和工艺应用。

7. 工艺工程流程:包括工艺设计、工艺实施、工艺改进等。

工艺工程流程是电子工艺的核心内容,工艺工程师需要了解各种工艺流程的设计原则和实施方法,以及如何通过工艺改进来提高产品的性能和可靠性。

8. 质量控制技术:包括过程控制、质量检验、可靠性测试等。

质量控制技术是电子工艺中至关重要的一环,工艺工程师需要了解如何通过过程控制和质量检验来确保产品的质量,以及如何通过可靠性测试来评估产品的寿命和可靠性。

二、半导体器件工艺1. 半导体器件概述:包括二极管、晶体管、场效应管等。

半导体器件是电子工艺中的重要组成部分,工艺工程师需要了解各种器件的结构、原理和性能。

2. 半导体器件制造流程:包括晶圆加工、器件制备、器件封装等。

半导体器件制造流程是电子工艺中的关键环节,工艺工程师需要了解各种制造工艺的原理和步骤,以及如何通过工艺优化来提高产品的性能和可靠性。

电子封装简介PPT课件

技术实力

• 本诺产品拥有自主知识产权,已申请国家基金项目及国家发明专利若干项 ,总部设立在上海;目前在日本、华东、 华南、华北、西北、东北地区设 有分支机构。

• 无论在研发, 工艺控制还是技术支持,本诺都拥有多年相关经验的博士硕士 等人才,保证本诺产品在性能上达到国际先进水平。

6

品质认证

本诺于2011年5月通过Iso9001国际标准认证,并于2011年6月开始5S现场 管理的推行,2012年9月通过Iso14001环境体系认证。本公司产品品质与 即时的专业技术支持,得以帮助我们的客户减少问题,降低成本、提高效 率。通过许多国际知名企业如京东方、中芯国际电子、富士康的供应商评 估并成为认可的策略伙伴都是本诺品质认证中的重要里程碑。

3

激情源于梦想,成功来自专注

• 企业愿景

最有竞争力的电子粘合剂品牌

• 企业精神

秉持专注,坚持创新

• 核心价值观

不惟学历重能力;不惟资历重成绩

4

核心竞争力

• 持续的研发能力 • 国际先进的生产工艺 • 多年累计的客户资源 • 灵活的客户订制服务 • 经验丰富的技术服务人员 • 开发及合成原材料的能力

41

三道光检 3rd Optical Inspection

检查Die Attach和Wire Bond之后有无各种废品

42

TSSOP/SOIC/QFP package后续工艺

EOL

Annealing 电镀退火

Trim/Form 切筋/成型

Molding 注塑

De-flash/ Plating 去溢料/电镀

15

LED 产品对比

我们的产品 8300C 8280C 8400C 9300C

《微电子与集成电路设计导论》第六章 新型微电子技术

纳电子器件——Memristor忆阻器 ➢ 全称记忆电阻(Memristor),是表示磁通与电荷关系的电路器件。

特点

➢ 电阻取决于多少电荷经过了器件。 ➢ 若电荷以一个方向流过,电阻会增加;

如果让电荷以反向流动,电阻就会减小。 ➢ 具有记忆能力,断电后电阻值保持不变。

纳电子器件——石墨烯

➢ 它是已知材料中最薄的一种,且牢固坚硬; ➢ 优良的导电特性:它在室温下传递电子的速度比已知导体都快。

优势

➢ 碳纳米管FET沟道为一维结构,载流子 迁移率大大提高。

➢ 碳纳米管FET参与碳纳米管导电的是表 面。

➢ 碳纳米管FET通过选择源漏材料,可完 全消除源漏结势垒

图6.4.2 CNT-FET典型结构示意图

纳电子器件——有机分子场效应晶体管

该技术利用了分子之间可自由组合的化学特性,晶体管电极之间的距离仅为1纳米到2 个纳米,是目前世界最小的晶体管。同时具有制造简单,造价低廉的优点。

2006年3月, 佐治亚理工学院 (Georgia Institute of Technology) 的研究 员宣布,成功地制造了石墨烯平面场效应 晶体管并观测到了量子干涉效应。并基于 此研究出根据石墨烯为基础的电路。

6.4.2 纳电子材料

纳米材料一诞生,即以其异乎寻常的特性引起了材料界的广泛关注。这 是因为纳米材料具有与传统材料明显不同的一些特征。

人类社会是在不断征服自然和不断攀登科技顶 峰而前进的,纳米技术也是如此。

现在世纪纳米技术和纳米材料,正向新材料、 微电子、计算机、医学、航天、航空、环境、 能源、生物技术和农业等诸多领域渗透。

纳米打假

纳米技术并非高不可攀,但也决非人人都能“纳”一把, 因此,我们要提前做好纳米技术的打假工作,建立一套十分 严格的评审和考核制度,为纳米技术的发展创造良好的空间, 防止样样都要“纳”一把现象的发生,尽量避免恶意炒作 “伪纳米”,不能等到造成极其严重的恶果后,再去打与堵。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

6.3 膜及膜电路的功能

对于电子封装工程来讲,膜及膜电路主要有以下四 大功能: 电气连接 元件搭载 特殊功能 表面改性

电气连接

印制线路板(PWB)的发明,使电路以膜的形式 与基板作成一体,元器件搭载在基板上并与导体端子相 连接,这对于整个系统的小型化、高性能、低功耗、高 可靠性及经济性等方面都有重大贡献。

填平法

光刻胶图形的形成 光刻胶

成膜 基板 成膜材料

光刻胶剥离 填平法的原理与工艺过程

蚀刻法

化学蚀刻法是在基板的全表面上印刷电路图形材 料的浆料,经烧成后,涂布光刻胶,再通过电路图形 掩模曝光后,用化学蚀刻的方法去除部分光刻胶,然 后通过有机洛剂将电路图形不对应部分的电极材料去 除掉。

薄膜光刻法是用磁控溅射、真空蒸镀等先在整个 基板表面形成电路材料的薄膜,再经光刻制取电路图 形。用这种方法可以获得精细度很高的图形,而且所 形成膜层的质量高,膜厚可精确控制。

6.4 电路图形的形成方法

应用于电子工业的膜层,例如电子元器件制造、电子封 装、平板显示器等,都需要形成电路图形。电路图形的 形成方法很多,主要有: 填平法 蚀刻法 掩模法 厚膜印刷(丝网印刷)法 喷沙法

填平法

先将光刻胶涂敷(甩胶)或将光刻胶干膜贴附 (贴膜)于基板表面,经光刻形成“负”的电路图形, 即没有电路的部分保留光刻胶。以此负图形为“模 型”,在其槽中印入导电浆料或沉积金属膜层,即所 谓“填干”。最后将残留的光刻胶剥离。这种方法缺 点是,采用印刷法填干时,导电胶膜中容易混入气泡。

LCD中TFT玻璃复合基板中特殊功能膜的作用

表面改性

如同在LSI元件表面沉积SiO2、Si3N4等钝化膜用于 绝缘、保护一样,在电子封装工程中也广泛用膜层作表 面改性。例如金属被釉基板、有机或无机绝缘层包覆的 金属芯基板等。又如,在塑料表面电镀金属以增加耐磨 性、降低接触电阻等,常用的方法有镀铑、镀金等。

6.2 薄膜和厚膜

在晶体管普及之前,真空电子管的板极、栅 极、灯丝等都由块体村料构成,电子管插在管座 上由导管连接,当时并无膜可言;20世纪60年代, 人们开始在纸、塑料、陶瓷上涂刷乃至真空蒸镀、 溅射金属膜,用以形成小型元器件及电路等。进 入晶体管时代,从半导体元件、微小型电路到大 规模集成电路,膜技术便成为整套工艺中 的核心与关键。

广义的电子封装工程应该是狭义的封装与实装工 程及基板技术的总和。将半导体、电子器件所具有的 电子的、物理的功能,转变为适用于机器或系统的形 式,并使之为人类杜士服务的科学与技术,统称为电 子封装工程。

按特征尺寸的量级,电子封装工程中的四个层次

电子封装中的制膜工程

电子封装工程中采用的膜分薄膜和厚膜两大类,前 者一般由溅射、真空蒸镀、CVD等方法制作,后者主要 采用丝网印刷法制作。此外还有喷涂、电镀、浆料喷射、 直接描画、LB法等各种不同的方法。从膜的功能讲,有 电阻、导体、绝缘、介电、保护以卫各种特殊的功能膜 等;从膜的村料讲,有金属、合金、氧化物、玻璃、陶 瓷、聚合物、半导体、非晶态等;此外,对膜层的尺寸、 形态、结构等也都有特殊的要求。

厚膜印刷法

丝网制版 丝网

乳胶膜 印刷 浆料

浆料

烧成

基板 浆料

基板

厚膜印刷法的原理与工艺过程

喷沙法

先在基板全表面由电路图形材料成膜,再在表面形 成光刻胶图形,经喷沙去除掉不需要的村料部分,保留 光刻胶图形覆盖的部分,剥离光刻胶后得到所需要的电 路图形。喷沙法采用光刻制版技术,能形成精细的电路 图形,但在喷沙过程中会产生灰尘。

就电子封装工程所涉及的膜层而论,膜厚一 般在1µm到数百微米之间,按膜层的形成方法, 将真空法(干式)和溶液法(湿式)沉积得到的 膜层称为薄膜,由浆料印刷法形成的膜层称为厚 膜,前者膜厚多为数微米,后者膜厚多为20µm上 下。

无论薄膜还是厚膜,采用不同的方法均可以 形成导体膜、电阻膜、介电质膜、保护膜及各种 各样的功能膜等。

掩模法

掩模定位Βιβλιοθήκη 掩模基板 溅射(蒸镀)成膜材料 去除掩模

掩模法的原理与工艺过程

厚膜印刷法

厚膜印刷法是通过网版在基板表面印刷厚膜导体浆 料,形成与网版对应的图形,经烧成法形成电路图形。 由于浆料仅印刷在需要的部位,因此材料的利用率高。 印刷机的价格较低,也可以降低设备总投资。厚膜印刷 法的缺点是线条精细度差,图形分辨率低,多次印刷难 以保持图形的一致性。

元件搭载

芯片装载在封装基板上,无论采用引线键合方式还 是倒装片方式都离不开焊盘;元器件搭载在基板上,特 别是LSI封装体实装在基板上,无论采用DIP、SMT、 COX.MCM等哪种方式,都离不开导体端子。

BGA、QFP两种封装形式引脚端子数与实装面积的对比

特殊功能

这里的所谓特殊功能泛指除电气连接、元件搭载、 表面改性以外的所有其他功能,其中电阻膜、绝缘膜、 介电质膜在电子封装中屡见不鲜。

第六章 电子封装中至关重要 的膜材料与膜技术

本章主要内容

6.1 电子封装工程的简单介绍 6.2 薄膜和厚膜 6.3 膜及膜电路的功能 6.4 电路图形的形成方法 6.5 电子封装工程中用到的薄膜材料

6.1 电子封装工程的简单介绍

电子封装的发展过程

狭义的封装主要是在后工程中完成,并可定义为: 利用膜技术及微细连接技术,将半导体元器件及其他 构成要素在框架或基板上布置、固定及连接,引出接 线端子,并通过可塑性绝缘介质灌封固定,构成整体 立体结构的工艺。

蚀刻法

化学蚀刻法的缺点有两个,一是使用有机洛剂,废液 处理比较困难;二是有时线条会出现残差(残留)。

薄膜光刻法的缺点是,设备投资大,而且工艺不容易 掌握。

蚀刻法

基板全表面成膜 成膜材料

基板 光刻胶图形的形成 光刻胶

蚀刻

光刻胶剥离

蚀刻法的原理与工艺过程

蚀刻法

化学烛刻法可能出现的线条残留

掩模法

先用机械或光刻等方法制作“正”的掩模,将掩 模按需要的电路图形位置定位,再由真空蒸镀等方法 成膜。借助“正”的掩模,基板表面即可形成所需要 的电路图形。这种方法的优点是工序少、电路图形精 细度高。缺点是需要预先制作掩模,而且有些薄膜沉 积技术,如溅射镀膜、离子镀等,不便于掩模沉积。