电子封装的跌落可靠性

电子封装中的可靠性问题

电子封装中的可靠性问题电子器件是一个较复杂的系统,其封装过程的缺陷和失效也是比较复杂的。

因此,研究封装缺陷和失效需要对封装过程有一个系统性的了解,这样才能从多个角度去分析缺陷产生的原因。

封装的失效机理可以分为两类:过应力和磨损。

过应力失效往往是瞬时的、灾难性的;磨损失效是长期的累积损坏,往往首先表示为性能退化,接着才是器件失效。

失效的负载类型又可以分为机械、热、电气、辐射和化学负载等。

影响封装缺陷和失效的因素是多种多样的,材料成分和属性、封装设计、环境条件和工艺参数等都会有所影响。

确定影响因素和预防封装缺陷和失效的基本前提。

影响因素可以通过试验或者模拟仿真的方法来确定,一般多采用物理模型法和数值参数法。

对于较复杂的缺陷和失效机理,常常采用试差法确定关键的影响因素,但是这个方法需要较长的试验时间和设备修正,效率低、花费高。

在分析失效机理的过程中,采用鱼骨图(因果图)展示影响因素是行业通用的方法。

鱼骨图可以说明复杂的原因及影响因素和封装缺陷之间的关系,也可以区分多种原因并将其分门别类。

生产应用中,有一类鱼骨图被称为6Ms:从机器、方法、材料、量度、人力和自然力等六个维度分析影响因素。

这一张图所示的是展示塑封芯片分层原因的鱼骨图,从设计、工艺、环境和材料四个方面进行了分析。

通过鱼骨图,清晰地展现了所有的影响因素,为失效分析奠定了良好基础。

引发失效的负载类型01机械载荷包括物理冲击、振动、填充颗粒在硅芯片上施加的应力(如收缩应力)和惯性力(如宇宙飞船的巨大加速度)等。

材料对这些载荷的响应可能表现为弹性形变、塑性形变、翘曲、脆性或柔性断裂、界面分层、疲劳裂缝产生和扩展、蠕变以及蠕变开裂等等。

02热载荷包括芯片黏结剂固化时的高温、引线键合前的预加热、成型工艺、后固化、邻近元器件的再加工、浸焊、气相焊接和回流焊接等等。

外部热载荷会使材料因热膨胀而发生尺寸变化,同时也会改变蠕变速率等物理属性。

如发生热膨胀系数失配(CTE失配)进而引发局部应力,并最终导致封装结构失效。

微电子封装中的可靠性设计与优化研究

微电子封装中的可靠性设计与优化研究微电子封装是现代电子技术中重要的环节,可靠性是该领域研究的关键问题。

本文将从可靠性设计与优化的角度出发,探讨微电子封装中的可靠性问题,并提出相应的研究方向和优化策略。

一、微电子封装中的可靠性问题微电子封装是将微电子芯片、集成电路与外部介质进行物理连接和保护的过程。

在封装过程中,由于温度、湿度、机械应力等外部环境因素的影响,以及封装材料的特性限制,微电子封装可能存在以下可靠性问题:1. 焊接可靠性:封装过程中,焊接是连接芯片和外部引脚的重要方式。

焊点的质量直接影响到整个封装的可靠性。

焊点可能出现冷焊、开裂、疏松等问题,从而引起芯片与引脚的断裂,甚至导致器件失效。

2. 热传导问题:微电子封装中,芯片产生的大量热量需要通过封装材料传导和散热。

若散热不良,会导致芯片温度过高,降低器件的可靠性和寿命。

3. 封装材料的降解:封装材料因长期暴露在恶劣环境下,可能会出现老化、腐蚀、电学性能下降等问题,进而影响封装的可靠性和性能。

4. 微结构效应:微电子封装中,芯片和封装材料之间存在微结构效应,如针对封装材料的热膨胀系数不匹配,可能引起应力集中,导致微裂纹的产生和扩展,最终导致器件失效。

二、可靠性设计与优化的研究方向针对微电子封装中的可靠性问题,需要进行可靠性设计与优化的研究。

以下是几个研究方向的介绍:1. 封装材料的选择与设计:选择合适的封装材料对于提高微电子封装的可靠性至关重要。

研究人员需要综合考虑材料的热导率、机械强度、阻尼特性等因素,设计出能够满足封装要求并具备良好可靠性的材料。

2. 计算机辅助工程与模拟仿真:借助计算机辅助工程软件和模拟仿真技术,可以对微电子封装进行虚拟建模和仿真分析。

通过分析封装过程中的热传导、应力分布等问题,提前发现潜在的可靠性问题,并采取相应措施进行改进。

3. 焊接工艺的优化:焊接是微电子封装过程中容易产生可靠性问题的环节之一。

优化焊接工艺参数,控制熔化焊料的温度、时间、流动性等因素,能够降低焊接过程中的应力和热应变,提高焊接的可靠性。

封装可靠性失效原因及其改善方案阐述

封装可靠性失效原因及其改善方案阐述长电科技(滁州)有限公司安徽省滁州市 239000 摘要:可靠性是产品质量的一个重要指标,就是产品在规定的条件下和规定的时间内,完成规定的功能的能力。

确切的讲,一个产品的使用寿命越接近设计寿命,代表可靠性越好。

1、产品的可靠性与规定的条件密切相关。

如产品使用的环境条件、负荷大小、使用方法等。

一般,温度越高、额定负载越大,产品的可靠性就越低。

2、产品的可靠性与规定的时间也有关系。

例如,一般大型桥梁、道路的设计寿命为50~100年。

3、产品的可靠性还与规定的功能有密切的关系。

例如,一个普通的晶体管有反向漏电流、放大倍数、反向击穿电压、特征频率等多项功能。

芯片封装质量直接影响整个器件和组件的性能,随着混合集成电路向着高性能、高密度以及小型化、低成本的方向发展,对芯片的封装技术和可靠性提出了更高的要求。

本文主要阐述了几种可靠性项目及其失效的机理以及封装导致的原因,以便封装生产中规避此类异常发生。

关键字可靠性;质量;可靠性项目;失效机理;封装导致的原因。

背景描述:电子器件是一个非常复杂的系统,其封装过程的缺陷和失效也是非常复杂的。

因此,研究封装缺陷和失效需要对封装过程有一个系统性的了解,这样才能从多个角度去分析缺陷产生的原因。

封装的失效机理可以分为两类:过应力和磨损。

过应力失效往往是瞬时的、灾难性的;磨损失效是长期的累积损坏,往往首先表示为性能退化,接着才是器件失效。

失效的负载类型又可以分为机械、热、电气、辐射和化学负载等。

影响封装缺陷和失效的因素是多种多样的,材料成分和属性、封装设计、环境条件和工艺参数等都会有所影响。

封装缺陷主要包括引线变形、底座偏移、翘曲、芯片破裂、分层、空洞、不均匀封装、毛边、外来颗粒和不完全固化等。

随着应用的要求越来越高,对产品封装可靠性要求也越来越高。

我们要识别一些可靠性项目考核目的、失效机理以及可能导致的原因,以便在前期FMEA中定义,从设计、生产角度来提升质量。

封装工艺对电子元件可靠性的影响

封装工艺对电子元件可靠性的影响封装工艺,这四个字听起来好像有点高大上,让人摸不着头脑,但其实它就在我们的日常生活中,而且对电子元件的可靠性有着至关重要的影响。

我先给您讲讲我自己的一个经历。

有一次,我家里的一台旧电脑突然出了毛病,总是死机,可把我急坏了。

我找了个懂行的朋友来帮忙看看,他打开机箱,检查了一番后告诉我,问题出在一个电子元件上,那个元件的封装工艺不过关,导致在使用过程中受到了一些细微的损伤,最终影响了整个电脑的运行。

这就让我很好奇了,这封装工艺到底是个啥?为啥能有这么大的威力?简单来说,封装工艺就像是给电子元件穿上一件“防护服”。

您想想,电子元件那么小,那么精密,在复杂的使用环境中,很容易受到各种外界因素的影响,比如温度的变化、湿度的高低、灰尘的侵袭等等。

而封装工艺呢,就是要保护这些娇贵的“小家伙”,让它们能够稳定地工作。

好的封装工艺可以有效地防止电子元件受到物理损伤。

就像给一个易碎的宝贝外面包上一层厚厚的海绵,不管怎么碰撞,里面的东西都能安然无恙。

而且,它还能阻挡湿气和灰尘的侵入。

您知道的,湿气会让元件生锈,灰尘多了可能会导致短路,这些可都不是闹着玩的。

另外,封装工艺对散热也很重要。

电子元件在工作的时候会发热,如果热量散不出去,温度过高,那性能就会下降,甚至直接坏掉。

好的封装就像是给元件装了一台高效的“空调”,能迅速把热量带走,让它们始终在舒适的温度下工作。

比如说,在手机里的芯片,它们的封装工艺就极其讲究。

现在的手机越做越薄,功能却越来越强大,这就要求芯片不仅性能要好,封装也得跟上。

要是封装不好,手机用一会儿就发烫,电量消耗得飞快,那谁还愿意用啊?再比如汽车里的电子控制单元,要经受各种恶劣的路况和环境,高温、低温、震动等等,如果封装不过关,那汽车可能随时会出故障,这可不是开玩笑的!还有在医疗设备中的电子元件,那更是要求严格。

毕竟这关系到人的生命健康,一点都马虎不得。

所以说,封装工艺真的是太重要了。

电子元器件的封装技术高密度和高可靠性的发展

电子元器件的封装技术高密度和高可靠性的发展随着电子科技行业的迅速发展,电子元器件在现代社会中扮演着重要的角色。

而电子元器件的封装技术则是保证电子设备正常运作的重要一环。

本文将探讨电子元器件的封装技术在高密度和高可靠性方面的发展。

一、电子元器件封装技术的发展概述电子元器件封装技术是指将电子器件连接、保护和隔离在一定的材料中,以确保其正常工作,并适应特定的使用环境。

它直接关系到电子设备的性能、可靠性和寿命。

随着科技的进步,电子元器件越来越小型化,对封装技术提出了更高的要求。

传统的封装技术已经不能满足高密度和高可靠性的需求,因此需要不断发展新的封装技术,以适应电子行业的快速发展。

二、高密度封装技术的发展高密度封装技术是指在有限的空间内尽可能多地集成更多的电子元器件。

它旨在提高电子设备的集成度和性能。

在高密度封装技术的发展过程中,主要有以下几种技术:1. 表面贴装技术(SMT)表面贴装技术是一种常见的高密度封装技术。

它通过将电子元器件直接粘贴到印刷电路板(PCB)上,并通过焊接连接,实现电子元器件的封装。

SMT技术具有封装密度高、尺寸小、可靠性高等优点,被广泛应用于电子产品中。

2. 超高密度封装技术(HDI)超高密度封装技术是一种将更多的电子元器件集成在更小的尺寸中的技术。

它采用先进的印制电路板工艺,如多层堆叠和微孔装配技术,以实现更高的集成度。

HDI技术广泛应用于移动通信、计算机和消费电子等领域,推动了电子产品的小型化和轻量化。

三、高可靠性封装技术的发展高可靠性封装技术是指电子元器件在复杂的使用环境下能够保持长期稳定可靠性的技术。

它涉及到材料的选择、封装工艺的优化和可靠性测试等方面。

1. 高可靠性材料的研发高可靠性封装技术离不开高可靠性材料的支撑。

近年来,随着新材料和新工艺的不断涌现,越来越多的高可靠性材料被应用于电子元器件的封装中。

例如,高温耐受材料、高精度封装材料和防腐蚀材料等,都为高可靠性封装提供了有力支持。

系统级封装的可靠性与失效分析技术研究

系统级封装的可靠性与失效分析技术研究一、概述随着微电子技术的快速发展,系统级封装(SiP,SysteminPackage)技术已经成为当今集成电路产业的重要发展方向。

SiP技术通过将多个具有不同功能或工艺的芯片及无源元件集成在一个封装体内,实现了系统功能的高度集成化和小型化,从而提高了产品的性能和可靠性。

随着封装密度的不断提高和工艺复杂性的增加,SiP技术的可靠性问题也日益凸显,失效分析技术的研究变得尤为重要。

系统级封装的可靠性主要受到封装材料、工艺、结构以及使用环境等多种因素的影响。

在封装材料方面,不同的材料具有不同的热膨胀系数、机械强度以及化学稳定性,这些差异可能导致封装体在温度变化、机械应力或化学腐蚀等条件下出现失效。

在工艺方面,封装过程中的焊接、封装胶填充等工艺环节可能引入缺陷,导致封装体的性能下降或失效。

封装体的结构设计和使用环境也是影响其可靠性的重要因素。

失效分析技术是研究和解决系统级封装可靠性问题的关键手段。

通过对失效封装体进行详细的物理和化学分析,可以确定失效的原因和机理,为改进封装工艺、优化结构设计以及提高产品可靠性提供重要依据。

目前,失效分析技术主要包括非破坏性分析和破坏性分析两大类。

非破坏性分析技术如射线检测、红外热成像等,可以在不破坏封装体的情况下检测其内部结构和性能。

而破坏性分析技术如开封、切片等,则需要通过破坏封装体来观察和分析其内部结构和失效模式。

本文旨在深入研究系统级封装的可靠性与失效分析技术,通过分析封装体的失效原因和机理,提出有效的可靠性提升方案和失效预防措施,为SiP技术的发展和应用提供有力支持。

1. 系统级封装技术的发展背景与现状随着信息技术的快速发展,电子产品正朝着小型化、集成化、高性能化的方向不断演进。

在这一背景下,系统级封装技术应运而生,成为推动电子产品发展的关键性技术之一。

系统级封装技术是指在单一封装结构内部,将多个裸芯片、元件或组件集成于一体,从而实现电子产品完整的系统或子系统功能。

半导体的封装可靠性测试

半导体的封装可靠性测试在当今科技高速发展的时代,半导体已经成为了各种电子设备的核心组件。

从智能手机到电脑,从汽车到航天飞机,半导体无处不在。

而半导体的封装可靠性测试则是确保这些半导体器件能够稳定、可靠运行的关键环节。

半导体封装,简单来说,就是将制造好的半导体芯片保护起来,并提供电气连接和机械支撑的过程。

就好像给一颗珍贵的“芯”穿上一件坚固而合身的“防护服”,让它能在复杂的电子世界中正常工作。

那么,为什么要进行封装可靠性测试呢?想象一下,如果半导体封装不可靠,芯片就可能会受到外界环境的影响,比如潮湿、高温、震动等,从而导致性能下降、甚至失效。

这不仅会影响到单个电子设备的正常使用,还可能在一些关键领域,如医疗、航空航天等,带来严重的后果。

所以,封装可靠性测试的重要性不言而喻。

封装可靠性测试包括多个方面,其中常见的有热循环测试、热冲击测试、湿度敏感测试、机械冲击测试等。

热循环测试模拟了半导体器件在不同温度环境下的工作情况。

在实际应用中,电子设备可能会经历从极寒的环境到高温的环境,比如从寒冷的户外进入温暖的室内。

这个测试就是要看看封装后的半导体能否经受住这样的温度变化。

测试时,将样品反复置于高温和低温之间,观察是否会出现封装材料的开裂、分层,以及芯片与封装之间的连接是否良好。

热冲击测试则更加剧烈和快速地改变温度,以检验半导体封装在极端温度变化下的耐受性。

这就像是把半导体器件瞬间从“冰窖”扔到“火炉”,然后再迅速扔回来。

湿度敏感测试针对的是半导体封装在潮湿环境下的可靠性。

因为在一些潮湿的地区或者特定的应用场景中,湿气可能会渗透到封装内部,导致腐蚀、短路等问题。

机械冲击测试则模拟了半导体器件在受到外力冲击时的情况,比如设备掉落、碰撞等。

这是为了确保封装能够保护芯片在这些意外情况下不受损坏。

在进行这些测试时,需要使用专门的测试设备和仪器。

这些设备能够精确地控制温度、湿度、冲击力等参数,以保证测试结果的准确性和可靠性。

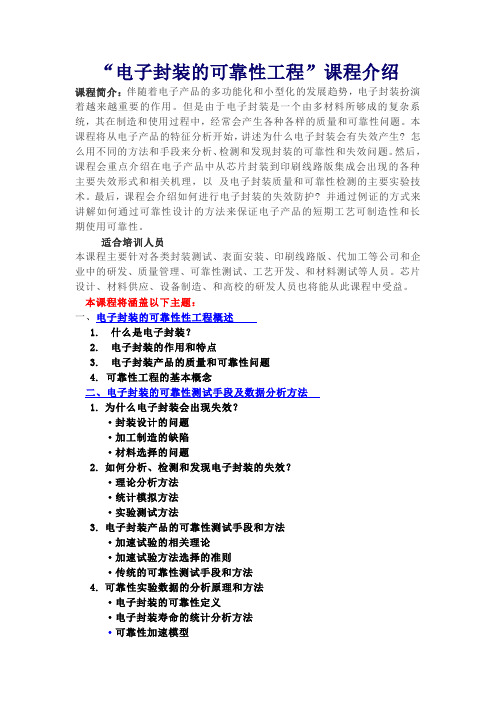

电子封装的可靠性工程

“电子封装的可靠性工程”课程介绍课程简介:伴随着电子产品的多功能化和小型化的发展趋势,电子封装扮演着越来越重要的作用。

但是由于电子封装是一个由多材料所够成的复杂系统,其在制造和使用过程中,经常会产生各种各样的质量和可靠性问题。

本课程将从电子产品的特征分析开始,讲述为什么电子封装会有失效产生? 怎么用不同的方法和手段来分析、检测和发现封装的可靠性和失效问题。

然后,课程会重点介绍在电子产品中从芯片封装到印刷线路版集成会出现的各种主要失效形式和相关机理,以及电子封装质量和可靠性检测的主要实验技术。

最后,课程会介绍如何进行电子封装的失效防护? 并通过例证的方式来讲解如何通过可靠性设计的方法来保证电子产品的短期工艺可制造性和长期使用可靠性。

适合培训人员本课程主要针对各类封装测试、表面安装、印刷线路版、代加工等公司和企业中的研发、质量管理、可靠性测试、工艺开发、和材料测试等人员。

芯片设计、材料供应、设备制造、和高校的研发人员也将能从此课程中受益。

本课程将涵盖以下主题:一、电子封装的可靠性性工程概述1. 什么是电子封装?2. 电子封装的作用和特点3. 电子封装产品的质量和可靠性问题4. 可靠性工程的基本概念二、电子封装的可靠性测试手段及数据分析方法1.为什么电子封装会出现失效?·封装设计的问题·加工制造的缺陷·材料选择的问题2.如何分析、检测和发现电子封装的失效?·理论分析方法·统计模拟方法·实验测试方法3.电子封装产品的可靠性测试手段和方法·加速试验的相关理论·加速试验方法选择的准则·传统的可靠性测试手段和方法4.可靠性实验数据的分析原理和方法·电子封装的可靠性定义·电子封装寿命的统计分析方法·可靠性加速模型三、电子封装产品的失效类型、特征和机理1.电子封装的失效类型、特征和机理概述2.电子元器件及其封装的主要失效类型、特征和机理·表面安装电子元器件的失效类型、特征和机理·脆性断裂特征和机理·爆米花失效特征和机理·引脚开裂失效特征和机理·塑封层失效特征和机理·非半导体器件的失效特征和机理·静电失效特征和机理3. 电子封装中内联接的主要失效类型、特征和机理·焊锡接点的缺陷·焊锡接点的疲劳失效·焊锡接点的蠕变失效·焊锡接点的晶须生长失效和机理·内联接的晶间化合物生长失效和机理·内联接的腐蚀失效和机理·内联接的电迁徙失效和机理4.印刷线路版的主要失效类型、特征和机理·材料相关的失效和机理·界面开裂失效和机理·信号/电源联接相关的缺陷、失效和机理·印刷线路版中穿孔相关的失效和机理四、关键的失效分析实验技术1.失效分析实验技术概述2.关键的缺陷检测技术·光学检测技术·X射线检测技术·声检测技术3.关键的微结构分析技术·冶金显微镜·电子扫描显微镜·X射线衍射仪4.关键的热性能分析技术·微分扫描热量仪·热机械分析仪·热重力分析仪5.关键的封装结构分析技术·投影云纹仪·云纹干涉仪·数字相关分析仪6.小结五、电子封装产品的失效防护与可靠性设计1.失效防护与可靠性设计的基本概念2.什么是电子封装产品的可靠性设计?3.热-机械失效问题的防护和可靠性设计方法4.电失效问题的防护和可靠性设计方法5.化学失效问题的防护和可靠性设计方法6.计算机辅助的虚拟可靠性设计方法7.有限元 (FEM) 分析方法概述8.例子1 –焊锡接点的失效防护和可靠性设计9.例子2 --双材料界面的失效防护和可靠性设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Fig. 14. Plastic strain concentration area on the critical corner bump

(a) the 3D component without resin, (b) the 3D component with resin1, and (c) the 3D component with resin2.

的金属间化合物界面层

芯片级封装的表面处理剂与焊球对基于JEDEC标准的跌落可靠性的影响

• 回流焊过程:生成IMC薄层 厚,脆;薄了,结合不好

在使用及跌落试验中,薄层会逐渐变厚 ---------取决于:表面处理剂,基板,焊料 • 表面处理剂: electroplated Nickel/Gold (Ni/Au) 电镀镍/金 Electroless nickel electroless palladium immersion gold (ENEPIG)化学镀Ni+浸Au化学镀Pd(钯) 实验用: • 焊料:三种SAC-- The tin–silver–copper 锡银铜合金

最好的情况: B2F结构,TSV下非焊球,有着 最好的抗跌落性。

• 为增加机械抗性,加入环氧树脂。

• 研究其保护作用: 两种,resin1的弹性模量是resin2三倍

局部模型,看到包裹着焊球的树脂最底部 对四种情况,F2F,B2F与TSV ,TSV+NO组合进行模拟,定性定

量比较

Fig. 13. Protect resin position.

5;resin1,中心位置有失效危险;resin2,PCB板面的焊点有更大 的危险

6;使用低杨氏模量环氧树脂,最大塑性形变会变低 7;B2F设计有着更可靠的抗冲击性,

最好搭配:B2F+No bump under TSVs+resin2

3. 不考虑焊点回流残余应力

4. 加载时间分两步:一是drop过程,二是 精确的瞬态动态分析

5. 20ms的阻尼过程,准静态分析,以消除 PCB板上的崩散效应

6. 接触的地方都有着关联约束

7. 材料性质为弹性,SAC105焊料合金的 三线性弹塑性行为以内插值法在图中显 示,铜为双线性,多晶硅认为是弹性正 交的。

• ABAQUS软件--有限元模拟 • 比较了两种设计下的行为: • F2F(face to face),B2F(back to face)

在不同 TSV通孔位置与成型树脂的机械性能。

• 可靠性评判标准:关键的焊凸点上的最大剪切塑性应变。

注意:Die1与die2

SAC105:49个(7×7)

49个SAC105焊点,

板级跌落试验条件

8级别分别对应不同的使用环境或者加速因子;

JESD22-B110

跌落产生冲击载荷:

1. 以惯性力形式直接作用于焊点

2. 另一方面能量转化为印刷电路板动能,使印刷电路板往复弯曲振动, 而印刷电路板刚度与元器件刚度不同,弯曲振动过程焊料微互连承受

一定应力应变作用。

互连失效机理:

• 沿着焊料焊盘界面层的脆性断裂,这过程与焊料硬化有关。 • 跌落过程焊料应变率高,会使焊料发生硬化,以至于裂纹发生在脆性

• 16图:F2F的,没有树脂,应变更小,但不代表更可靠。 因为应变集中在IMC层附近,更易引发最初的裂纹。树脂 的添加并不影响TSV通孔对应变的影响--对1,2都是TSV下 无焊点时应变最小,resin2的塑性应变是resin1时的一半 。最好:TSV下无焊点结构加resin2.

• 17图:B2F,resin2应变最小。同上

冲击能被塑性好的树脂及焊点吸收。 其应变更为明显

关键区域应变大小对比柱状图

Fig. 16. Molding resin’s effects on the F2F components.

Fig. 17. Molding resin’s effects on the B2F components.

上两图分析

(a) ENEPIG + SAC125Sb versus Ni/Au + SAC125Sb

韦伯分布图

(b) ENEPIG + SAC125NiSb versus Ni/Au + SAC125NiSb

(c) ENEPIG + SAC105Pt versus Ni/Au + SAC105Pt

失效模式分析

无铅回流焊工艺

JESD22-B104-B

Fig. 3. Schematic of a drop tower

Fig. 4. Acceleration versus time.

施加到线板的激励脉冲是加速度峰值1500g,延续时间0.5ms的半正弦脉冲。

莲须300次坠落试验或者到所有封装皆失效为止

焊料,表面处理剂成分图

• 比较两个最好情况,发现: B2F:1.62%,F2F:2.78%。

• --最佳结构:B2F结构TSV下无焊点,填充resin2树脂。

结论:

1;杨氏模量测量20%误差都可以不考虑的

2;高危险失效区在中心位置焊球处

3;无树脂填充时,关键区域在临近IMC层的芯片一边

4;No bump under TSVs比有更优异

SAC125Sb, SAC125NiSb, SAC105Pt • 封装: thin-profile fine-pitch ball grid array (TFBGA)

细间距球栅阵列

JESD22-B111

测试板:15个TFBGAs 每个:280个焊点

测试板材料: 0.28mm铜垫 -OSP(有机保焊膜) -0.43mm防焊漆 Sn3.0Ag0.5Cu (SAC305)—焊膏。

Fig. 8. PCB bending during drop test. 硅片Die刚性

纳米压痕,通过微为悬臂梁弯曲观测-----弹性模量测试

对于USG,Si,Cu: 应变对弹性模量变化不敏感

对IMC,Al: 有极小幅变化,忽略不计, 即百分之二十误差不影响焊 点应变

对SAC合金:从1.43%1.48%变化 因此需要高精度的弹性模量 测量系统

下面为对比实验,杨氏模量 误差不影响结果对比

两种硅通孔对比图

no bump under TSV

bumps under TSV

Critical bump maximum plastic strain

(a) F2F, bumps under TSVs, (b) F2F , no bumps under TSVs, (c) B2F, bumps under TSVs, (d) B2F, no bumps under TSVs critical region:接近金属间化合物层--坚硬脆性。裂纹产生于此并传播到焊球内引起微互 连失效。

A 0=1500G,tw=1ms

Fig. 4. Drop impact shock input acceleration.

全局建模结果作为局部分析的边界条件

Fig. 5. SAC105 elasto-plastic behavior

• 几种假设:

1. 仅分析了PCB板中心处C2W部件

2. 再分配层也考虑了,假设它会对板级的 机械可靠性有一点影响

Fig. 15. The shear strain of the solder bump and the molding resin;

(a) the 3D component with resin1, resin1相对刚性,略微变形

(b) the 3D component with resin2.

电子封装的跌落可靠性

drop-test

可靠性试验加载方式

循环载荷

热机械 循环弯曲、震动

动态机械载荷

跌落、弯曲、剪切、拉伸、冲击

电化学

温度、湿度、电压

手持电子产品的可靠性要求

动态机械可靠性

动态机械载荷

便携跌落危险 新功能(游戏、短信)键盘、按键的疲劳和弯曲 重量减轻紧凑包封机械保护 叠层封装封装体质量,总体尺寸 小型化互连尺度危险性(失效几率)

• 智能手机,数码相机,平板电脑

轻、巧、薄、便携性。使用环境比一般固定产品更复杂恶劣

• 跌落、撞击意外事件。

--要求良好的抗冲击性

跌落试验分类

• 产品级跌落:

• 复杂不可控,不可重复性,因为跌落与很多因 素相关,如产品设计,跌落方位,产品尺寸材 料等。

• 板级跌落:

可控性好,实验简单

可靠性测试标准

动态机械载荷下的可靠性非常重要

跌落、拉伸、剪切、弯曲、冲击和振动 焊点:

脆性断裂--对应力集中更为敏感 影响因素:金属间化合物(IMC)、润湿性、…

PCB: 绝缘层/铜线裂开 封装:焊球、焊点大小

研究意义

• 工作环境越来越恶劣

承受载荷越来越苛刻,几百个重力加速度的冲击载荷很常见。

• 美国电子工业协会(Electronic Industries Alliance) • EIA 的JESD标准:

测试用电路板的尺寸、元器件的布局、加载速度、跌落条件及测试步 骤做出了详细的规定

• JESD22-B110A JESD22-B111

分别指导电子部件冲击测试与手持类电子产品板级跌落测试

板级跌落试验设备250um,

长100um,厚4um的多晶硅 通道作为垂直连接,F2F中 铜骨架连接片1与片2。

有限元建模

几何对称,仅考虑1/4.局部图 进行网格化处理。

用作可靠性分析的焊点凸处 应变对金属间化合物,焊料Al 及填充树脂的网格密度非常 敏感。

跌落冲击加载:加速脉冲A

3D有限元建模分析3D C2W跌落可靠性—--确定最优内部结构与材料

• 3D wafer level packaging (3D-WLSiP)WL:晶圆级封装 多个晶圆垂直堆叠粘合