VLSI测试及可测性设计方法(第四章)

VLSI 设计方法

的电路完成版图设计

6

Generated by Foxit PDF Creator © Foxit Software For evaluation only.

集成电路的

设计层级

+

SYSTEM

MODULE GATE

SYSTEM

MODULE +

GATE

CIRCUIT

Vin Vout

DEVICE

G

S

D

n

n

+

+

S/W

Reconfigurable

PCB

uP

ROM

FPGA

MPEG

ATM ROM ASIC

S/W

Reconfigurable

uP Core SRAM

FPGA

ROM A/D Block

MPEG ROM

ATM Glue Logic

缺点:

设计工作量大,时间长--spice仿真,定制版图

利用优点,避免其缺点 模拟电路:难以进行逻辑抽象,只能依靠spice

仿真,电路规模较小 数字电路:版图结构规整;小规模模块

12

Generated by Foxit PDF Creator © Foxit Software For evaluation only.

SOC 9

Generated by Foxit PDF Creator © Foxit Software For evaluation only.

设计层级与设计方法

面对设计规模的挑战人们需 要提高设计层级来有效的完 成(Divide and conquer)

超大规模集成电路测试现状及关键技术

超大规模集成电路测试现状及关键技术一、本文概述随着信息技术的迅猛发展,超大规模集成电路(VLSI)已成为现代电子系统的核心组成部分,广泛应用于通信、计算机、消费电子等众多领域。

然而,随着集成电路规模的不断增大和复杂性的提升,其测试问题日益凸显,成为制约集成电路产业进一步发展的关键技术难题。

因此,对超大规模集成电路测试的现状进行深入分析,探讨其关键技术,对于提升我国集成电路产业的核心竞争力具有重要意义。

本文旨在全面概述超大规模集成电路测试的现状,分析当前面临的主要挑战,并深入探讨相关的关键技术。

我们将回顾超大规模集成电路测试的发展历程,阐述其基本原理和方法。

我们将分析当前超大规模集成电路测试面临的主要问题和挑战,如测试数据量巨大、测试成本高昂、测试效率低下等。

接着,我们将深入探讨超大规模集成电路测试的关键技术,包括可测试性设计、故障模型与故障诊断、测试数据生成与优化等。

我们将展望未来的发展趋势,提出相应的建议和对策,以期为我国集成电路产业的持续健康发展提供参考和借鉴。

二、VLSI测试现状随着科技的飞速发展,超大规模集成电路(VLSI)已经成为现代电子系统的核心组成部分。

然而,随着集成度的不断提高,VLSI的测试问题也日益凸显。

目前,VLSI测试面临的主要挑战包括测试数据的生成、测试复杂性的增加、测试成本的上升以及测试效率的提升等。

在测试数据生成方面,由于VLSI的规模庞大,传统的测试方法已经无法满足需求。

因此,研究人员提出了多种基于自动测试设备(ATE)和仿真工具的测试数据生成方法,以提高测试数据的覆盖率和故障检测能力。

测试复杂性的增加是另一个重要的问题。

由于VLSI结构复杂,故障模式多样,传统的测试方法往往难以有效应对。

为了解决这一问题,研究人员正在探索基于人工智能和机器学习的测试方法,以提高测试的智能化和自动化水平。

测试成本的上升也是一个不容忽视的问题。

随着VLSI规模的增加,测试所需的时间和资源也在不断增加,导致测试成本急剧上升。

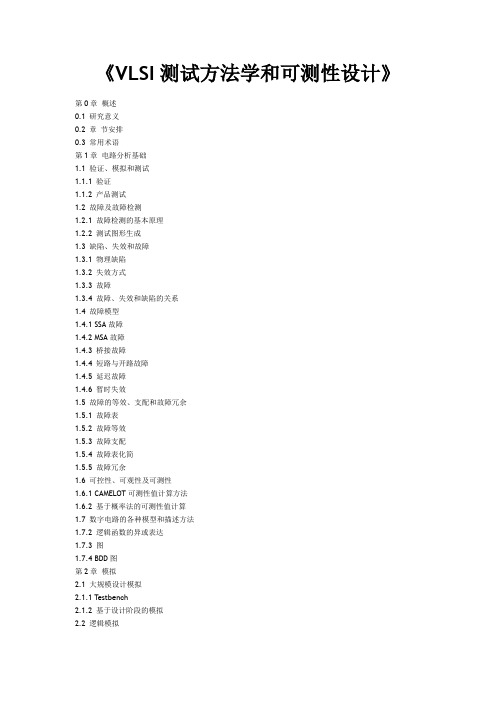

VLSI测试方法学和可测性设计

《VLSI测试方法学和可测性设计》第0章概述0.1 研究意义0.2 章节安排0.3 常用术语第1章电路分析基础1.1 验证、模拟和测试1.1.1 验证1.1.2 产品测试1.2 故障及故障检测1.2.1 故障检测的基本原理1.2.2 测试图形生成1.3 缺陷、失效和故障1.3.1 物理缺陷1.3.2 失效方式1.3.3 故障1.3.4 故障、失效和缺陷的关系1.4 故障模型1.4.1 SSA故障1.4.2 MSA故障1.4.3 桥接故障1.4.4 短路与开路故障1.4.5 延迟故障1.4.6 暂时失效1.5 故障的等效、支配和故障冗余1.5.1 故障表1.5.2 故障等效1.5.3 故障支配1.5.4 故障表化简1.5.5 故障冗余1.6 可控性、可观性及可测性1.6.1 CAMELOT可测性值计算方法1.6.2 基于概率法的可测性值计算1.7 数字电路的各种模型和描述方法1.7.2 逻辑函数的异或表达1.7.3 图1.7.4 BDD图第2章模拟2.1 大规模设计模拟2.1.1 T estbench2.1.2 基于设计阶段的模拟2.2 逻辑模拟2.2.1 编译模拟2.2.2 事件驱动模拟2.2.3 延迟模型2.3 故障模拟2.3.1 并行故障模拟2.3.2 演绎故障模拟2.3.3 并发性故障模拟2.3.4 故障模型结果分析第3章组合电路的测试3.1 简介3.2 异或法3.2.1 异或法3.2.2 不可检测故障3.2.3 多输出电路3.3 布尔差分3.3.1 对原始输入节点的布尔差分3.3.2 布尔差分的性质3.3.3 对电路内部节点的布尔差分3.4 路径敏化法3.4.1 确定性算法的基本过程3.4.2 无扇出分支的路径敏化法3.4.3 有扇出分支的路径敏化法3.5 D算法3.5.1 D算法关键术语3.5.2 D算法的基本步骤3.5.3 D算法举例3.6 PODEM算法3.6.1 PODEM算法思路3.6.2 PODEM算法流程3.6.3 PODEM算法举例3.7 其他测试生成算法3.7.1 FAN算法3.7.2 其他算法第4章时序电路的测试4.1 时序电路测试的概念4.2 时序电路的功能测试4.2.1 时序电路的检查序列4.2.2 时序电路功能测试4.3 时序电路的确定性测试生成4.3.1 时序电路的模型4.3.2 时序电路的测试生成模型4.3.3 扩展的向后驱赶算法4.3.4 扩展的向后驱赶算法举例4.4 时序电路的其他测试生成方法4.4.1 FASTEST算法4.4.2 CONTEST算法第5章专用可测性设计5.1 概述5.2 可测性分析5.2.1 可控性值的估计5.2.2 可观性值5.2.3 SCOAP算法描述5.2.4 可测性度量的应用5.3 可测性的改善方法5.3.1 插入测试点5.3.2 电路分块5.4 容易测试的电路5.4.1 C可测性5.4.2 变长测试5.5 组合电路的可测性设计5.5.1 用Reed-Muller模式设计组合电路5.5.2 异或门插入法5.5.3 组合电路的其他可测性设计方法5.6 时序电路可测性设计中的问题5.6.1 时序电路的初始化设计问题5.6.2 时间延迟效应的最小化5.6.3 逻辑冗余问题5.6.4 避免设计中非法状态5.6.5 增加逻辑以控制振荡第6章扫描路径法6.1 简介6.2 扫描路径设计6.2.1 基本的扫描路径设计6.2.2 部分扫描设计6.2.3 隔离的串行扫描设计6.2.4 非串行的扫描设计6.3 扫描路径的测试方法6.3.1 组合电路部分的测试生成6.3.2 测试施加6.3.3 扫描路径测试举例6.4 扫描路径设计及测试举例6.5 扫描路径的结构6.5.1 双口触发器和电平敏化锁存器6.5.2 电平敏化扫描设计6.5.3 随机编址的存储单元第7章边界扫描法7.1 边界扫描法的基本结构7.2 测试存取通道及控制7.2.1 测试存取通道的信号7.2.2 TAP控制器7.2.3 TAP控制器的操作7.3 寄存器及指令7.3.1 指令寄存器7.3.2 测试数据寄存器7.3.3 指令7.4 操作方式7.4.1 正常操作7.4.2 测试方式操作7.4.3 测试边界扫描寄存器7.5 边界扫描描述语言7.5.1 主体7.5.2 BSDL描述器件举例第8章随机测试和伪随机测试8.1 随机测试8.1.1 随机测试的概念8.1.2 故障检测率的估算8.1.3 测试图形长度的计算8.1.4 输入变量的优化8.2 伪随机序列8.2.1 同余伪随机序列8.2.2 反馈移位寄存器和异或门构成的伪随机序列生成电路8.3 LFSR的数学基础8.3.1 根据本原多项式优化伪随机序列发生电路8.3.2 LFSR的运算8.3.3 M序列的特性8.4 伪随机测试序列生成电路8.4.1 外接型PRSG8.4.2 内接型PRSG8.4.3 混合连接型PRSG8.5 与M序列相关的序列的生成方法8.5.1 Ford序列8.5.2 De Bruijn序列8.6 低功耗测试序列8.6.1 RSIC序列生成原理8.6.2 RSIC序列的数学表达8.6.3 RSIC序列的特性第9章内建自测试9.1 内建自测试的概念9.1.1 内建自测试简介9.1.2 内建自测试的结构9.1.3 内建自测试的测试生成9.2 响应数据压缩9.2.2 "1"计数9.2.3 跳变次数压缩9.3 特征分析法9.3.1 特征分析原理9.3.2 串行输入特征寄存器9.3.3 多输入的特征分析9.4 内建自测试的结构9.4.1 内建自测试9.4.2 自动测试9.4.3 循环内建自测试9.4.4 内建逻辑块观测器9.4.5 随机测试组合块9.4.6 STUMPS第10章电流测试10.1 简介10.2 IDDO测试机理10.2.1 基本概念10.2.2 无故障电路的电流分析10.2.3 转换延迟10.3 IDDO测试方法10.3.1 片外测试10.3.2 片内测试10.4 故障检测10.4.1 桥接10.4.2 栅氧10.4.3 开路故障10.4.4 泄漏故障10.4.5 延迟故障10.5 测试图形生成10.5.1 基于电路级模型的测试图形生成10.5.2 基于泄漏故障模型的测试图形生成10.6 深亚微米技术对电流测试的影响第11章存储器测试11. 1 存储器电路模型11.1.1 功能模型11.1.2 存储单元11.1.3 RAM组成11.2 存储器的缺陷和故障模型11.2.1 缺陷11.2.2 阵列故障模型11.2.3 周边逻辑11.3 存储器测试的类型11.3.1 性能测试11.3.3 功能测试11.3.4 电流测试11.4 存储器测试算法11.4.1 MSCAN算法11.4.2 GALPAT算法11.4.3 算法型测试序列11.4.4 Checkerboard测试11.4.5 Marching图形序列11.4.6 March测试的表达方法11.4.7 各种存储器测试算法的分析11.5 存储器测试方法11.5.1 存储器直接存取测试11.5.2 存储器内建自测试11.5.3 宏测试11.5.4 各种存储器测试方法比较11.6 存储器的冗余和修复第12章SoC测试12.1 SoC测试的基本问题12.1.1 SoC核的分类12.1.2 SoC测试问题12.1.3 存取、控制和隔离12.2 概念性的SoC测试结构12.2.1 测试源和测试收集12.2.2 测试存取机构12.2.3 测试壳12.3 测试策略12.3.1 核的非边界扫描测试12.3.2 核的边界扫描测试策略12. 4 IEEE P1500标准12. 5 SoC测试再探索。

VLSI测试与可测性设计第一讲

2002年9月16日

Testing Principle

2002年9月16日

Automatic Test Equipment Components

Consists of:

Powerful computer Powerful 32-bit Digital Signal Processor (DSP) for analog testing Test Program (written in high-level language) running on the computer Probe Head (actually touches the bare or packaged chip to perform fault detection experiments) Probe Card or Membrane Probe (contains electronics to measure signals on chip pin or pad)

2002年9月16日

Motivation

Need to understand some Automatic Test Equipment (ATE)

technology

Influences what tests are possible Serious analog measurement limitations at high digital frequency or in the analog domain Need to understand capabilities for digital logic, memory, and analog test in System-on-a-Chip (SOC) technology

VLSI考试重点

2

Ch. 12 - Test Technology Trends In Nanometer Age

Fault Models

A given fault model has k types of faults

k = 2 for o most ost fault au t models ode s

– Combinational Controllability /observability Calculation Rules – Levelization Algorithm

Probability-based testability analysis

– Probability-based Controllability/observability calculation rules

第三讲

逻辑模拟

Truth Table Based Gate Evaluation Parallel Gate Evaluation Compiled Code Simulation Event-Driven Simulation

带时延的逻辑模拟:Transport delay,Inertial delay 故障模拟

Pseudo Random Testing Pseudo-Random

Weighted LFSR: Weighted Pattern Generator

Output Response Analysis

Ones count testing, Transition count testing Aliasing gp probability y Signature analysis: SISR

VLSI测试及可测性设计方法课件

23

第四节

*D算法

24

D算 法

• 事实上,要检测或诊断某一个故障往往只 需找到其中一个或一些测试矢量就能满足 实际工作的需要。D算法就是其中的一种重 要方法。罗思(Roth)在1966年提出的D算 法对于任意非冗余的组合电路中的故障均 能找到某个(某些)故障的测试矢量,而 且它的计算方法很容易用计算机来实现。

• 讨论核心:如何充分发挥每个测试矢量的测试功 能,以进一步减少测试电路的测试矢量数。

45

第六节

特征分析法

46

常用的特征分析法

• 线性反馈移位寄存器(LFSR)组成 的特征分析器

• 跳变次数测试(TC) • 症候群(syndrome)测试

47

一个响应序列的特征应该满足如下几个条件:

1 这个特征应尽可能多地保留原序列中的有用(即 对故障检测和诊断有用的)信息。同时,各序列 的特征应有较明显的差异,尽量做到各种不同的 序列应有不同的特征。

D1 D2

1

1

0

1

0

0

0

0

1

0

0

1

0

0

1

0

1

1

0

1

1

0

0

1

1

0

1

1

1

1

1

1

D3 D4

1

1

1

1

1

1

0

1

0

0

0

0

1

0

0

1

0

0

1

0

1

1

0

1

1

0

0

1

1

0

1

1

可测性设计技术

可测性设计技术摘要本文从可测性设计与VLSI测试,VLSI设计之间的关系出发,将与可测性设计相关的VLSI 测试方法学、设计方法学的内容有机地融合在一起,文中简要介绍了VLSI可测性设计的理论基础和技术种类,可测性设计的现状,发展趋势,可测试性设计的内涵、意义和分类,并且探讨了可测性设计的实现方法。

关键词:可测性设计,自动测试生产,扫描技术,边界扫描技术,嵌入式自测试。

1可测性设计技术概述可测性的起源于发展过程20世纪70年代,美军在装备维护过程中发现,随着系统的复杂度不断提高,经典的测试方法已不能适应要求,甚至出现测试成本与研制成本倒挂的局面。

20世纪80年代中,美国军方相继实施了综合诊断研究计划。

并颁布《系统和装备的可测性大纲》,大纲将可测性作为与可靠性及维修等同的设计要求,并规定了可测性分析,设计及验证的要求及实施方法。

该标准的颁布标志这可测性作为一门独立学科的确立。

尽管可测性问题最早是从装备维护的角度提出,但随着集成电路(IC)技术的发展,满足IC测试的需求成为推动可测性技术发展的主要动力。

从发展的趋势上看,半导体芯片技术发展所带来的芯片复杂性的增长远远超过了相应测试技术的进步。

随着数字电路集成度不断提高,系统日趋复杂,对其测试也变得越来越困难。

当大规模集成电路LSI和超大规模集成电路VLSI问世之后,甚至出现研制与测试费用倒挂的局面。

这就迫使人们想到能否在电路的设计阶段就考虑测试问题,使设计出来的电路既能完成规定的功能,又能容易的被测试,这就是所谓的可测性设计技术。

因此也就出现了可测性的概念。

可测性的基本原理可测试性大纲将可测试性(testability)定义为:产品能及时准确地确定其状态(可工作、不可工作、性能下降),隔离其内部故障的设计特性。

以提高可测试性为目的进行的设计被称为可测试性设计(DFT: design for testability)。

可测试性是测试信息获取难易程度的表征。

可测性设计技术

可测性设计技术摘要本文从可测性设计与VLSI测试,VLSI设计之间的关系出发,将与可测性设计相关的VLSI 测试方法学、设计方法学的内容有机地融合在一起,文中简要介绍了VLSI可测性设计的理论基础和技术种类,可测性设计的现状,发展趋势,可测试性设计的内涵、意义和分类,并且探讨了可测性设计的实现方法。

关键词:可测性设计,自动测试生产,扫描技术,边界扫描技术,嵌入式自测试。

1可测性设计技术概述可测性的起源于发展过程20世纪70年代,美军在装备维护过程中发现,随着系统的复杂度不断提高,经典的测试方法已不能适应要求,甚至出现测试成本与研制成本倒挂的局面。

20世纪80年代中,美国军方相继实施了综合诊断研究计划。

并颁布《系统和装备的可测性大纲》,大纲将可测性作为与可靠性及维修等同的设计要求,并规定了可测性分析,设计及验证的要求及实施方法。

该标准的颁布标志这可测性作为一门独立学科的确立。

尽管可测性问题最早是从装备维护的角度提出,但随着集成电路(IC)技术的发展,满足IC测试的需求成为推动可测性技术发展的主要动力。

从发展的趋势上看,半导体芯片技术发展所带来的芯片复杂性的增长远远超过了相应测试技术的进步。

随着数字电路集成度不断提高,系统日趋复杂,对其测试也变得越来越困难。

当大规模集成电路LSI和超大规模集成电路VLSI问世之后,甚至出现研制与测试费用倒挂的局面。

这就迫使人们想到能否在电路的设计阶段就考虑测试问题,使设计出来的电路既能完成规定的功能,又能容易的被测试,这就是所谓的可测性设计技术。

因此也就出现了可测性的概念。

可测性的基本原理可测试性大纲将可测试性(testability)定义为:产品能及时准确地确定其状态(可工作、不可工作、性能下降),隔离其内部故障的设计特性。

以提高可测试性为目的进行的设计被称为可测试性设计(DFT: design for testability)。

可测试性是测试信息获取难易程度的表征。

数字集成电路可测性设计(DFT)讲义第1讲

Good chip appears to be faulty (fails test)

EE141 VLSI Test Principles and Architectures

11

Introduction

Electronic System Manufacturing

A

system consists of

Moore’s Law: scale of ICs doubles every 18 months

Growing size and complexity poses many and new testing challenges

VLSI M LSI

1960s 1970s 1980s 1990s 2000s

EE141 VLSI Test Principles and Architectures

5

Introduction

Importance of Testing

Moore’s Law results from decreasing feature size (dimensions)

from 10s of µm to 10s of nm for transistors and interconnecting wires

8

Introduction

Testing During VLSI Development

Design verification targets design errors

Corrections made prior to fabrication

Design Specification Design Fabrication Packaging Quality Assurance Design Verification Wafer Test Package Test Final Testing

VLSI测试与可测性设计

VLSI测试与可测性设计摘要:从可测性设计与 VLSI 测试、VLSI设计之间的关系出发,将与可测性设计相关的VLSI测试方法学、设计方法学的内容有机地融合在一起。

文中简要地介绍了VLSI可测性设计的理论基础和技术种类,简明地评述了可测性设计的现状和发展趋势,并且探讨了可测性设计的实现方法。

关键词:可测性设计、自动测试生成、扫描设计、边界扫描技术第一章引言在VLSI(超大规模集成电路)技术迅猛发展的今大,集成电路工业已经达到了一个的高度:上亿只晶体管集成在一个芯片上,片内时钟信号的频率超过2GHz。

随之而来的,是越来越突出的测试瓶颈问题。

一则,ATE(自动测试设备)的发展很难跟得上芯片的发展步伐(系统时钟、信号精度、存储数据量等)。

再则,高性能ATE的价格将是令人望而却步的。

而SoC(片上系统)的出现,更是对测试领域提出了新的挑战。

为了保证芯片的可靠性,测试是必不可少的手段。

而要突破测试瓶颈,只有一个唯一的途径:DFT可测性设计。

VLSI可测性设计是一些应用于VLSI设计的规则和方法的集合;是通过在电路中增加一些物理结构,使得该设计具有“容易被测试”的特性,并使其能够实现高质量的制造测试的方法的总称。

可测性设计的目的,不仅仅是测试矢量的自动生成和故障覆盖率的提高,也不仅仅是为了某种类型测试设备的需要。

可测性设计是集成电路设计学和测试方法学的有机融合。

一方而,集成电路测试方法学的每个新的突破,都会带来可测性设计技术领域的新的一飞跃。

另一方而,可测性设计越来越成为VLSI设计过程中不可或缺的一环,它已经渗透到集成电路设计的各个层而。

可测性设计的成败,直接影响到整个电路的性能,影响到芯片设计、制造和测试,乃至芯片成木、开发时间和产品品质等决定其市场竞争能力的因素。

因此,本文分别从“DFT与VLSI测试”、"DFT与VLSI设计”这两个角度,对自上个世纪70年代以来,VLSI可测性设计领域里丰硕的理论和实践成果,以及未来的发展趋势做了一个比较系统和全而的归纳和总结。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

可测性概念包括两方面内容

• 电路内的故障是否可以用有限的测试 图形来检测或定位。

• 故障效应观察的难易程度,也就是说 检测故障所需的测试图形的长度和生 成时间、施加时间长短的问题。

4

可测性设计的两种基本策略

• 为了获得最大的可测性而不惜成本地 进行设计。

• 采取一些切实有效的方法,增加少量 或有限的硬件开销来提高系统和电路 的可测性。

测试组合电路的测试向量可以用组合电路的测 试生成方法来生成。

36

切换逻辑

37

两种途径

• 第一种途径是:选用由时钟控制的电平触 发器或其它存储元件来设计电路,而不采 用常用的由时钟的上升沿或下降沿来触发 的边沿触发的时序元件,以克服切换时产 生的竞态现象对测试的影响。其典型例子 是选用电平触发的主从结构的触发器。当 然用主从结构触发器将影响工作速度。

35

主 要 测 试 步 骤(续)

(3)组合电路N的测试 在测试组合电路N时,它的测试激励来自原始

输入端PI和时序元件Yi的输出端,显见PI端的信 号可直接施加,而Yi的状态需要从“扫描输入” 端逐位移入。N的输出也有两部分,一部分是直 接可观察到的原始输出端PO,另一部分送到时序 元件Yi的输入端,这部分信号的观察要分两步操 作:第一步是将这些信号锁存到时序元件Yi中, 第二步是将时序元件Yi中的状态逐位移出,以便 在“扫描信号输出”端观察它们。

5

可测性设计可分为两大类

• 专项设计(Ad Hoc Design): 安功能基本要求设计系统和电路,采取一 些比较简单易行的措施,使它们的可测性 得到提高。

• 结构设计(Structured Design): 根据可测性设计的一般规则和基本模式来 进行电路的功能设计。 这两种方法的指导思想来源于上述两种 不同的基本策略。

29

电路分块的三点实施措施

• 分块后,可将一些控制点和观察点引出。 • 在各块之间利用选通信号来构成通路。 • 总线结构可以很方便地控制各模块之间的

信号沟通,因总线具有处高阻状态的第三 态,很容易使若干模块相互隔离和分块。

30

31

第二节

扫描测试 (Scan Test)

32

扫描设计的主要思路

将电路中的组合元件与时序元件隔离 开来,其中组合电路可以用组合电路 的测试方法来测试,而其中的时序电 路是串接成移位寄存器形式,以便把 测试信号移入时序元件内,也便于将 时序元件的状态移出来,使之得以观 察。

33

Scan Design总体框图

34

主要测试步骤

(1)将电路置成扫描测试状态,利用扫描时钟(系统时钟) 和扫描信号输入使移位寄存器置成全0和全1的状态,以检 查每个触发器是否有两种稳定状态;然后用输入序列 00110011…检查每个触发器翻转功能等。

(2)检查组合电路N和存储元件之间的连接关系。可以先在 “测试”状态下用测试号(扫描信号输入)把时序元件置 成某个状态,并在组合电路N的原始输入端PI输入必要的 测试矢量;然后把电路置成“正常”方式,把N的输出信 号送入时序元件;最后又返回 “测试”状态,利用扫描 方式,在原始输出端PO处观察响应(也可以在扫描的串 行输出端 观察),以判定连接电路是否有故障。

• 第二种途径是:采用专用的移位式锁存器 SRL(Shift Register Latch)。

38

移位式锁存器SRL(1)

39

移位式锁存器SRL(2)

40

第一种方案

利用L1/L2型的SRL进行设计。它的主要做法是 将一般时序电路模式中的每个时序元件Yi都用一 个SRL替代,每个SRL的L2作为正常输出端。在 进行测试时,把丫i+1的L2输出作为Yi的移位输入 信号,从而组成一个移位寄存器。这种做法本质 上是用主从结构的触发器作为时序元件,因此电 路在正常工作和测试时都是以主从结构方式工作。 它的主要缺点有两个:一个是所用的元件较多 (一对L1和L2只作一个时序元件使用),另一个 是正常工作时信号的路径比较长,影响工作速度 的提高。

17

18

19

20

举例

21

22

计算可控性值的流程图

23

计算可观性值的流程图

24

插入观察点

25

26

插入控制点

27

2.电 路 分 块

28

划分分块依据

• 以功能模块如ALU操作单元、控制单元来 进行划分。

• 以时序逻辑、开关网络进行划分,这些单 元可以组成一个系统。

• 根据逻辑结构进行划分。 划分方法的一般规则是采用多路转换器和 通道系统,每个部分测量的细节依赖于这 个部分的逻辑功能及相应的单元实现情况。

41

第二种方案

42

第三种方案

43

第三种方案缺点

测试时有时不能得到所需要的测试信号。 因为在测试组合电路N(1)和N(2)时需要 Y(1)和Y(2)提供必要的测试信号,因此Y(1) 和Y(2)应该是随意可控的。但是注意到 L1/L2*型SRL的特点,在扫描时钟A和B的 激励下,每个SRL的L2*应该是L1的前一拍 信号,而每个SRL的L1应该是前一个SRL的 L2*的前一拍信号,这样所给出的信号就有 一定的约束。

可控性值的估计

12

13

14

15

举例

16

可观性值的估计

• 定义5.3 为把节点N的信息传播到原始输 出,所需最少的组合逻辑值赋值次数叫做 节点N的组合可观性值,用CO (N)表示。

• 定义5.4 为把节点N的信息传播到原始输 出,所需最少的时序逻辑赋值次数叫做节 点N的时序可观性值,用SO (N)表示。

6

第一节

特定测试法 ( Ad Hoc )

7

Ad-Hoc常用的三种方法

• 在电路的某些“关键点”增加测试 点

• 把电路划分为功能块的形式(又称: “规划技术”)

• 建立“测试总线”

8

1.可 测 性 分 析

(增加测试点)

9

SCOAP可测试性度量

Goldstein (高尔德斯泰可测性度量)

10

11

第四章 可测性设计

1

容易测试的电路时间内完成。

• 在满足测试覆盖率的条件下测试图形 的长度应尽可能短。

2

可测性定义

Bennetts于1984年提出: “A digital IC is testable if test

patterns can be generated, applied, and evaluated in such a way as to satisfy predefined cost budget and time scale.”