射频CMOS集成电路设计

CMOS射频集成电路设计-CMOS射频IC器件模型

集成电路的设计和制作行业逐渐变成两个独立的产业方向,

出现了专门从事集成电路制造的代工厂(foundry)和无生产线

(fabless)的专业集成电路设 计公司。

CMOS射频IC器件模型

本书研究的芯片设计采用的是无生产线的集成电路设计

方法。所谓无生产线芯片设 计,是指设计者根据设计指标选

择某一种特定的工艺和代工厂,基于代工厂提供的工艺模 型

关于扩散电容Cd,有如下数学表示式:

其中,τT 为渡越时间(transittime)。

CMOS射频IC器件模型

2. 二极管线性模型

如果二极管工作在一个直流电压偏置点上,而且信号仅

在该点附近发生微小变化,就 引入了线性模型,即小信号模型

(small-signalmodel)。二极管线性模型通过偏置点(以 Q 表示)

signal工艺在第 五层金属(M5)和顶层金属(M6)之间又增加了

一层金属,通过降低金属之间氧化层厚度增 大电容值,该金属

与 M5之间形成的 MIM 电容约为1fF/μm2。图2-3给出了

CMOS工 艺的 MIM 电容的等效电路模型。

CMOS射频IC器件模型

图2-3 MIM 电容的等效电路模型

CMOS射频IC器件模型

通过引入基极 发射极扩散电容、基极 集电极扩散电容

(Cde、Cdc)以及二极管的结电 容(Cje、Cjc),可以将上述静态模

型修正为动态模型。图2-9(a)给出了动态埃伯斯 莫尔 模型。

对于射频工作条件下的电路,还要考虑引线电阻、电感以及

端点之间的分布电容, 如图2-9(b)所示。

CMOS射频IC器件模型

4)反向线性区(0<-UDS<UGD-UT0)

CMOS射频集成电路分析与设计

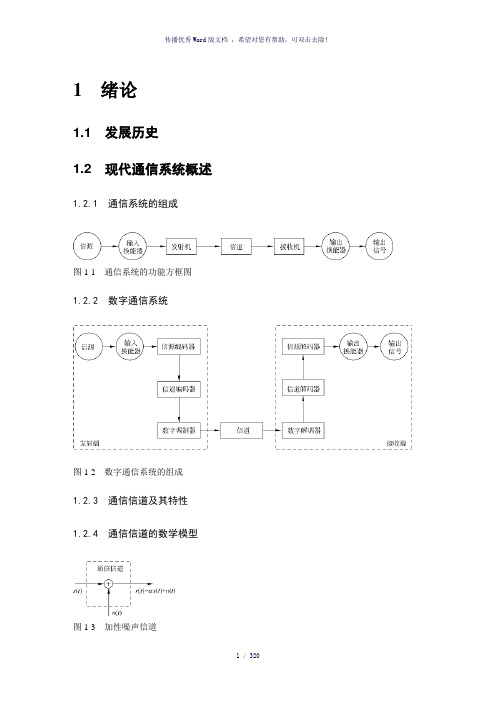

1 绪论1.1 发展历史1.2 现代通信系统概述1.2.1 通信系统的组成图1-1 通信系统的功能方框图1.2.2 数字通信系统图1-2 数字通信系统的组成1.2.3 通信信道及其特性1.2.4 通信信道的数学模型图1-3 加性噪声信道图1-4 带加性噪声的线性滤波信道图1-5 带加性噪声的线性时变滤波器1.3 射频电路在系统中的作用与地位图1-6 射频通信系统示意图图1-7 射频前端方框图1.4 射频电路与微波电路和低频电路的关系1.4.1 频段划分1.4.2 电路的寄生效应1.4.3 电路的设计考虑1.5 应用1.5.1 无线局域网图1-8 Prism Duette双频带收发机芯片组的总体结构图141.5.2 GSM1.5.3 WCDMA1.6 总结参考文献2 线性射频电路的基本特性和分析方法2.1 传输线图2-1 射频电路中常用的均匀传输线2.1.1 传输线波动方程图2-2 一小段传输线的等效电路2.1.2 终端接负载的无损传输线图2-3 以负载处为原点的坐标体系2.1.3 终端接特定负载的无损传输线的工作状态图2-4 短路传输线上电压、电流和输入阻抗的分布图图2-5 开路传输线上电压、电流和输入阻抗的分布图2.1.4 阻抗的周期性和倒置性2.1.5 微带线设计图2-6 微带线的几何结构图2-7 微带线的特性阻抗图2-8 微带线的有效介电常数2.2 Smith圆图2.2.1 阻抗圆图图2-9 阻抗圆图上的归一化阻抗2.2.2 Smith圆图上的反射系数和驻波系数图2-10 阻抗圆图2.2.3 导纳圆图图2-11 导纳圆图上的归一化导纳2.2.4 Smith圆图应用举例图2-12 例2.2的电路图图2-13 利用Smith圆图求解例2.2 2.3 双端口网络2.3.1 网络参量图2-14 双端口网络的电压和电流方向图2-15 双端口网络的入射波和反射波图2-16 S参数的测量2.3.2 网络的互联图2-17 双端口网络的串联图2-18 双端口网络的并联图2-19 双端口网络的串并联图2-20 双端口网络的并串联图2-21 双端口网络的级联2.3.3 信号流图分析法图2-22 信号流图分析法的简化规则图2-23 含电源和负载的双端口网络图2-24 用信号流图分析法分析双端口网络的简化过程2.4 射频电路中的无源分立集总参数元件图2-25 铝金属线归一化电流密度的横截面分布示意图图2-26 铝金属线横截面上的归一化电流密度分布随频率的变化(a=1mm)图2-27 金属铜和铝的趋肤深度随工作频率的变化图2-28 薄膜片上电阻图2-29 炭质电阻图2-30 高频电阻模型图2-31 炭质电阻的阻抗与频率的关系图2-32 表面贴封电容的内部结构图2-33 高频电容模型图2-34 实际电容的阻抗与频率的关系图2-35 高频电感\图2-36 高频电感模型图2-37 实际电感的阻抗与频率的关系2.5 总结参考文献习题图2-38 习题4图图2-39 习题7图图2-40 习题8图3 无源RLC网络和阻抗匹配3.1 无源RLC网络3.1.1 串联RLC网络图3-1 串联RLC网络图3-2 串联RLC网络的阻抗特性图3-3 串联RLC网络中电感储存的磁能、电容储存的电能以及回路储存的总能量随时间的变化情况图3-4 品质因子Q取不同值时回路阻抗的幅频特性和相频特性3.1.2 并联RLC网络图3-5 并联RLC网络图3-6 并联RLC网络的阻抗特性图3-7 品质因子QP取不同值时并联谐振回路阻抗的幅频特性和相频特性3.2 串并联阻抗等效互换图3-8 串并联RLC网络图3-9 电阻R和电抗X的串联形式和并联形式3.3 回路抽头时的阻抗变换图3-10 电感抽头和电容抽头的RLC谐振回路3.4 阻抗匹配图3-11 借以说明阻抗匹配概念的简单电路图3.4.1 L匹配图3-12 L匹配的电路结构图3-13 并/串联电感和电容的阻抗变化轨迹图3-14 利用Smith圆图来求解L匹配问题图3-15 L匹配网络图3-16 Smith圆图上的恒Qn圆3.4.2 T匹配和Pi匹配图3-17 T匹配网络图3-18 利用Smith圆图来设计T匹配网络图3-19 Pi匹配网络图3-20 利用Smith圆图来设计Pi匹配网络3.4.3 微带线匹配图3-21 微带线匹配网络图3-22 利用Smith圆图来设计微带线匹配网络图3-23 归一化阻抗zin=rin+jxin与电容所在位置之间的关系图3-24 更复杂的微带线匹配网络图3-25 全部由微带线组成的匹配网络3.5 总结参考文献习题图3-26 习题3图4 射频集成电路中的基本问题4.1 射频电路的性能度量4.1.1 功率增益和电压增益4.1.2 灵敏度和噪声系数图4-1 电阻的噪声模型4.1.3 线性度和动态范围图4-2 非线性4.1.4 系统设计4.2 射频电路仿真算法及商用仿真软件介绍4.2.1 SPICE模拟器应用于射频领域所遇到的限制4.2.2 射频电路仿真算法4.2.3 射频电路仿真工具4.3 CMOS射频集成电路实现的难点4.4 总结参考文献习题5 集成无源元件5.1 电阻图5-1 有拐角的电阻5.2 电容图5-2 MOS电容的理想C-V曲线图5-3 MIM电容的结构图5-4 三种互连线结构图5-5 “夹心”金属电容5.3 电感图5-6 射频集成电路中电感的典型应用5.3.1 片上平面螺旋型电感图5-7 片上平面螺旋型电感的结构图5-8 接地隔离层图5-9 片上平面螺旋型电感模型图5-10 焊盘的校准结构。

CMOS射频集成电路设计(负反馈)---Thomas Lee

vIN

+

σ

a

vOUT

f

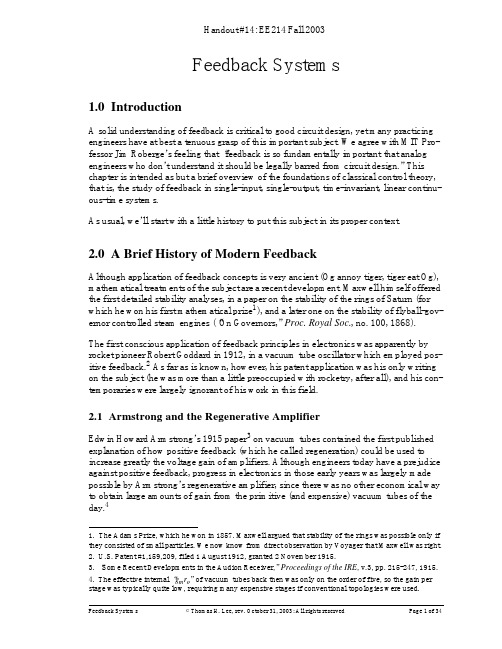

Here, the quantity a is known as the forward gain, while f is the feedback gain. In our particular example, a represents the gain of an ordinary (i.e., open-loop) single vacuum tube amplifier, while f represents the fraction of the output voltage that is fed back to the amplifier input. Since we have the block diagram, it’s straightforward to derive an expression for the overall gain of this amplifier. First, recognize that: σ = v IN + f ⋅ vOUT Next, note that: v OUT = a ⋅ σ = a ⋅ ( v IN + f ⋅ vOUT ) Solving for the input-output transfer function yields: a A = -------------1 – af

(3) (2) (1)

It is evident that any positive value of af smaller than unity gives us an overall gain A that exceeds a, the “ordinary” (open-loop) gain of the vacuum tube amplifier. If we make af equal to 0.9, the overall gain is increased to ten times the open-loop gain, while an af product of 0.99 gives us a factor of 100 gain increase, and so on. In this way, Armstrong was able to get gain from a single stage that others could obtain only by cascading several. This achievement allowed the construction of relatively inexpensive, high-gain receivers and therefore also enabled dramatic reductions in transmitter power because of the enhanced sensitivity provided by this increased gain. In short order, the positive feedback (regenerative) amplifier became a nearly universal idiom, and Westinghouse (to whom Armstrong had assigned patent rights) kept its legal staff quite busy trying to make sure that only licensees were using this revolutionary technology.

通信电子中的CMOS射频集成电路技术

通信电子中的CMOS射频集成电路技术近年来,通信电子发展日新月异,越来越多的新技术被应用于实际应用中。

而CMOS射频集成电路技术的应用在通信电子领域中也得到了广泛的关注,堪称射频IC设计的一大新方向。

CMOS,即互补金属氧化物半导体技术,在数字电路中有着广泛的应用。

CMOS技术的优点在于其低功耗、高噪声容限、良好的抗干扰性、器件尺寸小等特点,使得它成为了基于集成电路的数字电子领域的基础技术。

但是在射频信号处理技术中,CMOS 技术遇到了很多挑战。

其中之一就是CMOS技术器件的高失真率和低增益率等问题。

为了在CMOS技术上实现高效的射频信号处理,科学家们尝试了很多新思路,并发展出了一些新的CMOS射频集成电路技术。

这些新技术不仅在电路性能方面表现出色,而且制造成本低、稳定性高,易于实现大规模集成。

下面就让我们来一一了解这些技术。

1. CMOS RF SoC集成技术在射频集成电路设计中,过去通常采用上下转换器效应的基带和射频分离设计实现射频和数字部分之间的接口。

然而,这种设计方式会导致大量的串扰和电磁干扰,从而影响了射频信号的传输质量和数字信号的精度。

因此,近年来,科学家们发展出了一种名为CMOS RF SoC(System on Chip)的射频集成电路技术。

它将上下转换器效应和基带和射频分离设计的数字前端部分都整合到了一个几乎完全数字化的集成电路中,实现了数字信号的直接射频转换。

CMOS RF SoC的优点在于可靠性高、抗干扰能力强、功率消耗低等,因此在无线通信、雷达信号处理等领域得到了广泛应用。

特别是在实现高带宽、宽带、多频段接收等技术方面,CMOS RF SoC技术表现出了其他技术难以匹敌的优势。

2. 无源脉冲控制技术无源脉冲控制技术是一种实现CMOS射频集成电路的新思路。

与传统的被动无源电路设计不同的是,无源脉冲控制技术采用刻意设计的CMOS结构单元,通过设计单元间的电学耦合来实现信号的传输和信号的频率选择。

CMOS射频集成电路分析与设计

CMOS射频集成电路分析与设计CMOS射频集成电路的设计与分析是一个复杂的过程,需要考虑射频信号的传输、放大、滤波、混频等各个环节。

首先,设计师需要考虑输入和输出的阻抗匹配。

射频信号的传输需要保证能够顺利地传输到下一个级别,并且能够更好地与外部设备进行连接。

阻抗匹配可以通过调整电路中的元件值来实现,例如使用电容和电感。

其次,设计师需要进行放大器电路的设计。

放大器电路是射频电路中至关重要的一部分,可以对信号进行放大,使其能够被后续电路正确处理。

放大器电路的设计需要考虑增益、频率响应等参数。

CMOS射频集成电路中常使用共源极放大器、共栅极放大器等结构。

此外,滤波器也是射频电路中不可或缺的一部分。

滤波器可以隔离不需要的频率分量,以满足电路中的要求。

CMOS射频集成电路中常使用LC滤波器、SAW滤波器等。

滤波器的设计需要考虑通过带宽、阻带衰减、群延迟等参数。

最后,CMOS射频集成电路还需要进行混频器电路的设计。

混频器可将不同频率的信号混合在一起,产生新的频率。

混频器电路涉及到高频信号的相互作用以及非线性存在的问题。

设计师需要考虑混频器的转换增益、转换损耗等参数。

综上所述,CMOS射频集成电路分析与设计是一个复杂而且细致的过程。

需要设计师具备深厚的射频电路知识,并且熟悉相应的设计工具和模型。

同时,为了获得更好的性能和更高的集成度,设计师还需要不断地进行仿真验证、参数调整和优化。

随着射频通信和无线通信技术的发展,CMOS射频集成电路的分析与设计将会变得越来越重要,并且有着广阔的应用前景。

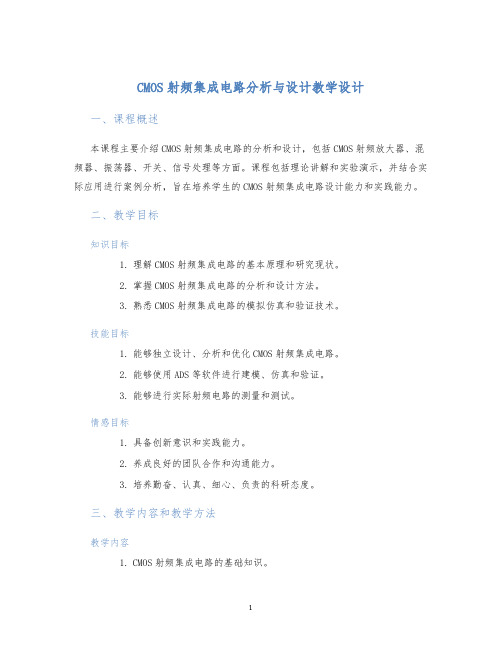

CMOS射频集成电路分析与设计教学设计

CMOS射频集成电路分析与设计教学设计一、课程概述本课程主要介绍CMOS射频集成电路的分析和设计,包括CMOS射频放大器、混频器、振荡器、开关、信号处理等方面。

课程包括理论讲解和实验演示,并结合实际应用进行案例分析,旨在培养学生的CMOS射频集成电路设计能力和实践能力。

二、教学目标知识目标1.理解CMOS射频集成电路的基本原理和研究现状。

2.掌握CMOS射频集成电路的分析和设计方法。

3.熟悉CMOS射频集成电路的模拟仿真和验证技术。

技能目标1.能够独立设计、分析和优化CMOS射频集成电路。

2.能够使用ADS等软件进行建模、仿真和验证。

3.能够进行实际射频电路的测量和测试。

情感目标1.具备创新意识和实践能力。

2.养成良好的团队合作和沟通能力。

3.培养勤奋、认真、细心、负责的科研态度。

三、教学内容和教学方法教学内容1.CMOS射频集成电路的基础知识。

2.CMOS射频放大器的分析和设计。

3.CMOS射频混频器的分析和设计。

4.CMOS射频振荡器的分析和设计。

5.CMOS射频开关的分析和设计。

6.CMOS射频信号处理的分析和设计。

教学方法1.理论授课:介绍CMOS射频电路的基本原理和设计方法,讲解重点难点知识点;课堂提问,探讨思路,激发学生的思考和学习兴趣。

2.实验教学:组织学生参加实验,包括数电基础实验和实际电路设计实验。

实验教学重点是让学生掌握模拟电路的设计、验证和优化方法。

3.课堂讨论:介绍实际CMOS射频电路应用案例,让学生讨论优缺点、经验和改进方案。

4.自主学习:推荐相关资料、书籍、论文,让学生自己探索、思考和分析。

四、教学评价考核方式1.平时成绩占比30%,包括课堂出勤、作业提交、实验报告等方面。

2.期末考试占比70%,考核学生对CMOS射频集成电路理论和实践的掌握程度和分析能力。

考核要求1.学生必须参加实验课,完成实验报告,课堂表现要积极,认真听讲,认真思考,课后可以自己尝试仿真或搭建实验电路进行实验验证。

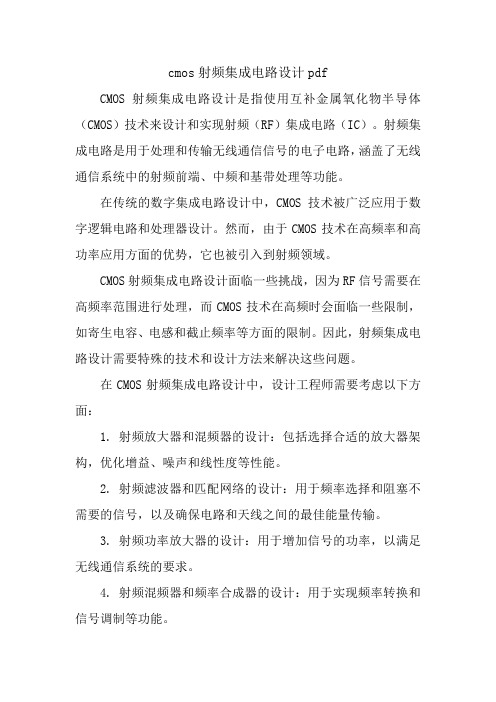

cmos射频集成电路设计pdf

cmos射频集成电路设计pdf

CMOS射频集成电路设计是指使用互补金属氧化物半导体(CMOS)技术来设计和实现射频(RF)集成电路(IC)。

射频集成电路是用于处理和传输无线通信信号的电子电路,涵盖了无线通信系统中的射频前端、中频和基带处理等功能。

在传统的数字集成电路设计中,CMOS技术被广泛应用于数字逻辑电路和处理器设计。

然而,由于CMOS技术在高频率和高功率应用方面的优势,它也被引入到射频领域。

CMOS射频集成电路设计面临一些挑战,因为RF信号需要在高频率范围进行处理,而CMOS技术在高频时会面临一些限制,如寄生电容、电感和截止频率等方面的限制。

因此,射频集成电路设计需要特殊的技术和设计方法来解决这些问题。

在CMOS射频集成电路设计中,设计工程师需要考虑以下方面:

1. 射频放大器和混频器的设计:包括选择合适的放大器架构,优化增益、噪声和线性度等性能。

2. 射频滤波器和匹配网络的设计:用于频率选择和阻塞不需要的信号,以及确保电路和天线之间的最佳能量传输。

3. 射频功率放大器的设计:用于增加信号的功率,以满足无线通信系统的要求。

4. 射频混频器和频率合成器的设计:用于实现频率转换和信号调制等功能。

5. 射频信号传输和接收电路的设计:包括天线、调制解调器和射频前端电路等。

CMOS射频集成电路设计需要深入理解射频电路和系统的工作原理、相关的无线通信标准和要求,以及CMOS技术的特点和限制。

通过合适的设计工具、模拟和仿真技术,设计工程师可以优化电路性能,满足射频通信系统的需求。

CMOS射频集成电路设计实验

Cadence软件使用 ——版图及后仿真

Cadence软件使用 ——版图及后仿真

将元件版图进行连接 DRC:设计规则检查

• 设计规则检查是必 须的,它保证设计是 否正确,满足要求可 以生产。 • 在版图编辑器的菜 单栏中选择 Assura Run DRC 弹出左图

Cadence软件使用 ——电路仿真

瞬态仿真:时域波形

Stop Time为仿真截止 时间 Accuracy Default为计 算精度

Cadence软件使用 ——电路仿真

DC分析:显示电路节点电压,静态工作点

DC分析还提供了扫描,即 在一定的变量下分析电路 工作点的变化

Cadence软件使用 ——电路仿真

Cadence软件使用 ——电路仿真

设置输出

点击Netlist and Run,开始对电路仿真

查看结果 ADE Results

Direct Plot

Main Form

Cadence软件使用 ——电路仿真

在弹出的窗口中作如下设置, 即对电路S参数的仿真 依次选择底下S11、S21、 S12、S22按钮就会画出相 应的S参数图 Plot Type 中选择其他的还可 以在Smith圆图或极坐标上显 示S参数仿真结果

•select选port •Gain Compress选择1dB,即 1dB压缩点 •外推值默认为输入最小值 •选择Input Referred 1dB Compression,即输入1dB 压缩点 •在原理图上选择输出端,可 以直接从结果上读出压缩点

Cadence软件使用 ——电路仿真

线性度IP3仿真 首先对输入port作如下设置:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程概况

●集成电路设计领域核心课程之一

●3学分48学时:每周3学时X16周

●目标:了解射频电路中的基本概念,培养初步的射频集成电路分析能力和设计能力,了解射频集成电路基本模块的分析方法和设计过程,了解无线通信系统模拟前端的系统结构,具有初步的系统设计能力

●上课时间:周三第二大节(9:50~12:15)●上课地点:四教4403

●答疑时间:周五下午4:00~5:00

●答疑地点:任课教师办公室

与前后课程之间的关系

参考书

●参考书:

◆池保勇、余志平、石秉学,《CMOS射频集成电路

分析与设计》,清华大学出版社,2006年11月

◆Thomas H.Lee,《The Design of CMOS

Radio-Frequency Integrated Circuits》

(Second Edition),电子工业出版社,2005年5

月(影印版)

◆Behzad Razavi,《RF Microelectronics》(第

二版),电子工业出版社,2012年08月(影印版)

参考文献来源

●杂志:

◆IEEE Journal of Solid-State Circuits (JSSC)

◆IEEE Transactions on Circuits and Systems, I, II (TCAS)

◆IEEE Transactions on Microwave Theory and Techniques (MTT)

◆IEEE Microwave and Wireless Components Letters (MWCL)

●会议:

◆IEEE International Solid-State Circuits Conference (ISSCC)

◆IEEE Symposium on VLSI Circuits (VLSI)

◆IEEE Custom Integrated Circuits Conference (CICC)

◆IEEE International Symposium on Circuits and Systems (ISCAS)

◆European Solid-State Circuits Conference (ESSCIRC)

◆IEEE Radio Frequency Integrated Circuits Symposium (RFIC)

◆Asian Solid-State Circuits Conference (A-SSCC)

◆IEEE International Microwave Symposium (IMS)

课程内容

考核

●作业(15%)+课程设计(45%)+考试(40%)

●作业:5次作业,每次3分

●课程设计:设计思路和结果、口头报告及文档●考试:开卷考试

课程设计

●课程设计

◆差分功率放大器(或其他RF模块)

●三人为一组,根据项目水平以及各人贡献给分●时间:课后完成,16周课上作口头报告(5分钟),期末考试后提交完整书面设计报告

●提供的资源:工艺库PDK文档、工艺库使用说明、课程设计说明文件、Cadence简单使用文档

●上机:每周三晚上7:30~10:00(第五周起)

◆四次上机培训。