电路设计原理图

设计层次电路原理图

绘制导线 将方块电路以及方块电路端口均放置完成后,还要用导线将这 些方块电路端口连接起来,这样才能使这些方块电路在电气 意义上连接起来。 先单击“连线工具条”中左上角的按钮,然后将光标移至工作 区中,此时鼠标指针上方就会出现一个“十”字光标。将鼠 标光标移到需要绘制导线的地方(“十”字光标随鼠标的的 移动而移动),在导线的起始点单击左键一次,然后在该点 拖动鼠标(左键一直按下),随着鼠标的拖动,工作区中就 会出现一条导线。导线绘制到终点后,单击一次鼠标右键即 可完成该条导线的绘制工作。

图4-1(b)

4.3 层次原理,结合下 图4-2所示实例,介绍绘制层次原理图的一般过程。 图4-2是一个层次原理图,整张原理图表示了 一个完整电路,包含: ◇存储器模块(Memory.sch) ◇CPU模块(CPU.sch) ◇电源模块(Power.sch) ◇CPU时钟模块(CPUClk.sch) ◇并行接口模块(PPI.sch) ◇串行接口模块(Serial.sch)

第4章 设计层次电路原理图

4.1 4.2 4.3 4.4

自上而下设计层次原理图 自下而上设计层次原理图 层次原理图的建立 层次原理图总图/功能电路原理图之间的切换

层次化电路图设计方法实际上是一种模块化的 设计方法。用户可将设计的系统划分为多个子系统, 子系统下面又可划分为若干功能模块,功能模块在 细分为若干基本模块。 设计好基本模块,定义好模块之间的链接关系, 即可完成整个设计过程。

双击绘制的 方块电路就 会弹出一个 属性设置对 话框,如图 3-5所示。 在该属性设 置对话框中 可以对方块 电路的名称、 颜色、边框 宽度、坐标、 大小等参数 进行设置。

绘制完方块电路后,还需要在该方块电路上放置方块 电路端口,才能完成一个方块电路的工作。 单击“连线工具条”上的方块电路端口制作按钮,然 后将光标移至工作区中,此时就会发现鼠标指针上 方有一个“十”字光标,如图3-7(左图)所示。

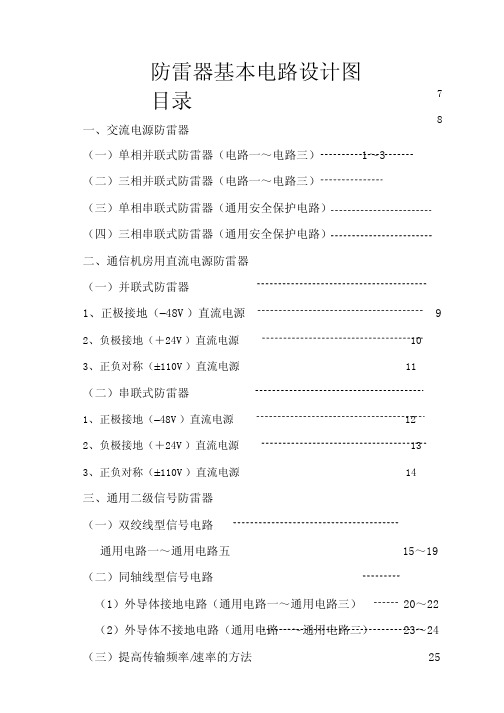

常用防雷电路设计参考原理图

防雷器基本电路设计图目录一、交流电源防雷器(一)单相并联式防雷器(电路一~电路三)1~3 (二)三相并联式防雷器(电路一~电路三)(三)单相串联式防雷器(通用安全保护电路)(四)三相串联式防雷器(通用安全保护电路)二、通信机房用直流电源防雷器(一)并联式防雷器7 81、正极接地(–48V)直流电源92、负极接地(+24V)直流电源103、正负对称(±110V)直流电源11 (二)串联式防雷器1、正极接地(–48V)直流电源122、负极接地(+24V)直流电源133、正负对称(±110V)直流电源14三、通用二级信号防雷器(一)双绞线型信号电路通用电路一~通用电路五15~19 (二)同轴线型信号电路(1)外导体接地电路(通用电路一~通用电路三)20~22 (2)外导体不接地电路(通用电路一~通用电路二)23~24 (三)提高传输频率/速率的方法25四、小功率电源变压器或开关电源保护电路(电路一~电路三)26~28五、通讯电子设备的保护电路(电路一~电路三)六、直流电源与信号同传的保护电路七、信号电路的双重二级保护方式八、检测/控制电路的保护(接地、不接地)九、单级信号防雷器29~313233 34~351、只用玻璃放电管的保护电路362、只用半导体过压保护器的保护电路373、只用TVS 管的保护电路384、复合单级保护电路39十、天馈防雷器1、单级电路天馈防雷器402、二级电路天馈防雷器413、三级电路天馈防雷器42十一、防静电保护器431 一、交流电源防雷器(一)单相并联式防雷器说明:1、优点:电路简单,采用复合对称电路,共模、差模全保护,L、N 可以随便接。

缺点:压敏电阻RV1 短路失效后易引起火灾。

最好在每个压敏电阻上串联一个工频保险丝以防压敏电阻短路起火。

如果L、N 线不可能接反,则可省去压敏电阻RV2、RV3,将放电管G 的上端直接接到N 线上,构成“1+1”电路。

2、压敏电阻的压敏电压值参照下表选取(选压敏电压高一点的更安全、耐用,故障率低,但残压略高);根据通流容量要求选择外形尺寸和封装形式,或采用几个压敏600V。

AltiumDesigner电路设计之原理图设计基础

总结词

元件库缺失是电路设计中最常见的问题 之一,它可能导致设计无法进行或无法 正确进行。

VS

பைடு நூலகம்

详细描述

当设计师在Altium Designer中找不到所 需的元件库时,可以尝试以下解决方案: 1. 检查元件库是否已经正确安装;2. 确 认元件库的路径是否正确;3. 尝试在网 上查找该元件库并下载安装;4. 如果以 上方法都无法解决问题,可以联系 Altium Designer的技术支持寻求帮助。

PROTEL

一款经典的电路设计软件 ,具有丰富的元件库和强 大的布线功能。

02 原理图设计基本元素

电路元件

电阻(Resistor)

电容(Capacitor)

表示电路中电阻的元件,用于限制电流。

表示电路中电容的元件,用于存储电荷。

电感(Inductor)

二极管(Diode)

表示电路中电感的元件,用于存储磁场能 量。

通过原理图,设计师可以清晰 地理解电路的工作原理,便于 后续的电路板设计和调试。

原理图设计通常使用专门的原 理图设计软件,如Altium Designer。

原理图设计流程

收集资料

收集相关的电路元件资料、芯 片数据手册等。

检查与修改

对绘制的原理图进行检查和修 改,确保其正确性和可实现性 。

确定设计目标

模块化设计

详细描述

层次化电路原理图设计是将整个电路按照功能划分为若干个模块,每个模块对应一个子图。这种设计方法有利于 提高电路的可读性和可维护性,便于多人协作设计和项目管理。在设计时,应遵循模块化设计原则,合理划分模 块,明确模块间的接口和信号传递关系。

实例四:混合电路原理图设计

总结词

多种元件与技术融合

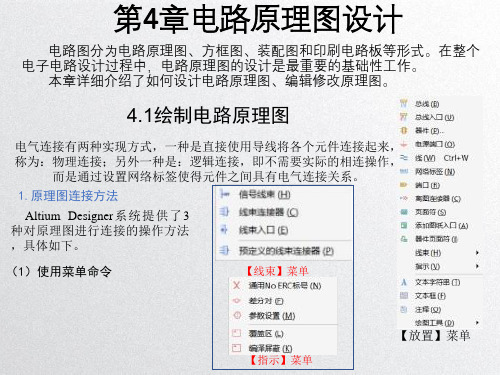

第4章 电路原理图设计

3.设置完毕,单击

按钮,关闭对话框。光标变为十字型,带有一

个定义好的线束连接器,带有端口,且线束入口分类显示,如图所示。

4. 在自动绘制导线状态下,按Tab键,会打开如图所示的【点对点布线选项】对话框 ,可设置绘制导线的定时时间以及避免切割导线的要求。

开始点对点自动绘制导

绘制完成

【点对点布线选项】对话框

5

3.放置电源和地端口

电源端口和地端口是电路原理图中必不可少的组成部分。系统为用户提供了多种 电源和地端口的形式,每种形式都有一个相应的网络标签作为标识。

在Altium Designer系统中,通过执 行【视图】|【工具栏】|【自定义】 命令,单击弹出的Customizing Sch Editor对话框的【工具栏】标签页, 同时在Altium Designer工具栏会出 现一个专用的【原理图快捷键】工 具栏,用于显示所有可用的快捷操 作,如图示。

2

2. 绘制导线 元件之间的电气连接,主要是通过导线来完成。导线是电路原理图中最重要也是 用得最多的图元,它具有电气连接的意义

例:放置总线入口

(1)执行【放置】|【总线入口】命令,或者,单击布线工具栏中的绘制总线入口图 标 ,光标变为十字型,并带有总线入口/或\

开始放置总线入口

(2)按空格键调整总线入口的方向(有 、 、 、 四种选择),移动光标到需要的位置处 (总线与导线之间),连续单击鼠标,即可完成总线入口的放置,如图所示。单击鼠标右键或按 Esc键退出放置状态。

开关电源制作设计(电路原理图+PCB)

一、工作原理我们先熟悉一款开关电源的工作原理,该电源可输出5V电压,如图1所示。

1. 抗干扰电路在电网输入端首先设置一个NTC5D-9负温度系数热敏电阻,作用是保护后面的整流桥,刚开机时热敏电阻处于冷态,阻值比较大,可以限制输入电流,正常工作时,电阻比较小。

这样对开机时的浪涌电流起到有效的缓冲作用。

电容CY1、CY2、CY3、CY4用以滤除从工频电网上进入开关稳压电源和从开关稳压电源进入工频电网的不对称杂散信号,电容CX1、CX2用以滤除从工频电网上进入开关稳压电源和从开关稳压电源进入工频电网的对称杂散信号,用电感L1抑制从工频电网上进入开关稳压电源和从开关稳压电源进入工频电网的频率相同、相位相反的杂散干扰电流信号。

采用高频特性好的瓷片电容和铁芯电感,实现开关稳压电源电路中的高频辐射不污染工频电网和工频电网上的杂散电磁波不会窜入开关稳压电源电路中而干扰和影响其工作,对高频分量或工频的谐波分量具有急剧阻止通过功能,而对于几百赫兹以下的低频分量近似一条短路线。

图1 开关电源的工作原理图2. 整流滤波电路在电路中D1、D2、D3、D4组成全桥整流电路,把输入的交流电压进行全波整流,然后用C1进行滤波,最后变成直流输出供电电压,为后级的功率变换器供电,整流滤波后的电压约为300V。

3. UC3842供电与振荡300V的脉动直流电压,此电压经R12降压后给C4充电,供电UC3842的7脚,当C4的电压达到UC3842的启动电压门槛值时,UC3842开始工作并提供驱动脉冲,由6脚输出推动开关管工作。

一旦开关管工作,反馈绕组的能量经过D6整流,C4滤波,又供电到UC3842的7脚,这时可以不需要R12的启动了。

C9、R11接UC3842的定时端,和内部电路构成振荡电路,振荡的工作频率计算为:f=1.8/(Rt*Ct)代入数据可计算工作频率:f=68.18K4. 稳压电路该电路主要由精密稳压源T L 4 3 1 和线性光耦P C 8 1 7 组成,假设输出电压↑→经过R 1 6 、R 1 9 、R20、RES3的取样电压↑→TL431的1脚电压↑,当该脚电压大于TL431的基准电压2.5V时,TL431的2、3脚导通,→通过光电耦合到UC3842的2脚,于是UC3842的6脚驱动脉冲的占空比↓→开关变压器T1绕组上的能量↓→输出电压↓,达到稳压作用;反之,假设输出电压下降,则稳压过程与上相反。

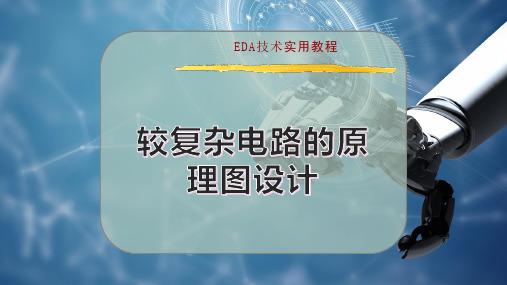

较复杂电路的原理图设计

1.4 频率计顶层电路设计

图6-17 频率计顶层电路原理图(文件:ft_top.gdf)

1.4 频率计顶层电路设计

图6-18 频率计工作时序波形

EDA技术实用教程

图6-12 两位十进制计数器工作波形

Байду номын сангаас

1.2 频率计主结构电路设计

图6-13 两位十进制频率计顶层设计原理图文件

1.2 频率计主结构电路设计

图6-14 两位十进制频率计测频仿真波形

1.3 测频时序控制电路设计

图6-15 测频时序控制电路

较复杂电路的原理图设计

1.3 测频时序控制电路设计

图6-16 测频时序控制电路工作波形

EDA技术实用教程

较复杂电路的原理图设计

1.1 设计有时钟使能的两位十进制计数器

图6-9 用74390设计一个有时钟使能的两位十进制计数器

1.1 设计有时钟使能的两位十进制计数器

图6-10 调出元件7439

图6-11 从Help中了解74390的详细功能

1.1 设计有时钟使能的两位十进制计数器

AD15电路原理图设计 PPT

2.2.2 原理图编辑界面

➢ 1. 主菜单栏

➢2. 标准工具栏

➢3. 布线工具栏

2.2.2 原理图编辑界面

➢ 4. 实用工具栏

➢ 5. 格式化工具栏

➢ 6. 编辑窗口

编辑窗口就是进行电路原理图设计的工作平台。在此窗口内,用户可以新画一个原理图,也可 以对现有的原理图进行编辑和修改。

➢ 7. 【图纸】框

2.6.1 原理图连接方法

➢ 1.使用菜单命令 执行【放置】命令,则弹出菜单列表。 2.使用【布线】工具栏

【放置】菜单中,直接单击该工具栏中的相应图标,即可完成相 同的功能操作。 3.使用快捷键 在Altium Designer系统中,提供了一个专用的【快捷方式】面 板,用于显示所有可用的快捷操作,用户可随时查阅。

2.6.7 放置输入/输出端口

(1)执行【放置】/【端口】命令,光标变为十字型,并带有一个输入输出端口符号。 (2)移动光标到适当位置处,当出现红色米字标志时,表示光标已捕捉到电气连接点。单击鼠 标确定端口的一端位置,然后拖动鼠标使端口的大小合适,再次单击鼠标确定端口的另一端位置, 即完成了输入输出端口的一次放置。 (3)双击所放置的端口(或在放置状态下,按Tab键),打开【端口属性】对话框。 (4)单击鼠标右键或按Esc键即可退出放置状态。

ad15电路原理图设计21电路原理图的设计步骤22原理图编辑环境221创建原理图文件222原理图编辑界面223原理图编辑画面管理224原理图纸的设置225原理图工作区参数设置226元器件库的操作23元器件的放置231使用实用工具栏或菜单命令放置元器件232使用元器件库管理器放置元器件24编辑及调整元器件的属性241元器件属性的编辑242元器件自动标号243快速自动标号与恢复25调整元器件251元器件位置的调整252元器件的简单复制与粘贴253元器件的智能粘贴254元器件的阵列粘贴26绘制电路原理图261原理图连接方法262绘制导线263放置电源和地端口264绘制总线265放置总线入口266放置网络标号267放置输入输出端口268放置线束269放置电气节点2610放置没有erc标志27思考与练习大家学习辛苦了还是要坚持大家学习辛苦了还是要坚持继续保持安静继续保持安静布线工具栏222编辑窗口编辑窗口就是进行电路原理图设计的工作平台

最简单的短路保护电路图汇总(六款模拟电路设计原理图详解)

最简单的短路保护电路图汇总(六款模拟电路设计原理图详解)最简单的短路保护电路图(一)简易交流电源短路保护电路交流电源电压正常时,继电器吸合,接通负载(Rfz)回路。

当负载发生短路故障时,KA两端电压迅速下降,KA释放,切断负载回路。

同时,发光二极管VL点亮,指示电路发生短路。

最简单的短路保护电路图(二)这是一个自锁的保护电路,短路时:Q3极被拉低,Q2导通,形成自锁,迫使Q3截止,Q3截至后面负载没有电压,这时有没有负载已经没有关系了,所以即使拿掉负载也不会有输出。

要想拿掉负载后恢复输出,可以在Q3得CE结上接一个电阻,取1K左右。

C2和C3很重要,在自锁后,重启电路就靠这两个电容,否则启动失败。

原理是上电时,电容两端电压不能突变,C2使得Q2基极在上电瞬间保持高电平,使得Q2不导通。

C3则使得上电瞬间Q3基极保持低电平,使得Q3导通Vout有电压。

这样R5位高电平,锁住导通。

最简单的短路保护电路图(三)缺相保护电路由于电网自身原因或电源输入接线不可靠,开关电源有时会出现缺相运行的情况,且掉相运行不易被及时发现。

当电源处于缺相运行时,整流桥某一臂无电流,而其它臂会严重过流造成损坏,同时使逆变器工作出现异常,因此必须对缺相进行保护。

检测电网缺相通常采用电流互感器或电子缺相检测电路。

由于电流互感器检测成本高、体积大,故开关电源中一般采用电子缺相保护电路。

图5是一个简单的电子缺相保护电路。

三相平衡时,R1~R3结点H电位很低,光耦合输出近似为零电平。

当缺相时,H点电位抬高,光耦输出高电平,经比较器进行比较,输出低电平,封锁驱动信号。

比较器的基准可调,以便调节缺相动作阈值。

该缺相保护适用于三相四线制,而不适用于三相三线制。

电路稍加变动,亦可用高电平封锁PWM信号。

图5 三相四线制的缺相保护电路图6是一种用于三相三线制电源缺相保护电路,A、B、C缺任何一相,光耦器输出电平低于比较器的反相输入端的基准电压,比较器输出低电平,封锁PWM驱动信号,关闭电源。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Note: The 2.5V must be powered up before 3.3V.

4

5VPM VDD33 JP1 L2 VO33 BEAD VDD33 GND + C10 22U C11 + C12 0.1U 100U GND

3

5VPM

1 2 3

5V GROUND LAN_WAKE CONNECTOR

DC2 0.1U

DC3 0.1U

DC4 0.1U

DC5 0.1U

DC6 0.1U

4

GND GND GND GND GND CLK GND REQB AD31 AD29 GND AD27 AD25 CBE3B CBE3B AD23 GND AD21 AD19 AD17 CBE2B GND IRDYB DEVSELB GND PERRB SERRB CBE1B AD14 GND AD12 AD10 GND AD8 AD7 AD5 AD3 GND AD1

U4 5VPM 5VCC VO33 VAUX33 1 2 3 4 Vsby GND Vcc GND Vout GND Vaux GND CMPWR300 8 7 6 5 GND Q1 VCTRL VCTRL 2SB1197K VDD25

3

VDD33

LWAKE

GND

GND

GND

LWAKE

VDD25

+ C17 22U

The 9346 EEPROM should be functional when powered by 3.3V

RTL8139DL

AD[0..16] CBE0B

AD[0..16] AD[24..31] AD[24..31] U2 AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 AD8 AD9 AD10 AD11 AD12 AD13 AD14 AD15 AD16 12 11 10 9 8 7 6 5 27 26 23 25 4 28 29 3 2 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 29C010 I/O0 I/O1 I/O2 I/O3 I/O4 I/O5 I/O6 I/O7 VCC VSS OE WE CE 13 14 15 17 18 19 20 21 32 16 24 31 22 BootROMOE BootROMCS BC1 0.1U GND AD24 AD25 AD26 AD27 AD28 AD29 AD30 AD31 5VCC

1

for EMI supression

2

RXIN+ RXIN-

RXIN+ RXIN-

1 2 3

RD+ RDCT TDCT TD+

C15

0.1U

GND C16 0.1U

TXD-

TXD-

15 14

GND

TXD+

TXD+

16

R13 50

R14 50

1

C23 0.1U GND Title TCL Networks Equipment Co.LTD Size B Date:

4

B2 BEAD C3 0.1U GND

B3 X1 BEAD C4 C1 L1 BEAD CRYSTAL GND VDD33 C5 27pF GND BLOCK 1 GND BLOCK 2 C6 27pF GND

4

R1 OUT2 3 2

33 CLKOUT Y1 25MHz XTALFB

4 1 GND 0.1U

E

Rev 1.10 1 of 4

A

B

C

D

E

Important:

*For lump VAUX, C12 must be large enough to avoid power supply's compatibility *For RTL8139DL application, all bead must be rated 300mA/100ohm@100MHz

CLK

REQB

3

CBE2B IRDYB DEVSELB

PERRB SERRB CBE1B

2

-12V TRST# TCK +12V GND TMS TDO TDI +5V +5V +5V INTA# INTB# INTC# INTD# +5V PRSNT1# N/C N/C +5V PRSNT2# N/C GND GND GND GND N/C VAUX33 GND RST# CLK +5V GND GNT# REQ# GND +5V PME# AD31 AD30 AD29 +3.3V GND AD28 AD27 AD26 AD25 GND +3.3V AD24 CBE3# IDSEL AD23 +3.3V GND AD22 AD21 AD20 AD19 GND +3.3V AD18 AD17 AD16 CBE2# +3.3V GND FRAME# IRDY# GND +3.3V TRDY# DEVSEL# GND GND STOP# LOCK# +3.3V PERR# N/C +3.3V N/C SERR# GND +3.3V PAR CBE1# AD15 AD14 +3.3V GND AD13 AD12 AD11 AD10 GND GND AD9 AD8 AD7 +3.3V AD5 AD3 GND AD1 +5V ACK64# +5V +5V PCIJB CBE0# +3.3V AD6 AD4 GND AD2 AD0 +5V REQ64# +5V +5V PCIJA

VCC

OUT1 GND OSC 25MHz

0.1U

0.1U

RXINRXIN+ TXDTXD+ R2 5VCC R3 15K GND GND 1K (ISOLATEB)

LWAKE CLKOUT XTALFB PMEB VCTRL

B4 C9 R6 5.6K 1% 0.1U GND PMEB GND VCTRL ModemGNTB ModemREQB

0 VDD25 VDD25

GND CLKOUT XTALFB

R4

510

LED2 LWAKE LED RXIN+ RXINGND ISOB GND TXD+ TXD-

3

VDD25

3

75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51

1 1

Title TCL Networks Quipment Co., LTD Size B Date:

A B C D

Document Number NIC 10/100BASE 8139DL Sunday, June 22, 2003 Sheet

E

Rev 1.10 4 of 4

A

B

C

D

E

VDD33 B1 BEAD C2 GND

R5 VDD33

510

LED1 LED

U1 R8 R9 AUX EECS EESK EEDI EEDO AD0 AD1 GND AD2 AD3 NC VDD AD4 AD5 AD6 BROMOE VDD AD7 CBE0B GND AD8 AD9 AD10 AD11 AD12 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 AUX EECS EESK EEDI EEDO AD0 AD1 GND AD2 AD3 VDD33 AD4 AD5 AD6 BootRomOE VDD33 AD7 CBE0B GND AD8 AD9 AD10 AD11 AD12 5.6K VAUX33 5.6K 5VPM 5VPM EECS EESK EEDI EEDO 1 2 3 4 CS SK DI DO U2 VCC NC NC GND 9346 8 7 6 5 VDD33 BC1 GND 0.1U GND VAUX33

C18 0.1U

GND

GND

C13 0.1U GND R11 50

2

C14 0.1U

GND

R12 50 U5 1 U6 RX+ CT RXTXCMT TX+ PE68515 7 2 5 3 6 4 11 5 12 6 10 7 8 TX+ TXRX+ N/C N/C RXN/C N/C RJ8-45 GND 9 CH_GND R16 75 R17 75 R18 75 R19 75 C21 0.01U/3KV ( C O N N E C T TO CHASSIS GND)

A B C D

Document Number NIC 10/100 BASE 8139DL Sunday, June 22, 2003 Sheet

E

Rev 1.10 2 of 4

A

B

C

D

E

5VCC AD[0..31] AD[0..31]

5VCC VDD33 VDD33

4

DC1 JB1 GND TDO 5VCC 5VCC 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 52 53 54 55 56 57 58 59 60 61 62 JA1 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 52 53 54 55 56 57 58 59 60 61 62 0.1U