集成计数器及寄存器共23页

北京科技大学数电实验四 Quartus II集成计数器及移位寄存器应用

北京科技大学实验报告学院:高等工程师学院专业:自动化(卓越计划)班级:自E181姓名:杨威学号:41818074 实验日期:2020 年5月26日一、实验名称:集成计数器及其应用1、实验内容与要求(1)用74161和必要逻辑门设计一个带进位输出的10进制计数器,采用同步置数方法设计;(2)用两个74161和必要的逻辑门设计一个带进位输出的60进制秒计数器;2、实验相关知识与原理(1)74161是常用的同步集成计数器,4位2进制,同步预置,异步清零。

引脚图功能表其中X。

3、10进制计数器(1)实验设计1)确定输入/输出变量输入变量:时钟信号CLK、复位信号CLRN;输出变量:计数输出QD、QC、QB、QA,进位输出RCO,显示译码输出OA、OB、OC、OD、OE、OF、OG2)计数范围:0000-10013)预置数值:00004)置数控制端LDN:计数到1001时输出低电平5)进位输出RCO:计数到1001时输出高电平画出如下状态转换表:CP QDQCQBQA0 00001 00012 00103 00114 01005 01016 01107 01117 10009 100110 0000(2)原理图截图仿真波形如下功能验证表格CLRN QD QC QB QA RCO0 0 0 0 0 01 0 0 0 1 01 0 0 1 0 01 0 0 1 1 01 0 1 0 0 01 0 1 0 1 01 0 1 1 0 01 0 1 1 1 01 1 0 0 0 01 1 0 0 1 11 0 0 0 0 04、60进制秒计数器(1)实验设计1)确定输入/输出变量输入变量:时钟信号CLK、复位信号CLRN;输出变量:计数十位输出QD2、QC2、QB2、QA2和计数个位输出QD1、QC1、QB1、QA1,进位输出RCO2)计数范围:0000 0000-0101 10013)预置数值:0000 00004)置数控制端LDN1(个位):计数到0101 1001时输出低电平5)清零端CLRN2(十位):计数到0110时输出低电平6)ENT:个位计数到1001时输出高电平7)进位输出RCO:计数到1001时输出高电平画出如下状态转换表CP QD2QC2QB2QA2QD1QC1QB1QA1CPQD2QC2QB2QA2QD1QC1QB1QA1CPQD2QC2QB2QA2QD1QC1QB1QA10 0000 0000 20 0010 0000 40 0100 00001 0000 0001 21 0010 0001 41 0100 00012 0000 0010 22 0010 0010 42 0100 00103 0000 0011 23 0010 0011 43 0100 00114 0000 0100 24 0010 0100 44 0100 01005 0000 0101 25 0010 0101 45 0100 01016 0000 0110 26 0010 0110 46 0100 01107 0000 0111 27 0010 0111 47 0100 01118 0000 1000 28 0010 1000 48 0100 10009 0000 1001 29 0010 1001 49 0100 100110 0001 0000 30 0011 0000 50 0101 000011 0001 0001 31 0011 0001 51 0101 000112 0001 0010 32 0011 0010 52 0101 001013 0001 0011 33 0011 0011 53 0101 001114 0001 0100 34 0011 0100 54 0101 010015 0001 0101 35 0011 0101 55 0101 010116 0001 0110 36 0011 0110 56 0101 011017 0001 0111 37 0011 0111 57 0101 011118 0001 1000 38 0011 1000 58 0101 100019 0001 1001 39 0011 1001 59 0101 100160 0000 0000 (2)设计原理图截图(3)实验仿真仿真波形:仿真结果表:5、实验思考题:(1)总结任意模计数器的设计方法。

集成计数器及寄存器

实验六 集成计数器及寄存器及寄存器

五、实验报告

1. 整理实验内容和各实验数据。 2.画出实验内容上、2所要求的电路图及波形图。

3.总结计数器使用特点。

实验六 集成计数器及寄存器

下次预习内容

实验八 波形产生及单稳态触发器

实验六 集成计数器及寄存器

六、实验结束

出 2 分频信号,即实现二进制计数。当 1不加信号,计数脉冲从 CP2码,最高位 输入时, D、 码接法,先模 5计数,后模2计数,由 QACP 、Q D、 QC、 Q01 B、 输出 5421 BCD 置 9 都是异步操作,而且置 9是优先的,所以称 R R02 为异步清 0端,SQ 91 、 、QB实现五进制计数。 Q AC 作进位输出,波形对称。 SQ 为异步置 9端。

92 91 92 01 02

实验六 集成计数器及寄存器

四、实验内容

1、集成计数器74LS90功能测试。 • 74LS90 是二一五一十进制异步计数器。具有下述功能: 1)直接置0(R0(1) •R0(2) =1),直接置9(S9(1) •S9(2) =1) 2)二进制计数(Cp1输入;Qa输出) 3)五进制计数(CP2输入 ;Qd,Qc,Qb输出)

清 0 0 × 1 置 9 × 0 1 时 CP1 × × ↓ 钟 CP2 × × 1 ↓ QA ↓ R0(1)、R0(2) 1 0 × 1 × 0 S9(1)、S9(2) QD 0 1 QA

输 QC 0 0 输

出 QB 0 0 0 1 出 QA 功 能

异步清 0 异步置 9 二进制计数 五进制计数 十进制计数 十进制计数

注意:

R0 均为高电平有效 0 、R9 × 0 × × 为下降沿触发 0 × 0 CP

1 ↓ QD

NO52同步时序电路

QA QB QC QD CP S1

CLR 74LS194 S0

RABCDL

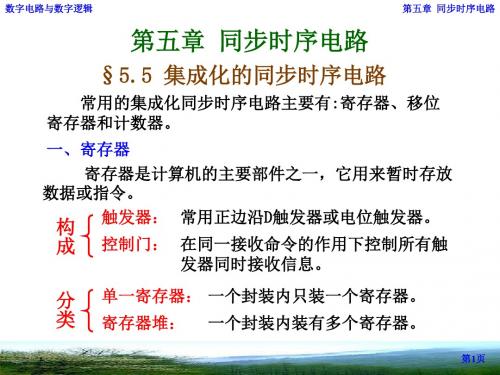

第五章 同步时序电路

R—右移串行输入 L—左移串行输入 A、B、C、D—

并行输入

12 3 4567 8

CLR R A B C D L GND

CLR CK S1 S0

0

功

能

直接清零

1 2 3 4 5 6 7 8 9 10

输出 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND

控制

八D寄存器 :三态输出

低电平 有效

共输出控制 共时钟

第5页

数字电路与数字逻辑

2.寄存器堆

第五章 同步时序电路

第6页

数字电路与数字逻辑

第五章 同步时序电路

第7页

数字电路与数字逻辑

根据移位数据的输 FF 入-输出方式,又 可将它分为四种:

Q3

F3 1D C1 Rd

Q2

F2 1D C1 Rd

Q1

F1 1D C1 Rd

置0

D1

D2

D3

D4

Rd是异步清零控制端。 输入

D1~D4是并行数据输入端,CK为时钟脉冲端。

Q1~Q4是并行数据输出端。

CK

第3页

数字电路与数字逻辑

输出

Q4

F4 Sd 1D C1Rd

Q3

F3 Sd 1D C1Rd

Q2

F2 Sd 1D C1 Rd

(3)按计数器中触发器翻转是否与计数脉冲同 步分为同步计数器和异步计数器。

第26页

数字电路与数字逻辑

第五章 同步时序电路

1.二进制同步计数器 (1)二进制同步加法计数器

数字集成电路中的基本模块演示文稿

VDD C3

C0

C1

C2

C3

在预充电阶段(Ø=0),传输管进位链中的所有中间节点都被预充电到

VDD,在求值阶段,当有输入进位且传播信号为PK为高电平,或进位产

设计生运算信功能号块(. 28GK)为高电平,节点CK放电

第28页,共83页。

• 棍棒图

数据通道版图由三排组织成位片式的单元组成:

Propagate/Generate Row

• 数据通路常常组织成位片式结构 • 每一个对一位进行操作——位片式

设计运算功能块. 7

第7页,共83页。

设计运算功能块. 8

第8页,共83页。

(二) 数据通路的特点:(它在很大程度上决定了整个系统的性 能) •规整性:(Bit-slice)优化版图

•局域性:(时间、空间,算子相邻布置)版图紧凑

设计运算功能块. 14

第14页,共83页。

加法器的反向特性

设计运算功能块. 15

第15页,共83页。

逐位(行波、串行)进位加法器

(1)结构:一个N位加法器可以通过把N个一位的全加器电路串联起来构成,第i 级的 Carry−out用来产生第i+1 级的 SUM和Carr y (2 )特点:结构直观简单,运行速度慢,最坏情形下关键路径的

FA

FA

FA

FA

P0 G1

P0 G1

P2 G2

P3 G3

BP=P oP1P2P3

Ci,0

C o,0

Co,1

C o,2

FA

FA

FA

FA

C o,3

Multiplexe页,共83页。

例11.3 曼彻斯特进位链加法器中的进位旁路

P0

西门子200smart编码器高速计数器

上述脉冲当量的计算只是理论上的推算。实际上各种误差因素不

可避免,例如传送带主动轴直径(包括皮带厚度)的测量误差,传送带 的安装偏差、张紧度,系统在工作台面上定位偏差等等,都将影响理论 计算值。脉冲当量的误差所引起的累积误差会随着工件在传送带上运动 距离的增大而迅速增加,甚至达到不可容忍的地步。须现场测试脉冲当 量值。

(HSC)指 令根

据 HSC 特 殊 内

存 位 的状 态 配 置 和控 制 高 速 计数

器。参 数 N指 定 高 速 计数 器 的 号 码。

第27页,共46页。

读取高速计数器当前值

欲存取高速计数器的计数值,您需要利用内

存类型(HC)和计数器号码(例如HC0)指定

高速计数器的地址。如下所示,高速计数器的

1 = 异常中止 1 = 异常中止

PTO管线溢出/下溢

0 = 无溢出; 1 = 溢出/下溢

PTO空闲

0 = 进行中;

1 = PTO空闲

第38页,共46页。

高速输出关联特殊寄存器

Q0.0 SM67.0 SM67.1 SM67.2 SM67.3 SM67.4 SM67.5 SM67.6 SM67.7

编码器

知识拓展-编码器

脉冲和脉冲当量

计算工件在传送带上的位置时,需确定每两个脉冲之间的距离即脉冲当 量。若某主动轴的直径为d=43 mm,则减速电机每旋转一周,皮带上工件移

动距离L=π•d=3.14×43=136.35 mm。若分辨率500 线,及旋转一周脉冲数

为500,故脉冲当量μ为μ=L/500≈0.273 mm。

SMB36至SMB65被用于监控和控制高速计数器HSC0、 HSC1和HSC2;

SMB136至SMB165被用于监控和控制高速计数器HSC3 、HSC4和HSC5。 下面,我们就对相应的特殊寄存器进行介绍

寄存器与计数器最新课件

H

×

× × ×××× L L L L

L

L

×

× ABCDA BCD

L

H

H ××××

加计数

L

H

H

××××

减计数

寄存器与计数器最新课件

49

6.4.2 集成同步非二进制计数器

其产品多以BCD码为主,下面以典型产品 74LS192为例讨论。

寄存器与计数器最新课件

50

寄存器与计数器最新课件

51

74LS192具有以下功能: (1) CLR=1时异步清零,它为高电平有效。 (2) CLR=0(异步清零无效)、LD=0时异步置数。 (3) CLR=0,LD=1(异步置数无效)且减法时钟 CPD=1时,则在加法时钟CPU上升沿作用下,计数 器按照8421BCD码进行递增计数:0000~1001。 (4) CLR=0,LD=1且加法时钟CPU=1时,则在减 法时钟CPD上升沿作用下,按照8421BCD码进行 递减计数:1001~0000。

6.1.1 寄存器

在数字电路中,用来存放二进制数据或代码的

电路称为寄存器 。

1

0

1

0

1

0

1

上述寄存器的寄存时间?

寄存器与计数器最新课件

0

1

集成寄存器74LS175

寄存器与计数器最新课件

2

74LS175真值表

课外查资料:了解集成寄存器74LS373与 74LS374。

寄存器与计数器最新课件

3

6.1.2 移位寄存器

进制);

寄存器与计数器最新课件

56

(4) 计数器为异步清零,R0(1)、R0(2)是清零输入端,且高电 平有效。

因此,74LS93实际上是一个二-八-十六进制异步加法 计数器,采用反馈清零法可构成小于十六的任意进制异步加 法计数器。

【精选】集成计数器寄存器 doc资料

集成计数器寄存器实验五 集成计数器寄存器一、实验目的1.熟悉集成计数器逻辑功能和各控制端作用。

2.掌握计数器使用方法。

二、实验仪器及材料1. 双踪示波器2. 器件 74LS290 十进制计数器 2片 74LS00 二输入端四与非门1片。

三、实验内容及步骤1.集成计数器74LS290功能测试。

74LS290是二一五一十进制异步计数器。

逻辑简图为图5.1所示:74LS290具有下述功能:直接置0(R0(1).R0(2)=1),直接置9(S 9(1).S 9(2)=1)二进制计数(CP1输入Q A 输出),五进制计数(CP 2输入Q D Q C Q B 输出) 十进制计数(两种接法如图5.2A 、B 所示)按芯片引脚图分别测试上述功能,并列入表5.1、表5.2、表5.3中。

R R 1) 2)图5.1 74LS290逻辑图(A)十进制(B)二一五混合进制图5.2 十进制计数器2.分别用2片74LS290计算器级连成二一五混合进制、十进制计数器。

(1)画出连线电路图。

(2)按图接线,并将输出端接到发光二极管的相应输入端,用单脉作为输入脉冲验证是否正确。

(3)画出四位十进制计数器连接图并总结多级计数连规律。

表5.1 功能表表5.2 二一五混合进制表5.3 十进制四、实验报告1.整理实验内容和各实验数据。

2.画出实验内容1、2所要求的电路图及波形图。

3.总结计数器使用特点。

ARM微处理器有37个32位长的寄存器,其中包括30个通用寄存器,6个状态寄存器和一个程序计数器寄存器(PC)。

如图3.2所示,ARM微处理器中将这37个寄存器分成不同的组,在ARM微处理器的每种工作模式下只能使用其中一组寄存器。

我们知道,ARM微处理器共有7种模式,其中用户模式和系统模式拥有物理空间上完全相同的寄存器,而其它5种异常模式都有一些自己独立的寄存器。

从图上可以看出,在用户和系统模式下可以使用R0-R15和CPSR共17个寄存器;在FIQ模式下可以使用R0-R15,CPSR,CP SR共18个寄存器,其中R8-R14以及SPSR寄存器是FIQ模式专有寄存器,其它寄存器和用户模式共用相同的物理寄存器;在IRQ、SVC、Undef、Abort模式下可以使用的寄存器都是18个(R0-R15,CPSR,SPSR),其中R13,R14,CPSR是各个模式专有的,其它和用户模式共用相同的物理寄存器。

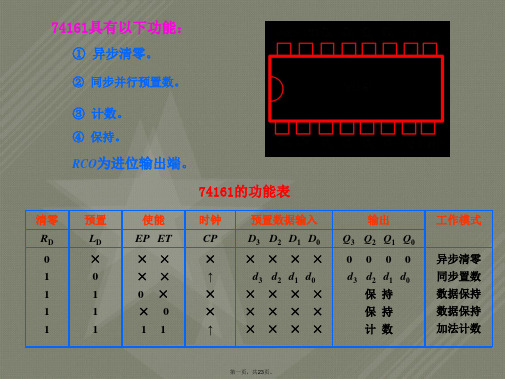

74LS161的逻辑功能-谭

表5-14 74LS161的功能表

异步清0功 能最优先

CP上升 沿有效

同步并 行置数

CO= Q3 Q2 Q1 Q0 CTT

第六页,共23页。

图5-22 74LS161的时序图

第七页,共23页。

2.应用举例

(1)同步二进制加法计数

返回

实现四位二进制加法计数

1/9/2022

8

第八页,共23页。

(2)构成16以内的任意进制加法计数器: ① 设计思想:利用脉冲反馈法 用S0,S1,S2…,SM…SN表示输入0,1,2,…,

触发器的 CP之间的 型号

关系

74X160

74X161

74X162

同步

74X163

74X190

74X191

74X192

74X193

74X290

74X293

异步

74X90

74X92

1/9/2022 74X93

计数模式

清零方式

预置数方式

十进制 “加” 计数器

异步(低电平有效) 同步(低电平有效)

4 位二进制“加” 计数器 异步(低电平有效) 同步(低电平有效)

有进位时,高位计数功能T =1; 无进位时,高位保持功能T =0。

第十五页,共23页。

用两片CT74LS161级联成16×16进制同步加法计数器

低位片

高位片

在计到1111以前,CO1=0,高位片保持原状态不变 在计到1111时,CO1=1,高位片在下一个CP加一

② 再用脉冲反馈法

第十六页,共23页。

二-八-十六进制“加” 计数器 异步(高电平有效)

无

二-五-十进制“加” 计数器 异步(高电平有效) 预置 9,异步(高电平有效)