IC老化测试

IC_测试报表(包括ESD、老化测试以及所对应的适用标准_Excel格式)Process_reliability

Stress condition

Vcc+10%,125 ° C, 48hours Vcc+10%,125 ° C, 1000hours

Sample size

500DUTs/lot

lots

3

Read out(hrs/eye)

0/48hours

Spec(fail/ss) lot 1/500 Cum 2/1500

3

---

EM TS

Electromigration Thermal shock

电流密度J=1~5E6A/CM2 温度=175° C -65 ° C to 151 ° C(liquid to liquid)

20DUTs(metal line, via Co,stack patterns) 77DUTs/lot

THB

Temperature Humidity Bias

85 ° C/85%RH, 1000 hours

77DUTs/lot

3

0,168,500,1000hours

1/77

2/231

JESD22-A101

TC

Temperature Cycling test

1. -65 to 150 ° C (Condition C) 500 total cycles or 2. -55 to 125 ° C (Condition B) 1000 total cycles 121± 2° C/100%RH/2atm Condition Duration: A 24 hours (-0,+2) B 48 hours (-0, +2) C 96 hours (-0, +5) D 168 hours (-0, +5) E 240 hours (-0, +8) F 336 hours (-0, +8). Step 1 : TCT(-65° C/150° C, 5 cycles) Step 2 : Bake(125° C, 24 hours) Step 3 : Soak(30° C/60%RH, 192 hours) Step 4 : IR reflow ( 260 ° C ), 3 Passes. Step 5: Scanning Acoustic Microscopy HBM or MM HBM: >+/-2000v MM: >+/-100V Class1--Room Temperature: V-test: >+/-1.5Vcc; I-test: >+/-1.5Icc; Class2--Maximum Ambient Temperature: V-test: >+/-1.5Vcc; I-test: >+/-1.5Icc; NMOS and PMOS :Vg at Max.Isub@RT

海思芯片HTOL老化测试技术规

HTOL测试技术规范拟制:克鲁鲁尔审核:批准:日期:2019-10-30历史版本记录适用范围:该测试它以电压、温度拉偏方式,加速的方式模拟芯片的运行状况,用于芯片寿命和长期上电运行的可靠性评估。

本规范适用于量产芯片验证测试阶段的HTOL老化测试需求。

简介:HTOL(High Temperature Operating Life)测试是芯片电路可靠性的一项关键性的基础测试,它用应力加速的方式模拟芯片的长期运行,以此评估芯片寿命和长期上电运行的可靠性,通常称为老化测试。

本规范介绍DFT和EVB两种模式的HTOL测试方法,HTOL可靠性测试工程师需要依据实际情况选择合适的模式完成HTOL测试。

引用文件:下列文件中的条款通过本规范的引用而成为本规范的条款。

凡是注日期的引用文件,其随后所有的修改单(不包括勘误的内容)或修订版均不适用于本规范,然而,鼓励根据本规范达成协议的各方研究是否可使用这些文件的最新版本。

凡是不注日期的引用文件,其最新版本适用于本规范。

1. 测试流程1.1 HTOL测试概要HTOL主要用于评估芯片的寿命和电路可靠性,需要项目SE、封装工程师、可靠性工程师、硬件工程师、FT测试工程师共同参与,主要工作包括:HTOL向量、HTOL测试方案、HTOL环境调试、HTOL测试流程执行、测试结果分析、失效定位等。

HTOL可以用两种方式进行测试:DFT测试模式和EVB测试模式。

1.2 DFT和EVB模式对比DFT(Design For Testability)测试模式:集成度较高的IC一般有DFT设计,其HTOL模式一般在DFT测试模式下进行,以扫描链、内建BIST、内部环回、JTAG,实现内部逻辑的翻转、读写、自测试和IO的翻转等,其数字逻辑、memory、IP、IO的以串行方式运行。

EVB(Evaluation Board)功能模式:即正常应用模式,HTOL也可以在该模式下更符合实际应用场景,该模式下芯片各模块一般按照真实的应用场景并行运行。

电子元器件老化测试项目及注意事项

电子元器件老化测试项目及注意事项电子产品在加工过程中,由于经历了复杂的加工和元器件物料的大量使用,无论是加工缺陷还是元器件缺陷,都可分为明显缺陷和潜在缺陷,明显缺陷指那些导致产品不能正常工作的缺陷,例如短路/断路。

而潜在缺陷导致产品暂时可以使用,但在使用中缺陷会很快暴露出来,产品不能正常工作。

潜在缺陷则无法用常规检验手段发现,而是运用老化的方法来剔除。

如果老化方法效果不好,则未被剔除的潜在缺陷将最终在产品运行期间以早期失效(或故障)的形式表现出来,从而导致产品返修率上升,维修成本增加。

一、概念老化(Burn in)是指在一定的环境温度下、较长的时间内对元器件连续施加环境应力,而环境应力筛选(ESS:Environment Stress Screen )则不仅包括高温应力,还包括其他很多应力,例如温度循环、随机振动等,通过电-热应力的综合作用来加速元器件内部的各种物理、化学反应过程,促使隐藏于元器件内部的各种潜在缺陷及早暴露,从而达到剔除早期失效产品的目的。

老化是属于环境应力筛选的一种。

二、作用1.对于工艺制造过程中可能存在的一系列缺陷,如表面沾污、引线焊接不良、沟道漏电、硅片裂纹、氧化层缺陷和局部发热点等都有较好的筛选效果。

2.对于无缺陷的元器件,老化也可促使其电参数稳定。

三、老化测试项目主要的老化试验项目是:1、光老化测试:光老化是户外使用材料受到的主要老化破坏,对于室内使用材料,也会受到一定程度的光老化。

模拟光老化主要的三种灯源各有优异,碳弧灯最早发明使用,建立的测量体系较早、很多日本标准和纤维材料方面的标准都使用碳弧灯,但由于碳弧灯价格较高、性能不够稳定(灯管使用90小时后需要更换),已经逐渐被氙弧灯、紫外灯代替。

氙灯在模拟自然光方面有较大优势,价格也相对较低,适合多数产品的使用。

紫外灯产生的是400nm以下的光,能较好地加速模拟自然光中紫外线对材料的破坏作用,加速因子比氙灯要高,光源稳定性也比氙灯要好,但容易产生非自然光产出的破坏(尤其是UVB灯)。

IC可靠性测试项目及参考标准

IC产品的质量与可靠性测试(IC Quality & Reliability T est)质量(Quality)和可靠性(Reliability)在一定程度上可以说是IC产品的生命。

质量(Quality)就是产品性能的测量,它回答了一个产品是否合乎规格(SPEC)的要求,是否符合各项性能指标的问题;可靠性(Reliability)则是对产品耐久力的测量,它回答了一个产品生命周期有多长,简单说,它能用多久的问题。

所以说质量(Quality)解决的是现阶段的问题,可靠性(Reliability)解决的是一段时间以后的问题。

知道了两者的区别,我们发现,Quality的问题解决方法往往比较直接,设计和制造单位在产品生产出来后,通过简单的测试,就可以知道产品的性能是否达到SPEC的要求,这种测试在IC的设计和制造单位就可以进行。

相对而言,Reliability的问题似乎就变的十分棘手,这个产品能用多久,谁能保证产品今天能用,明天就一定能用?为了解决这个问题,人们制定了各种各样的标准,如: JESD22-A108-A、EIAJED- 4701-D101,注:JEDEC(Joint Electron Device Engineering Council)电子设备工程联合委员会,,著名国际电子行业标准化组织之一;EIAJED:日本电子工业协会,著名国际电子行业标准化组织之一。

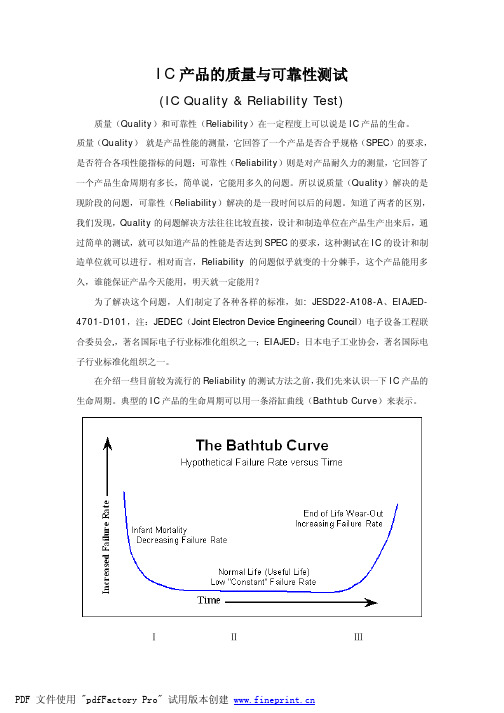

在介绍一些目前较为流行的Reliability的测试方法之前,我们先来认识一下IC产品的生命周期。

典型的IC产品的生命周期可以用一条浴缸曲线(Bathtub Curve)来表示。

ⅠⅡⅢØRegion (I) 被称为早夭期(Infancy period)这个阶段产品的failure rate 快速下降,造成失效的原因在于IC设计和生产过程中的缺陷;ØRegion (II) 被称为使用期(Useful life period)在这个阶段产品的failure rate保持稳定,失效的原因往往是随机的,比如温度变化等等;ØRegion (III) 被称为磨耗期(Wear-Out period)在这个阶段failure rate 会快速升高,失效的原因就是产品长期使用所造成的老化等。

电子产品工作寿命实验

工作寿命实验(OLT)IC 工作寿命试验(Operating Life Test)为利用温度及电压加速的方法,藉由短时间的试验来评估IC的在长时间可工作下之寿命,典型的浴缸曲线(Bathtub Curve)分成早夭期(Infant Mortality)及可使用期(Useful Life)和老化期(Wear out),对于不同区段的故障率评估皆有其相对应的试验手法。

常见的工作寿命试验方法有:BI(Burn-in) / ELFR(Early Life Failure Rate)⎝评估早夭阶段的故障率或藉由BI手法降低出货的早夭率,一般用DPPM(Defect Parts Per-Million)表示。

HTOL(High Temperature Operating Life)⎝评估可使用期的寿命时间,一般用FIT或MTTF表示。

TDDB(Time dependent Dielectric Breakdown)/HCI(Hot Carrier Injection)/EM(Electromigration)等试验评估各种材料在老化期的寿命表现。

对于不同的产品属性也有相对应的测试方法及条件,如HTGB(High Temperature Gate Bias) / HTRG(High Temperature Reverse Bias) /BLT(Bias Life Test) / IOL(Intermittent Operation Life)等试验手法。

上述各项实验条件均需要施加电源或信号源使得组件进入工作状态或稳态,经由电压/温度及时间的加速因子(Acceleration Factor)交互作用下达到材料老化的效果,并藉由试验结果计算出预估产品的故障率及FIT(Failure In Time)和MTTF(Mean Time To Failure)。

近年来较热门的议题为IC工作寿命的故障涵盖率,利用具备深向内存的预烧系统来执行IC的工作寿命实验,使其在固定的试验时间内的提高IC内逻辑闸的Toggle Rate,IC的寿命试验的Fault Coverage提升后可靠度自然也相对提升。

芯片的老化测试原理

芯片的老化测试原理芯片的老化测试是为了评估芯片在长期使用过程中的可靠性和稳定性,主要是通过模拟芯片在长时间工作状态下的加速老化试验来进行。

老化测试的目的是发现芯片可能存在的性能退化、工作异常、失效等问题,以便在芯片进入大规模生产之前及时修正和改进。

芯片老化测试的原理主要包括两个方面:加速老化试验和可靠性评估。

加速老化试验是通过对芯片进行加速老化处理,让芯片在短时间内暴露于高温、高电压、高频率等应力环境下,模拟芯片在长期使用过程中所遇到的各种极端条件,以达到加速芯片老化的目的。

常用的加速老化试验方法主要有温度老化、电压老化、频率老化等。

其中,温度老化试验是指将芯片暴露在高温环境下,通过提高芯片周围环境温度,使芯片的温度升高,模拟芯片在长时间工作下的温度应力。

这是因为芯片在工作过程中会产生热量,如果长时间处于高温环境下,会加速芯片内部结构的变化、元件失效等,从而影响芯片的性能和可靠性。

电压老化试验是指对芯片施加高电压,以模拟芯片在长时间工作下的电压应力。

电压应力会导致芯片内部电场分布的不均匀,从而引发漏电流的增加、介电层破裂等问题,进而影响芯片的稳定性和可靠性。

频率老化试验是指提高芯片的工作频率,模拟芯片长时间工作下的高频应力。

频率应力会引起芯片内部电磁辐射等问题,从而增加信号噪声、干扰等,影响芯片的性能和可靠性。

可靠性评估是在芯片经过加速老化试验后,对芯片进行性能测试和分析,以评估其在长期使用过程中的可靠性。

可靠性评估主要包括温度早期失效、寿命测试、退化分析等。

温度早期失效测试是指在芯片经过加速老化试验后,对芯片进行一系列的温度变化测试,以检测芯片在不同温度条件下的性能变化。

寿命测试是指对芯片进行长时间稳定工作测试,以评估芯片的寿命和可靠性。

退化分析是通过对芯片的性能数据进行分析,找出芯片在老化过程中可能存在的问题,从而优化设计和工艺等方面。

总结起来,芯片的老化测试原理主要包括加速老化试验和可靠性评估。

IC芯片的检测方法大全

芯片的检测方法一、查板方法:1.观察法:有无烧糊、烧断、起泡、板面断线、插口锈蚀。

2.表测法:+5V、GND电阻是否是太小(在50欧姆以下)。

3.通电检查:对明确已坏板,可略调高电压0.5-1V,开机后用手搓板上的IC,让有问题的芯片发热,从而感知出来。

4.逻辑笔检查:对重点怀疑的IC输入、输出、控制极各端检查信号有无、强弱。

5.辨别各大工作区:大部分板都有区域上的明确分工,如:控制区(CPU)、时钟区(晶振)(分频)、背景画面区、动作区(人物、飞机)、声音产生合成区等。

这对电脑板的深入维修十分重要。

二、排错方法:1.将怀疑的芯片,根据手册的指示,首先检查输入、输出端是否有信号(波型),如有入无出,再查IC的控制信号(时钟)等的有无,如有则此IC坏的可能性极大,无控制信号,追查到它的前一极,直到找到损坏的IC为止。

2.找到的暂时不要从极上取下可选用同一型号。

或程序内容相同的IC背在上面,开机观察是否好转,以确认该IC是否损坏。

3.用切线、借跳线法寻找短路线:发现有的信线和地线、+5V或其它多个IC不应相连的脚短路,可切断该线再测量,判断是IC问题还是板面走线问题,或从其它IC上借用信号焊接到波型不对的IC上看现象画面是否变好,判断该IC的好坏。

4.对照法:找一块相同内容的好电脑板对照测量相应IC的引脚波型和其数来确认的IC是否损坏。

5.用微机万用编程器(ALL-03/07)(EXPRO-80/100等)中的ICTEST软件测试IC。

三、电脑芯片拆卸方法:1.剪脚法:不伤板,不能再生利用。

2.拖锡法:在IC脚两边上焊满锡,利用高温烙铁来回拖动,同时起出IC(易伤板,但可保全测试IC)。

3.烧烤法:在酒精灯、煤气灶、电炉上烧烤,等板上锡溶化后起出IC(不易掌握)。

4.锡锅法:在电炉上作专用锡锅,待锡溶化后,将板上要卸的IC浸入锡锅内,即可起出IC又不伤板,但设备不易制作。

5.电热风枪:用专用电热风枪卸片,吹要卸的IC引脚部分,即可将化锡后的IC起出(注意吹板时要晃动风枪否则也会将电脑板吹起泡,但风枪成本高,一般约2000元左右)作为专业硬件维修,板卡维修是非常重要的项目之一。

集成电路芯片封装测

2 0 0 8 级毕业生毕业设计(论文)设计课题:集成电路芯片封装测试的工艺流程专业∶班级∶姓名∶指导老师∶前言本次毕业设计的课题是集成电路芯片封装测试的工艺流程。

在集成电路芯片的制造过程中,由于温度、噪音、空气中的微粒、人为的操作失误及机器设备的误差,致使外表看上去很完美的芯片内部有可能出现开短路的情况,严重影响芯片的质量,因此,在集成电路芯片封装测试中,电性能测试就是为了检查芯片是否存在上述现象。

本次设计是将芯片放入机器里,根据事先存好的芯片测试程序,在特定的高温环境下对芯片进行相应的测试,看测试出来的数据是否符合芯片的标准。

在整个测试流程中,电性能测试是相当重要的,所有的芯片在推向市场以前必须经过电性能测试。

摘要本次设计包括第一章集成电路设计概述,主要陈述了集成电路(IC)的发展,当前国际集成电路技术发展趋势,我国微电子技术的发展现状;集成电路制造材料概述,其中包括半导体材料、绝缘体材料、金属材料、材料系统等等;集成电路制造工艺流程,外延生长,掩膜的制版工艺,光刻,刻蚀,掺杂,绝缘层的形成,金属层的形成;第二章是集成电路芯片封装,包括以下内容,集成电路芯片封装概述、集成电路芯片封装历程、封装定义及其功能、封装的分类、封装的发展趋势。

第三章是FCBGA的工艺流程,硅片回流(water reflow),粘膜,硅片切割,载体转换,焊剂铺垫,焊膏铺垫,芯片粘贴,回流,助焊剂清除。

第四章是FCBGA的测试工艺流程,半成品仓库(Raw Store),老化板装载/卸载(Board Load/Unload),老化测试(Burn In),电性能测试(Electrical Test),激光印码(Laser Mark),脱水烘烤(Desiccant Bake),焊球粘贴(Ballattach)包装(Pack),最终目测检验(Final Visual Insection)。

第五章是CMT 站点简介,包括以下内容:CMT全称,CMT前后站点简介,CMT站点的四种测试,CMT站点所用到的化学品,C MT站点所用到的几种系统,CMT站点的产品的两条主路径,CMT站点一般安全行为,CMT站点所需要用到的命令,什么叫STD?什么情况下需要运行STD?第六章是电性能测试的过程。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第一章测试座与老化座的区别3、CSP封装量产测试中存在的问题如前所述,CSP封装芯片的量产测试采用类似晶圆测试的方法进行,但是两者的区别在于:晶圆的测试,探针是扎在管芯的PAD(通常情况下为铝金属)上,而CSP封装的测试,探针是扎到CSP封装的锡球上。

问题由此产生,在晶圆测试中铝质的PAD对探针污染很小,测试过程中不需要经常对探针进行清洁(一般测试几百上千颗进行在线清针一次即可),而CSP封装的锡球对探针污染非常严重,特别是在空气中放置一段时间后,加重了锡球的氧化,对探针的污染就更为严重,另外流过探针的电流大小也会直接影响探针和锡球之间的电气接触。

这样对探针的抗粘粘度及抗氧化能力要求很高,对于一般的探针,测试几十颗就需要对其进行清洁,否则随着沾污越来越严重,会造成探针与锡球之间的接触电阻大到2欧姆以上(一般情况下在0.5欧姆以下),从而严重影响测试结果。

对于本文所举实例而言,在负载电阻仅为8.2欧姆的情况下,这样测试得到的VOP-P及PO值仅为真实值的8.2/(8.2+2+2),既0.672倍左右,从而导致测试的严重失效,同时也会影响到THD测试值。

所以在测试过程中需要对探针进行不断的清洁动作,这样在不断的清针过程中,既浪费了测试的时间又加速了探针的老化,导致针卡寿命急剧缩短,同样也会造成测试的误判,需要通过多次的复测才能达到比较可信的测试良率。

在当前下游整机厂家对IC封装尺寸及性能的要求日益提高的情况下,无疑,目前的CSP封装以其超小的封装尺寸、优良的散热性能以及较高的性价比,当为众多消费类芯片的封装首选,但是,采用CSP封装,尤其是目前的无铅封装,给产品的量产测试带来了一定的技术难题,本文就CSP封装量产测试的基本方法、测试中存在的问题以及简单经济的解决办法稍做阐述,并举以实例,希望能够对一些正在寻求CSP测试解决方案的工程师能有一些帮助。

1、CSP封装简介CSP封装,即Chip Scale Package,芯片级封装;也称Chip Size Package,芯片尺寸封装,如图为一9脚的CSP封装的芯片,是最近几年才发展起来的新型集成电路封装技术。

应用CSP技术封装的产品封装密度高,性能好,体积小,重量轻,与表面安装技术兼容,因此它的发展速度相当快,现已成为集成电路重要的封装技术之一。

目前已开发出多种类型的CSP,品种多达100多种;另外,CSP产品的市场也是很大的,并且还在不断扩大,与其相关的测试也在迅速发展。

2、CSP封装量产测试的基本方法CSP封装的芯片测试,由于其封装较小,采用普通的机械手测试无法实现,目前主要采用类似晶圆测试的方法,在芯片完成置球封装后,先不做划片,而直接用探针卡进行测试,测试完成后,再实行划片、分选和包装。

测试时探针卡固定在探针台上,探针直接扎在CSP封装的锡球上以实现电气连接,然后测试机通过导线施加电压或波形等激励进行测试芯片的相关电气参数,以目前CSP封装应用较多的消费类芯片手机音频功放为例,作详细说明以便大家理解,其功能框图如下:在此针对接触电阻稍作说明:在实际生产测试中,探针的接触电阻在很大程度上取决于PAD的材料、清洗的次数、以及探针的状况。

就探针而言,目前主要有钨针和钨铼针两种,其中钨铼合金的探针接触电阻比钨稍高,抗疲劳性相似。

但是,由于钨铼合金的晶格结构比钨更加紧密,其探针顶端的______________平面更加光滑。

因此,这些探针顶端被污染的可能性更小,更容易清洁,其接触电阻也比钨更加稳定。

所以一般的探针材料均选用钨铼合金。

另外影响接触电阻的关键参数为触点压力,触点压力的定义为探针顶端施加到接触区域的压力,顶端压力主要由探针台的驱动器件控制,额外的Z运动(垂直行程)会令其直线上升,一般情况下,接触电阻会随着压力的增大,探针从开始接触PAD并逐渐深入PAD氧化物,并接触到PAD金属的亚表层而减小,但当压力达到一定的程度后,接触电阻就接本保持不变,此时再增加触点压力会损伤PAD 或者芯片内部结构,而导致芯片直接失效。

因此,在正常的生产过程中,触点压力的大小有比较严格的控制的,一般表现为探针台设置的OVER DRIVER大小。

4、CSP封装量产测试问题的解决由以上分析可知,问题的关键在于探针与锡球的接触电阻过大,那么如何才能减小接触电阻或者消除接触电阻的影响呢?通常,工程师们会从探针的角度出发,寻找一种抗沾污能力较强的探针,就目前来讲,这种材料的探针也确实存在,但费用极其昂贵,用其测试低附加值的消费类产品得不偿失;另外一种方法就是采用类似成品量产测试中使用的socket (测试座),这种socket是用贵金属金特殊加工的弹簧针来实现电气接触,从实际的应用的结果来说,效果相对较好,但其价格为普通探针卡的4到5倍,且寿命比一般的针卡短,因此这种方法也只能作为过度所用。

本文所提到的即经济又简单的方法为:借助kelvin的接触方式(或称四线测试方式)来消除接触电阻的影响,所谓Kelvin接触;既对于每个测试点都有一条激励线F 和一条检测线S,二者严格分开,各自构成独立回路;同时要求S 线必须接到一个有极高输入阻抗的测试回路上,使流过检测线S 的电流极小,近似为零,这样在S线上就不会有电压损失,检测出来的电压最为准确。

针对本文实例具体做法也非常简单,只需要在VO+及VO-端在原来的基础上多加上一根探针作为测量用,让电流只从另外一根探针上流过,这样从这根测试用探针测试出来的电压值就是很准确的输出电压值了。

第二章测试座的种类IC/测试座/老化座/插座IC Test and Burn-In Socket得技通电子代理YAMAICHI,ENPLAS,WELLS-CTI,3M Textool,TI,MERITEC,PLASTRONICS等各大厂商生产的IC老化测试座/ 原型贴片测试座,封装类型主要有BGA,CSP,DIP,PGA,PLCC,QFN/MLF,QFP,SOJ,SOP,TSOP,SSOP,SOT/TO……我公司可按照客户要求定制测试座/ 转接座,详情请来电咨询。

注:请点击封装分类表中的封装类型或点击厂商LOGO 图标进入对应页面了解详情。

IC插座(IC Socket)/测试座/烧录座/主要封装类型:BGA老化测试座CSP老化测试座DIP老化测试座PGA老化测试座PLCC老化测试座QFN/ MLF老化测试座QFP老化测试座QFP贴片测试座TSOP老化测试座SOP老化测试座TSOP贴片测试座SOT/ TO 老化测试座IC 插座/适配座/老化座/适配器/编程座/烧录座厂商主要类型:现货供应特价销售中!第三章测试座/适配座的保养与清洗方法活动适配器的保养与清洗方法:“UP&UP”系列的活动适配器均采用优质材料原厂精工生产,采用翻盖顶针结构,顶针为良好电气导通性能的优质铍金测试针,芯片定位快捷准确,再结合性能良好的欧式插针,经久耐用。

坚持对适配器良好的日常保养与维护,不仅有利于保证适配器长期处于“完好”状态,而且还可延长适配器的使用寿命。

因此必须按下列要求进行认真而有效的日常保养。

活动适配器的翻盖与座体由铰链连接,具有一定夹角,请不要强行后翻,以免损坏。

将芯片清洗干净后再放入活动适配器,避免松香等杂质进入适配器内污染测试针而引起短路或接触不良等。

多次使用之后或者定期对活动适配器进行清洗,可用超声波和酒精一起清洗。

注意:黑色翻盖易被强力清洁剂如天那水、苯、丙酮或者稀释剂等腐蚀,请用酒精等中性溶剂清洗干净活动座。

不用时请密封存放,以免灰尘杂质进入活动适配器内部。

活动适配器的清洗方法:(超声波+酒精清洗)清洗过程:1、首先,把活动适配器翻盖打开,接着把活动适配器倒放在超声波清洁器内,如图1;2、然后,在超声波清洁器内倒入适量的酒精,酒精的份量以把整个座头浸没为佳(如图2),并打开超声波清洁器开关,开始进行清洗工作,大概十分钟之后(如果活动座比较脏,清洗时间可以适当延长),把超声波清洁器开关关掉,用镊子把座头取出。

3、最后,用吹风筒把座头彻底吹干。

“UP&UP”系列的BGA系列活动适配器有:一)BGA80F、BGA100、BGA120、BGA130、BGA256:适用于管脚间距为0.75mm 和0.8mm 的BGA 封装字库,满足目前绝大部分BGA封装芯片的需要。

各种活动适配器分别配套“UP&UP”系列编程器使用。

二)EBGA64:适用于管脚间距为1.0mm的BGA封装字库,如MOTOROLA 388C的字库RD28F128K3,“UP&UP”系列编程器均适用三)BGA40:适用于管脚间距为0.5m 的BGA封装字库,如NOKIA 8310的字库29BDS643DT,“UP&UP”系列编程器均适用。

第四章测试座的寿命简单介绍集成电路老化测试座该产品用于航空航天、军工、科研单位以及集成电路生产企业,可配进口老化台、老化板做器件及高、低温测试、老化筛选作连接之用: 产品型号及规格;IC-8J、IC-14J、IC-16J、IC-18J 、IC-18J(K)宽跨度、IC-20J、IC-24J、IC-24Z窄脚、IC-28J、IC-28J(K)宽跨度、IC-40J主要技术指标;间距;2.54mm 环境温度;-55℃—+155℃绝缘电阻;≤0.01欧工作电压;DC500V 单脚插入力;≤0.2Kg 弹片金层厚度;2umAu:lu(镍金)插拔寿命;高低温状态下插拔寿命;2000-3000次TO封装集成电路老化测试插座该插座用于金属壳封装集成电路的老化、测试、筛选作连结之用,连结金属管材料采用磷青铜表面镀金、镀银、镀镍等工艺,该插座耐高温、绝缘性能好,经久耐用,深受用户的欢迎。

产品型号及规格;TO-4、6、8、10、12 主要技术指标;环境温度;-20℃—+255℃接触电阻;≤0.01欧工作电压;DC500V 单脚插入力;≤0.2Kg磷青铜管镀银层厚度;1um 镍2um 银高低温状态下插拔寿命;2000-3000次IC集成电路老化测试座(DIP封装)详细介绍:集成电路老化测试座该系列夹具适用于DIP封装的双列直插式集成电路的老化、测试、筛选及可靠性试验作连接之用。

该产品广泛运用于航空航天、军工、科研院所、电子、通讯产品型号及规格;IC-8J、IC-14J、IC-16J、IC-18J 、IC-18J(K)宽跨度、IC-20J、______________IC-24J、IC-24Z窄脚、IC-28J、IC-28J(K)宽跨度、IC-40J 主要技术指标;间距;2.54mm 环境温度;-55℃—+155℃接触电阻;≤0.01 欧工作电压;DC500V 单脚插入力;≤0.2Kg 弹片金层厚度;1um 镍2um 金插拔寿命;高低温状态下插拔寿命;2000-3000次IC老化测试座:该产品用于航空航天、军工、科研单位以及集成电路生产企业,可配进口老化台、老化板做器件及高、低温测试、老化筛选作连接之用:产品型号及规格;IC-8J、IC-14J、IC-16J、IC-18J 、IC-18J(K)宽跨度、IC-20J、IC-24J、IC-24Z窄脚、IC-28J、IC-28J (K)宽跨度、IC-40J主要技术指标;间距;2.54mm 环境温度;-55℃—+155℃绝缘电阻;≤0.01欧工作电压;DC500V单脚插入力;≤0.2Kg 弹片金层厚度;2umAu:lu(镍金)插拔寿命;高低温状态下插拔寿命;2000-3000次BGA产品说明:特点:1.BGA测试座透过转接板与PCB板连接,使得测试座与板子之间容易组装及拆拔和便于操作及维修。