模可变计数器设计(Verilog语言)解答

实验二 模可变计数器讲解

南昌大学实验报告学生姓名:学号:专业班级:中兴101班实验类型:□验证□综合■设计□创新实验日期:2012、10、18成绩:实验二模可变计数器的设计一、实验目的1.学习计数器的VHDL设计、波形仿真和硬件测试;2.学会自己设计程序;3.学会设计模可变计数器;4.学习多层次设计方法。

二、实验内容与要求1.计设置一位控制模的位M,要求M=0:模23计数;当M=1:模109计数。

2.计数结果用静态数码管显示,一个四位二进制表示0~9中的一个数;3.给出此项设计的仿真波形;4.应用实验装置验证此计数器的功能。

三、实验思路1.按照实验要求,本实验可分为四个模块进程:分频、模23与109计数转换、数码管控制、七段译码。

2.模可变计数器原理:即在原有的模值计数器上加入模值转换功能3.计数器的数码管显示需注意十位和百位的进位即:当个位数的数值为9的下一个脉冲来时转换为,同时向十位进一,转换的算法为:9(1001)+7(0111)=0(0000),并进一位;当数值为99时,用同样的方法转换:153(1001 1001B,数码管显示99)+103(01100111B)=100(0001 0000 0000);4.要求分别实现模23和模109的计数,因此我分别用buffer变量GW、SW 、 BW 代表个位、十位、百位。

还有一个控制模的位M,当M为0时实现模23计数,只用到GW和SW分别为个位和十位计数;当M为1时实现模109计数,用GW 、SW、 BW 分别为个位十位和百位计数。

由于端口不能参与运算,因些在结构体中定义了se10、 sel1、 sel2三个buffer变量,分别用来对应SEL(0)、 SEL(1)、SEL(2);在程序的最后用端口接收信号。

5.进程敏感信号为RST EN M 三个,当RST为低电平,EN为高电平时则计数,否则不计数。

6.位选信号的设置:用整形变量CNT8分别使不同的位选信号对应不同的输入,而得到不同输出。

模可变计数器设计(Verilog语言)解答

模可变计数器设计(一)实验目的1、进一步熟悉实验装置和Quartus n软件的使用;2、进一步熟悉和掌握EDA 设计流程;3 、学习简单组合、时序电路的EDA 设计;4、学习计数器中二进制码到BCD 码的转换技巧;5、学习实验装置上数码管的输出方法。

(二)设计要求完成设计、仿真、调试、下载、硬件测试等环节,在EDA 实验装置上实现模可变计数器功能,具体要求如下:1 、设置一个按键控制改变模值,按键按下时模为10-99 之间(具体数值自行确定)的数,没按下时模为100-199 之间(具体数值自行确定)的数;2、计数结果用三位数码管十进制显示。

(三) 主要仪器设备3、微机 1 台4、QuartusII 集成开发软件 1 套5、EDA 实验装置 1 套(四) 实验步骤主要有三个模块1:一个模20 和模119 的计数器2:数码管的显示3:BCD 的调整源程序:module count (clk,m,en,rst,a,sel,SG,d);input clk,m,en,rst;output [7:0] SG;output [2:0] sel;output a;(* synthesis, keep *) reg clk1;(* synthesis, keep *) wire [3:0] gw,sw,bw;/*(* synthesis, keep *) */reg [3:0]a;reg [11:0] q;reg [11:0] model;reg [7:0] cnt,SG;reg [2:0] sel;reg [0:0]d;output [0:0]d;always @(posedge clk) begin cnt=cnt+1;if (cnt==200) begin clk1=1'b1; cnt=0; endelse clk1=1'b0; //200 分频,CLK 为数码管扫描频率,CLK1 为计数频率if (sel<2) sel=sel+1; else sel=0; end //sel 为数码管选择always @(sel) begincase (sel)0: a=bw; //0 数码管为百位1: a=sw; //1 数码管为十位2: a=gw; //2 数码管为个位default: a=0;endcasecase (a)0:SG<=8'b00111111; 1:SG<=8'b00000110;2:SG<=8'b01011011; 3:SG<=8'b01001111;4:SG<=8'b01100110; 5:SG<=8'b01101101;6:SG<=8'b01111101; 7:SG<=8'b00000111;8:SG<=8'b01111111; 9:SG<=8'b01101111; //8 段译码值default: SG=8'b11111111;endcase endalways @(m)if (m) model=12'b000000100000; // 模值20else model=12'b000100011001; // 模值119assign gw=q[3:0];assign sw=q[7:4];assign bw=q[11:8];always @(posedge clk1,negedge rst)beginif (!rst) q=0;else if (en)beginif (q<model)beginif (gw==9) begin q=q+7; if (sw==9) q=q+96; end //BCD 调整else q=q+1;endelse q=0;endendalways @(q)if(qvmodel) d<=0; else d<=1; endmodule波形仿真:iimulatioin WaveformsSimulation sode : TillingA.B Master Time Sar19L9 ns ■[POinler: 39.3^1 us Imeival:39.32 us Stan :End:he. 14 us 37.. 42 UH 33. 7 us39.9B LLS4k 26 us54 us 4X B2 usP 1 i111■Clk1是计数频率,每来一个 clk1信号q 计数一次Simula ion Wa^efor™ Sinulatlon lode: Tiling如图所rst=1有效时开始计数 clk 为扫描频率sel=0时数码管显示百位 a=0 sel=1时数码管显示十位 a=1 sel=2时数码管显示个位 a=3 m=1模20计数器 m=0模119计数器管脚分配:* I HI Ik * Jij19.3ns J hRoirter.6fl.H us Interval.68.09 UE Slarl End.lane<>0□ S&elk<>1B clkl曲+ 0-L玮tT IF Len^1.nCH- 1±1 sei尬1.田Q B i辭El 勿u 3.dM68.14 us63.16 us ■6E. 18 usI63.22 us 68. 24 usW [1] X [3]连[01 X [1] X [3]迪[0] X [1] X [3] ® [o] X [1] X [3]址[0] II :MasierTiiTiB Bar.68.12 usIIISG[0] SG[1] SG[2] SG[3] SG[4] SG[5] SG[6] SG[7] clkPIN_F13PIN_F14PIN_F15PIN_E15PIN_F16PIN_F17PIN_E18PIN_F18 PIN_C13en PIN_H8m rst sel[0] sel[1] sel[2] d[0] PIN_J9PIN_C5PIN_G18PIN_G17PIN_G16 PIN_G13(五)实验心得本实验主要是三大模块的编写,第一次的实验在老师给的参考代码下进行的,不过错误依然很多,主要有几个重点药掌握,一是首先要编写出能够计数的模块,用m 来控制模值的变化m=1 时模值为20 m=0 时模值为119;二是计数模块都是二进制计数的,而要在数码管上显示计数的话就必须进行BCD 调整,并且q 是一个是十二位的寄存器,通过把gw=q[3:0]; sw=q[7:4]; bw=q[11:8] 赋值的方法;一个个的显示在数码管上,由于clk 的频率比较快,所以可以看到三位数码管显示的值,我觉得管脚分配也是比较关键的!一开始我就把个位和百位显示的值搞反了序列信号发生和检测器设计(一)实验目的1、进一步熟悉EDA实验装置和Quartus n软件的使用方法;2 、学习有限状态机法进行数字系统设计;3、学习使用原理图输入法进行设计。

实验二:模可变计数器

南昌大学实验报告学生姓名:刘志强学号:6100409222 专业班级:电子091班实验类型:验证□综合□设计■创新□实验日期:实验成绩:实验二模可变计数器设计(模23/模109)一、设计思路/原理图数字电路以前学过模值计数器的设计,而这个实验只是在原类型题加了一个模值转换的设置,再加上要求用数码管显示,所以必须把计数结果转换成BCD码,所以干脆直接使用BCD码进行模值控制。

二、实验程序(程序来源:网络)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt109 isport(clk,rst,en,M:in std_logic;cq,cqq,cqqq: out std_logic_vector (3 downto 0)) ;end cnt109;architecture behav of cnt109 isbeginprocess(clk,rst,en,M)variable cq1:std_logic_vector (11 downto 0);variable Z:std_logic_vector (11 downto 0);begincase M iswhen '0' => Z:="000000100010";when '1' => Z:="000100001000";end case;if rst='1' then cq1:=(others=>'0');elsif clk'event and clk='1' thenif en='1' thenif cq1<Z thenif cq1(7 downto 0) =153 then cq1:=cq1+103;elsif cq1(3 downto 0)=9 then cq1:=cq1+7;else cq1:=cq1+1;end if;else cq1 :=( others =>'0') ;end if;end if;end if;cq<=cq1( 3 downto 0);cqq<=cq1 ( 7 downto 4 ) ;cqqq<=cq1 ( 11 downto 8);end process;end behav转化成可调用的元:;、七段动态译码程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DECL7S ISPORT(D:IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED7S:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END DECL7S;ARCHITECTURE one OF DECL7S ISBEGINPROCESS(D)BEGINCASE D ISWHEN "0000"=>LED7S<="00111111";WHEN "0001"=>LED7S<="00000110";WHEN "0010"=>LED7S<="01011011";WHEN "0011"=>LED7S<="01001111";WHEN "0100"=>LED7S<="01100110";WHEN "0101"=>LED7S<="01101101";WHEN "0110"=>LED7S<="01111101";WHEN "0111"=>LED7S<="00000111";WHEN "1000"=>LED7S<="01111111";WHEN "1001"=>LED7S<="01101111";WHEN OTHERS=> NULL;END CASE;END PROCESS;END ARCHITECTURE;它的模块图如下:顶层文件:对文件保存并进行编译仿真,在验证仿真正确后进行管脚绑定如下图,然后进行下载测试。

verilog实验 计数器实验报告

计数器1、实现目标及介绍实验实现了一个简易的计数器,计数范围可达899(0~899),通过key4按键计数,每按下一次,计数加一,百位数显示在led上,个位与十位显示在数码管上。

为十进制计数,数码管1计数到九后置零。

数码管2获得进位加一,数码管2到9后当再次获得个位进位时再次向百位进一,点亮led1,每百位点亮一个led。

此外key4为清零键,可随时按键清零。

2、效果展示计数99清零计数100视频展示(双击观看)3、代码实现与模块分析1.顶层模块module jishuqi(input wire clk,rst, //时钟和复位输入input wire key1, //拨码计output wire [7:0]led,output wire [8:0] segment_led_1,segment_led_2 //数码管输出);wire key_pulse;reg [7:0] cnt; //计时计数器reg [7:0] hud; //百位计数initial hud[7:0] <= 8'b11111111;always @(posedge clk or negedge rst)begin //数码管显示要按照十进制的方式显示if(!rst)begin cnt <= 8'h00;hud [7:0] <= 8'b11111111;endelse if(key_pulse)beginif(cnt[3:0] == 4'd9) //个位进位判断begincnt[3:0] <= 4'd0;if(cnt[7:4] == 4'd9 ) //十位进位判断begincnt[7:4] <= 4'd0;hud[7:0] <= hud[7:0] - 1'b1;endelsecnt[7:4] <= cnt[7:4] + 1'b1;endelse cnt[3:0] <= cnt[3:0] + 1'b1;endelsecnt <= cnt;endassign led = hud;//例化调用数码管显示模块segment u2(.seg_data_1 (cnt[7:4]), //g_data input.seg_data_2 (cnt[3:0]), //g_data input.seg_led_1 (segment_led_1), //MSB~LSB = SEG,DP,G,F,E,D,C,B,A.seg_led_2 (segment_led_2) //MSB~LSB = SEG,DP,G,F,E,D,C,B,A);//例化调用消抖模块debounce u1 (.clk (clk),.rst (rst),.key (key1),.key_pulse (key_pulse));endmodule2.数码管显示模块module segment (seg_data_1,seg_data_2,seg_led_1,seg_led_2);input [3:0] seg_data_1;//数码管需要显示0~9十个数字,所以最少需要4位输入做译码input [3:0] seg_data_2; //小脚丫上第二个数码管output [8:0] seg_led_1;//在小脚丫上控制一个数码管需要9个信号MSB~LSB=DIG、DP、G、F、E、D、C、B、Aoutput [8:0] seg_led_2;//在小脚丫上第二个数码管的控制信号MSB~LSB=DIG、DP、G、F、E、D、C、B、Areg [8:0] seg [9:0];//定义了一个reg型的数组变量,相当于一个10*9的存储器,存储器一共有10个数,每个数有9位宽initial//在过程块中只能给reg型变量赋值,Verilog中有两种过程块always和initial //initial和always不同,其中语句只执行一次beginseg[0] = 9'h3f; //对存储器中第一个数赋值9'b00_0011_1111,相当于共阴极接地,DP点变低不亮,7段显示数字0seg[1] = 9'h06; //7段显示数字 1seg[2] = 9'h5b; //7段显示数字 2seg[3] = 9'h4f; //7段显示数字 3seg[4] = 9'h66; //7段显示数字 4seg[5] = 9'h6d; //7段显示数字 5seg[6] = 9'h7d; //7段显示数字 6seg[7] = 9'h07; //7段显示数字7seg[8] = 9'h7f; //7段显示数字8seg[9] = 9'h6f; //7段显示数字9endassign seg_led_1 = seg[seg_data_1]; //连续赋值,这样输入不同四位数,就能输出对于译码的9位输出assign seg_led_2 = seg[seg_data_2];endmodule3.按键消抖模块//按键消抖module debounce (clk,rst,key,key_pulse);parameter N = 2; //要消除的按键的数量input clk;input rst;input [N-1:0] key; //输入的按键output [N-1:0] key_pulse; //按键动作产生的脉冲reg [N-1:0] key_rst_pre; //定义一个寄存器型变量存储上一个触发时的按键值reg [N-1:0] key_rst; //定义一个寄存器变量储存储当前时刻触发的按键值wire [N-1:0] key_edge; //检测到按键由高到低变化是产生一个高脉冲//利用非阻塞赋值特点,将两个时钟触发时按键状态存储在两个寄存器变量中always @(posedge clk or negedge rst)beginif (!rst)beginkey_rst <= {N{1'b1}}; //初始化时给key_rst赋值全为1,{}中表示N个1key_rst_pre <= {N{1'b1}};endelsebeginkey_rst <= key; //第一个时钟上升沿触发之后key的值赋给key_rst,同时key_rst的值赋给key_rst_prekey_rst_pre <= key_rst; //非阻塞赋值。

实验一 模可变计数器

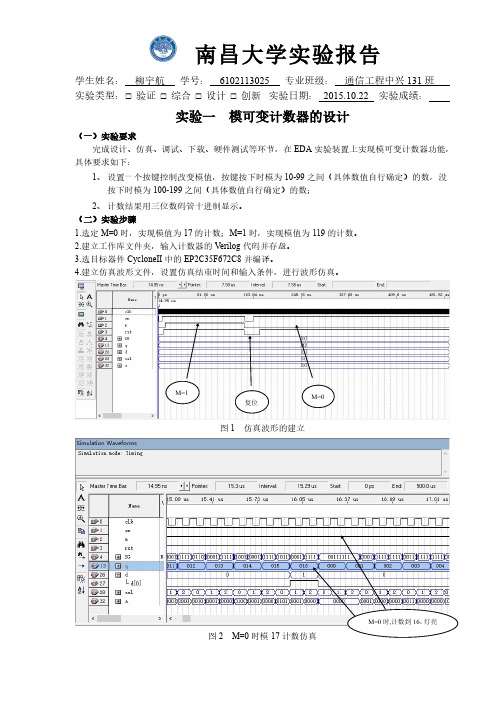

南昌大学实验报告学生姓名:柳宇航学号:6102113025专业班级:通信工程中兴131班实验类型:□验证□综合□设计□创新实验日期:2015.10.22实验成绩:实验一模可变计数器的设计(一)实验要求完成设计、仿真、调试、下载、硬件测试等环节,在EDA实验装置上实现模可变计数器功能,具体要求如下:1、设置一个按键控制改变模值,按键按下时模为10-99之间(具体数值自行确定)的数,没按下时模为100-199之间(具体数值自行确定)的数;2、计数结果用三位数码管十进制显示。

(二)实验步骤1.选定M=0时,实现模值为17的计数;M=1时,实现模值为119的计数。

2.建立工作库文件夹,输入计数器的Verilog代码并存盘。

3.选目标器件CycloneII中的EP2C35F672C8并编译。

4.建立仿真波形文件,设置仿真结束时间和输入条件,进行波形仿真。

图1仿真波形的建立图2M=0时模17计数仿真M=0时,计数到16,灯亮M=1M=0复位M=1时,计数到118,灯亮图3M=1时模119计数仿真波形分析:当RST为高电平时,计数清零。

当RST为低电平,使能位EN为高电平时,开始计数:模控制位M为低电平时,则计数器记到16时归0后重新计数,实现模为17的计数功能;模控制位M为高电平时,则计数器记到118时归0后重新计数,实现模为119的计数功能。

当EN 为低电平时,暂停计数。

5.管脚分配clk PIN_C13en PIN_A5m PIN_B5rst PIN_A6sel[0]PIN_G18sel[1]PIN_G17sel[2]PIN_G16SG[0]PIN_F13SG[1]PIN_F14SG[2]PIN_F15SG[3]PIN_E15SG[4]PIN_F16SG[5]PIN_F17SG[6]PIN_E18SG[7]PIN_F18d[0]PIN_H106.下载测试。

下载到实验箱上测试,下推K7(M=0),可以从实验箱数码管观察到0~16模17计数。

计数器(1):Verilog常用写法

计数器(1):Verilog常⽤写法 计数器是⾮常基本的使⽤,没有计数器就⽆法处理时序。

我在学习时发现市⾯上有⼏种不同的计数器写法,⾮常有趣,在此记录下来:⼀、时序逻辑和组合逻辑彻底分开1.代码1//======================================================================2// --- 名称 : Count_13// --- 作者 : xianyu_FPGA4// --- ⽇期 : 2018-12-105// --- 描述 : 模10计数器,0到10循环累加6//======================================================================78module Count_19 (10input clk ,11input rst_n ,12output reg [ 3:0] cnt13 );1415//----------------------------------------------------------------------16//-- 组合电路17//----------------------------------------------------------------------18reg [ 3:0] cnt_n ;1920always @(*)begin21if(cnt == 4'd9)22 cnt_n = 4'd0;23else24 cnt_n = cnt + 1'b1;25end2627//----------------------------------------------------------------------28//-- 时序电路29//----------------------------------------------------------------------30always @(posedge clk or negedge rst_n)begin31if(!rst_n)32 cnt <= 4'b0;33else34 cnt <= cnt_n;35end3637endmodule3839/*40//----------------------------------------------------------------------41//-- 组合电路也可以这样写42//----------------------------------------------------------------------43wire [ 3:0] cnt_n ;4445assign cnt_n = (cnt==4'd9)? 4'd0 : cnt+1'b1;4647*/2.写法1的RTL视图3.写法2的RTL视图⼆、最常见的写法1.代码1//======================================================================2// --- 名称 : Count_23// --- 作者 : xianyu_FPGA4// --- ⽇期 : 2018-12-105// --- 描述 : 模10计数器,0到10循环累加6//======================================================================78module Count_29 (10input clk ,11input rst_n ,12output reg [ 3:0] cnt13 );1415always @(posedge clk or negedge rst_n)begin16if(!rst_n)17 cnt <= 4'd0;18else if(cnt==4'd9)19 cnt <= 4'd0;20else21 cnt <= cnt + 1'b1;22end23242526endmodule2.RTL视图三.代码⽚段写法1.代码1//====================================================================== 2// --- 名称 : Count_33// --- 作者 : xianyu_FPGA4// --- ⽇期 : 2018-12-105// --- 描述 : 模10计数器,0到10循环累加6//====================================================================== 78module Count_39//---------------------<端⼝声明>---------------------------------------10 (11input clk ,12input rst_n ,13output reg [ 3:0] cnt14 );15//---------------------<信号定义>---------------------------------------16wire add_cnt ;17wire end_cnt ;1819//----------------------------------------------------------------------20//-- 0-9计数21//----------------------------------------------------------------------22always @(posedge clk or negedge rst_n)begin23if(!rst_n)24 cnt <= 'd0;25else if(add_cnt)begin26if(end_cnt)27 cnt <= 'd0;28else29 cnt <= cnt + 1'b1;30end31else32 cnt <= cnt;33end3435assign add_cnt = 1;36assign end_cnt = add_cnt && cnt==10-1;3738394041endmodule2.RTL视图四、⾃减计数器(较少⽤到)1.代码1//====================================================================== 2// --- 名称 : Count_43// --- 作者 : xianyu_FPGA4// --- ⽇期 : 2018-12-195// --- 描述 : 模10⾃减计数器,10到0循环累减6//====================================================================== 78module Count_49//---------------------<端⼝声明>---------------------------------------10 (11input clk ,12input rst_n ,13output reg [ 3:0] cnt14 );15//---------------------<参数定义>---------------------------------------16parameter CNT_MAX = 10 ;1718//----------------------------------------------------------------------19//-- 10到0循环累减20//----------------------------------------------------------------------21always @(posedge clk or negedge rst_n)begin22if(!rst_n) begin23 cnt <= 0;24end25else if(cnt==0) begin26 cnt <= CNT_MAX;27end28else begin29 cnt <= cnt - 1;30end31end323334endmodule2.RTL视图3.仿真波形五、新学到的⼀种⾮常简洁的计数器 本以为计数器就是这样了,近来学习开源骚客《SDRAM那些事⼉》系列教程,⼜发现⼀种新的写法,对于特定功能的实现上⾮常简洁。

verilog计数器设计原理

Verilog计数器设计原理1. 介绍计数器是一种常见的数字电路,用于计算和记录事件的数量。

在数字系统中,计数器通常用于生成时钟信号、控制状态机、实现频率分频等应用。

Verilog是一种硬件描述语言,可以用于设计和仿真数字电路。

本文将详细介绍与Verilog计数器设计相关的基本原理。

2. 计数器的基本概念计数器是一种能够在输入脉冲信号的作用下进行累加或递减操作的数字电路。

它通常由触发器和逻辑门组成,触发器用于存储和传递数据,逻辑门用于控制触发器的工作状态。

2.1 同步计数器同步计数器是通过时钟信号来同步各个触发器的状态转换,以实现数据的累加或递减操作。

它包含一个时钟输入端(CLK)和一个复位输入端(RST)。

2.1.1 同步正向计数器同步正向计数器是最简单的同步计数器之一,它能够在每个上升沿时钟信号到达时进行累加操作。

2.1.1.1 原理同步正向计数器由多个触发器和逻辑门组成,其中每个触发器都有一个时钟输入端和一个复位输入端。

当时钟信号的上升沿到达时,触发器的状态将根据输入信号进行更新。

具体的原理如下:1.初始化:将计数器的初始值设置为0。

2.时钟边沿检测:当时钟信号的上升沿到达时,进入下一步操作。

3.累加操作:根据触发器的当前状态进行累加操作。

如果触发器为0,则变为1;如果触发器为1,则变为0。

4.检测溢出:如果最高位触发器由1变为0,则表示计数溢出,需要将其他低位触发器进行进位操作。

2.1.1.2 Verilog代码示例以下是一个4位同步正向计数器的Verilog代码示例:module synchronous_counter(input wire clk,input wire rst,output wire [3:0] count);reg [3:0] count;always @(posedge clk or posedge rst)beginif (rst)count <= 4'b0000;elsecount <= count + 1;endendmodule2.1.2 同步递减计数器同步递减计数器是同步正向计数器的一种扩展,它能够在每个上升沿时钟信号到达时进行递减操作。

模M的可逆计数器

西安邮电学院FPGA实验报告-模M可逆计数器系部名称:电工院学生姓名:何慧敏(28)(04084041)专业名称:微电子班级:0802模M的可逆计数器的设计一、实验目的本实验实现模M可逆计数器的设计仿真,M为参数,完成RTL的设计和功能仿真。

二、功能定义模M可逆计数器实现的功能是:此计数器可以实现任意模M的可加可减的计数器。

任意模M定义为参数,可以通过改变M的值来实现所计的数;而可逆计数器指的是这个计数器通过某一输入来实现可加可减的计数。

三、端口说明四、时序波形上图为计数器实现加运算的计数波形上图为计数器实现减运算的计数波形五、模块框图六、仿真验证针对本实验的功能要求,我用V erilog仿真程序对主模块进行实例化来仿真验证并输出波形。

通过验证,与预想结果一致。

当in为1时,实现减法计数器;当in=0时,实现加法计数器。

七、V erilog 代码主模块:module jishu(clk,load,in,count);input clk,in,load;output count;parameter M=4;reg [M:0] count;always @(posedge clk or posedge load)if(in)beginif(load)count<=M-1;elsebeginif(count)count<=count-1;elsecount<=M-1;endendelsebeginif(load)count<=0;elsebeginif(count!=(M-1))count<=count+1;elsecount<=0;endendendmodule激励模块:module stimulate;reg clk,in,load;wire count;jishu a1(.clk(clk),.in(in),.load(load),.count(count)); initialbeginclk=1'b0;forever #5 clk=~clk;endinitialbeginin=1'b0;#200 in=1'b1;endinitialbeginload=1'b1;#8 load=1'b0;#125 load=1'b1;#133 load=1'b0;endendmodule八、设计及仿真环境设计环境及仿真环境:modelsim。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

模可变计数器设计(一)实验目的1、进一步熟悉实验装置和Quartus n软件的使用;2、进一步熟悉和掌握EDA 设计流程;3 、学习简单组合、时序电路的EDA 设计;4、学习计数器中二进制码到BCD 码的转换技巧;5、学习实验装置上数码管的输出方法。

(二)设计要求完成设计、仿真、调试、下载、硬件测试等环节,在EDA 实验装置上实现模可变计数器功能,具体要求如下:1 、设置一个按键控制改变模值,按键按下时模为10-99 之间(具体数值自行确定)的数,没按下时模为100-199 之间(具体数值自行确定)的数;2、计数结果用三位数码管十进制显示。

(三) 主要仪器设备3、微机 1 台4、QuartusII 集成开发软件 1 套5、EDA 实验装置 1 套(四) 实验步骤主要有三个模块1:一个模20 和模119 的计数器2:数码管的显示3:BCD 的调整源程序:module count (clk,m,en,rst,a,sel,SG,d);input clk,m,en,rst;output [7:0] SG;output [2:0] sel;output a;(* synthesis, keep *) reg clk1;(* synthesis, keep *) wire [3:0] gw,sw,bw;/*(* synthesis, keep *) */reg [3:0]a;reg [11:0] q;reg [11:0] model;reg [7:0] cnt,SG;reg [2:0] sel;reg [0:0]d;output [0:0]d;always @(posedge clk) begin cnt=cnt+1;if (cnt==200) begin clk1=1'b1; cnt=0; endelse clk1=1'b0; //200 分频,CLK 为数码管扫描频率,CLK1 为计数频率if (sel<2) sel=sel+1; else sel=0; end //sel 为数码管选择always @(sel) begincase (sel)0: a=bw; //0 数码管为百位1: a=sw; //1 数码管为十位2: a=gw; //2 数码管为个位default: a=0;endcasecase (a)0:SG<=8'b00111111; 1:SG<=8'b00000110;2:SG<=8'b01011011; 3:SG<=8'b01001111;4:SG<=8'b01100110; 5:SG<=8'b01101101;6:SG<=8'b01111101; 7:SG<=8'b00000111;8:SG<=8'b01111111; 9:SG<=8'b01101111; //8 段译码值default: SG=8'b11111111;endcase endalways @(m)if (m) model=12'b000000100000; // 模值20else model=12'b000100011001; // 模值119assign gw=q[3:0];assign sw=q[7:4];assign bw=q[11:8];always @(posedge clk1,negedge rst)beginif (!rst) q=0;else if (en)beginif (q<model)beginif (gw==9) begin q=q+7; if (sw==9) q=q+96; end //BCD 调整else q=q+1;endelse q=0;endendalways @(q)if(qvmodel) d<=0; else d<=1; endmodule波形仿真:iimulatioin WaveformsSimulation sode : TillingA.B Master Time Sar19L9 ns ■[POinler: 39.3^1 us Imeival:39.32 us Stan :End:he. 14 us 37.. 42 UH 33. 7 us39.9B LLS4k 26 us54 us 4X B2 usP 1 i111■Clk1是计数频率,每来一个 clk1信号q 计数一次Simula ion Wa^efor™ Sinulatlon lode: Tiling如图所rst=1有效时开始计数 clk 为扫描频率sel=0时数码管显示百位 a=0 sel=1时数码管显示十位 a=1 sel=2时数码管显示个位 a=3 m=1模20计数器 m=0模119计数器管脚分配:* I HI Ik * Jij19.3ns J hRoirter.6fl.H us Interval.68.09 UE Slarl End.lane<>0□ S&elk<>1B clkl曲+ 0-L玮tT IF Len^1.nCH- 1±1 sei尬1.田Q B i辭El 勿u 3.dM68.14 us63.16 us ■6E. 18 usI63.22 us 68. 24 usW [1] X [3]连[01 X [1] X [3]迪[0] X [1] X [3] ® [o] X [1] X [3]址[0] II :MasierTiiTiB Bar.68.12 usIIISG[0] SG[1] SG[2] SG[3] SG[4] SG[5] SG[6] SG[7] clkPIN_F13PIN_F14PIN_F15PIN_E15PIN_F16PIN_F17PIN_E18PIN_F18 PIN_C13en PIN_H8m rst sel[0] sel[1] sel[2] d[0] PIN_J9PIN_C5PIN_G18PIN_G17PIN_G16 PIN_G13(五)实验心得本实验主要是三大模块的编写,第一次的实验在老师给的参考代码下进行的,不过错误依然很多,主要有几个重点药掌握,一是首先要编写出能够计数的模块,用m 来控制模值的变化m=1 时模值为20 m=0 时模值为119;二是计数模块都是二进制计数的,而要在数码管上显示计数的话就必须进行BCD 调整,并且q 是一个是十二位的寄存器,通过把gw=q[3:0]; sw=q[7:4]; bw=q[11:8] 赋值的方法;一个个的显示在数码管上,由于clk 的频率比较快,所以可以看到三位数码管显示的值,我觉得管脚分配也是比较关键的!一开始我就把个位和百位显示的值搞反了序列信号发生和检测器设计(一)实验目的1、进一步熟悉EDA实验装置和Quartus n软件的使用方法;2 、学习有限状态机法进行数字系统设计;3、学习使用原理图输入法进行设计。

(二)设计要求完成设计、仿真、调试、下载、硬件测试等环节,在EDA 实验装置上实现一个串行序列信号发生器和一个序列信号检测器的功能,具体要求如下:1、先用设计0111010011011010序列信号发生器,其最后6BIT 数据用LED 显示出来;2、再设计一个序列信号检测器,检测上述序列信号,若检测到串行序列“11101”则输出为“ 1 ”,否则输出为“ 0”;(三)主要仪器设备1、微机1台2、QuartusII 集成开发软件1套3、EDA 实验装置1套(四)实验步骤主要两部分1 :序列信号发生器设置q<=16'b0111010011011010;q[0]<=q[15];Q<=q[15]; q[15:1]<=q[14:0] ;通过循环移位串行输出2:序列信号检测器状转移态图一共有六个状态分别为S = 5'd00000,A = 5'd00001,B = 5'd00011,C = 5'd00110,D = 5'd01101,E = 5'd11010;源程序:module xulie(clk,rst,z,Q,led);in put clk,rst; output Q,z; output [4:0] led; reg [4:0] led; reg [4:0] state; reg Q,z; reg [4:0] a; reg [15:0] q; parameter S = 5'd00000,A = 5'd00001,B = 5'd00011,C = 5'd00110,D = 5'd01101,E = 5'd11010;always @(posedge clk)beginif(rst==0) begi n q<=16'b0111010011011010; endelse begi nq[0]<=q[15];Q<=q[15]; q[15:1]<=q[14:0]; endendalways @(posedge clk)beginif(state==D && Q==1)begi n z<=1;led<=5'b11101;e ndelse begi n z<=0;led<=5'b00000;e nd endalways @(posedge clk or n egedge rst)if(!rst)beginstate<=S;e ndelsecasex(state)S: if(Q==1)state<=A;else A:state<=S;if (Q==1) state<=B;else B:state<= S;if (Q==1) state<=C;else C:state<=S;if(Q==0) state<=D;else D: state<=C; if(Q==1)state<=E;else E: state<=S; if(Q==0)state<=S;else state<=A; default: state<=S; endcase en dmodule波形仿真simulation VVavefo 『rn£ SinijJation node i Tilling当rst=1011101001101101011101z=1并且同时使11101序列显示在五个led 灯上(五)实验心得做实验之前准备了很多,实验时还是出现了很多问题,一开始序列信号发生器在第一个周期 之后就会多出一个 0 即输出 00111010011011010,原因在于 Q<=q[15]; q[15:1]<=q[14:0];q[0]<=Q;因为q[0]<=Q 需要一个时钟的上升沿才能执行,所以就会多输出一个0;其次状态转移图也是关键,需要记忆六个不同的状态;做这个实验让我学到了 casex 的一些用法;进一步了解编写verilog 语言NarieQ elkB led"8 rstzj .14 III 1卜9,9 ns 士 Pioinier52.15 nsrrtetvoJ;32 55 ns sterf Ops End 0 ps0 psI. 28 us 2. 56 us S. B4 UE 1 ・ i5. 12 us6. 4 ue7. ca usi8. us L0. 24 us 11. 52 ucin j Jnsr11l! J —1 1-L1 _|_L ~I1 1―L—J~~[ J-1_1- ~L0000J 111 oi 1Cooooo-1 1 'MesierTime BarIII。