微波炉控制器的设计与分析

微波炉控制系统的设计与实现

微波炉控制系统的设计与实现微波炉是当今家庭中必不可少的家用电器之一,其方便、快捷、安全的特点受到了人们的欢迎。

然而,微波炉在工作过程中需要通过控制系统来调节电磁波的输出,以确保食品的加热效果和安全性。

因此,设计和实现一个稳定可靠的微波炉控制系统是必不可少的。

一、控制系统的功能需求微波炉控制系统主要需要完成如下功能:电源控制、电磁波输出控制、时间计时和显示以及安全机制的设计。

其中,电源控制需要控制微波炉的电源输入和输出,以保证稳定工作;电磁波输出控制主要用于调节电磁波的输出功率;时间计时和显示则是通过LED显示屏或者液晶屏来显示时间,并进行倒计时;安全机制用于保证用户的安全,在炉门未关闭时自动切断电源。

二、控制系统的工作原理微波炉的工作原理是通过控制系统来调节电源输入和输出电磁波的功率、频率和时序。

当用户开启微波炉时,系统首先进行电源控制,确保电源正常工作,然后进入电磁波输出控制阶段。

在输出控制阶段中,系统根据用户设定的输出功率和烹饪时间来控制电磁波的输出功率和时序,以确保食品能够均匀加热。

同时,系统还需要进行时间计时和显示,为用户提供倒计时和时间显示功能。

当烹饪结束时,系统自动关闭电源,同时启动安全机制,切断电源,以保证用户的安全。

三、控制系统的硬件设计控制系统的硬件主要包括中央处理器(CPU)、晶振、存储器、显示屏、光电传感器和电源控制模块等。

其中,CPU是控制系统的核心,用于控制微波炉的工作流程。

晶振则提供稳定的时钟信号,为系统提供精准的时间计时功能。

存储器用于存储微波炉的各种工作参数和数据,以便后续的查询和更新。

显示屏则提供时间计时和烹饪过程的显示功能,便于用户操作和使用。

光电传感器则用于检测炉门的关闭状态,以触发安全机制的启动。

电源控制模块用于对电源进行控制和管理,确保系统的稳定性和安全性。

四、控制系统的软件设计控制系统的软件设计涉及到编程语言、操作系统和控制程序的编写等方面。

在编程语言方面,常用的有C语言、汇编语言和嵌入式语言等。

VHDL微波炉控制器设计

目录一、绪论 (2)二、关键技术简介 (2)2.1 FPGA简介 (2)2.2 VHDL语言概述 (2)2.3 ALTIUM DESIGNER简介 (3)三、微波炉定时控制器的设计方案分析 (4)3.1 系统设计的要求 (4)3.2 系统总体功能描述 (4)3.3 各模块的功能实现 (5)3.3.1 输入模块 (5)3.3.2 状态控制模块 (5)3.3.3 显示模块 (5)四、系统详细设计 (7)4.1控制模块 (7)4.1.1状态转换控制 (7)4.1.2数据装载 (9)4.1.3 烹饪计时 (10)4.1.4 控制模块的实现 (11)五、系统仿真 (11)5.1状态控制器仿真 (11)5.2 数据装载器的仿真 (12)5.3 烹饪计时器的仿真 (13)六、结论 (14)一、绪论随着人民生活水平的提高,微波炉开始进人越来越多的家庭,它给人们的生活带来了极大的方便。

微波炉由 2450MHz 的超高频来加热食物。

它省时、省电、方便和卫生。

作为现代的烹饪工具,微波炉的控制器体现着它的重要性能指标。

目前大部分微波炉控制器采用单片机进行设计,电路比较复杂,性能不够灵活。

本文采用先进的EDA技术,利用ALTIUM DESIGNER工作平台和VHDL设计语言,设计了一种新型的微波炉控制器系统。

该系统具有系统复位、时间设定、烹饪计时等功能,在 FPGA 上实现。

二、关键技术简介2.1 FPGA简介FPGA(Field-Programmable GateArray),即现场可编程门阵列,它是在PAL、 GAL、CPLD 等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

目前以硬件描述语言(Verilog 或 VHDL)所完成的电路设计,可以经过简单的综合与布局,快速的烧录至 FPGA 上进行测试,是现代 IC 设计验证的技术主流。

微波炉控制器的设计与分析

的 状态 转 换条 件 及 输 出信 号进 行 分 析 ,我 们 可得 到 其状 态 转 换 图如 图 3 , 3 主 要 VH L漂程 序 D 状态控 制器 K Q的 V D 源 程序 Z HL

A C IE T R R F K Q S R H T c U E A T O Z I

T P T T Y E I (I L ,L M E T E L C ,T M R Y ESA ETP S D E A P T S ,S T C O K I E ,

1系统 设计 要求 设计 一个微 波炉 控制 器 W L Z ,通过 该控制 器再 配 以 4 七段 数码 二极 B KQ 个 管 完 成 微波 炉 的定 时 及信 息 显示 。各信 号功 能要 求 : () L 1 C K是秒 时脉 冲输 入 ,它 接受 每秒 一 个 时钟 脉冲 的 节拍信 号 。 () E E 2 R S T为 复位 信 号 ,高 电平 有效 ,用 于 芯片 的 复位 功 能 。 () E T为测试信 号 ,高 电平有 效 ,用于 测试 4 七段 数码 管二极 管工 3TS 个 作是 否正常 。 ( 】 E T是 烹调 时 间设置 控 制信 号 ,高 电平 有效 。 4ST ()A A 是一 个 1 总线输 入信 号 ,输入 所设 的时 间长短 ,它又 高 到 5DTO 6位 低分 为 四组,每 一组 是 BD 输入 ,分 别表示 分 、 上 十位 、 位 的数字 。例 C码 秒 个

I E T F R SE =’ 1 T E ’ H N C R TT < IL UR S A E = D E: E S F C K’EV NT A D L = l L I L E N C K ’ ’ CR T T <N X T T U R S A E = E S A E:

微波炉控制器

微波炉控制器微波炉是一种微波加热食品的现代化烹调灶具,它由电源、磁控管、控制电路和烹调腔组成。

其中,微波炉控制器部分完成各工作状态之间的切换功能,可以通过硬件语言描述的数字系统来实现。

详细分析微波炉控制器的原理和组成结构,并设计一个简单的具有定时和信息显示功能的微波炉控制器。

一、系统设计要求设计一个具备定时和信息显示功能的微波炉控制器。

要求该微波炉控制器能够在任意时刻取消当前工作,复位为初始状态。

可以根据需要设置烹调时间的长短,系统最长的烹调时间为59分59秒;开始烹调后,能够显示剩余时间的多少。

显示微波炉控制器的烹调状态。

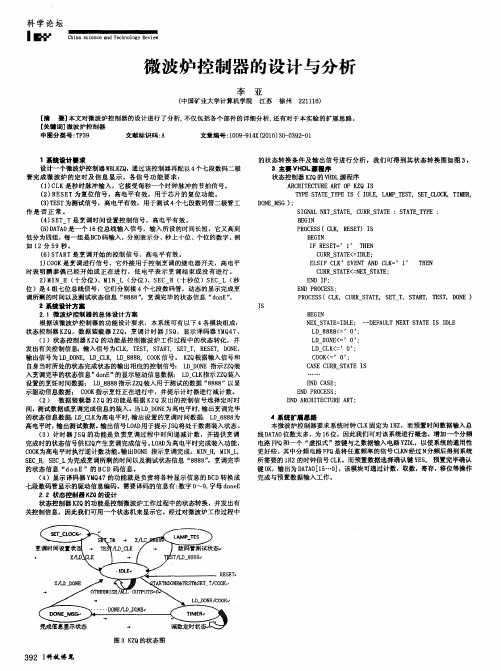

二、系统设计方案分析上述设计要求,微波炉控制器可由以下四个电路模块组成:状态控制电路,其功能是控制微波炉工作过程中的状态转换,并发出相关控制信号;数据装载电路,其功能是根据控制信号选择定时时间,测试数据或计时完成信息的载入;计时电路,其功能是对时钟进行减法计数,提供烹调完成时的状态信号;显示译码电路,其功能是显示微波炉控制器的各状态信息。

图1 微波炉控制器的系统框图微波炉控制器的系统框图如图1所示。

其中,CLK为时钟输入信号,时钟上升沿敏感;RESET为复位信号,高电平有效时系统复位清零;TEST为数码显示管测试信号,高电平有效,用于测试显示管是否正常工作;SET_T为烹调时间设置信号,高电平有效时允许设置烹调时间;DATA为定时时间输入信号,用于设置烹调时间的长短,其由高到低分别表示定时时间分、秒的十位,个位;START为烹调开始信号,高电平有效时开始烹调;输出信号COOK指示微波炉状态,高电平时表示烹调进行时;SEC0、SEC1、MIN0、MIN1分别表示秒个位、秒十位、分个位、分十位。

顶层模块的RTL原理图如下:微波炉控制器的工作流程如下:首先,对系统进行复位清零,使其各电路模块均处于初始状态;当烹调时间设置信号SET_T有效时,读入时间信号DATA[15…0]的取值,此时系统自动复位并显示设置的时间信息,按下开始键START,系统进入烹调状态,COOK信号变为高电平,时钟计数器开始减法计数,显示剩余烹调时间。

基于Verilog的微波炉控制器的设计

基于FPGA 的微波炉控制器的设计一、设计任务及要求该实验主要完成微波炉控制器的设计。

主要功能有复位开关、模式选择、烹调时间设置、LED 指示烹调状态及数码管显示烹调剩余时间。

上电后,系统处于复位状态。

工作时首先进行烹调时间设置,并使用数码管显示时间信息,设要求最长的烹调时间为59分59秒,时间设置完毕后系统处于等待状态状态;选择开始烹调模式时系统进入烹调状态,时间显示数码管按每秒减1的倒计时方式显示剩余烹调时间;烹调结束后,系统回到复位状态。

二、设计方案及流程微波炉控制器系统主要有一下五个电路模块组成:分频模块、模式选择电路、时间设置电路、倒计时模块、显示模块。

分频模块完成系统50MHz 的时钟向1Hz 的分频,使计时器能够按照1S 的频率倒计时。

模式选择电路,其功能是控制微波炉工作过程中模式的切换,选择不同的模式系统计入不同的工作状态。

时间设置模块,该模块主要是可根据用户需求输入烹调时间;倒计时电路会根据用户所设置的时间进行倒计时,由数码管显示电路显示目前烹调状态,同时由LED 灯指示系统反正在烹调。

系统总体框图如下:系统的输入输出信号如下:输入clk ,key0,key1,key2,key3,key4五个信号,输出hex0,hex1,hex2,hex3,sec_flag ,cook 六个信号。

时间设置模块50MHz 分1Hz 的 分频模块数码管显示电路倒计时电路模式选择模块图1 系统总体框图clk作为50MHz分频模块的输入,时钟上升沿有效。

Key3作为模式选择信号,mode0表示系统进入分设置模块,mode1表示系统进入秒设置模块,mode2表示系统设置时间完成,进入烹调状态。

key2的作用是在mode0及mode1模式下对分、秒设置进行加操作,按一下分、秒加1。

key1的作用是在mode0及mode1模式下对分、秒设置进行减操作,按一下分、秒信号减1。

key0作为系统的复位信号,在不同模式下按下key0系统都会进入复位状态,数码管显示”0000”,cook标志的LED灯处于灭状态。

微波炉控制器设计[1]

![微波炉控制器设计[1]](https://img.taocdn.com/s3/m/2b3c1e86b52acfc788ebc987.png)

二、文献综述现有市售的微波炉其主要弊端为:不能按既有程序进行烹调,在节能方面也未做过多考虑。

烹调经验告诉我们,家常菜大多可按固定程序烹调、炖肉、煮饭、烘烤。

若采取分时、分档火力加热,则可节能。

微波炉控制系统功能比较齐全,在火力档位设了解冻、烹调、烘烤、保温、自定义加热、自定义烹调以及按给定程序烹调等七种主要功能,其中程序烹调共设置了八种不同的烹调流程,供用户选择。

在控制方面,实现了智能化,信息化管理,并且具有密码开锁功能,即只有知道相应模式键继续运行的号码的人,才能对该机进行操作等等功能。

STC12C5404AD单片机是具有全新流水线和精简指令集结构的高速率、低功耗新一代单片机。

它带有8路10位精度ADC、4路PWM/PCA(可编程计数器阵列)、SPI同步通信口以及内部集成的MAX810专用复位电路。

这些特点不但增加了开发者的使用灵活性,同时还可以帮助用户减小PCB尺寸和系统成本。

此外,STC12C5404AD型处理器还可以通过串口(P3.0/P3.1)直接下载用户程序,从而使其适合于在系统(ISP)及在应用(IAP)中编程,因而可为许多计算密集的嵌入式控制应用领域提供功能强大、使用灵活且性价比高的解决方案。

STC12C5404AD是STC系列单片机,采用RISC型CPU内核,兼容普通8051指令集,片内含有10KB Flash 程序存储器,2KB Flash 数据存储器,512B RAM 数据存储器,同时内部还有看门狗(WDT);片内集成MAX810专用复位电路、8通道10位ADC以及4通道PWM,具有在系统编程(ISP)和在应用编程(IAP),片内资源丰富、集成度高、使用方便。

STC12C5404AD对系统的工作进行实施调度,实现外部输入参数的设置、蓄电池及负载的管理、工作状态的指示等。

电磁式继电器一般由铁芯、线圈、衔铁、触点簧片等组成。

只要在线圈两端加上一定的电压,线圈中就会流过一定的电流,从而产生电磁效应,衔铁就会在电磁力吸引的作用下克服返回弹簧的拉力吸向铁芯,从而带动衔铁的动触点与静触点(常开触点)吸合。

浅析智能微波炉控制系统设计的相关要点

浅析智能微波炉控制系统设计的相关要点摘要:微波炉已经逐渐走进了我们大部分的家庭,使用微波炉给我们带来了很多的方便。

而随着控制技术和智能技术的发展,微波炉也朝着智能化、信息化的方向发展。

为此,本文首先对微波炉进行了简要概述,分析了当前智能微波炉的特点,并以某智能微波炉的可编程微波炉控制系统为例进行了探讨。

关键词:智能微波炉;控制系统;设计要点1.微波炉概述微波炉是用微波来加热食品的,微波炉加热过程很短,其中养分和维生素丢失少,并且矿物质、氨基酸的存活率会比其他方法高许多。

与煤炉、煤气相比较而言,其工作时不会产生类似于碳未完全焚烧而导致有害气体和烟尘,其工作加热食物是在炉腔中实现的,不会存在明火,用起来更加安全安心。

微波炉的电路控制系统将220V交流电压通过高压变压器的变压和高压整流器的整流,转换成4200V左右的直流电压,送至磁控管产生微波,微波能量通过波导管传到炉内腔中。

因为金属的特性,微波不能穿过炉内,只能在炉腔中反复折射,反复穿透食品,被脂肪、含有水分的蛋白质的物质吸收能量,加热食品,这样才能完成加热过程。

2.智能微波炉的特点微波炉作为家用电器之一,已广泛进入人们的生活,其类型也从最初的机械控制发展到目前的电脑控制。

采用微电脑控制技术和传感器感测技术,实现微波炉的智能化加热烹调是微波炉技术发展的一大方向。

这种智能微波炉无需使用者在操作按键上输入烹调时间、加热功率、食物重量等参数,只要按下启动键,微波炉内的传感器就检测到食物温度、整齐湿度等参数不断输出给电脑控制芯片,微电脑控制芯片进行一系列的运算、比较、分析之后,输出相应的指令,自动控制微波炉的加热时间和功率大小,实现智能化全自动烹调。

3.智能微波炉控制系统设计实例分析通过上述对智能微波炉特点的分析,当前智能微波炉已经成为微波炉的主流产品,良好的控制系统设计是微波炉正常运行工作的基本保障。

为此,本节对智能微波炉中可编程微波炉控制系统为例进行分析,其除了可以实现常规的解冻、烹调、烘烤基本功能之外,还可以实现微波炉面板关闭的自动监测,通过Internet对微波炉进行远程智能控制等。

微波炉可编程逻辑控制系统设计

微波炉可编程逻辑控制系统设计微波炉可编程逻辑控制系统设计随着人们生活水平的提高,微波炉已经成为广大家庭不可或缺的电器,相信大家对微波炉已经非常熟悉了。

它能够以独特的方式加热食物,既快捷又方便。

但是,目前市场上的微波炉普遍存在着定时不准确、温度控制不稳定、操作复杂等问题,给用户的使用带来了不便。

为此,设计一种微波炉可编程逻辑控制系统,是非常有必要的。

需求分析:我们的系统需要满足以下几个主要功能:1.定时功能:以最短的时间精确地加热食物,避免加热过头。

2.温度控制:通过精确测量微波的温度,避免加热不均匀。

3.操作简单:用户操作界面应该简单直观,方便不同用户的使用。

基于以上需求分析,我们可以开始系统的设计。

硬件方案1.温度传感器:我们需要一种能够准确测量微波温度的传感器,在市面上有很多种温度传感器,常用的有热电偶、热敏电阻、热电阻等。

我们考虑使用一种精度高、反应速度快、稳定性好的热敏电阻。

2.触控屏:使用触控屏可以简化用户的操作,让用户界面更加直观,可触控的屏幕也可以避免误操作和按键损坏等问题。

3.微波开关:微波加热的过程中,需要让微波源开关控制微波闸门的开关,以达到加热的目的。

4.微波管:微波的加热核心是微波管。

我们需要选购高品质的微波管,以确保加热效果稳定并且寿命长。

5.逻辑控制板:所有硬件的控制需要一个逻辑控制板来负责。

我们可以使用单片机或者嵌入式芯片。

软件方案1.程序设计:我们需要编写运行在逻辑控制板上的程序。

程序需要实现用户控制界面、温度传感器数据采集、微波开关控制等功能。

程序同时需要确保稳定高效,以此保证系统的性能。

2.内存管理:部分程序需要保存在逻辑控制板的内存中,因此我们需要实现程序的内存管理。

其中,存储程序的部分,需要保证读写速度快、容量足够。

3.硬件驱动:逻辑控制板需要控制各种硬件,如温度传感器、微波管等。

因此,我们需要考虑如何写好各种硬件的驱动程序以及如何控制硬件的状态。

总结本文介绍了微波炉可编程逻辑控制系统的设计方案,包括硬件方案和软件方案。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA系统设计组成员及负责模块:冀鹏超状态控制器KZQ设计陆威数据装载器ZZQ设计韩华凯烹饪计时器JSQ设计凌智烹饪计时器JSQ设计白浚材显示译码器YMQ47设计孙兵剑微波炉控制器WBLKZQ设计微波炉控制器的设计与分析一.系统设计要求现在设计一个微波炉控制器WBLKZQ,其外部接口如图1所示。

通过该控制器再配以4个七段数码二极管完成微波炉的定时及信息显示。

图1 微波炉控制器外部接口符号图图1中的各信号的功能及要求如下:CLK是秒表时钟脉冲输入,它接收每秒一个时钟脉冲的节拍信号。

RESET为复位信号,高电平有效,用于芯片的复位功能。

TEST为测试信号,高电平有效。

用于测试4哥七段数码二极管工作是否正常。

SET_TS是烹调时间设置控制信号,高电平有效。

DATA0的一个人16位的总线输入信号,输入所设置的时间长短,它由高到低分为4组,每一组是BCD码输入,分别表示分、秒上十位个位的数字,如12分59秒。

START是烹调开始的控制信号,高电平有效。

COOK是烹调进行信号,它外接用于控制烹调的继电器开关,高电平时表明烹调已经开始或正在进行,低电平表示烹调结束或没有进行。

MIN_H(十分位)、MIN_L(分位)、SEC_H(十秒位)和SEC_L(秒位)是4组七位总线信号,它们分别接4个七段数码管,动态地显示完成烹调所剩的时间以及测试状态信息“8888”、烹调完毕的状态信息“donE”。

该微波炉控制器WBLKZQ的具体功能要求如下:上电后系统首先处于一种复位状态。

在工作时首先按SEC_L键设置烹调时间,此时系统读入DATA0的数据作为烹调所需时间,然后系统自动回到复位状态,同时4个七段数码管显示时间信息(假设系统最长的烹调时间为59分59秒)。

再按START键后系统进入烹调状态,COOK信号开始为高电平,此时4个七段数码管每隔一秒钟变化一次,用以刷新还剩多少时间结束烹调。

烹调结束后,COOK信号变为低电平,同时4个七段数码管组合在一起显示“donE”的信息,然后系统回到复位状态。

系统可以通过按RESET键随时回到复位状态。

在复位状态下,按TEST键在4个数码管上会显示“8888”的信息,它可以测试4个七段数码管工作是否正常。

二.系统设计要1.微波炉控制器的总体设计方案根据该微波炉控制器的功能设计要求,本系统可由以下4个模块组成:①状态控制器KZQ;②数据装载器ZZQ;③烹调计时器JSQ;④显示译码器YMQ47。

其内部组成原理如图2所示。

图2 微波炉控制器WBLKZQ的内部组成原理图(1)状态控制器KZQ的功能是控制微波炉工作过程中的状态转换,并发出有关控制信息:输入信号为CLK、TEST、START、SET_T、RESET和DONE,输出信号为LD_DONE、LD_CLK、LD_8888和COOK信号。

KZQ根据输入信号和自身当时所处的状态完成状态的转换和输出相应的控制信号:LD_DONE指示ZZQ装入烹调完毕的状态信息“donE”的显示驱动信息数据;LD_CLK 指示ZZQ装入设置的烹饪时间数据;LD_8888指示ZZQ装入用于测试的数据“8888”以显示驱动信息数据;COOK指示烹饪正在进行之中,并提示计时器进行减计数。

(2)数据装载器ZZQ的功能是根据KZQ发出的控制信号选择定时时间、测试数据或烹调完成信息的装入。

当LD_DONE为高电平时,输出烹调完毕的状态信息数据;LD_CLK为高电平时,输出设置的烹饪时间数据;LD_8888为高电平时,输出测试数据。

输出信号LOAD用于提示JSQ将处于数据装入状态。

(3)计时器JSQ的功能是负责烹调过程中的时间递减计数,并提供烹调完成时的状态信号提供KZQ产生烹调完成信号。

LOAD为高电平时完成装入功能,COOK为高电平时执行逆计数功能。

输入DONE指示烹调完成。

MIN_H、MIN_L、SEC_H、和SEC_L为完成烹调所剩的时间以及测试状态信息“8888”、烹调完毕的状态信息“donE”的BCD码信息。

(4)显示译码器YMQ47的功能就是负责将各种显示信息的BCD转换成七段数码管显示的驱动信息编码。

需要译码的信息有:数字0~9,字母d、o、n、E。

2.状态控制器KZQ的设计状态控制器KZQ的功能是控制微波炉工作过程中的状态转换,并发出有关控制信息,因此我们可用一个状态机来实现它。

经过对微波炉工作过程中的状态转换条件及输出信号进行分析,我们可得到其状态转换图如图3所示,其输入、输出端口如图4所示。

图3 KZQ的输入输出端口图图4 KZQ的输入输出端口图3.数据装载器ZZQ的设计ZZQ的输入、输出端口如5所示,根据其应完成的逻辑功能,它本质上就是一个三选一数据选择器。

本设计采用一个进程来完成,但由于三个被选择的数据只有一个来自输入端口,因此另两个被选择的数据则通过在进程的说明部分定义两个常数来产生。

由于用于显示“8888”的常数ALL-8需分解成4个8,分别经过四个4—7译码器译码后才是真正的显示驱动信息编码,因此该常数应是4个分段的是4位BCD码,故应设为“11000”。

同理,显示“donE”的常数DONE可设为“11101”,其中d、o、n、E的BCD 码分别为:“1010”、“1011”、“1100”、“1101”。

该模块的主要程序如下:图5 ZZQ的输入输出端口PROCESS(DATA1,LD_8888.LD_CLK.LD_DONE)ISCONSTANT ALL_8:STD_LOGIC_VECTOR(15 DOWNTO 0):="11000";CONSTANT DONE:STD_LOGIC_VECTOR(15 DOWNTO 0):="11101";V ARIABLE TEMP:STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINLOAD<=LD_8888 OR LD_DONE OR LD_CLK;TEMP:=LD_8888 & LD_DONE & LD_CLK;CASE TEMP ISWHEN "100"=>DATA2<=ALL_8; --LOAD_8888=1WHEN "010"=>DATA2<=DONE; --LOAD_DONE=1WHEN "001"=>DATA2<=DATA1; --LOAD_CLK=1WHEN OTHERS=>NULL;END CASE;END PROCESS;4.烹调计时器JSQ的设计烹调计时器JSQ为减数计时器,其最大计时时间为59:59。

因此我们可用两个减计数十进制计数器DCNT10和两个减计数六进制计数器DCNT6级联构成。

JSQ的内部组成原理如图6所示。

图6 JSQ的内部组成原理图5.显示译码器YMQ47的设计本显示译码器YMQ47不但要对数字0~9进行显示译码,还要对字母d、o、n、E进行显示译码,其译码对照表如表1所示。

表1 YMQ47的译码对照表显示的数字或字母BCD编码七段显示驱动编码(g~a)0 00001 00012 00103 00114 01005 01016 01107 01118 10009 1001三.主要VHDL源程序1.状态控制器KZQ的VHDL源程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY KZQ ISPORT(RESET,SET_T,START,TEST,CLK,DONE:IN STD_LOGIC;COOK,LD_8888,LD_CLK,LD_DONE:OUT STD_LOGIC);END ENTITY KZQ;ARCHITECTURE ART OF KZQ ISTYPE STATE_TYPE IS(IDLE,LAMP_TEST,SET_CLOCK,TIMER,DONE_MSG); SIGNAL NXT_STATE,CURR_STATE:STATE_TYPE;BEGINPROCESS(CLK,RESET)ISBEGINIF RESET='1' THENCURR_STATE<=IDLE;ELSIF CLK'EVENT AND CLK='1' THENCURR_STATE<=NXT_STA TE;END IF;END PROCESS;PROCESS(CLK,CURR_STATE,SET_T,START,TEST,DONE)ISBEGINNXT_STATE<=IDLE; --DEFAULT NEX STATE IS IDLELD_8888<='0';LD_DONE<='0';LD_CLK<='0';COOK<='0';CASE CURR_STA TE ISWHEN LAMP_TEST=>LD_8888<='1';COOK<='0';WHEN SET_CLOCK=>LD_CLK<='1';COOK<='0';WHEN DONE_MSG=>LD_DONE<='0';COOK<='0';WHEN IDLE=>IF(TEST='1')THENNXT_STATE<=LAMP_TEST;LD_8888<='1';ELSIF SET_T='1'THENNXT_STATE<=SET_CLOCK;LD_CLK<='1';ELSIF ((START='1')AND(DONE='0'))THENNXT_STATE<=TIMER;COOK<='1';END IF;WHEN TIMER=>IF DONE='1'THENNXT_STATE<=DONE_MSG;LD_DONE<='1';ELSENXT_STATE<=TIMER;COOK<='1';END IF;END CASE;END PROCESS;END ARCHITECTURE ART;2.数据装载器ZZQ的VHDL源程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY ZZQ ISPORT(DATA1:IN STD_LOGIC_VECTOR(15 DOWNTO 0);LD_8888:IN STD_LOGIC;LD_CLK:IN STD_LOGIC;LD_DONE:IN STD_LOGIC;DATA2:OUT STD_LOGIC_VECTOR(15 DOWNTO 0);LOAD:OUT STD_LOGIC);END ENTITY ZZQ;ARCHITECTURE ART OF ZZQ ISBEGINPROCESS(DATA1,LD_8888,LD_CLK,LD_DONE)ISCONSTANT ALL_8:STD_LOGIC_VECTOR(15 DOWNTO 0):="11000";CONSTANT DONE:STD_LOGIC_VECTOR(15 DOWNTO 0):="11101";V ARIABLE TEMP:STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINLOAD<=LD_8888 OR LD_DONE OR LD_CLK;TEMP:=LD_8888 & LD_DONE&LD_CLK;CASE TEMP ISWHEN"100"=>DATA2<=ALL_8;WHEN"010"=>DATA2<=DONE;WHEN"001"=>DATA2<=DATA1;WHEN OTHERS=>NULL;END CASE;END PROCESS;3.烹调计时器JSQ的VHDL源程序--DCNT10.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DCNT10 ISPORT(CLK:IN STD_LOGIC;LOAD:IN STD_LOGIC;ENA:IN STD_LOGIC;DATAIN:IN STD_LOGIC_VECTOR(3 DOWNTO 0);CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CARRY_OUT:OUT STD_LOGIC);END ENTITY DCNT10ARCHITECTURE ART OF DCNT10 ISSIGNAL CQI:STD_LOGIC_VECTOR(3 DOWNTO 0); BEGINPROCESS(CLK,LOAD,ENA)ISBEGINIF LOAD='1' THENCQI<=DATAIN;ELSIF CLK'EVENT AND CLK='1' THENIF ENA='1' THENIF CQI="000" THEN CQI<="1001";ELSE CQI<=CQI-'1';END IF;END IF;END IF;END PROCESS;PROCESS(CLK,CQI)ISBEGINIF CLK'EVENT AND CLK='1' THENIF CQI="0000" THEN CARRY_OUT<='1';ELSE CARRY_OUT<='0';END IF;END IF;END PROCESS;CQ<=CQI;END ARCHITECTURE ART;--DCNT6.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DCNT6 ISPORT(CLK:IN STD_LOGIC;LOAD:IN STD_LOGIC;ENA:IN STD_LOGIC;DATAIN:IN STD_LOGIC_VECTOR(3 DOWNTO 0);CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CARRY_OUT:OUT STD_LOGIC);END ENTITY DCNT6;ARCHITECTURE ART OF DCNT6 ISSIGNAL CQI:STD_LOGIC_VECTOR(3 DOWNTO 0); BEGINPROCESS(CLK,LOAD,ENA)ISBEGINIF LOAD='1' THENCQI<=DATAIN;ELSIF CLK'EVENT AND CLK='1' THENIF ENA='1' THENIF CQI="0000" THEN CQI<="0101";ELSE CQI<=CQI-'1';END IF;END IF;END IF;END PROCESS;PROCESS(CLK,CQI)ISBEGINIF CLK'EVENT AND CLK='1' THENIF CQI="0000" THEN CARRY_OUT<='1';ELSE CARRY_OUT<='0';END IF;END IF;END PROCESS;CQ<=CQI;END ARCHITECTURE ART;--JSQ.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY JSQ ISPORT(COOK:IN STD_LOGIC;DATA3:IN STD_LOGIC_VECTOR(15 DOWNTO 0);LOAD:IN STD_LOGIC;CLK:IN STD_LOGIC;SEC_L:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);SEC_H:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);MIN_L:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);MIN_H:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);DONE:OUT STD_LOGIC);END ENTITY JSQ;ARCHITECTURE ART OF JSQ ISCOMPONENT DCNT10 ISPORT(CLK,LOAD,ENA:IN STD_LOGIC;DATAIN:IN STD_LOGIC_VECTOR(3 DOWNTO 0);CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CARRY_OUT:OUT STD_LOGIC);END COMPONENT DCNT10;COMPONENT DCNT6 ISPORT(CLK,LOAD,ENA:IN STD_LOGIC;DATAIN:IN STD_LOGIC_VECTOR(3 DOWNTO 0);CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CARRY_OUT:OUT STD_LOGIC);END COMPONENT DCNT6;SIGNAL NEWCLK:STD_LOGIC;SIGNAL S1:STD_LOGIC;SIGNAL S2:STD_LOGIC;SIGNAL S3:STD_LOGIC;SIGNAL S4:STD_LOGIC;BEGINU1:DCNT10 PORT MAP(CLK, LOAD, COOK, DA TA3(3 DOWNTO 0), SEC_L, S1); U2:DCNT6 PORT MAP(S1, LOAD, COOK, DATA3(7 DOWNTO 4), SEC_H, S2);U3:DCNT10 PORT MAP(S2, LOAD, COOK, DATA3(11 DOWNTO 8), MIN_L, S3); U4:DCNT6 PORT MAP(S3, LOAD, COOK, DATA3(15 DOWNTO 12), MIN_H, S4); DONE<=S1 AND S2 AND S3 AND S4;END ARCHITECTURE ART;4.显示译码器YMQ47的源程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY YMQ47 ISPORT(AIN4:IN STD_LOGIC_VECTOR(3 DOWNTO 0);DOUT7:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END ENTITY YMQ47;ARCHITECTURE ART OF YMQ47 ISBEGINPROCESS(AIN4)BEGINCASE AIN4 ISWHEN"0000"=>DOUT7<="0111111";WHEN"0001"=>DOUT7<="0000100";WHEN"0010"=>DOUT7<="1011011";WHEN"0011"=>DOUT7<="1001111";WHEN"0100"=>DOUT7<="1100110";WHEN"0101"=>DOUT7<="1101101";WHEN"0110"=>DOUT7<="1111101";WHEN"0111"=>DOUT7<="0000111";WHEN"1000"=>DOUT7<="1111111";WHEN"1001"=>DOUT7<="1101111";WHEN"1010"=>DOUT7<="1011110";WHEN"1011"=>DOUT7<="1011100";WHEN"1100"=>DOUT7<="1010100";WHEN"1101"=>DOUT7<="1111001";WHEN OTHERS=>DOUT7<="0000000";END CASE;END PROCESS;END ARCHITECTURE ART;5.微波炉控制器WBLKZQ的VHDL源程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY WBLKZQ ISPORT(RESET,SET_T,START,TEST,CLK:IN STD_LOGIC;COOK:OUT STD_LOGIC;SEC_L,SEC_H,MIN_L,MIN_H:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END ENTITY WBLKZQ;ARCHITECTURE ART OF WBLKZQ ISCOMPONENT KZQ ISPORT(RESET,SET_T,START,TEST,CLK,DONE:IN STD_LOGIC;COOK,LD_8888,LD_CLK,LD_DONE:OUT STD_LOGIC);END COMPONENT KZQ;COMPONENT ZZQ ISPORT(DATA1:IN STD_LOGIC_VECTOR(15 DOWNTO 0);LD_8888:IN STD_LOGIC;LD_CLK:IN STD_LOGIC;LD_DONE:IN STD_LOGIC;DATA2:OUT STD_LOGIC_VECTOR(15 DOWNTO 0);LOAD:OUT STD_LOGIC);END COMPONENT ZZQ;COMPONENT JSQ ISPORT(COOK:IN STD_LOGIC;DATA3:IN STD_LOGIC_VECTOR(15 DOWNTO 0);LOAD:IN STD_LOGIC;CLK:IN STD_LOGIC;SEC_L:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);SEC_H:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);MIN_L:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);MIN_H:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);DONE:OUT STD_LOGIC);END COMPONENT JSQ;COMPONENT YMQ47PORT(AIN4:IN STD_LOGIC_VECTOR(3 DOWNTO 0);END COMPONENT YMQ47 ;SIGNAL S1:STD_LOGIC;SIGNAL S2:STD_LOGIC;SIGNAL S3:STD_LOGIC;SIGNAL S4:STD_LOGIC;SIGNAL S5:STD_LOGIC;SIGNAL S6:STD_LOGIC_VECTOR(15 DOWNTO 0);SIGNAL S7:STD_LOGIC;SIGNAL S8:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL S9:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL S10:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL S11:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINU1:KZQ PORT MAP(RESET,SET_T,START,TEST,CLK,S1,S2,S3,S4,S5);U2:ZZQ PORT MAP(DA TA0(15 DOWNTO 0),S3,S4,S5,S6(15 DOWNTO 0),S7);U3:JSQ PORT MAP(S2,S6(15 DOWNTO 0),S7,CLK,S8(3 DOWNTO 0),S9(3 DOWNTO 0),S10(3 DOWNTO 0),S11(3 DOWNTO 0),S1);U4:YMQ47 PORT MAP(S8(3 DOWNTO 0),SEC_L(6 DOWNTO 0));U5:YMQ47 PORT MAP(S9(3 DOWNTO 0),SEC_H(6 DOWNTO 0));U6:YMQ47 PORT MAP(S10(3 DOWNTO 0),MIN_L(6 DOWNTO 0));U7:YMQ47 PORT MAP(S11(3 DOWNTO 0),MIN_H(6 DOWNTO 0));COOK<=S2;END ARCHITECTURE ART;四.系统仿真状态控制器KZQ、数据装载器ZZQ、烹调计时器JSQ和显示译码YMQ47的仿真分别如图7、图8、图9、图10所示:图7状态控制器KZQ的仿真图图8数据装载器ZZQ的仿真图图9烹调计时器JSQ的仿真图图10显示译码器YMQ47仿真图四.设计心得FPGA系统设计是一门比较难的课程,在这次设计中,我们全组花了不少的时间,其中有苦也有乐,苦的是我们付出了不少的汗水,乐的是在付出的过程中我们学到了许多。