vhdl条件赋值语句

任务3 VHDL的赋值语句

进行的,或者说是并行运行的,其执行 方式与书写的顺序无关。

来,也可以是互为独立、互不相关、异 步运行的(如多时钟情况)。

在执行中,并行语句之间可以有信息往

每一并行语句内部的语句运行方式可以

有两种不同的方式,即并行执行方式(如 块语句)和顺序执行方式(如进程语句)。

Architecture

Begin

ARCHITECTURE

式 BEGIN p1:PROCESS(a,b) VARIABLE comb:STD_LOGIC_VECTOR(1 DOWNTO 0); -变量定义 BEGIN comb:= a & b; --变量赋值(此处为用并置运算符将 a和b连接成一个两位矢量) CASE comb IS --CASE_WHEN多项选择语句 WHEN “00”=>y<=„1‟; --当ab=00时,y=1 WHEN “01”=>y<=„1‟; --当ab=01时,y=1 WHEN “10”=>y<=„1‟; --当ab=10时,y=1 WHEN “11”=>y<=„0‟; --当ab=11时,y=0 WHEN OTHERS=>y<=„X‟; --当ab的取值为其他情况时, y的取值不确定 END CASE; END PROCESS p1; END 赋值语句

语法格式:

signal_name <= 逻辑表达式

VHDL支持所有的标准逻辑运算:

AND, OR, NOT, XOR, XNOR, NAND

例:4

选 1 数据选择器

a b c d

s

2 x

mux

Architecture a of mux4_1 is Begin x <= (a AND NOT(s(1)) AND NOT(s(0))) OR (b AND NOT(s(1)) AND s(0)) OR (c AND s(1) AND NOT(s(0))) OR (d AND s(1) AND s(0)) ; 逻辑表达式 End a;

VHDL语句

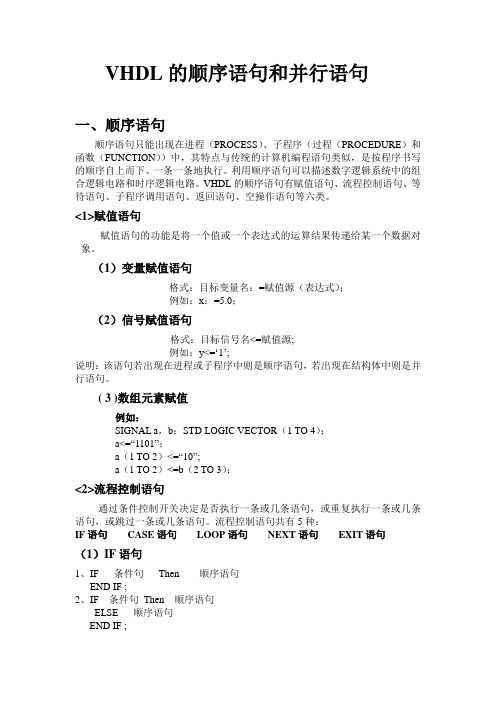

VHDL的顺序语句和并行语句一、顺序语句顺序语句只能出现在进程(PROCESS)、子程序(过程(PROCEDURE)和函数(FUNCTION))中,其特点与传统的计算机编程语句类似,是按程序书写的顺序自上而下、一条一条地执行。

利用顺序语句可以描述数字逻辑系统中的组合逻辑电路和时序逻辑电路。

VHDL的顺序语句有赋值语句、流程控制语句、等待语句、子程序调用语句、返回语句、空操作语句等六类。

<1>赋值语句赋值语句的功能是将一个值或一个表达式的运算结果传递给某一个数据对象。

(1)变量赋值语句格式:目标变量名:=赋值源(表达式);例如:x:=5.0;(2)信号赋值语句格式:目标信号名<=赋值源;例如:y<=…1‟;说明:该语句若出现在进程或子程序中则是顺序语句,若出现在结构体中则是并行语句。

( 3 )数组元素赋值例如:SIGNAL a,b:STD LOGIC VECTOR(1 TO 4);a<=“1101”;a(1 TO 2)<=“10”;a(1 TO 2)<=b(2 TO 3);<2>流程控制语句通过条件控制开关决定是否执行一条或几条语句,或重复执行一条或几条语句,或跳过一条或几条语句。

流程控制语句共有5种:IF语句CASE语句LOOP语句NEXT语句EXIT语句(1)IF语句1、IF 条件句Then 顺序语句END IF ;2、IF 条件句Then 顺序语句ELSE 顺序语句END IF ;3、IF 条件句Then 顺序语句ELSIF 条件句Then 顺序语句...ELSE 顺序语句END IF4、IF 条件句ThenIF 条件句Then...END IFEND IF例子:8线-3线优先编码器的设计LIBRARY IEEE;USE IEEE.STD LOGIC 1164.ALLENTITY coder ISPORT(a:IN STD LOGIC VECTOR(0 TO 7);y:OUT STD LOGIC VECTOR(0 TO 2));END coder;ARCHITECTURE example2 OF coder ISBEGINPROCESS(a)BEGINIF (a(7)=…0‟)THEN y<=”111”;ELSIF (a(6)=‟0‟) THEN y<=”011”;ELSIF (a(5)=‟0‟) THEN y<=”101”;ELSIF (a(4)=‟0‟) THEN y<=”001”;ELSIF (a(3)=‟0‟) THEN y<=”110”;ELSIF (a(2)=‟0‟) THEN y<=”010”;ELSIF (a(1)=‟0‟) THEN y<=”100”;ELSE y<=”000”;END IF;END PROCESS;END example2;(2)CASE语句格式:CASE 表达式ISWhen 选择值=>顺序语句;When 选择值=>顺序语句;…When OTHERS =>顺序语句;END CASE;说明:“=>”不是运算符,相当“THEN”。

VHDL基本语句

例

ARCHITECTURE example OF mux4 IS BEGIN PROCESS (sel) 注 BEGIN ●CASE中的选择值必须在表达式的取值范围内; CASE sel IS WHEN 0=> q <= d0 ; ●CASE语句是无序的,所有表达式值都是并行 WHEN 1=> q <= d1 ; 处理;而IF语句是有序的,最起始、最优先 WHEN 2=> q<= d3 ; WHEN 3=> q<= d4 ; 的先处理; WHEN others => NULL; ●可以有很多分支,但OTHERS分支只能有一个, END CASE; 且只能位于最后;用来使所有选择值能涵盖表 END PROCESS; END example; 达式的所有取值,以免插入不必要的锁存器

3、用于多选控制的IF语句:

格式 IF 条件1 THEN

<顺序处理语句1>;

ELSIF 条件2 THEN <顺序处理语句2>; : ELSIF 条件n-1 THEN <顺序处理语句n-1>; ELSE <顺序处理语句n>; END IF;

P1: PROCESS (clk) BEGIN

IF (clk‘ event and clk=‗1‘ ) THEN

顺序语句

赋值语句

VHDL设计实体内的数据传递以及对端口界面外部数据的读写 都必须通过赋值语句的运行来实现。 功能是将一个值或表达式的运算结果传递给某一数据对象。 赋值语句有两种: 信号赋值语句和变量赋值语句 区别

第10章 VHDL基本语句-ST

15

10.1 顺 序 语 句

10.1.9 RETURN语句

过程 函数

返回语句仅用于子程序

16

10.1 顺 序 语 句

10.1.10 NULL语句 空操作语句不完成任何操作,常用于CASE语句。

17

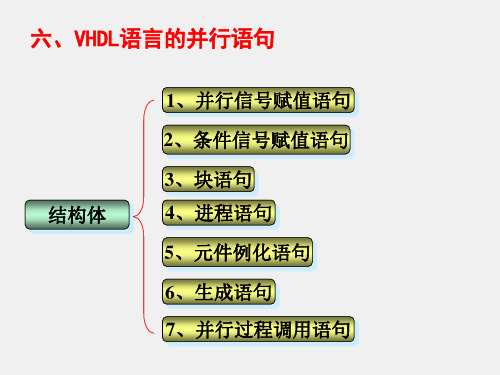

10.2 VHDL并行语句

结构体中可综合并行语句:

18

10.2 VHDL并行语句

10.2.1 并行信号赋值语句 赋值目标必须都是信号

28

10.2 VHDL并行语句

10.2.6 REPORT语句 REPORT语句用来报告计算的有关信息,本身不可综合,仅用于仿真。

29

10.2 VHDL并行语句

10.2.7 断言语句 断言语句也不可综合,仅用于仿真

30

10.3 属性描述与定义语句

1. 信号类属性

2. 数据区间类属性

'RANGE [(n)]

EDA技术实用教程

第10章 VHDL基本语句

1

10.1 顺 序 语 句

顺序语句的特点:(仿真)执行顺序与其书写顺序是一致的 进程与子程序(函数、过程) 10.1.1 赋值语句

信号赋值 赋值目标 <= 赋值源 变量赋值 赋值目标 := 赋值源 注意赋值符号左右两端数据类型一致,以及与=>的区别 10.1.2 IF语句

32

10.1.3 CASE语句 单个普通数值数、数值选择范围、并列数值、混合方式

IF语句中条件句逐项顺序执行,具有向上相与的逻辑功能 CASE语句中条件句的次序不重要,其执行过程接近于并行方式

2

10.1 顺 序 语 句

10.1.3 CASE语句

3

10.1 顺 序 语 句

第5章VHDL基本描述语句

多个赋值源

SVEC(0) <= V1; --将V1在上面的赋值1,赋给SVEC(0)

SVEC(1) <= V2;

SVEC(2) <= S1; SVEC(3) <= S2;

--将V2在上面的赋值1,赋给SVEC(1)

--将S1在上面的赋值1,赋给SVEC(2) --将最下面的赋予S2的值‘0’,赋给SVEC(3)

FOR LOOP循环主要用在规定数目的重复情况;

WHILE LOOP则根据控制条件执行循环直到条件为

FALSE。

FOR LOOP语句

FOR LOOP格式:

[标号:] FOR 循环变量 IN 循环次数范围 LOOP

顺序处理语句;

END LOOP [标号];

循环变量:属于LOOP语句的局部变量,不需要事先定义,也不能 被赋值,它的值从循环次数范围的初值开始,执行一次顺序语句 自动加一,当其值超出循环次数范围时,则退出循环语句。

5.1.1赋值语句

语句格式: 变量赋值目标:= 赋值源;

信号赋值目标<= 赋值源;

比较: (1)信号赋值有一定的延时,在时序电路中,在时 钟信号触发下的信号赋值,目标信号要比源信号延迟 一个时钟周期;变量赋值语句立即执行,没有延时。 (2)进程中同一变量多次赋值时按顺序立即执行, 而信号多次赋值时,只有进程结束前最后一个赋值被 执行。

不完整IF语句

作用:形成锁存,用于构成时序电路,而组合电路只能

使用完整的IF语句。

例5-6: IF (clk’event and clk=’1’) then

Q<=d;

End if;

二选一IF语句

语句格式:

IF 条件 THEN 顺序执行语句1;

任务3VHDL的赋值语句

说明语句

构

造

功能描述语句

体

块语句

结

进程语句

构

信号赋值语句

图

子程序调用语句

元件例化语句

并行语句

构 造 体

并行语句1 signal

并行语句2 signal

并行语句3

并行语句

各种并行语句在结构体中的执行是同步 进行的,或者说是并行运行的,其执行 方式与书写的顺序无关。

在执行中,并行语句之间可以有信息往 来,也可以是互为独立、互不相关、异 步运行的(如多时钟情况)。

s

例:4 选 1 数据选择器

2

a b

c

Architecture a of mux4_1 is d

Begin

mux x

x <= (a AND NOT(s(1)) AND NOT(s(0))) OR

(b AND NOT(s(1)) AND s(0)) OR

(c AND s(1) AND NOT(s(0))) OR

j <= w when (a = ‘1’) else x when (b = ‘1’) else y when (c = ‘1’) else z when (d = ‘1’) else ‘0’ ;

允许有多个 控制信号

选择信号赋值语句(With_Select_When)

语法格式:

WITH selection_signal SELECT signal_name <= value_1 WHEN value_a, value_2 WHEN value_b, ... value_n WHEN value_n, value_x WHEN OTHERS;

WHEN “00”=>y<=‘1’; --当ab=00时,y=1

VHDL并行语句

PROCEDURE 过程名(参数1;参数2;) IS [声明语句;]

BEGIN [顺序处理语句;]

END 过程名;

并行过程调用:

过程名(关联参数表);

参数关联方式

位置关联方式 名字关联方式 =>

例:设有一过程PROCEDURE vect(a,b:IN BIT;

output1 <= a AND b ; output2 <= c + d ; g <= e OR f ; h <= e XOR f ; s1 <= g ; END ARCHITECTURE curt;

2、条件信号赋值语句

赋值目标 <= 表达式 WHEN 赋值条件 ELSE 表达式 WHEN 赋值条件 ELSE ... 表达式 ;

PROCESS语句在VHDL程序中,是描述硬件并行工作 行为的最常用、最基本的语句。

PROCESS 组成 PROCESS语句结构

进程说明

顺序描述语句

敏感信号参数表

信

变

进

子

顺

进

号

量

程

程

序

程

赋

赋

启

序

描

跳

值

值

动

调

述

出

语

语

语

用

语

语

句

句

句

语

句

句

句

说明

(1) 进程说明部分主要定义一些局部量,可包括数据 类型、常数、属性、子程序等。但需注意,在进程说 明部分中不允许定义信号和共享变量。

-- 指定信号

-- 指定变量

-- 过程调用

四 VHDL语句

例:用WHEN-ELSE实现四选一数据选择器 实现四选一数据选择器

LIBRARY IEEE; ; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY mux4 IS PORT( a0,a1,a2,a3:IN STD_LOGIC; s :IN STD_LOGIC_VECTOR(1 DOWNTO 0); y :OUT STD_LOGIC ); END mux4; ARCHITECTURE archmux OF mux4 IS BEGIN y<= a0 WHEN s="00" ELSE a1 WHEN s="01" ELSE a2 WHEN s="10" ELSE a3 ; END archmux;

例:设计一个电路,包含一个半加器和一个半减器,分 设计一个电路,包含一个半加器和一个半减器, 别算出A+B和A-B的结果. 的结果. 别算出 和 的结果

LIBRARY IEEE; ; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY adsub IS PORT( a,b co,sum,bo,sub ); END adsub;

2,变量 , 语句格式: 语句格式:

VARIABLE 变量名称:数据类型 初值; 变量名称:数据类型:=初值 初值; 1,变量只能在进程和子程序中定义和使用. ,变量只能在进程和子程序中定义和使用. 2,变量赋值没有时间延时. 2,变量赋值没有时间延时. 3,变量不能放在进程的敏感信号表中. ,变量不能放在进程的敏感信号表中. 4,变量所赋值的数据类型必须与定义的数据类型一致. ,变量所赋值的数据类型必须与定义的数据类型一致.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

vhdl条件赋值语句

vhdl是一种硬件描述语言,用于描述硬件电路的行为和结构。

在vhdl中,条件赋值语句是一种常用的语法结构,用于根据特定条件给变量赋值。

下面列举了10个关于vhdl条件赋值语句的例子。

1. 当输入信号X为1时,将输出信号Y赋值为0;否则将Y赋值为1。

```vhdl

process (X)

begin

if X = '1' then

Y <= '0';

else

Y <= '1';

end if;

end process;

```

2. 当输入信号A为0时,将输出信号B赋值为C的值;否则将B赋值为D的值。

```vhdl

process (A, C, D)

begin

if A = '0' then

B <= C;

else

B <= D;

end if;

end process;

```

3. 根据输入信号Sel的值,选择对应的输入信号并赋值给输出信号Out。

```vhdl

process (Sel, In1, In2, In3)

begin

case Sel is

when "00" =>

Out <= In1;

when "01" =>

Out <= In2;

when "10" =>

Out <= In3;

when others =>

Out <= "0000";

end case;

end process;

```

4. 如果输入信号X大于等于Y,则将输出信号Z赋值为1;否则将Z赋值为0。

```vhdl

process (X, Y)

begin

if X >= Y then

Z <= '1';

else

Z <= '0';

end if;

end process;

```

5. 当输入信号Valid为1且输入信号Data的值为偶数时,将输出信号Even赋值为1;否则将Even赋值为0。

```vhdl

process (Valid, Data)

begin

if Valid = '1' and Data mod 2 = 0 then

Even <= '1';

Even <= '0';

end if;

end process;

```

6. 当输入信号X为1时,将输出信号Y赋值为X的平方;否则将Y 赋值为X的立方。

```vhdl

process (X)

begin

if X = '1' then

Y <= X * X;

else

Y <= X * X * X;

end if;

end process;

```

7. 如果输入信号A等于B且C等于D,则将输出信号X赋值为1;否则将X赋值为0。

```vhdl

process (A, B, C, D)

if A = B and C = D then

X <= '1';

else

X <= '0';

end if;

end process;

```

8. 根据输入信号Sel的值,选择对应的输入信号的最大值并赋值给输出信号Max。

```vhdl

process (Sel, In1, In2, In3)

begin

case Sel is

when "00" =>

Max <= In1;

when "01" =>

Max <= In2;

when "10" =>

Max <= In3;

when others =>

Max <= '0';

end case;

end process;

```

9. 当输入信号A为0时,将输出信号B赋值为1;当A为1时,将B赋值为2;否则将B赋值为3。

```vhdl

process (A)

begin

case A is

when '0' =>

B <= '1';

when '1' =>

B <= '2';

when others =>

B <= '3';

end case;

end process;

```

10. 根据输入信号Sel的值,选择对应的输入信号并将其左移一位后赋值给输出信号Out。

```vhdl

process (Sel, In1, In2, In3)

begin

case Sel is

when "00" =>

Out <= In1 sll 1;

when "01" =>

Out <= In2 sll 1;

when "10" =>

Out <= In3 sll 1;

when others =>

Out <= '0';

end case;

end process;

```

以上是10个关于vhdl条件赋值语句的例子,每个例子都展示了不同的条件判断和赋值方式。

通过合理使用条件赋值语句,可以实现复杂的电路行为描述,提高硬件设计的灵活性和可重用性。