vhdl if else语句

verilog中if else时序综合出的电路

一、引言Verilog作为一种硬件描述语言,在数字电路设计中有着广泛的应用。

在Verilog中,if else条件语句是一种常见的逻辑控制结构,用于在电路设计中进行条件判断和执行不同的操作。

在进行时序综合时,if else语句会被转化为硬件电路,因此了解if else时序综合出的电路对于Verilog电路设计具有重要的意义。

二、if else时序综合1. if else语句在Verilog中,if else语句用于根据条件的真假执行不同的操作。

例如:```if (condition)// do somethingelse// do something else```这样的语句在逻辑电路中会被转化为一个条件判断电路,根据条件的真假选择不同的路径。

2. 时序综合时序综合是将逻辑电路描述转化为物理电路的过程,包括将Verilog 描述转化为逻辑门、寄存器等电路元件。

在进行时序综合时,if else语句会被转化为逻辑门电路。

三、if else时序综合出的电路1. 逻辑门在Verilog中,if else语句会被转化为逻辑门电路。

对于简单的if else条件语句,可能被转化为一个MUX(多路选择器)电路,根据条件的真假选择不同的输入。

2. 寄存器在一些复杂的情况下,if else语句会被转化为寄存器电路。

如果条件判断需要在多个时钟周期内进行,就需要引入寄存器来存储条件的真假,以保持状态一致性。

3. 时序逻辑对于包含时序逻辑的if else语句,会涉及到时序逻辑电路的设计。

时序逻辑包括时钟信号、时钟边沿等时序特性,需要特别考虑时序综合的影响。

四、影响因素1. 条件复杂度if else语句中条件的复杂度会对时序综合出的电路产生影响。

复杂的条件判断可能需要更多的逻辑门或寄存器来实现,增加电路的复杂度和面积。

2. 时序要求对于需要满足一定时序要求的电路,if else时序综合出的电路需要符合时序约束,保证在时钟周期内正确地执行条件判断。

VHDL基本语句

例

ARCHITECTURE example OF mux4 IS BEGIN PROCESS (sel) 注 BEGIN ●CASE中的选择值必须在表达式的取值范围内; CASE sel IS WHEN 0=> q <= d0 ; ●CASE语句是无序的,所有表达式值都是并行 WHEN 1=> q <= d1 ; 处理;而IF语句是有序的,最起始、最优先 WHEN 2=> q<= d3 ; WHEN 3=> q<= d4 ; 的先处理; WHEN others => NULL; ●可以有很多分支,但OTHERS分支只能有一个, END CASE; 且只能位于最后;用来使所有选择值能涵盖表 END PROCESS; END example; 达式的所有取值,以免插入不必要的锁存器

3、用于多选控制的IF语句:

格式 IF 条件1 THEN

<顺序处理语句1>;

ELSIF 条件2 THEN <顺序处理语句2>; : ELSIF 条件n-1 THEN <顺序处理语句n-1>; ELSE <顺序处理语句n>; END IF;

P1: PROCESS (clk) BEGIN

IF (clk‘ event and clk=‗1‘ ) THEN

顺序语句

赋值语句

VHDL设计实体内的数据传递以及对端口界面外部数据的读写 都必须通过赋值语句的运行来实现。 功能是将一个值或表达式的运算结果传递给某一数据对象。 赋值语句有两种: 信号赋值语句和变量赋值语句 区别

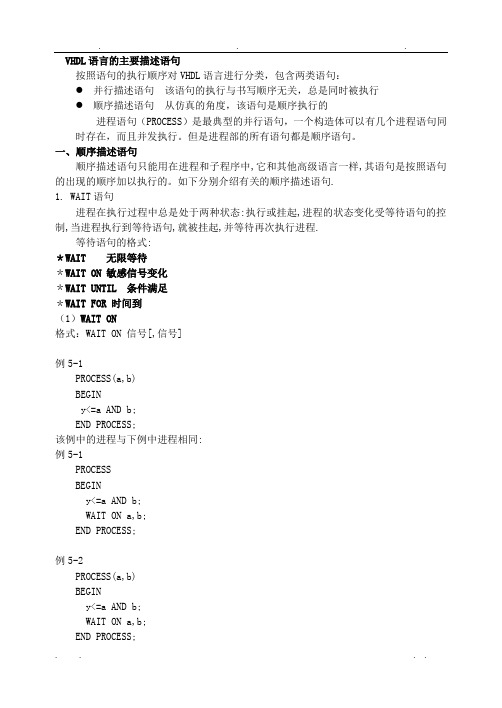

VHDL语言的主要描述语句

VHDL语言的主要描述语句按照语句的执行顺序对VHDL语言进行分类,包含两类语句:●并行描述语句该语句的执行与书写顺序无关,总是同时被执行●顺序描述语句从仿真的角度,该语句是顺序执行的进程语句(PROCESS)是最典型的并行语句,一个构造体可以有几个进程语句同时存在,而且并发执行。

但是进程部的所有语句都是顺序语句。

一、顺序描述语句顺序描述语句只能用在进程和子程序中,它和其他高级语言一样,其语句是按照语句的出现的顺序加以执行的。

如下分别介绍有关的顺序描述语句.1.WAIT语句进程在执行过程中总是处于两种状态:执行或挂起,进程的状态变化受等待语句的控制,当进程执行到等待语句,就被挂起,并等待再次执行进程.等待语句的格式:*WAIT 无限等待*WAIT ON 敏感信号变化*WAIT UNTIL 条件满足*WAIT FOR 时间到(1)WAIT ON格式:WAIT ON 信号[,信号]例5-1PROCESS(a,b)BEGINy<=a AND b;END PROCESS;该例中的进程与下例中进程相同:例5-1PROCESSBEGINy<=a AND b;WAIT ON a,b;END PROCESS;例5-2PROCESS(a,b)BEGINy<=a AND b;WAIT ON a,b;END PROCESS;(2)WAIT UNTIL 直到条件满足格式: WAIT UNTIL 布尔表达式当进程执行到该语句时,被挂起;若布尔表达式为真时,进程将被启动.例: WAIT UNTIL ((x*10)<100)(3)WAIT FOR 等到时间到格式: WAIT FOR 时间表达式当进程执行到该语句时,被挂起;等待一定的时间后,进程将被启动.例: WAIT FOR 20 ns;WAIT FOR (a*(b+c);(4)多条件WAIT 语句例: WAIT ON nmi,interrupt UNTIL ((nmi=TRUE) OR (interrupt=TRUE)) FOR 5 us 该等待有三个条件:第一,信号nmi和interrupt 任何一个有一次刷新动作第二, 信号nmi和interrupt 任何一个为真第三, 已等待5 us只要一个以上的条件被满足,进程就被启动.*注意:多条件等待时,表达式的值至少应包含一个信号量的值。

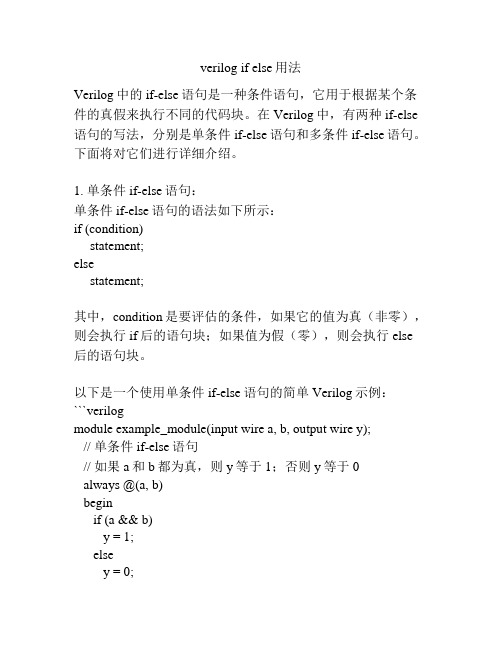

verilog if else用法

verilog if else用法Verilog中的if-else语句是一种条件语句,它用于根据某个条件的真假来执行不同的代码块。

在Verilog中,有两种if-else 语句的写法,分别是单条件if-else语句和多条件if-else语句。

下面将对它们进行详细介绍。

1. 单条件if-else语句:单条件if-else语句的语法如下所示:if (condition)statement;elsestatement;其中,condition是要评估的条件,如果它的值为真(非零),则会执行if后的语句块;如果值为假(零),则会执行else 后的语句块。

以下是一个使用单条件if-else语句的简单Verilog示例:```verilogmodule example_module(input wire a, b, output wire y);// 单条件if-else语句// 如果a和b都为真,则y等于1;否则y等于0always @(a, b)beginif (a && b)y = 1;elsey = 0;endendmodule```2. 多条件if-else语句:多条件if-else语句的语法如下所示:if (condition)statement;else if (condition)statement;elsestatement;其中,condition是要评估的条件,它们按顺序逐个进行评估,直到找到一个条件为真为止。

如果所有条件都为假,则执行else后的语句块。

以下是一个使用多条件if-else语句的Verilog示例:```verilogmodule example_module(input wire a, b, c, output wire y);// 多条件if-else语句// 根据a、b和c的值,计算y的取值always @(a, b, c)beginif (a && b)y = 1;else if (b && c)y = 2;else if (a || c)y = 3;elsey = 0;endendmodule```可以看到,在上述示例中,根据条件的真假,y的取值会有不同的选择。

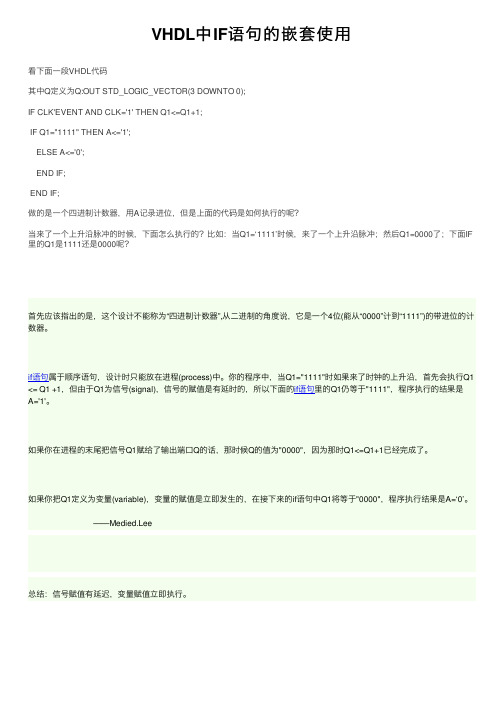

VHDL中IF语句的嵌套使用

VHDL中 IF语句的嵌套使用

看下面一段VHDL代码 其中Q定义为Q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); IF CLK'EVENT AND CLK='1' THEN Q1<=Q1+1; IF Q1="1111" THEN A<='1';

ELSE A<='0'; END IF; END IF; 做的是一个四进制计数器,用A记录进位,但是上面的代码是如何执行的呢? 当来了一个上升沿脉冲的时候,下面怎么执行的?比如:当Q1=‘1111’时候,来了一个上升沿脉冲;然后Q1=0000了;下面IF 里的Q1是1111还是0000呢?

首先应该指出的是,这个设计不能称为“四进制计数器”,从二进制的角度说,它是一个4位(能从“0000”计到“1111”)的带进位的计 数器。

if语句属于顺序语句,设="1111"时如果来了时钟的上升沿,首先会执行Q1 <= Q1 +1,但由于Q1为信号(signal),信号的赋值是有延时的,所以下面的if语句里的Q1仍等于"1111",程序执行的结果是 A='1'。

如果你在进程的末尾把信号Q1赋给了输出端口Q的话,那时候Q的值为"0000",因为那时Q1<=Q1+1已经完成了。

如果你把Q1定义为变量(variable),变量的赋值是立即发生的,在接下来的if语句中Q1将等于"0000",程序执行结果是A=‘0’。 ——Medied.Lee

总结:信号赋值有延迟,变量赋值立即执行。

vhdl中if语句和case语句的综合_不同

VHDL中 If语句和Case语句的综合If 和case语句是VHDL里边两个非常重要的语句,如何用好她们来描述逻辑电路和时序电路是学会VHDL编程重要的一步。

if 和case语句有一定的相关性,也有一定的区别。

相同的地方是他们可以实现几乎一样的功能。

下面主要介绍一下她们之间的区别。

If 语句每个分支之间是有优先级的,综合得到的电路是类似级联的结构。

Case语句每个分支是平等的,综合得到的电路则是一个多路选择器。

因此,多个if elseif语句综合得到的逻辑电路延时往往比case语句要大。

一些初学者在一开始往往喜欢用if elsif语句,因为这种语法表达起来更加直接,但是在运行速度比较关键的项目中,使用case语句的效果会更好。

下面的例子给出了if语句和case语句的综合结果If 语句综合结果Case语句综合结果有关if, case语句另外一个值得一提的东西是在用if或者case语句做逻辑电路的时候,必须为信号设置默认值。

有两种方法,第一种方法是在if, case 语句之前对目标信号进行赋值,采用这种方法,就不必专门写else或者when others语句对信号进行默认赋值。

第二种方法就是在else或者when others语句中对信号进行默认条件下的赋值。

如果违反了上述规则,那么会在综合电路的时候形成一个transparent latch(锁存器),也就是电平触发的锁存器,这对电路的时序分析等会造成很大的麻烦。

在时序电路中,如果没有在else语句或者when others语句中对信号赋值,那么综合工具会认为寄存器保持当前输入。

从电路图上看,即把寄存器的输出接回寄存器的输入。

有兴趣的朋友可以用综合工具试一下面的代码,鉴于篇幅,时序电路部分的代码就不贴了,有需要的朋友可以给我留言。

library ieee;useuse CaseComb isport(aSel : in std_logic_vector(3 downto 0);aDin : in std_logic_vector(3 downto 0);aDout : out std_logic);end CaseComb;architecture rtl of CaseComb isbeginprocess(aSel, aDin)begincase aSel iswhen "1000" =>aDout <= aDin(3);when "0100" =>aDout <= aDin(2);when "0010" =>aDout <= aDin(1);when "0001" =>aDout <= aDin(0);when others =>--aDout <= '0';end case;end process;end rtl;library ieee;useuse IfComb isport(aSel : in std_logic_vector(3 downto 0);aDin : in std_logic_vector(3 downto 0);aDout : out std_logic);end IfComb;architecture rtl of IfComb isbeginprocess(aSel, aDin)beginif aSel(3)='1' thenaDout <= aDin(3);elsif aSel(2)='1' thenaDout <= aDin(2);elsif aSel(1)='1' thenaDout <= aDin(1);elsif aSel(0)='1' thenaDout <= aDin(0);--else-- aDout <= '0';end if;end process;end rtl;。

vhdl if else语句

vhdl if else语句

VHDL

(VeryHigh-SpeedIntegratedCircuitHardwareDescriptionLanguag e)是一种硬件描述语言,它可以用来描述数字电路的行为。

if-else 语句是VHDL中常用的条件语句。

它用于根据一个条件是否成立来执

行不同的操作,语法如下:

if condition_1 then

--执行操作1

elsif condition_2 then

--执行操作2

else

--执行操作3

end if;

其中,condition_1是一个布尔表达式,如果它的值为TRUE,就执行第一个操作;如果值为FALSE,则继续判断condition_2,如果

它的值为TRUE,则执行第二个操作;如果condition_2的值也为FALSE,则执行第三个操作。

在VHDL中,if-else语句也可以嵌套使用,以实现更复杂的条

件判断。

在使用if-else语句时,需要注意以下几点:

1. 条件表达式必须是布尔型的,即只能取TRUE或FALSE两个值。

2. 在每个条件分支中,必须有且仅有一个操作被执行。

3. else语句是可选的,如果没有else语句,则当所有条件都

不成立时,不会执行任何操作。

4. 在VHDL中,if-else语句可以与选择语句(case语句)结合使用,以实现更灵活的条件判断。

总之,if-else语句是VHDL中常用的条件语句,用于根据一个条件是否成立来执行不同的操作。

要使用if-else语句,需要熟悉它的语法和注意事项。

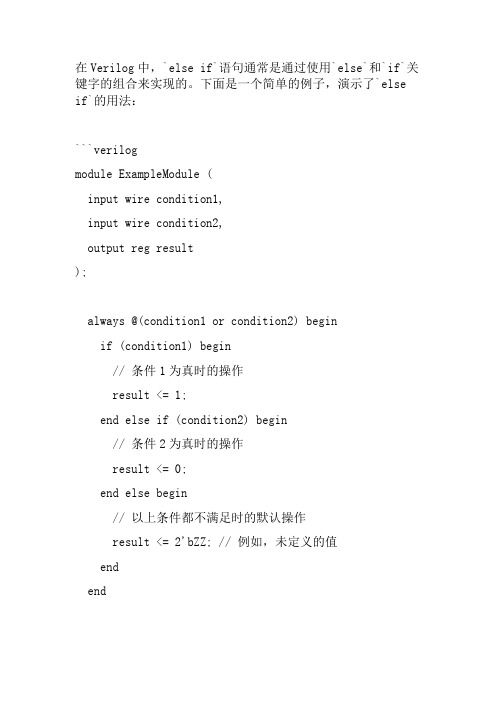

verilog中else if的用法

在Verilog中,`else if`语句通常是通过使用`else`和`if`关键字的组合来实现的。

下面是一个简单的例子,演示了`else if`的用法:```verilogmodule ExampleModule (input wire condition1,input wire condition2,output reg result);always @(condition1 or condition2) beginif (condition1) begin// 条件1为真时的操作result <= 1;end else if (condition2) begin// 条件2为真时的操作result <= 0;end else begin// 以上条件都不满足时的默认操作result <= 2'bZZ; // 例如,未定义的值endendendmodule```在这个例子中,`ExampleModule`模块有两个输入条件`condition1` 和 `condition2`,以及一个输出 `result`。

在`always` 块中,使用 `if`、`else if` 和 `else` 来根据不同的条件执行相应的操作。

这个例子中,当 `condition1` 为真时,`result` 被赋值为 1;当 `condition2` 为真时,`result` 被赋值为 0;如果以上两个条件都不满足,就执行`else` 块中的操作,这里将 `result` 设置为未定义的值`2'bZZ`。

请注意,Verilog中的条件语句可以根据具体的需求嵌套使用,以处理更复杂的情况。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

vhdl if else语句

VHDL是硬件描述语言,用于描述数字电路。

if-else语句是VHDL中的一种常见控制结构。

if-else语句用于在某些条件下执行不同的操作。

其语法如下:

if (condition) then

--执行语句1

elsif (condition2) then

--执行语句2

else

--执行语句3

end if;

上面的语法中,condition是一个布尔表达式,用于检查是否满足某个条件。

如果满足该条件,则执行语句1。

如果不满足该条件,则继续检查condition2。

如果满足condition2,则执行语句2。

如果都不满足条件,则执行语句3。

在VHDL中,if-else语句可以嵌套使用。

例如:

if (condition) then

if (condition2) then

--执行语句1

else

--执行语句2

end if;

else

--执行语句3

end if;

此外,VHDL还提供了一种简化if-else语句的方式,称为when-else语句。

其语法如下:

case variable is

when value1 =>

--执行语句1

when value2 =>

--执行语句2

when others =>

--执行语句3

end case;

在上面的语法中,variable是一个变量,value1和value2是变量的不同取值。

当variable的值等于value1时,执行语句1。

当variable的值等于value2时,执行语句2。

当variable的值不等于value1和value2时,执行语句3。

总之,if-else语句是VHDL中非常重要的控制结构,用于根据不同的条件执行不同的操作。

使用if-else语句可以使代码更加清晰易懂。