基于FPGA的图像采集系统设计与实现

基于FPGA的一体化实时图像采集系统设计

快 速采 样 、存 储及 图像 数据 处 理 就 显 得 尤 为必 要。 传统 的使 用单 片机作 为控 制器 对数 据进 行 间

B a s e d o n C MO S i m a g e s e n s o r ,o n e F i e l d P r o g r a m ma b l e G a t e A r r a y ( F P G A )i s c h o s e n a s t h e

7 2 6 0 0 0 )

Ab s t r a c t : I n o r d e r t o o b t a i n r e a l - t i me a n d p r e c i s i o n i ma g e f r o m CMOS i ma g e s e n s o r ,a n i mp r o v e d r e a l - t i me d a t a a c q u i s i t i o n s y s t e m i s d e s i g n e d b a s e d o n t h e c o mb i n a t i 刘 萌

( 商洛学 院 物理与电子信息工程系, 陕西商洛 7 2 6 0 0 0 )

摘 要: 为 了通过 C MO S图像探测器实时准确 的获取 图像 。 设计 了一套基 于 F P G A结合 S D R A M

的 实时图像 采 集 系统。根据 C MO S图像探 测 器输 出图像 格式 的特 点 ,选 用 了一 片 X i l i n x公 司

Ke y wor ds : CMOS i ma g e s e n s o r ;F PGA;p i n g — po ng o p e r a t i o n;SDRAM

基于FPGA的多路图像采集系统的软件设计

ue o r AA7 1 H vd od c d r n woF GA oahe e tea q iio ssfu S 1 3 ie e o esa d t P t c iv h c ust n,soa e n ipa ft h n e ma e i trg ,a d dsly o woc a n li g ,

fl sre .I fr e e l e h ac d o f u ain o wo F GA,a d te F mnb s c n g rt n, te I U6 6 ul cen t ut rrai s te c sa e c n g rt ft P — h z i o n h C o iu o f u ai i o h T 5

( 安 工 业 大 学 计 算机 科 学 与 工程 学 院 , 西 西 安 7 0 3 ) 西 陕 10 2

摘 要 :分 析 了 现 有 的 视 频 采 集 方 案 的 研 究现 状 。 对如 何 采 用 C D 摄 像 头采 集 多通 道 、 C 高分 辨 率 、 高质 量 的 图像 以及

基 于 F G 的 嵌 入 式 图 像 采 集 系统 的 实 现 方 法做 了研 究 。 与传 统 图像 采 集 系统 相 比 . 系统 主要 利 用 四 片视 频 解码 PA 该

关键 词 : A 7 l H;F G I U 6 ;图像 采 集 S A l3 P A; T 5 5

,

文 章 编 号 :17 — 2 6 2 1 )3 14 0 6 4 6 3 (0 号 :I 99 , 1 ’ P

文献标识码 : A

The s fwa e de i n o u t- ha ne m a e a q sto s s e b s d o FPGA o t r sg fm lic n li g c uiii n y t m a e n

基于ZYNQ FPGA实现图像采集存储显示

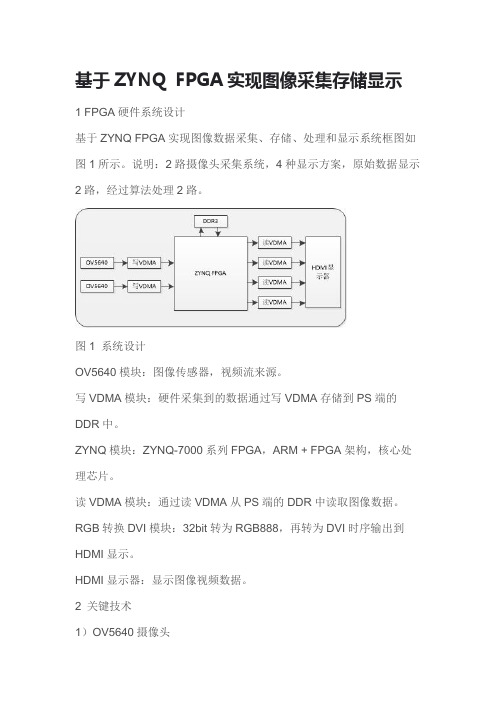

基于ZYNQ FPGA实现图像采集存储显示1 FPGA硬件系统设计基于ZYNQ FPGA实现图像数据采集、存储、处理和显示系统框图如图1所示。

说明:2路摄像头采集系统,4种显示方案,原始数据显示2路,经过算法处理2路。

图1 系统设计OV5640模块:图像传感器,视频流来源。

写VDMA模块:硬件采集到的数据通过写VDMA存储到PS端的DDR中。

ZYNQ模块:ZYNQ-7000系列FPGA,ARM + FPGA架构,核心处理芯片。

读VDMA模块:通过读VDMA从PS端的DDR中读取图像数据。

RGB转换DVI模块:32bit转为RGB888,再转为DVI时序输出到HDMI显示。

HDMI显示器:显示图像视频数据。

2 关键技术1)OV5640摄像头设计中采用两片美国OmniVision公司的CMOS图像传感器OV5640,OV5640芯片支持DVP和MIPI接口。

为保证OV5640正常工作,需要依次实现以下时序要求。

a、ResetB拉低、PWND拉高;b、DOVDD和AVDD同时上电;c、电源稳定5ms后,拉低PWND,再过1ms,拉高ResetB;d、20ms后初始化OV5640DESCCB寄存器。

e、通过IIC接口配置,配置目标为RGB565、30FPS、720输出格式;f、FPGA接收来自OV5640的视频流数据输入,需要对摄像头完成相应的时序操作。

每次传输8bit,16bit为一个像素点,所以要进行数据转换8bit-16bit-32bit;2)图像处理算法边缘检测算法要求首先找到图片中物体的边缘,由于边缘处颜色变化一般比较明显,在工程上一般借助卷积滤波器实现,卷积滤波器相当于求导的离散版本。

针对图像进行边缘检测,有多种不同的滤波器算子,我们采用的Sobel滤波器算子图1,分别针对图像水平方向的边缘以及竖直方向的边缘,求和得出图像的边缘。

图1 滤波器算子3)ZYNQ FPGAZYNQ 7000系列基于Xilinx 全可编程的扩展处理平台结构,芯片内部集成ARM 公司双核Cortex-A9处理器的处理系统(PS端)和基于Xilinx逻辑资源的可编程逻辑系统(PL端)。

基于FPGA和USB3.0的高速视频图像采集处理系统设计

摘要随着机器视觉的广泛应用,以及工业4.0和“中国制造2025”的提出,在数字图像的采集、传输、处理等领域也提出了越来越高的要求。

传统的基于ISA接口、PCI接口、串行和并行等接口的图像采集卡已经不能满足人们对于高分辨率、实时性的图像采集的需求了。

一种基于FPGA和USB3.0高速接口,进行实时高速图像采集传输的研究越来越成为国内外在高速图像采集研究领域的一个新的热点。

针对高速传输和实时传输这两点要求,通过采用FPGA作为核心控制芯片与USB3.0高速接口协调工作的架构,实现高帧率、高分辨率、实时性的高速图像的采集和传输,并由上位机进行可视化操作和数据的保存。

整体系统采用先硬件后软件的设计方式进行设计,并对系统各模块进行了测试和仿真验证。

通过在FPGA 内部实现滤波和边缘检测等图像预处理操作,验证了FPGA独特的并行数据处理方式在信号及图像处理方面的巨大优势。

在系统硬件设计部分,采用OV5640传感器作为采集前端,选用Altera的Cyclone IV E系列FPGA作为系统控制芯片,由DDR2存储芯片进行数据缓存,采用Cypress公司的USB3.0集成型USB3.0芯片作为数据高速接口,完成了各模块的电路设计和采集卡PCB实物制作。

系统软件设计,主要分为FPGA逻辑程序部分、USB3.0固件程序部分和上位机应用软件部分。

通过在FPGA上搭建“软核”的方式,由Qsys系统完成OV5640的配置和初始化工作。

由GPIF II接口完成FPGA和FX3之间的数据通路。

通过编写状态机完成Slave FIFO的时序控制,在Eclipse中完成USB3.0固件程序的设计和开发。

上位机采用VS2013软件通过MFC方式设计,从而完成整体图像采集数据通路,并在上位机中显示和保存。

整体设计实现预期要求,各模块功能正常,USB3.0传输速度稳定在320MB/s,通过上位机保存至PC机硬盘的图像分辨率大小为1920*1080,与传感器寄存器设置一致,采集卡图像采集帧率为30fps,滤波及边缘检测预处理符合要求,采集系统具有实际应用价值和研究意义。

基于FPGA的图像采集模块设计

口可兼 容 +5V, 常 工 作 时 功 耗 为 0 4 W , 闲 时 功 耗 为 正 . 空 o 0 。 钟 丢失 、 源 电 压 降 低 都 会 引起 芯 片 的 自动 复 . 7W 时 电 位, 因此 要 保 证 供 电系 统 的 稳 定 可靠 性 。

足 够 的 IE以及 RAM 单 元 , 在 其 内 部 实 现 像 预 处 理 为

行 同步信号 , 只有 在行 场 同步 信号 同时有效 时 , 且 才是 有

且 用 DS P的 IC总 线 来 配 置 其 内部 的 各 个 寄存 器 。这 里 把 S AA7 1 H 相 应 的 信 号 R 1 RTS 13 TS 、 0分 别 配 置 成 场 、

* 基 金 项 目: 东省 自然 科 学 基 金 ( o 62 69 。 广 N . 0 9 6 )

提 供 了保 障 , 且 具 有 足 够 的 I( 引 脚 使 其 方 便 与 其 他 设 并 /)

备 相 接 。本 文 将 详 细 描 述 F GA如 何 对 S P AA7 1 H 解 码 13 后 的 图 像 数 据 信 号 及 一 些 控 制 信 号 进 行 采 集 , 得 到 一 幅 并 完 整 的 图像 供后 续 系 统 进 行 处 理 。也 就 是 说 , 何 编 写 出 如 F GA程 序 来 控 制 各 个 信 号 , 而 采 集 图 像 。 最 后 , P 从 在 Qu ru IMo eSm 等 软 件 上 验 证 了 系 统 中一 些 重 要 的 at sI、 d l i 信 号 , 到 了较 为满 意 的效 果 。 达

出 8位 “ ’ VP 总线 , 标 准 的 I 为 TU6 6 YUV 5、 4:2: 2格 式 。 S AA7 1 H 的模 拟 与 数 字 部 分 均采 用 +3 3V, 字 Io接 13 . 数 /

基于FPGA的双通道CMOS图像采集系统设计

0 引 言

整 个 系 统 的 可 靠 性 。 同 时 , 用 2片 大 容 量 的 S R M 以 采 D A

目前 , 越来越多 的图像采集 系统采用 C S图像传 感 MO

器 …作为图像采 集器件 。随着 集成 电路设 计技 术 的不断 提高 , MO C S图像传 感器 的采集速 度不 断增大 。在 实际 应用 中, 传统 的单通道 数据传输 方式和单 片机实现 的图像 处理系统 已经远远无法满 足设计要 求 , 须采用新 的数据 必 传输方式和设计方法来实现图像采集 、 传输和存储功能。

本 文 设 计 了一 种 以 F G 芯 片 为 核 心 处 理 器 的 双 通 道 PA

乒乓操作 的方式进行 数据存储 , 保证 能够实时地接 收图像

传感器产生的图像数据 。 经综合 分 析 和考 虑,P A采 用 A e FG hr a的 C c n yl e o E 2 3 F8 C 视频采集芯片用 飞利 浦的 S A 132块 型 P C 5 4 4 8, A 71 , 号为 K S 42的 S R M 和 F G 463 D A P A构成 图像 帧存储 与传输

Ab ta t Re lt r c s ig o g s u u l o t — e k i mb d e ma e p o e sn y tm. a i g sr c : a — me p o e sn fi e i s al a b t e n c n e e d d i g rc s i g s s i ma y l e T kn

teavnaeo aae poes g af l por al gt ar ( P A)b sdC S i g cu io h da t fprll rcsi , e rga g l n id mm b a r y F G e e a ae MO mae aq it n si ss m ids nd T em d l s ut eds n fs i fsotFF yt ei e . h o u rc r ei ,rtni t u( IO)adpn—ags r cn l e r ue e s g et u g i r n igpn o t h o g s e sd tee o i a

基于FPGA的实时视频图像采集与显示系统的设计与实现

基于FPGA的实时视频图像采集与显示系统的设计与实现作者:贡镇来源:《现代电子技术》2013年第13期摘要:主要针对目前视频图像处理发展的现状,结合FPGA技术,设计了一个基于FPGA的实时视频图像采集与显示系统。

系统采用FPGA作为主控芯片,搭载专用的编码解码芯片进行图像的采集与显示,主要包括解码芯片的初始化、编码芯片的初始化、FPGA图像采集、PLL设置等几个功能模块。

采用FPGA的标准设计流程及一些常用技巧来对整个系统进行编程。

重点在于利用FPFA开发平台对普通相机输出的图像进行采集与显示,最终能在连接的RCA端口显示屏显示。

关键词: FPGA;视频图像采集;编码芯片;解码芯片中图分类号: TN911⁃34 文献标识码: A 文章编号: 1004⁃373X(2013)13⁃0046⁃03Design and Implementation of real⁃time video image captureand display system based on FPGAGONG Zhen(Anhui University of Science and Technology, Huainan 232000, China)Abstract: Based on the current development status of the video image processing and FPGA technology, a FPGA⁃based real⁃time video image capture and display system is designed in this paper. Equipped with dedicated coding and decoding ship for image capture and display, the system adopts FPGA as the main control chip, which are composed of decoding chip initialization module, the encoding chip initialization module, FPGA image acquisition module and PLL setting module. FPGA⁃standard design flow and some commonly used techniques are taken to program the entire system. The focus is to realize the ordinary camera output image acquisition and display via the FPFA development platform, and ultimately connect the RCA port display screen.Keywords: FPGA; video image capture; coding chip; decoding chip0 引言随着时代的发展,人们在图像处理领域取得了相当多的成果,研究出了很多算法,例如中值滤波、高通滤波等。

基于FPGA的图像处理系统设计与实现

基于FPGA的图像处理系统设计与实现图像处理是计算机视觉领域中的重要技术之一,可以对图像进行增强、滤波、分割、识别等操作,广泛应用于医学图像处理、工业检测、安防监控等领域。

而FPGA(Field Programmable Gate Array)可编程门阵列,则是一种自由可编程的数字电路,具有并行处理能力和灵活性。

本文将介绍基于FPGA的图像处理系统的设计与实现。

一、系统设计流程1. 系统需求分析:首先需要明确图像处理系统的具体需求,例如实时性、处理的图像类型、处理的算法等。

根据需求,选择合适的FPGA芯片和外设。

2. 图像采集与预处理:使用图像传感器或摄像头采集图像数据,然后对图像进行预处理,如去噪、增强、颜色空间转换等,从而提高后续处理的准确性和效果。

3. 图像处理算法设计与优化:根据具体的图像处理需求,选择适合的图像处理算法,并对算法进行优化,以提高处理速度和效率。

常用的图像处理算法包括滤波、边缘检测、图像分割等。

4. FPGA硬件设计:基于选定的FPGA芯片,设计硬件电路,包括图像存储、图像处理模块、通信接口等。

通过使用硬件描述语言(如Verilog、VHDL)进行功能模块设计,并进行仿真和验证。

5. 系统集成与编程:将设计好的硬件电路与软件进行集成,包括FPGA程序编写、软件驱动开发、系统调试等。

确保系统的稳定运行和功能实现。

6. 系统测试与优化:对整个系统进行完整的测试和验证,包括功能性测试、性能测试、稳定性测试等。

根据测试结果,对系统进行优化,提高系统的性能和可靠性。

二、关键技术及挑战1. FPGA芯片选择:不同的FPGA芯片具有不同的资源和性能特点,需要根据系统需求选择合适的芯片。

一方面需要考虑芯片的处理能力和资源利用率,以满足图像处理算法的实时性和效果。

另一方面,还需要考虑芯片的功耗和成本,以便在实际应用中具有可行性。

2. 图像处理算法优化:在FPGA上实现图像处理算法需要考虑到算法的计算复杂度和存储开销。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的图像采集系统设计与实现摘要现在是科技迅速发展的年代,数字图像处理技术在这个年代中得到了迅猛的发展并在各行各业得到了广泛的应用。

可编程逻辑器件(FPGA)凭借其较低的开发成本、较高的并行处理速度、较大的灵活性及其较短的开发周期等特点,在图像处理系统中有独特的优势。

针对视频图像采集的可靠性和实时性,本设计采用Altera公司生产的CycloneⅡEP2C8Q208C8NK芯片,先由CCD图像传感器采集模拟信号,在经过芯片TVP5150将模拟量转换为标准的YUV4:2:2的数据信号,把数据信号输入到FPGA芯片中并在其中将该数据转换到RGB色域后在输出到ADV7123芯片进行D/A转换,最后经过VGA接口电路把处理过的图像呈现在显示屏上。

经过相关的调试工作,系统通用性比较好,并且移动性能也不错。

该系统的软件部分采用自顶向下的设计方法,模块化设计思想,硬件语言编程,只修改源程序,不必更改硬件电路,就可实现在线编程,实时控制,从而有效地减少系统的体积,不但增加了系统可靠性,降低研制成本,并且能够对控制逻辑进行修改升级,十分灵活。

该系统包括三个功能模块:图像采集模块、图像处理模块、图像显示模块。

关键词:FPGA;TVP5150;RGB色域;ADV7123芯片Image acquisition system based on FPGA design andimplementationAbstractIt is the rapid development of science and technology, digital image processing technology has been rapid development in this era and has been widely used in all walks of life, and the maturity of FPGA technology has changed the commonly used parallel computer or digital signal processor (DSP), a special integrated circuit (ASIC) as the embedded processor usage. Programmable logic device (FPGA) with its low cost, high parallel processing speed, flexibility and short development cycle and other characteristics, has its unique advantages in image processing system. The project demand, this paper presents a solution of image acquisition and processing system based on FPGA, and the use of low cost and high performance of Altera company's CyclonelI series FPGA EP2C8Q208C8N as the core, design and development of integrated system of hardware and software of image acquisition and processing.In view of the reliability of video image acquisition and real-time performance, this paper describes how to FPGA for video acquisition system control. Using Cyclone Ⅱ EP2C8Q208C8NK chip produced by Altera company, is responsible for receiving and processing video data from the TVP5150 decoding, converts the data into RGB color gamut in the output to the ADV7123 chip. After debugging, the system better generality, and mobile performance is also good.Keywords:FPGA;TVP5150;RGB color gamut;ADV7123 chip目录1 前言 (1)1.1课题背景与意义 (1)1.2研究的现状及特点 (2)1.3研究的主要内容 (2)2 图像采集系统的硬件电路设计 (3)2.1采集系统硬件的总体设计 (3)2.2FPGA核心模块 (5)2.3外围电路 (6)2.4图像采集电路 (7)2.4.1图像传感器 (7)2.4.2A/D转换电路 (8)2.5图像显示电路 (8)3 图像采集系统的软件设计 (11)3.1系统的设计环境 (11)3.2设计的主要流程 (12)3.3设计内部数据量的变换 (12)3.3.1IIC数据总线 (12)4 调试 (17)参考文献 (18)致谢 (19)附录 (20)1 前言1.1 课题背景与意义随着多媒体技术在各个应用领域不断普及,用户会不断要求新产品具有更大的图像容量、更高的图像质量和更快的图像处理速度,这为图像的存储和处理提出了更高的要求。

在数字图像处理可视电话通信、数字电视等应用中,遇到的首要难题就是数据量过大,导致图像传输和存储成问题。

现场可编程门阵列(FPGA),与传统逻辑电路和门阵列相比FPGA 具有不同的结构它增强了电路设计的灵活性。

不但降低了开发成本,而且也减小了设计风险,并且充分挖掘图像处理算法中的并行性,在较低主频下能获得可观的执行速度。

因此,在信号处理方面得到了广泛的应用。

FPGA作为系统以及图像采集处理板卡的核心器件,外围器件的电路和功能已经得到尽可能的简化,许多外围的功能器件的接口都不需要单独的接口芯片来完成,均由FPGA来实现.整个系统中仅仅需要FPGA以及FPGA配置芯片、SDRAM、PCI接口芯片三个主要的芯片,整体上看提高了电路的稳定性,而且其先进的开发工具使整个系统的设计调试周期大大缩短。

因此FPGA内部逻辑设计就成为图像采集处理系统设计的核心和关键。

1.2 研究的现状及特点20世纪20年代,图像处理首次得到应用。

20世纪60年代中期,随电子计算机的发展得到普遍应用。

60年代末,图像处理技术不断完善,逐渐成为一个新兴的学科。

利用数字图像处理主要是为了修改图形,改善图像质量,或是从图像中提起有效信息,还有利用数字图像处理可以对图像进行体积压缩,便于传输和保存。

数字图像处理主要研究以下内容:傅立叶变换、小波变换等各种图像变换;对图像进行编码和压缩;采用各种方法对图像进行复原和增强;对图像进行分割、描述和识别等。

随着技术的发展,数字图像处理主要应用于通讯技术、宇宙探索遥感技术和生物工程等领域。

数字图像处理因易于实现非线性处理,处理程序和处理参数可变,故是一项通用性强、精度高、处理方法灵活、信息保存、传送可靠的图像处理技术。

主要用于图像变换、量测、模式识别、模拟以及图像产生,并广泛应用在遥感、宇宙观测、影像医学、通信、刑侦及多种工业领域[1]。

而在对图像处理这一技术上FPGA具有以下几种特点:(1):高性能,可以在一片FPGA中完成多种处理功能(2):灵活性高使产品快速面市,方便产品跟新,满足不断发展的需求(3):低开发成本并且结构化容易操作(4):不会过时,其拥有非常广泛的客户基础,而且FPGA可以很容易的从一个工作节点移植到下一个工作节点。

1.3 研究的主要内容先利用CCD图像传感器采集图像模拟量输入给TVP5150芯片,再利用Altera公司的CyclonelI系列FPGA EP2C8Q208C8N芯片,负责接受和处理来自TVP5150解码后的视频数据,将该数据转换到RGB色域后在输出到ADV7123芯片再传输到液晶显示器。

在系统设计过程中需要研究以下问题:(1):制定图像采集系统的整体的设计方案.。

(2):设计图像采集模块,图像处理模块,图像显示模块,和FPGA主控制模块。

(3):程序的编译与仿真,通过对程序的编译与仿真实现了对FPGA芯片控制,将数据转换到RGB色域后输出。

系统设计过程中主要通过Quartus9.1的开发环境编译系统的程序,然后使用下载软件将程序下载到单片机运行,通过运行情况修改程序再进行调试。

调试的是从单个模块开始,然后进行综合调试至系统功能的实现。

2 图像采集系统的硬件电路设计2.1 采集系统硬件的总体设计如图2-1所示:该系统包括几个功能模块:图像采集模块、图像处理模块、图像显示模块。

其中图像采集模块主要由外接摄像头和TVP5150 解码芯片组成,完成视频信号的采集和硬件解码能,并以ITU-656 标准输出YUV 4:2:2 信号;图像处理模块选用的FPGA 是Altera 公司生产的Cyclone ⅡEP2C8Q208C8N 芯片构成,完成系统控制,视频信号的采集以及后续处理等工作;图像显示模块主要由ADV7123 芯片、VGA 接口和CRT 显示器等组成,主要完成视频信号的数模转换,输出并显示视频信号。

图2-1 图像采集系统的硬件总体设计在图2-1所示视频图像的采集与处理过程中,FPGA作为整个系统的控制与处理核心,主要是通过该芯片的I/O 管脚来控制数据采集芯片TVP5150和高速D/A 转换芯片ADV7123,并且负责接受和处理来自TVP5150解码后的视频数据,将该数据转换到RGB 色域后输出到ADV7123芯片。

实物如图2-2所示:图2-2 硬件实物2.2 FPGA核心模块在充分考虑性价比和设计功能的基础上,决定采用Altera公司CycloneII系列的FPGA,它是Altera公司最新一代SRAMI艺、中等规模的低成本FPGA,与Stratix结构类似,是目前的主流产品。

它支持各种单端I/O标准(如LVlvrL、LVCOS、和SSTL.2/3),通过LVDS和RSDS 标准提供多达227个通道的差分I/O支持,LVDS通道高达640Mbps。

它具有生成时钟锁相环以及DDR、SDR和快速RAM(FCRAM)存储器所需的专用双数据率(DDR)接口等。