计算机组成原理 主存储器设计举例

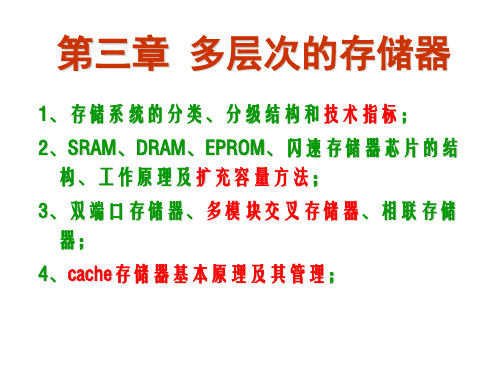

数字逻辑与计算机组成原理:第三章 存储器系统(1)

A3 0

字线

地0 A2 0 址

译

A1

0码 器

A0 0

15

读 / 写选通

… …

…

0,0 … 0,7

16×8矩阵

15,0 … 15,7

0

…

7 位线

读/写控制电路

D0

… D7

(2) 重合法(双译码方式)

0 A4

0,00

…

0 A3

阵

A2

译

0码

31,0

…

A1

器 X 31

0 A0

… …

或低表示存储的是1或0。 T5和T6是两个门控管,读写操作时,两管需导通。

六管存储单元

保持

字驱动线处于低电位时,T5、T6 截止, 切断了两根位线与触发器之间的 联系。

六管存储单元

单译码方式

读出时: 字线接通 1)位线1和位线2上加高电平; 2)若存储元原存0,A点为低电

平,B点为高电平,位线2无电 流,读出0。

3)若存储元原存1,A点为高电 平,B点为低电平,位线2有电

流,读出1。

静态 RAM 基本电路的 读 操作(双译码方式)

位线A1

A T1 ~ T4 B

位线2

T5

行地址选择

T6

行选

T5、T6 开

列选

T7、T8 开

T7

T8

读选择有效

列地址选择 写放大器

写放大器

VA

T6

读放

读放

DOUT

T8 DOUT

DIN

1.主存与CPU的连接

是由总线支持的; 总线包括数据总线、地址总线和控制总线; CPU通过使用MAR(存储器地址寄存器)和MDR(存储

计算机组成原理与汇编实验报告

计算机组成原理与汇编实验报告姓名:学号:学院:信息科学与工程学院班级:实验1 存储器实验实验目的⏹掌握静态存储随机存储器RAM的工作特性⏹掌握静态存储随机存储器RAM的读写方法实验设备74LS273(一片),静态存储器MEMORY 6116(一片),与门(一片),与非门(一片),单脉冲(一片),开关若干,灯泡若干实验原理在微机系统中,常用的静态RAM 有6116、6264、62256 等。

在本实验中使用的是6116。

6116 为2K╳8 位的静态RAM,其逻辑图3.1如下:图3.1 6116逻辑图其中A0~10 为11 根地址线,I/O0~7 为8 根数据线,CS 为片选端,OE 为数据输出选通端,WR 为写信号端。

其工作方式见下表3-1:表3-1工作方式表实验所用的半导体静态存储器电路原理如图3.2 所示,实验中的静态存储器一片6116(2K×8)构成,其数据线接至数据总线,地址线由地址锁存器(74LS273)给出。

地址灯AD0—AD7 与地址线相连,显示地址线内容。

数据开关经一三态门(74LS245)连至数据总线,分时给出地址和数据。

图3.2 存储器实验原理图因地址寄存器为8 位,接入6116 的地址A7—A0,而高三位A8—A10 接地,所以其实际容量为256 字节。

6116 有三个控制线:CE(片选线)、OE(读线)、WE(写线)。

当片选有效(CE=0)时,OE=0时进行读操作,WE=0时进行写操作。

本实验中将OE 常接地,在此情况下,当CE=0、WE=0 时进行读操作,CE=0、WE=1 时进行写操作,其写时间与T3 脉冲宽度一致。

控制信号SW-B 为低电平有效,控制信号LDAR 为高电平有效。

实验步骤1. 选择实验设备:根据实验原理图,将所需要的组件从组件列表中拖到实验设计流程栏中。

搭建实验流程:将已选择的组件进行连线(鼠标从一个引脚的端点拖动到另一组件的引脚端,即完成连线)。

计算机组成原理存储器(1)(1)

计算机组成原理存储器(1)(1)1.存储器⼀、单选题(题数 54,共7 )1在下述存储器中,允许随机访问的存储器是()。

(1.2分)A、磁带 B 、磁盘 C 、磁⿎ D 、半导体存储器正确答案 D2若存储周期250ns,每次读出16位,则该存储器的数据传送率为()。

(1.2分)A、4×10^6字节/秒B、4M字节/秒C、8×10^6字节/秒D、8M字节/秒正确答案 C3下列有关RAM和ROM得叙述中正确的是()。

IRAM是易失性存储器,ROM是⾮易失性存储器IIRAM和ROM都是采⽤随机存取⽅式进⾏信息访问IIIRAM和ROM都可⽤做CacheIVRAM和ROM都需要进⾏刷新(1.2分)A、仅I和IIB、仅I和IIIC、仅I,II,IIID、仅II,III,IV正确答案 A4静态RAM利⽤()。

(1.2分)A、电容存储信息B、触发器存储信息C、门电路存储信息D、读电流存储信息正确答案 B5关于计算机中存储容量单位的叙述,其中错误的是()。

(1.2分)A、最⼩的计量单位为位(bit),表⽰⼀位“0”或“1”B、最基本的计量单位是字节(Byte),⼀个字节等于8bC、⼀台计算机的编址单位、指令字长和数据字长都⼀样,且是字节的整数倍D、主存容量为1KB,其含义是主存中能存放1024个字节的⼆进制信息正确答案 C6若CPU的地址线为16根,则能够直接访问的存储区最⼤容量为()。

(1.2分)A、1MB、640KC、64KD、384K正确答案 C7由2K×4的芯⽚组成容量为4KB的存储器需要()⽚这样的存储芯⽚。

(1.2分)A、2B、4C、8D、16正确答案 B8下⾯什么存储器是⽬前已被淘汰的存储器。

(1.2分)A、半导体存储器B、磁表⾯存储器C、磁芯存储器D、光盘存储器正确答案 C9下列⼏种存储器中,()是易失性存储器。

(1.2分)A、cacheB、EPROMC、FlashMemoryD 、 C D-ROM正确答案 A10下⾯关于半导体存储器组织叙述中,错误的是什么。

计算机组成原理 存储器课件举例讲解

刷新按行进行,用于提供对所要刷新的行进行计数;

仲裁电路

对同时产生的来自CPU的访问存储器的请求和来自刷新定

时器的刷新请求的优先权进行裁定;

定时发生器

提供行地址选通/RAS、列地址选通/CAS和写信号/WE。

2020/3/22

38

3.3.3 读/写周期 行、列地址分开传送

读时序

写时序

行地址 RAS 有效

硬盘 磁带

光盘存储器:用光介质(光学性质)构成的存储器; 光盘

按存取方式分

半导体

随机存储器:存取时间和存储单元的物理位置无关; 存储器

顺序存储器:存取时间和存储单元的物理位置有关; 磁带

半顺序存储器:存取时间部分地依赖于存储单元的物理位置;

磁盘存储器

2020/3/22

5

3.1.1 存储器分类(2/3)

一个写操作 中数据不允 许改变

32

正确的SRAM的写入时序图

2020/3/22

33

3.3 DRAM存储器

动态RAM(DRAM) 因为该存储器必须定时刷新,才能维持其中的信息不变;

DRAM的存储元 由MOS晶体管和电容组成的记忆电路; 电容上的电量来表现存储的信息; 充电—1,放电—0。 结构形式 四管存储元 单管存储元

2、内存包括cache和主存

2、虚存系统包括主存和辅存

在CPU看来,容量相当于辅存容量,速度相当于CACHE速度。

2020/3/22

9

3.1.2 存储器的分级结构(2/2)

存储器分级结构中应解决的问题: 当需从辅存中寻找指定内容调入主存时,如何准确定位? 依靠相应的辅助软硬件。 当CPU访问cache,而待访问内容不在cache中时,应如何 处理? 从主存向cache中调入相应内容。

计算机组成原理4第四章存储器PPT课件精选全文

4.2

11

4.2

请问: 主机存储容量为4GB,按字节寻址,其地址线 位数应为多少位?数据线位数多少位? 按字寻址(16位为一个字),则地址线和数据线 各是多少根呢?

12

数据在主存中的存放

设存储字长为64位(8个字节),即一个存 取周期最多能够从主存读或写64位数据。

读写的数据有4种不同长度:

字节 半字 单字 双字

34

3. 动态 RAM 和静态 RAM 的比较

主存

DRAM

SRAM

存储原理

电容

触发器

集成度

高

低

芯片引脚

少

多

功耗

小

大

价格

低

高

速度

慢

快

刷新

有

无

4.2

缓存

35

内容回顾: 半导体存储芯片的基本结构 4.2

…… ……

地

译

存

读

数

址

码

储

写

据

线

驱

矩

电

线

动

阵

路

片选线

读/写控制线

地址线(单向) 数据线(双向) 芯片容量

D0

…… D 7

22

(2) 重合法(1K*1位重合法存储器芯片)

0 A4

0,00

…

0,31

0 A3

X 地

X0

32×32

… …

0址

矩阵

A2

译

0码

31,0

…

31,31

A1

器 X 31

0 A0

Y0 Y 地址译码器 Y31 A 9 0A 8 0A 7 0A 6 0A 5 0

计算机组成原理9-存储器

ABC 0 0 00 0 0 11 0 1 02 0 1 13 1 0 04 1 0 15 1 1 06 1 1 17

ABC 0 0 00 001 010 0 1 13 100 1 0 11 1 1 02 111

30

奇偶校验码

• 奇偶校验码是主存采用的一种最简单的行之有效的方法。

1)构成法则:

1011 0001 1011 0001 1 1011 0001 0

//1的个数为奇数 //1的个数为偶数

校验码包含 有效信息和校验位

• 奇偶校验逻辑 主要采用异或门校验码的生成和检错。

32

奇偶校验码

校验位( 偶形成 ) ⊕

1:奇数个1 0:偶数个1

⊕

⊕

⊕⊕⊕⊕ D7 D6 D5 D4 D3 D2 D1 D0

37

海明校验

例:N=7,k=4 , r=3的海明码位数为:

位号 Pi占位

123456 7 P1 P2 A1 P3 A2 A3 A4

A1~A4 为有效信息, 海明码的每一位都被P1,P2,…,Pr中的一至若干位所校验。 规律:第i位由校验位位号之和等于i的那些校验位所校验。 如:第5位,被P1、P3校验,

• 部分译码方式 地址不唯一

A15 A14 A13 A12 A11 C A10 P U A9

A0

D4~D7 D0~D3

3/8

译码器

12

CPU和主存的连接

• 系统模式 1)最小系统模式 2)较大系统模式 3)专用存储总线模式 速度匹配与时序控制

CPU 操作和访存操作的时钟周期 时钟周期 总线周期:CPU通过系统总线对存储器的一次读 写操作。由数个时钟周期组成

A15 A14 A13 A12

主存储器设计举例

❖ 例题 已知: ① CPU的地址总线16根(A15—A0,A0为低位) ② 双向数据总线8根(D7—D0) ③ 控制总线中与主存有关的信号有MREQ(允许访

存,低电平有效),R/ W(高电平为读命令,低电 平为写命令) 要求:主存地址空间满足如下分配: ① 0—8191为系统程序区,由只读存储芯片组成. ② 8192—32767为用户程序区;最后(最大地 址)2K 地址空间为系统程序工作区. ③ 地址用十进制且按字节编址.

改错题:

1.用64K*32位的DRAM芯片组成一个2M*64位 的半导体主存储器,该主存的地址寄存器和

2数.码静寄态存存器储分器别(S是RA1M6位)是与属3于2位非。易失性存贮 器。

1.用256K*16位的EDRAM芯片组成一个内存条,若 要构建4M*16位的半导体主存储器。试求:

(1) 该主存的地址寄存器和数码寄存器各需要多少位? (2)该主存共需几个内存条? (3) 当每个内存条的地址线均采用双译码实现时,其需

3 .扩展型操作码意指: 指令字长度不变,但让操作

码的长度随

的减少而增加,因而是一种

指令优化技术。

4 .在操作数寻址方式中,若D表示形式地址时,相

对寻址方式的操作数有效地址为

;若采

用基址寻址方式 (其中基址寄存器为32位,形式

地址D为20位),则其操作数的最大存储空间是

存储单元。

5.条件转移、无条件转移、转子程序、返回主程序、 中断返回指令都属于 类指令,这类指令在指 令格式中所表示的地址是 的地址。

需的实际刷新时间是多少?

设计题:

1.① 试设计出字长为4位的X±Y的补码加法器 逻辑图(含溢出判断电路).

② 写出三种判溢的逻辑表达式

计算机组成原理-第3章_存储系统

存储周期 RW 刷新1 RW 刷新2 …

500ns 500ns

刷新间隔2ms

用在低速系统中

各刷新周期分散安排 在存取周期中。

… RW 128 RW

例如上图所示的DRAM有128行,如果刷新周期为 2ms,则每一行必须每隔2ms÷128=62.5us进行一次。

5、存储器控制电路

DRAM刷新需要硬件电路支持,它们集成在一个芯片 上,形成DRAM控制器,是CPU和DRAM间的接口电路。

写周期:实现写操作,要求CS和WE同时有效,有效期间地址 和数据信号不能变化;为了保证CS和WE变为无效前能把数据 可靠的写入,数据必须提前一段时间在数据总线上稳定存在; 而在WE变为高电平后再经过一段时间地址信号才允许改变。

*** DRAM存储器

1、DRAM存储元的记忆原理

SRAM存储器的存储元是一个 触发器,它具有两个稳定的状态。

外存储器:简称“外存”,大容量辅助存储器;磁表面存储

器或光盘存储器;存放需联机保存但暂时不需要的程序和数 据。容量从几十MB到几百GB,甚至更大。存取速度为若干

ms。

其他功能的存储器:如微程序控制器的控存、在显示和印刷 输出设备中的字库和数据缓冲存储器。

*** 主存储器的技术指标

主要性能指标:存储容量、存取时间、存储周期和存储器带宽。

地址信息到达时,使T5、T6、T7、T8导通,存储 元的信息被送到I/O与I/O线上, I/O与I/O线接上一个 差动读出放大器,从其电流方向,可以得出所存信息 是“1”或“0”。也可I/O或I/O一端接到外部,看其 有无电流通过,得出所存信息。

扩充:存储芯片规格的表示

在很多内存产品介绍文档中,都会用M×W的方式来表示芯 片的容量。