数字IC设计工具介绍

数字IC设计——整理

数字集成电路设计整理一、概念1. ASIC——Application Specific Integrated Circuit专用集成电路ASIC在批量生产时与通用集成电路(IC)相比具有体积更小、功耗更低、可靠性提高、性能提高、保密性增强、成本降低等优点。

ASIC分为全定制和半定制。

全定制设计需要设计者完成所有电路的设计,半定制使用库里的标准逻辑单元(Standard Cell),设计时可以从标准逻辑单元库中选择SSI(门电路)、MSI(如加法器、比较器等)、数据通路(如ALU、存储器、总线等)、存储器甚至系统级模块(如乘法器、微控制器等)和IP核,这些逻辑单元已经布局完毕,而且设计得较为可靠,设计者可以较方便地完成系统设计。

全定制能够比半定制的ASIC芯片运行速度更快。

2.IP——Intellectual Property知识产权3.数字后端指将前端设计产生的门级网表通过EDA设计工具进行布局布线和进行物理验证并最终产生供制造用的GDSII数据的过程。

其主要工作职责有:芯片物理结构分析、逻辑分析、建立后端设计流程、版图布局布线、版图编辑、版图物理验证、联络代工厂并提交生产数据。

作为连接设计与制造的桥梁,合格的版图设计人员既要懂得IC 设计、版图设计方面的专业知识,还要熟悉制程厂的工作流程、制程原理等相关知识。

4.Standard Cell——标准单元库5.RTL——寄存器传输级描述通过一个寄存器到另一个寄存器的逻辑变换和传输来描述设计。

逻辑值被存储在寄存器中,通过一些组合逻辑对其要求值,随后将结果存储于下一个寄存器。

RTL的功能类似于软件与硬件之间的桥梁。

是与工艺无关的网表的文本结构描述。

6.布局(Place)布线(Route)布图规划floorplan比布局更重要。

规划包括指令,macro的放置,电源线的设计power plan。

floorplan一旦确定,芯片的面积就定下来了,也与整个设计的timming和布通率有很大关系。

Synopsys系列工具简介

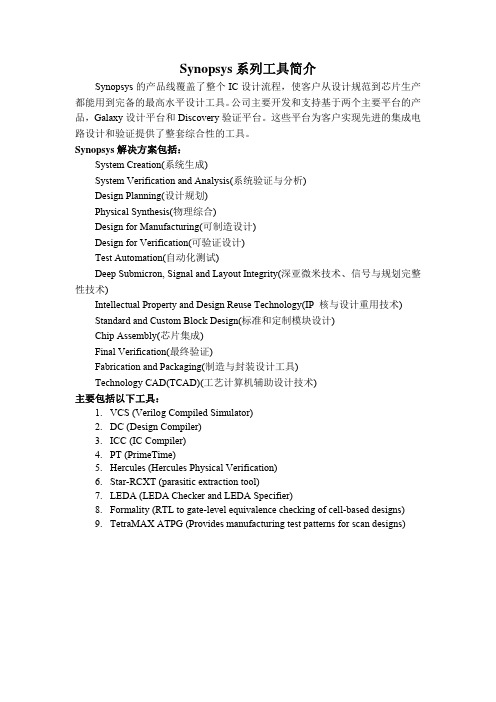

Synopsys系列工具简介Synopsys的产品线覆盖了整个IC设计流程,使客户从设计规范到芯片生产都能用到完备的最高水平设计工具。

公司主要开发和支持基于两个主要平台的产品,Galaxy设计平台和Discovery验证平台。

这些平台为客户实现先进的集成电路设计和验证提供了整套综合性的工具。

Synopsys解决方案包括:System Creation(系统生成)System Verification and Analysis(系统验证与分析)Design Planning(设计规划)Physical Synthesis(物理综合)Design for Manufacturing(可制造设计)Design for Verification(可验证设计)Test Automation(自动化测试)Deep Submicron, Signal and Layout Integrity(深亚微米技术、信号与规划完整性技术)Intellectual Property and Design Reuse Technology(IP 核与设计重用技术)Standard and Custom Block Design(标准和定制模块设计)Chip Assembly(芯片集成)Final Verification(最终验证)Fabrication and Packaging(制造与封装设计工具)Technology CAD(TCAD)(工艺计算机辅助设计技术)主要包括以下工具:1.VCS (Verilog Compiled Simulator)2.DC (Design Compiler)3.ICC (IC Compiler)4.PT (PrimeTime)5.Hercules (Hercules Physical Verification)6.Star-RCXT (parasitic extraction tool)7.LEDA (LEDA Checker and LEDA Specifier)8.Formality (RTL to gate-level equivalence checking of cell-based designs)9.TetraMAX ATPG (Provides manufacturing test patterns for scan designs)1.VCS (Verilog Compiled Simulator)VCS是编译型Verilog模拟器,它完全支持OVI标准的Verilog HDL语言、PLI和SDF。

Allegro中L、XL和GXL介绍

Allegro L, XL和GXL会在2006年7月上市。对Allegro平台的最新版本更多细节感兴趣的人士可以注册参加一个就近的Cadence技术大会,或者联系Cadence在当地的销售经理。

“在板级分配网络上有抖动的定制激励,为网络分配不同的时钟速度,这些功能大大简化了各种类型接口的批量模式分析。” Celestica工程经理Kai Keskinen说道,“在板级设置好以后,使用源同步信号的接口的全部模拟可显著加速。

“设计师日益希望整合和达到新的高速接口如PCI Express 和 DDR2的多重需求。我们的客户在寻找为他们特定水平的设计需求量身定做的技术,”Cadence负责Allegro与Virtuoso设计平台营销的公司副总裁Charlie Giorgetti说,“Allegro平台这次最新的发布和分割,是另一个显示Cadence继续领先于为硅封装电路板协同设计市场分支提供深思熟虑的设计解决方案的例子。

Allegro Design Workbench XL是全新产品,可为Allegro 设计库提供组件信息和库管理,可使库修订控制自动化,并向全世界的公司设计中心提供发布包括一致性信息如RoHS的已知库的方法。这可使设计周期和组件搜索缩减达50%。

数字ic设计流程与模拟IC

数字ic设计流程与模拟IC1. 首先是使用HDL语言进行电路描述,写出可综合的代码。

然后用仿真工具作前仿真,对理想状况下的功能进行验证。

这一步可以使用Vhdl或Verilog作为工作语言,EDA工具方面就我所知可以用Synopsys的VSS(for Vhdl)、VCS(for Verilog)Cadence的工具也就是著名的Verilog-XL和NC Verilog2.前仿真通过以后,可以把代码拿去综合,把语言描述转化成电路网表,并进行逻辑和时序电路的优化。

在这一步通过综合器可以引入门延时,关键要看使用了什么工艺的库这一步的输出文件可以有多种格式,常用的有EDIF格式。

综合工具Synopsys的Design Compiler,Cadence的Ambit3,综合后的输出文件,可以拿去做layout,将电路fit到可编程的片子里或者布到硅片上这要看你是做单元库的还是全定制的。

全定制的话,专门有版图工程师帮你画版图,Cadence的工具是layout editor单元库的话,下面一步就是自动布局布线,auto place & route,简称apr cadence的工具是Silicon Ensembler,Avanti的是Apollo layout出来以后就要进行extract,只知道用Avanti的Star_rcxt,然后做后仿真,如果后仿真不通过的话,只能iteration,就是回过头去改。

4,接下来就是做DRC,ERC,LVS了,如果没有什么问题的话,就tape out GDSII格式的文件,送制版厂做掩膜板,制作完毕上流水线流片,然后就看是不是work 了做DRC,ERC,LVSAvanti的是Hercules,Venus,其它公司的你们补充好了btw:后仿真之前的输出文件忘记说了,应该是带有完整的延时信息的设计文件如:*.VHO,*.sdfRTL->SIM->DC->SIM-->PT-->DC---ASTRO--->PT----DRC,LVS--->TAPE OUT1。

数字IC设计

数字IC设计数字IC设计是指采用数字电路元件和技术,在符合设定功能要求的基础上,实现指定功能的集成电路设计。

数字IC设计是集成电路设计的一个重要分支,该设计应用面广,广泛应用于通信、计算机、工业、家用电器等领域中。

本文将从数字IC设计的概念、发展历程、设计方法、常用的设计工具等方面进行探讨。

一、数字IC设计的概念数字IC设计是指使用数字电路元件及技术,在设定的功能要求的前提下,实现指定功能的集成电路的设计。

数字IC设计是由组合逻辑、时序逻辑、存储器等数字电路元件构成的。

数字IC设计的核心是实现数字电路设计的复杂性,在各种复杂的应用领域中,进行数字电路系统的快速设计和优化。

数字IC设计的关键是实现函数逻辑关系的描述和形式化,使用数字语言,对电路系统的逻辑关系进行严格的描述和方便化的实现。

数字IC设计具有复杂性、可扩展性、可靠性、精度高、功耗低等特点。

二、数字IC设计的发展历程数字IC设计发展历程从20世纪60年代开始,到今天数十年来经历了从基础到高级的一系列发展过程。

其中有一些重要的里程碑事件,大大促进了数字IC设计的发展。

早期的数字IC设计是使用硬件直接链接模拟电路实现,其设计过程比较简单,如模拟计算器。

1971年,美国Texas Instruments公司推出了世界上第一款集成电路计算器TMS0100,该计算器采用了数字IC设计技术进行实现。

在此之后,数字IC设计开始迎来了快速的发展,人们越来越依赖集成电路和数字IC设计技术带来的方便和高效性。

20世纪80年代,数字IC的设计和制造技术日趋成熟,数字IC的速度和芯片的集成度愈加高。

随着数字IC设计技术的不断提高和发展,出现了大规模集成(LSI),超大规模集成(VLSI)和超高规模集成(UHVSI)等技术,这一系列的技术标志着数字IC设计的进一步发展。

21世纪以来,数字IC设计技术与微电子技术的迅速发展,尤其是3D器件、功能扩张技术和生物微型芯片等的出现,有力地推动了数字IC设计技术向更为高级、复杂和智能方向发展,以应对日益复杂的计算和控制技术需求。

最常用的几种EDA软件

最常用的几种EDA软件EDA技术是在电子CAD技术基础上发展起来的计算机软件系统,是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。

利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程在计算机上自动处理完成。

现在对EDA的概念或范畴用得很宽。

包括在机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有EDA的应用。

目前EDA 技术已在各大公司、企事业单位和科研教学部门广泛使用。

例如在飞机制造过程中,从设计、性能测试及特性分析直到飞行模拟,都可能涉及到EDA技术。

本文所指的EDA技术,主要针对电子电路设计、PCB设计和IC设计。

EDA 设计可分为系统级、电路级和物理实现级。

EDA常用软件EDA工具层出不穷,目前进入我国并具有广泛影响的EDA软件有:EWB、PSPICE、OrCAD、PCAD、Protel、ViewLogic、Mentor、Graphics、Synopsys、LSIlogic、Cadence、MicroSim等等。

这些工具都有较强的功能,一般可用于几个方面,例如很多软件都可以进行电路设计与仿真,同时以可以进行PCB自动布局布线,可输出多种网表文件与第三方软件接口。

下面按主要功能或主要应用场合,分为电路设计与仿真工具、PCB设计软件、IC 设计软件、PLD设计工具及其它EDA软件,进行简单介绍。

1、电子电路设计与仿真工具电子电路设计与仿真工具包括SPICE/PSPICE;EWB;Matlab;SystemView;MMICAD 等。

下面简单介绍前三个软件。

(1)SPICE(Simulation Program with Integrated Circuit Emphasis)是由美国加州大学推出的电路分析仿真软件,是20世纪80年代世界上应用最广的电路设计软件,1998年被定为美国国家标准。

数字ic设计知识点

数字ic设计知识点数字 IC 设计知识点数字 IC 设计是现代电子系统设计中的重要领域之一,它涉及到数字电路设计、逻辑设计、时序设计等多个方面的知识点。

本文将为您介绍一些基本的数字 IC 设计知识点,希望对您在该领域的学习和实践有所帮助。

I. 逻辑门逻辑门是数字 IC 设计中最基本的组成单元,它能够实现布尔逻辑运算。

常见的逻辑门包括与门、或门、非门、与非门、或非门、异或门等。

逻辑门的功能可以通过真值表或逻辑表达式来描述。

II. 布尔代数布尔代数是数字 IC 设计中描述逻辑运算的基本数学工具。

它包括布尔运算、布尔函数和布尔表达式等概念。

通过使用布尔代数,可以简化逻辑电路的设计和分析过程。

III. 组合逻辑电路组合逻辑电路是由逻辑门和连线连接而成的电路。

它的输出仅取决于当前的输入状态,与过去的输入状态无关。

组合逻辑电路可以实现各种逻辑功能,如加法器、减法器、多路选择器等。

IV. 时序逻辑电路时序逻辑电路是由逻辑门、存储元件和时钟信号组成的电路。

它的输出取决于当前的输入状态以及过去的输入状态。

时序逻辑电路可以实现各种时序功能,如触发器、计数器、状态机等。

V. 数字系统数字系统是由数字 IC 设计构成的系统,它可以完成数字信号的处理和运算。

常见的数字系统包括二进制系统、八进制系统、十进制系统和十六进制系统等。

VI. IC 设计流程IC 设计流程是指从需求分析到芯片生产的全过程,它包括需求分析、系统设计、电路设计、物理设计、验证仿真和芯片生产等阶段。

严格的 IC 设计流程可以确保芯片的功能和性能符合设计要求。

VII. 数字 IC 设计工具数字 IC 设计工具是用于辅助数字 IC 设计的软件工具,它包括逻辑设计工具、布局设计工具、验证仿真工具等。

常用的数字 IC 设计工具有EDA工具、VHDL/Verilog语言和IC设计软件等。

VIII. 数字 IC 测试数字IC 测试是指对已制造的芯片进行功能验证和故障检测的过程。

CADENCE全定制IC设计流程

CADENCE全定制IC设计流程CADENCE是一种广泛应用于集成电路(IC)设计的软件工具。

它提供了完整的设计流程和工具,用于设计、验证和制造IC芯片。

在基于CADENCE的全定制IC设计流程中,在IC设计的每个阶段都使用到了CADENCE工具套件,包括电路和物理设计工具、模拟和数字仿真工具、布图工具以及物理验证工具等。

下面是使用CADENCE进行全定制IC设计的一般流程:1.设计需求分析:根据所需的功能和性能需求,进行设计需求分析。

这包括确定电路拓扑结构、电路规范和性能指标等。

2. 电路设计:使用CADENCE中的Schematic设计工具,绘制电路原理图。

根据设计需求,选择合适的电子元件并进行电路布线。

使用CADENCE的仿真工具,验证电路的功能和性能。

3.物理设计:将电路原理图转换为布局图。

使用CADENCE的布局工具,在设计规范的限制下进行器件布局和连线布线。

这包括选择合适的器件大小和排列方式,以优化电路性能和功耗。

4.物理验证:使用CADENCE的物理验证工具,对电路布局进行验证。

这包括电路的电性能分析、功耗分析、时序等效验证以及电磁兼容性分析等。

根据验证结果进行布局优化和改进。

5.交互测试:将设计与其他模块和子系统进行集成测试。

使用CADENCE的模拟工具和数字仿真工具,对整个系统进行功能验证和性能评估。

7.物理制造:通过CADENCE的布局生成工具,生成用于物理制造的设计数据库文件。

这包括物理制造规则检查、填充、光刻掩膜生成等。

8.物理验证:使用CADENCE的物理验证工具,对物理制造的设计进行验证。

这包括工艺模拟、功耗分析、封装和信号完整性分析等。

9.物理制造:将设计数据库文件发送给制造厂商进行实际制造。

这包括掩膜制造、芯片加工、封装和测试等。

10.性能评估:对实际制造的芯片进行性能评估和测试。

使用CADENCE的集成测试工具,进行功能测试、速度测试和功耗测试等。

11.系统集成:将IC芯片集成到目标系统中,并进行系统级测试和验证。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

COMPOSER - CADENCE 逻辑图输入

这个工具主要针对中小规模的ASIC以及MCU电路的逻辑设计,大的东西可能需要综合了。

虽然现在电路越设计越大,有人言必称SYNOPSYS,但只要仔细到市场上端详一下,其实相当大部分真正火暴卖钱的东西还是用CADENCE的COMPOSER加VIRTUOSO加VERILOG—XL加DRACULA流程做的。

原因很简单,客户可不买你什么流程的帐,什么便宜性能又好就买什么。

备用PC上的工具:WORKVIEW OFFICE

DC - SYNOPSYS 逻辑综合

这个不用说了,最经典的。

但老实说在我们现在的设计流程里用得还不多,最关键问题还是一个市场切入问题。

备用工作站上的工具:AMBIT,这个工具其实很不错,它和SE都是CADENCE出的,联合起来用的优势就很明显了。

PC上用的备用工具可以选NT版的SYNOPSYS,SYNPILIFY也不错,但主要是用做FPGA综合的。

其实最终你拿到的库有时最能说明问题,它不支持某工具,转换?急吧。

VIRTUOSO - CADENCE 版图设计

这个大家比较熟了,但个人还是喜欢用PC上的TANNER。

原因是层与层之间的覆盖关系用调色的模式显示出来比直接覆盖显示就是舒服。

可惜人家老大,国产的《熊猫》也学了这个模式。

倒是以前有个COMPASS,比较好用,可惜现在不知哪去了。

SE - CADENCE 自动布局布线

有了它,很多手工版图的活儿就可以不用做的,实在是一大进步。

可惜残酷市场上如果规模不大的东西人家手画的东西比你自动布的小40%,麻烦就大了。

APOLLO用的人还不是很多吧。

PC上的TANNER 据说也能做,针对线宽比较粗,规模不太大的设计。

VERILOG—XL - CADENCE 逻辑仿真

VERILOG就是CADENCE的发明,我们的版本比较老,现在该工具是不是停止开发了?CADENCE 新推都叫NC-VERILOG。

SYNOPSYS的VCS是不是比NC强,反正两公司喊的挺凶,哪位对这个两个东西都比较了解,不妨对比一下。

PC上的Model Sim也很不错。

我一直觉得仿真是数字逻辑设计的核心,DEGUG 靠脑子和手推是不够用的。

可惜往往有时候还不能过分依赖仿真结果,因为一些因素还是不能完全包罗进去。

如果哪天真的仿真完芯片就必定OK了,做芯片的乐趣也没了。

DRACULA - CADENCE LVS、DRC、ERC、LPE

虽然比较老,已经成了CADENCE搭售的产品,但是经典了。

STAR—SIM - SYNOPSYS(原A VANT!)后仿真

如果你对小规模的电路不放心(尤其是自建库的设计),用这个做一次FULL-CHIP的后仿真,问题就不大了。

还有一个是查电路的故障,一个芯片所有逻辑设计都对的,东西就出不来,可以针对性的仿真内部的关键信号。

不看过就不知道,其实内部信号的传输远不如你在数字仿真时漂亮。

以上都是传统工具,还有好多新出的工具,因为只是停留在概念基础上,不敢评论了。

以下是几个硬件工具:

示波器、信号发生器、逻辑分析仪:

尤其是逻辑分析仪,查找硬件故障,甚至分析简单的通讯协议,好东西。

就是聚焦离子束,用来修改芯片逻辑实在太爽了。

FIB的高手还可以帮你挖开二次铝修改底下的一次铝。

这个你可以扎到你没有邦定的PAD上测试,配合使用FIB就更好了,可以测试电路内部几乎任意点的信号值。

电镜扫描仪:

如果你的电路有缺陷(比如功耗大),它能帮你查出一部分的问题,但铝短路情况查不出。

我一直对怎样查出连铝这样的问题比较感兴趣,总之为了得到这样一个诊断结果我跑了好几个地方,花了不少钱和几个月时间。

芯片测试仪:

这个一般倒不必非摸透,大概了解点对设计有好处。

(1)代码输入:

语言输入:Summit VisualHDL Summit

Renior

Mentor

图形输入:composer Candence

Viewlogic

Viewdraw

(2)电路仿真:数字电路仿真

Verilog:

VCS

Synopsys

Verilog—XL

Candence

modle-sim

Mentor

Vhdl:

VSS

Synopsys

NC—vhdl

Candence

modle-sim

Mentor

模拟电路仿真

Hsipce

Synopsys

Spectre Simulator ,Pspice Cadence

SmartSpice

Silvaco

(3)逻辑综合:

DC Expert Synopsys

BuilderGates

Cadence

Blaster RTL Magama

Synplify PRO

Synplify

其实对于一般的IC设计而言,使用哪家EDA公司的工具都相差不大,我认为关键是建立design team的IC设计全流程平台,从前端到后端的工具都要具备而且必须走通,例如:可以使用Synoposys的EDA工具在Solaris系统下建立IC设计的前后端设计平台,也可使用Mentor公司的windows平台工具建立这个平台,还可以混合使用各个EDA公司的设计工具,例如:在PC机上使用ModelSim进行功仿,在Solaris工作站上使用DC做综合,用Candence的NC做后仿、然后再使用Candence的SE或SoC Encounter或Virtuoso 做后端设计,我们的design center就是混用各个EDA公司工具,这样做是有依据的:一般设计人员都习惯在自己的PC上编码、功仿以及调试,而windows平台的仿真工具当推Mentor的ModelSim最优秀,至于逻辑综合选用DC就不用解释了,而后端选用Candence的工具是因为Candence在APR和全定制版图设计与验证很有优势,工具成熟,因此Mentor+Synoposys+Candence的黄金搭档非常不错!这个平台在我们design center已使用了多年,实践证明还是很得力的!

总之选用哪家EDA公司的工具并不重要,关键是要建立一个完整的平台,只有在平台上工作才能事半功倍!

(注:本资料素材和资料部分来自网络,仅供参考。

请预览后才下载,期待你的好评与关注!)。