西安交通大学组成专题实验报告

多普勒效应综合实验报告西安交通大学

多普勒效应综合实验报告西安交通大学【实验目的】

1、测量超声接收器运动速度与接收频率之间的关系,验证多普勒效应,并由f一V关系直线的斜率求声速。

2、利用多普勒效应测量物体运动过程中多个时间点的速度,查看V一t关系曲线,或调阅有关测量数据,即可得出物体在运动过程中的速度变化情况。

【实验原理】

1、超声的多普勒效应

根据声波的多普勒效应公式,当声源与接收器之间有相对运动时,接收器接收到的频率f为:f=f0/

式中f0为声源发射频率,u为声速,V1为接收器运动速率,α1为声源与接收器连线与接收器运动方向之间的夹角,V2为声源运动速率,α2为声源与接收器连线与声源运动方向之间的夹角。

2、超声的红外调制与接收

早期产品中,接收器接收的超声信号由导线接入实验仪进行处理。

由于超声接收器安装在运动体上,导线的存在对运动状态有一定影响,导线的折断也给使用带来麻烦。

西 安 交 通 大 学 实 验 报 告 生物信息学

课程生物信息学实验名称核酸和蛋白质序列数据的使用系别实验日期:专业班级组别交报告日期:姓名学号报告退发:(订正、重做)同组人无教师审批签字:实验目的:了解常用的序列数据库,掌握基本的序列数据信息的查询方法。

实验步骤:在序列数据库中查找某条基因序列(insulin人的),通过相关一系列数据库的搜索、比对与结果解释实验结果:1.该基因的功能是?DNA结合、RNA结合、雄激素受体结合、酶结合、蛋白结合、转录激活活性、转录调控区的DNA结合、微管蛋白结合、泛素蛋白与连接酶结合、泛素蛋白连接酶的活性、提高泛素蛋白连接酶的活性、锌离子结合3. 该蛋白质有没有保守的功能结构域该蛋白质有保守的功能结构域。

分别为cd00027(Location:1763 –1842 Blast Score: 107)cd00162(Location:23 –68 Blast Score: 134)pfam04873(Location:655 –978 Blast Score: 1301)pfam12820(Location:344 –507 Blast Score: 809)pfam13923(Location:20 –65 Blast Score: 135)4. 该蛋白质的功能是怎样的?①E3泛素蛋白连接酶,专门介导L YS-6'-联泛素链的形成,并通过促胞对DNA损伤的反应,在DNA修复中起着核心的作用;目前还不清楚是否也介导其他类型的泛素链形成。

E3泛素蛋白连接酶的活性是其抑癌能必需的。

②BARD1- BRCA1异源二聚体协调各种不同的细胞通路,如DNA损伤修复,泛素化和转录调控,以维持基因组稳定性。

③调节中心体微核。

④从G2到有丝分裂的正常细胞周期进程所必需的。

⑤参与转录调控在DNA损伤反应中的P21。

⑥为FANCD2靶向DNA损伤位点所需。

⑦可以用作转录调控因子。

⑧绑定到ACACA 和防止其去磷酸化,抑制脂质合成。

西安交通大学电子专题实验实验报告

一:实验目的和要求

(1)了解完整的PCB板设计工序及方法;

(2)掌握制作元件原理图库、封装库的方法;

(3)掌握PCB板设计方法及其后处理;

(4)学习并掌握Protel DXP软件平台。

二:实验用仪器和软件环境

(1)微机(最低配置: Pentium 4 CPU, 128M内存);

(2)Protel DXP 2004软件;

(3)Windows XP环境

三:实验设计题目及实现的功能

本实验要求在Protel DXP软件平台上设计AVR单片机开发板电路的PCB板,根据学号分配任务,我要画的是RST、OSC、Power 、JTAG、LED、红外的电路图及对应的PCB板。

Protel DXP允许你从原理图直接运行一个大型电路仿真的阵列,通过仿真,可以显示它的波形。

四:实验步骤及结果

(1)创建一个新项目

(2)创建一个新的原理图图纸

电路图

显示器元件图

(3)设置项目选项

(4)创建一个新的PCB文件。

KFVK

西安交通大学实验报告课程___程序设计_____________实验名称_______________第页共页系别_口硕01________________________________ 实验日期年月日专业班级________________组别_____________ 实验报告日期年月日姓名__王小明______________学号__10209019__________ 报告退发 ( 订正、重做 )同组人_________________________________ 教师审批签字实验名称一.题目二.环境(windows XP)三.实验步骤(算法分析)If TextBox1.Text <> "" ThenlistBoxCourse.Items.Insert(listBoxCourse.SelectedIndex, TextBox1.Text)End IfIf listBoxCourse.SelectedIndex >= 0 ThenlistBoxCourse.Items.RemoveAt(listBoxCourse.SelectedIndex) End IfListBoxMajor.Items.Clear()Select Case ComboBoxMajor.SelectedIndexCase 0ListBoxMajor.Items.Add("口腔医学")Case 1ListBoxMajor.Items.Add("临床医学") Case 2ListBoxMajor.Items.Add("机械")Case 3ListBoxMajor.Items.Add("电气")Case 4ListBoxMajor.Items.Add("能动")Case 5ListBoxMajor.Items.Add("电信")Case 6ListBoxMajor.Items.Add("经济")Case 7ListBoxMajor.Items.Add("公馆")Case 8ListBoxMajor.Items.Add("法医")End SelectIf ComboBoxMajor.SelectedIndex >= 0 ThenListBoxMajor.Items.Add(ComboBoxMajor.SelectedIndex)ComboBoxMajor.Items.RemoveAt(ComboBoxMajor.SelectedIndex) End If3. Dim intsum, i As Integerintsum = 1i = 3While i <= 99intsum = intsum + ii = i + 2End WhileTextBox1.Text = "1+3+5+...+99=" + intsum.ToStringDim a, n, t, Sum As Integera = TextBox1.Textn = TextBox2.Textt = 1Sum = 0While t < nSum = Sum + aa = (1 ^ (t)) * a * 10 + 5t = t + 1End WhileTextBox3.Text = "5+55+555+5555+55555+555555=" + Sum.ToString四.实验数据、结果(代码、运行结果屏幕截图)五.总结。

西安交通大学计算机组成原理实验报告

西安交通大学计算机组成原理实验报告姓名:***班级:物联网**学号:实验一存储器的访问与实现一、实验目的1、理解计算机主存储器的分类及作用;2、掌握ROM、RAM的读写方法。

二、实验原理存储器按存取方式分,可分为随机存储器和顺序存储器。

如果存储器中的任何存储单元的内容都可随机存取,称为随机存储器,计算机中的主存储器都是随机存储器。

如果存储器只能按某种顺序存取,则称为顺序存储器,磁带是顺序存储器,磁盘是半顺序存储器,它们的特点是存储容量大,存取速度慢,一般作为外部存储器使用。

如果按存储器的读写功能分,有些存储器的内容是固定不变的,即只能读出不能写入,这种存储器称为只读存储器(ROM);既能读出又能写入的存储器,称为随机读写存储器(RAM)。

实际上真正的ROM基本上不用了,用的是光可擦除可编程的ROM(EPROM)和电可擦除可编程的ROM(EEPROM)。

EEPROM用的越来越多,有取代EPROM之势,比如容量很大的闪存(FLASH)现在用的就很广泛,常说的U盘就是用FLASH做的。

按信息的可保存性分,存储器可分为非永久性记忆存储器和永久性记忆存储器。

ROM、EPROM、EEPROM都是永久记忆存储器,它们断电后存储内容可保存。

RAM则是非永久性记忆存储器,断电后存储器中存储的内容丢失。

随机读写存储器类型随机存储器按其元件的类型来分,有双极存储器和MOS存储器两类。

在存取速度和价格两方面,双极存储器比MOS存储器高,故双极存储器主要用于高速的小容量存储体系。

在MOS存储器中,根据存储信息机构的原理不同,又分为静态随机存储器(SRAM)和动态随机存储器(DRAM)。

静态随机存储器采用双稳态触发器来保存信息,只要不断电,信息就不会丢失;动态随机存储器利用记忆电容来保存信息,使用时只有不断地给电容充电才能使信息保持。

静态随机存储器的集成度较低,功耗也较大;动态随机存储器的集成度较高,功耗低。

现在计算机中,内存容量较大,常由动态随机存储器构成。

数学实验报告

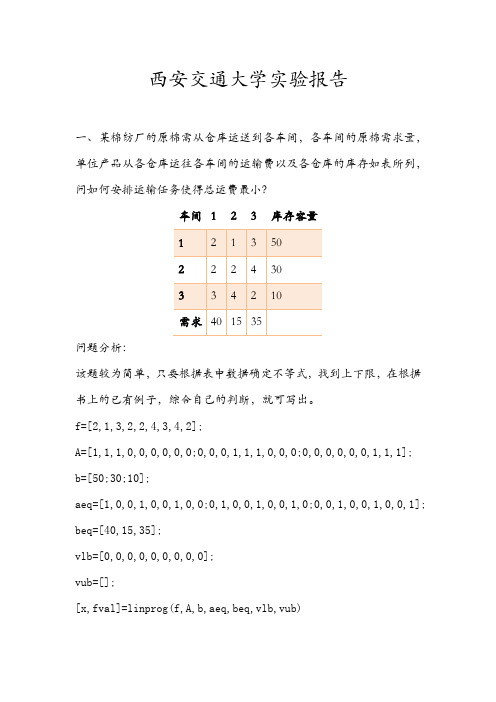

西安交通大学实验报告一、某棉纺厂的原棉需从仓库运送到各车间,各车间的原棉需求量,单位产品从各仓库运往各车间的运输费以及各仓库的库存如表所列,问如何安排运输任务使得总运费最小?问题分析:该题较为简单,只要根据表中数据确定不等式,找到上下限,在根据书上的已有例子,综合自己的判断,就可写出。

f=[2,1,3,2,2,4,3,4,2];A=[1,1,1,0,0,0,0,0,0;0,0,0,1,1,1,0,0,0;0,0,0,0,0,0,1,1,1];b=[50;30;10];aeq=[1,0,0,1,0,0,1,0,0;0,1,0,0,1,0,0,1,0;0,0,1,0,0,1,0,0,1]; beq=[40,15,35];vlb=[0,0,0,0,0,0,0,0,0];vub=[];[x,fval]=linprog(f,A,b,aeq,beq,vlb,vub)结果分析:由运行结果可知,第一车间由1,2仓库分别运进10,20单位的原棉,第二车间由1仓库运进15单位的原棉,第三车间由1,3仓库分别运进25,10单位的原棉,即可使总运费最小。

二、某校学生在大学三年级第一学期必须要选修的课程只有一门,可供限定选修的课程有8门,任意选修课程有10门,由于一些课程之间互有联系,所以可能在选修某门课程中必须同时选修其他课程,这18门课程的学分数和要求同时选修课程的相应信息如表:按学校规定,每个学生每学期选修的总学分不能少于21学分,因此,学生必须在上述18门课程中至少选修19学分学校同时还规定学生每学期选修任意选修课的学分不能少于3学分,也不能超过6学分,为了达到学校的要求,试为该学生确定一种选课方案。

问题分析:本题是一道典型的0-1规划的问题,本体的难点在于,选了B一定要选A,但选了A却有选B,和不选B这两种方案,故不可采用以前普通的计算方式,考虑相减,即A-B>=0就可解决该问题。

c=[-5,-5,-4,-4,-3,-3,-3,-2,-3,-3,-3,-2,-2,-2,-1,-1,-1,-1];a=[-5,-5,-4,-4,-3,-3,-3,-2,-3,-3,-3,-2,-2,-2,-1,-1,-1,-1;0,0,0,0,0,0,0,0,3,3,3,2,2,2,1,1,1,1;0,0,0,0,0,0,0,0,-3,-3,-3,-2,-2,-2,-1,-1,-1,-1;-1,0,0,0,1,0,0,0,0,0,0,0,0,0,0,0,0,0;0,-1,0,0,0,0,1,0,0,0,0,0,0,0,0,0,0,0;0,0,0,0,0,0,0,-1,1,0,0,0,0,0,0,0,0,0;0,0,0,0,0,-1,0,0,0,1,0,0,0,0,0,0,0,0;0,0,0,-1,0,0,0,0,0,0,1,0,0,0,0,0,0,0;0,0,0,0,-1,0,0,0,0,0,0,1,0,0,0,0,0,0;0,0,0,0,0,0,-1,0,0,0,0,0,1,0,0,0,0,0;0,0,0,0,0,-1,0,0,0,0,0,0,0,1,0,0,0,0];b=[-19;6;-3;0;0;0;0;0;0;0;0];[x,favl]=bintprog(c,a,b)favl=-favl;结果分析:有实验结果可知,连选前10门课才可达到学校的要求。

西安交通大学理论力学小组大作业报告

西安交通大学理论力学小组大作业报告组员:李鲁熙,钟锦涛,王瑞杰,靳宇栋,陈云翔,曾云豪,王涛实验时间:2014-2015学期下实验主要内容:搭建桁架,多点摩擦,柔性摩擦,三线摆测物体转动惯量理论力学实验报告——桁架(一)实验准备小组成员:李鲁熙王瑞杰陈云翔曾云豪靳宇栋王涛钟锦涛总计实验时间:26小时实验器材:一次性筷子、大头针、手电钻、卷尺、锯子(二)设计思路为了利用三角形的稳定性,我们将桁架的顶端设计成成了三角形。

这样一来底面只能是三角形或六边形。

如果底面是三角形,桁架只有三个侧面,而如果底面是六边形,那么桁架会有六个侧面。

为了增加桁架的载重量,我们选择了六边形地面。

相对于增加载重量,我们在减轻桁架自身重量上下了更多的功夫。

我们将桁架的六个侧面分为两个种类。

一种侧面主要用于承载重量,因此这种侧面上的杆件是斜着的,这样就可以将施于桁架上的力分散到下面。

另一种侧面主要用于防止桁架变形,因为桁架的侧面都是倾斜着的,所以在加上重物的时候可能会变形压向某一侧面。

因此这种侧面上的杆件都是水平的,起着相当于固定每个竖直杆件的作用。

(三)搭建过程在搭建桁架时首先要决定杆件之间如何连接,对于这个细节我们采用的方法是将两根杆件重叠一部分,然后再重叠的部分上加一块很短的杆件,再用手电钻打孔将大头针插入并固定。

我们首先搭建三个杆件是倾斜的侧面,为了使最后的桁架有良好的载重性,我们在搭建时尽量保证这三个侧面尺寸相同。

然后将这三个侧面组合起来便可以得到桁架的主体结构。

但是我们经过尝试发现将这三个侧面整齐地组合起来很困难,因为这些侧面很大而且很难立起来钻孔。

最后我们在地面上铺一张纸,纸上面画一个和设计桁架底面相同的正五边形。

将三个侧面的一个底边分别对在五边形的三个对边上,再将它们立起来从上到下用大头针固定。

在搭建好主体结构后,我们再在新形成的三个侧面上分别搭上相等数量的水平杆件便完成了搭建。

(四)问题及解决方案在此次实验中我们遇到的最大的问题就是很难把三个侧面整齐的组装起来。

(完整word版)FPGA专题实验实验报告-西安交通大学

实验1:状态机问题一:你觉得上面这段代码中,q 到底在怎样变化?答:首先语句中缺少begin,q <= q也不合理;如果有异步复位信号,q=0;否则,如果有上升沿且a不等于1,q=q;如果有上升沿且a=1,q直接等于b;问题二:本页中,q 到底在怎样变化?答:复位时,q=0;否则q=d。

问题三:sync电路图:仿真:该电路使输入信号与时钟同步,并产生稳定脉冲信号,进行节拍分配。

四、红路灯电路系统框图:问题分析:东西南北都有车时,状态转换时,东西绿灯时间长于60s;三秒后,南北通行,绿灯时间少于40s。

计数器不能使用同一个,但可以减少触发器数目实验2:数字钟环节二仿真时注意问题:1.仿真1小时需要多少时间?答:取决于输入信号clk的频率。

2.现在的时钟是秒时钟,实际系统的时钟是50MHz.那用50MHz的时钟的情况下,仿真1小时要多少时间?如何解决该问题?答:1/50000000*60*60=0.000072 s;可以将输入信号分频。

环节三1,复位如何输入的?按键防抖如何制作的?修改按键防抖的间隔会导致什么问题?答:复位信号由clock顶层文件输入,按键防抖思路是使按键信号通过触发器进行延迟,持续输入十个上升沿才认为按键一次,避免了抖动。

增加时间会导致按键时间边长,短按可能误认为是抖动。

2,数码管的显示使用组合逻辑输出好还是时序逻辑输出好?答:组合逻辑好环节四:闰年:y1和y2分别为输入的年高两位和年低两位,y为年份,当cout=1时为闰年,cou=0时为平年。

如果y2=0则y1能被4整除时为闰年:当y2!=0时y2能被4整除则为闰年。

后面通过将y1循环加100次再加上y2得到年份y。

process(y1,y2)variable i:integer;beginif y2=0 thenif (y1 rem 4)=0 thencout<='1';else cout<='0';end if;elsif y1 rem 4=0 thencout<='1';else cout<='0';end if;i:=y1;for n in 0 to 99 loopi:=i+i;end loop;y<=i+y2;end process;实验3:SRAM环节二、两种仿真的比较lab/lab3/step1/memtest.vhd用功能仿真和时序仿真两种方法,比较一下SS的状态数值的变化。

西安交通大学电子系统设计专题实验.(DOC)

电子系统设计专题实验报告实验一、基于 AVR ATMega128 的硬件(PCB)设计 一、 实验目的和要求目的: (1)掌握印制电路板设计的基本原则及印制电路板的设计制作流程。

(2)掌握 Protel DXP 2004 SP2 软件的基本功能。

(3)在 Protel DXP 2004 SP2 软件平台,完成电路图到 PCB 图的设计制作过 程。

要求: (1)根据实验要求, 完成原理图的设计,并在 Protel DXP 2004 SP2 软件平台 上设计制作出相应的 PCB 图。

(2)要求 PCB 图布局布线美观,抗干扰性能强。

图中所用到的元件封装必须 符合实际的元件尺寸。

二、 实验设备及设计开发环境操作系统: XP 软件:Protel DXP 2004 SP 2三、 实验内容根据 ATMega128 的电路图设计一个单片机电路板,其中包括基本电路、复位 电路、时钟振荡器(ISP、键盘、RT Clock)。

MCU 原理图如图四、 实验步骤1. 创建新的工程项目,并新建原理图图纸 2. 设置工程参数,包括基本原理图参数设置。

3. 绘制原理图:在元件库中查找所用元件,并进行必要说明,如标签、总线、 端口等。

4. 放置各个模块与图纸合适位置,方便之后端口的对接及导入。

5. 对原理图进行电气检查,编译查错时,直至消除后保存原理图。

6. 创建新的 PCB 文件,并对 PCB 进行正确合理的参数设置(注意:在设置尺 寸时,不宜设置太小,不利于元件布局及布线),保存文件。

7. 导入原理图,将元件合理放置,原则:组合功能的元件(键盘开关)有序放 置在一起,使得各个元件布线交叉尽可能的少。

8. 对电路板自动布线,进行规则检查,注意检查 PCB 有没有缺线、缺元件的 情况修改错误的地方,并注意印刷线路的宽度设置,不宜太宽。

9. 重复步骤 8,对电路板布局不断进行修改优化,直到 PCB 的规则检查没有警告、错误,电路板元件布局思路清晰,布线方式正确合理。

西安交通大学组成专题实验报告汇编

计算机组织与结构专题实验报告 MIPS 单周期处理器的设计学生姓名 赵荣建 专业班级 计算机45班 学 号 2140505119 指导教师 姜欣宁 完成日期 2017-05-09一.实验目的根据所学的CPU组成原理,自主设计一个MIPS32位的单周期处理器。

二.设计方案参照计算机组成原理教材上的MIPS32位处理器的工作原理。

1.构建数据通路取指周期:a.从指令寄存器PC输出端得到地址b.送地址到指令存储器IM地址端Ac.从指令存储器IM的数据端RD得到指令d.计算下地址:通过运算器,PC+4形成下地址,送回到PC。

2. .MIPS 寄存器集:定义了32个32位的寄存器3.MIPS三种指令格式:R-类型、I-类型和J-类型R-类型格式:* 所有指令操作吗OP都是0;特定操作由funct决定。

* 机器语言指令中,字段分配格式如上图;前两个寄存器rs、 rt 是源寄存器,rd是目的寄存器。

而在汇编语言格式中,第一个寄存器是目的寄存器。

如:add $t0,$s4,$s5 #[rd]=[rs]+[rt],[t0]=[s4]+[s5];I-类型格式:* 指令含4个字段;op, rs, rt 和 imm* 有两个寄存器操作数和一个16位立即数操作数,一些指令中,rt也可作为源寄存器。

J-类型格式:* 有一个26位立即数操作数,扩展后形成目的地址。

4.算逻单元ALU 的设计ALU 工作原理图* 两级控制:通过系统控制器(Control )B A和运算器控制器(ALU Control)产生ALU的控制信号:ALUoper* ALU控制信号对照表:5.单周期数据通路的构建1)构件:PC、指令存储器、寄存器文件RF和数据存储器; 2)取指令的过程:PC→IM: A/RD3)取源操作数的过程:IM:RD→RF:A1/RD1。

4)立即数的符号扩展的过程:IM:RD(Instr:15:0)→Sign Extend(15:0→Signimm31:0);其中Signimm15:0=Instr15:0, Signimm31:16=Instr155)存储器地址计算:6)向寄存器文件写入数据RegWrite信号被置成1,写入过程在时钟周期最后的时钟上升沿完成。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

计算机组织与结构专题实验报告 MIPS 单周期处理器的设计学生姓名 赵荣建 专业班级计算机45班 学 号 ********** 指导教师 姜欣宁 完成日期 2017-05-09一.实验目的根据所学的CPU组成原理,自主设计一个MIPS32位的单周期处理器。

二.设计方案参照计算机组成原理教材上的MIPS32位处理器的工作原理。

1.构建数据通路取指令指令译码指令执行存储器访问结果写回取指周期:a.从指令寄存器PC输出端得到地址b.送地址到指令存储器IM地址端Ac.从指令存储器IM的数据端RD得到指令d.计算下地址:通过运算器,PC+4形成下地址,送回到PC。

2. .MIPS 寄存器集:定义了32个32位的寄存器3.MIPS三种指令格式:R-类型、I-类型和J-类型R-类型格式:* 所有指令操作吗OP都是0;特定操作由funct决定。

* 机器语言指令中,字段分配格式如上图;前两个寄存器rs、 rt 是源寄存器,rd是目的寄存器。

而在汇编语言格式中,第一个寄存器是目的寄存器。

如:add $t0,$s4,$s5 #[rd]=[rs]+[rt],[t0]=[s4]+[s5];I-类型格式:* 指令含4个字段;op, rs, rt 和 imm* 有两个寄存器操作数和一个16位立即数操作数,一些指令中,rt也可作为源寄存器。

J-类型格式:* 有一个26位立即数操作数,扩展后形成目的地址。

4.算逻单元ALU 的设计ALU 工作原理图* 两级控制:通过系统控制器(Control )B A和运算器控制器(ALU Control)产生ALU的控制信号:ALUoper* ALU控制信号对照表:5.单周期数据通路的构建1)构件:PC、指令存储器、寄存器文件RF和数据存储器; 2)取指令的过程:PC→IM: A/RD3)取源操作数的过程:IM:RD→RF:A1/RD1。

4)立即数的符号扩展的过程:IM:RD(Instr:15:0)→Sign Extend(15:0→Signimm31:0);其中Signimm15:0=Instr15:0, Signimm31:16=Instr155)存储器地址计算:6)向寄存器文件写入数据RegWrite信号被置成1,写入过程在时钟周期最后的时钟上升沿完成。

7)形成PC的下地址指令占4个字节,字编址。

6.单周期控制器的构建控制单元基于指令中的opcode字段(31:26)、funct字段(5:0)产生控制信号;主译码的真值表。

见下图:7.完整的单周期MIPS处理器三.设计过程1.指令集设计R型指令指令序号指令译码结果(B)存储指令(H)$t0,$t1,$t2 100010<2> and$s3,$s4,$s5 000000 10100 10101 10011 0000010010002959824<3> or$s0,$s6,$s7 000000 10110 10111 10000 0000010010102d78025<4> xor$t3,$t4,$t5 000000 01100 01101 01011 00000100110018d5826<5> slt$t7,$t5,$t6 000000 01101 01110 01111 0000010101001ae782a<6> nor$t7,$t5,$t6 000000 01101 01110 01111 0000010011101ae7827<13> srl$t0,$s1,$t5 000000 10001 01101 01000 00000000010022d4002<14> sll$t0,$s1,$t2 000000 10001 01010 01000 00000000000022a4000<17> inc $t0,$t6 000000 01110 00000 01000 0000000001101c04003指令序号指令译码结果(B)存储指令(H)00000001<11> beq $t1,$t1,1 000100 01001 01001 000000000000000111290001 J型指令指令序号指令译码结果(B)存储指令(H)2.MIPS 32位单周期处理器结构设计CPU设计结构图如下:信号说明:a1:pc中的指令的地址送往IM去寻找指令a2:pc产生的下一条指令的地址a3:pc中指令的地址加4a4:取pc中指令的地址加4后的高六位b1:取J型指令的低26位b2:操作码字段高六位b3:第一个源操作数的寄存器地址,R型的21-25位,I型的21-25位b4:第二个源操作数的寄存器地址,R型的16-20位,I型指令的目的寄存器地址,16-20位b5:R型指令的目的寄存器地址,11-15位b6:I型指令的立即数,0-15位b7:R型指令的低六位,0-5位b8:b4和b5经二路选择器二选一b20:从IM中取出来的指令内容c1:I型指令将16位立即数扩展成32位c2:存入目的寄存器的内容c3:从源寄存器1中取出的内容c4:从源寄存器2中取出的内容c5:c1和c4二选一c6:ALU计算出的结果,也是读DM的地址c7:从DM中取出的内容c8、c9:针对不同类型的指令对进行pc值的修正的选择d1:功能选择信号e类信号:主操作控制信号,主要是各部件的读写控制信号核心模块说明:IM:按序号存放指令(共17条,其中lw指令执行了两次),在CPU启动时从<0>开始执行。

Rf:主寄存器,存放32个32位字,存储情况见下表(十进制表示,单数行是地址序号,双数行是对应的存储值):<0> <1> <2> <3> <4> <5> <6> <7>7 6 5 4 3 2 1 0<16> <17> <18> <19> <20> <21> <22> <23>DM是对应的存储值):<0> <1> <2> <3> <4> <5> <6> <7>8 7 6 5 4 3 2 1<16> <17> <18> <19> <20> <21> <22> <23>8 7 6 5 4 3 2 1<24> <25> <26> <27> <28> <29> <30> <31>tRf:测试模块,用于输出指令执行结果以检验是否正确;IRf:测试模块,用于输出当前执行的指令,与tRf搭配使用。

四.代码分析1.Add //完成分支指令的目标地址计算//library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity add isPort ( a: in STD_LOGIC_VECTOR (31 downto 0);b : in STD_LOGIC_VECTOR (31 downto 0);y : out STD_LOGIC_VECTOR (31 downto 0));end add;architecture Behavioral of add isbeginy<=a + b;-------将a和b相加赋给yend Behavioral;2.Add4 //完成PC+1(采用字寻址)的计算//library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity Add4 isport(pcin:in std_logic_vector(31 downto 0);pcout:out std_logic_vector(31 downto 0)); end Add4;architecture behave of Add4 isbeginprocess(pcin)beginpcout <= pcin + 1;---------pc值的修改end process;end behave;3.ALU //主运算器//library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity alu isPort (a1, b1 : in STD_LOGIC_vector(31 downto 0);alucontr: in STD_LOGIC_VECTOR (3 downto 0);result : buffer STD_LOGIC_VECTOR (31 downto 0);zero : out STD_LOGIC);end alu;architecture behave of alu is--signal d1: integer;--signal c1,f1: bit_vector(31 downto 0);beginprocess(a1,b1,alucontr)begincase alucontr iswhen "0000"=> result<= a1 and b1; ------and 与操作when "0001"=> result<= a1 or b1; -----or或操作when "0010"=> result<= a1 + b1; -----add 相加when "0011"=> result<= a1 xor b1; -----xor异或when "0100"=> result<= a1 nor b1; ------nor或非操作when "0101"=> result<=TO_STDLOGICVECTOR(to_bitvector(a1) sll conv_integer(b1)); ------Sll将a1向左移动b1数值位when "0110"=> result<= a1 - b1; -----sub减法when "1001"=> result<= a1 + 1; ------inc自增when "1010"=> result<= a1 - 1; -------dec自减when "0111"=> ----slt比较大小if(a1<b1)then result<=x"00000001";else result<=x"00000000";end if;when "1000"=> result<=TO_STDLOGICVECTOR(to_bitvector(a1) srl conv_integer(b1)); ------srl算术右移when others=> result<=x"00000000";end case;if(a1=b1)then --beq 判断分支指令是否转移当a1=b1时进行转移zero<='1';elsezero<='0';end if;end process;end behave;4.and_gate //与门,完成分支指令的判定//library ieee;use ieee.std_logic_1164.all;entity and_gate isport(a,b:in std_logic;c:out std_logic);end and_gate;architecture dataflow of and_gate isbeginc <= a and b;end dataflow;5.mux2_1 //5位二路选择器,由控制信号选择目的寄存器//library ieee;use ieee.std_logic_1164.all;entity mux2_1 isgeneric (width:integer:=5);Port ( d0,d1 : in STD_LOGIC_VECTOR (width-1 downto 0);s : in STD_LOGIC;y : out STD_LOGIC_VECTOR (width-1 downto 0));end mux2_1;architecture Behavioral of mux2_1 isbeginy<=d0 when s='0' else d1;---------s位0选择d0,若s为1选择d1 end Behavioral;6.Rf //32个32位寄存器组成的主寄存器,有预存//library ieee;use ieee.std_logic_1164.all;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity regfile isPort ( clk : in STD_LOGIC;we3 : in STD_LOGIC;------写使能信号ra1 : in STD_LOGIC_VECTOR (4 downto 0);------源寄存器1的地址ra2 : in STD_LOGIC_VECTOR (4 downto 0);------- 源寄存器2的地址wa3 : in STD_LOGIC_VECTOR (4 downto 0);--------目的寄存器地址wd3 : in STD_LOGIC_VECTOR (31 downto 0);-------写入目的寄存器的内容rd1 : out STD_LOGIC_VECTOR (31 downto 0);--------从源寄存器1中读出的内容rd2 : out STD_LOGIC_VECTOR (31 downto 0));-------从源寄存器2中读出的内容end regfile;architecture Behavioral of regfile is--subtype ramtype is std_logic_vector(31 downto 0);--type memory is array(0 to 31) of ramtype;type ramtype is array(31 downto 0) of STD_LOGIC_VECTOR(31 DOWNTO 0); SIGNAL mem:ramtype:=--signal mem_initial:memory:=((x"00000000"),(x"00000001"),(x"00000002"),(x"00000003"),(x"00000004" ),(x"00000005"),(x"00000006"),(x"00000007"),(x"00000008"),(x"00000009"),(x"0000000a"),(x"0000000b"),(x"0000000c") ,(x"0000000d"),(x"0000000e"),(x"0000000f"),(x"00000000"),(x"00000001"),(x"00000002"),(x"00000003"),(x"00000004") ,(x"00000005"),(x"00000006"),(x"00000007"),(x"00000008"),(x"00000009"),(x"0000000a"),(x"0000000b"),(x"0000000c") ,(x"0000000d"),(x"0000000e"),(x"00000000"));---------预先存入32个寄存器的32位数beginprocess(clk) beginif (clk'event and clk='1') thenif (we3='1') then mem(CONV_INTEGER(wa3))<=wd3;------写使能信号为一,将目的寄存器的内容写入目的寄存器地址所对的单元内end if;end if;end process;process(ra1,ra2) beginif(conv_integer(ra1)=0)then rd1<=x"00000000";else rd1<=mem(conv_integer(ra1));------读出源寄存器1中的内容end if;if(conv_integer(ra2)=0) then rd2<=x"00000000";else rd2<=mem(conv_integer(ra2));--------- -读出源寄存器2中的内容end if;end process;end Behavioral;7.signext //符号拓展模块,将16位立即数拓展为32位,用于分支指令// library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity signext isPort ( a : in STD_LOGIC_VECTOR (15 downto 0);y : out STD_LOGIC_VECTOR (31 downto 0));end signext;architecture Behavioral of signext isbeginY<=X"0000"& a when a(15)='0' else x"ffff" &a;-----------16位数扩展为32位,若是正数,前面扩展0,负数则扩展1end Behavioral;8.PC //程序计数器,提供取指令地址//library ieee;use ieee.std_logic_1164.all;entity pc is --实体描述port(pc_in: in std_logic_vector(31 downto 0);clk,reset: in std_logic;pc_out: out std_logic_vector(31 downto 0));end pc;architecture behave of pc is --实体的行为描述--signal pc_temp: std_logic_vector(31 downto 0);beginF:process(clk)beginif (clk'event and clk = '1') thenif(reset='0')thenpc_out <= pc_in;end if;end if;end process;end behave;9.IM //指令存储器,已预存17条指令,由PC指出地址//library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use IEEE.STD_LOGIC_ARITH.ALL;entity IM isport(--clk,read,write:in std_logic;address:in std_logic_vector(31 downto 0);--im_in:in std_logic_vector(31 downto 0);im_out:out std_logic_vector(31 downto 0));end IM;architecture behave of IM issubtype dword is std_logic_vector(31 downto 0);type memory is array(0 to 18) of dword;signal mem_initial:memory:=((x"02328020"),(x"012a4022"),(x"02959824"),(x"02d78025"),(x"018d5826" ),(x"01ae782a"),(x"01ae7827"),(x"8d300001"),(x"ad290001"),(x"8d300001"),(x"21280001"),(x"11290001" )--beq,(x"00000000"),(x"022d4002"),(x"022a4000"),(x"08000011")--J,(x"00000000"),(x"01c04003"),(x"01a04004"));-----------指令寄存器中预先存储了17条指令beginprocess(address)beginim_out<=mem_initial(conv_integer(address));end process;end behave;10.control //主控制器,用于译码指令输出控制信号// library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity controller isPort ( memtoreg,memwrite,memread : out STD_LOGIC;op : in STD_LOGIC_VECTOR (5 downto 0);branch,alusrc : out STD_LOGIC;regdst,regwrite : out STD_LOGIC;jump : out STD_LOGIC;aluop : out STD_LOGIC_VECTOR (1 downto 0));end controller;architecture Behavioral of controller issignal controls:STD_LOGIC_VECTOR (9 downto 0);beginprocess(op)begincase op iswhen "000000"=>controls<="0110000010";--R型when "100011"=>controls<="1101001000";-----lw(只有这种情况memread会是1)when "101011"=>controls<="0001010000";------swwhen "000100"=>controls<="0000110000";------beqwhen "001111"=>controls<="010*******";-------luiwhen "001000"=>controls<="010*******";------addiwhen "000010"=>controls<="0000000100";--J型转移when others =>controls<="----------";end case;end process;memread <=controls(9);regwrite<=controls(8);regdst <=controls(7);alusrc <=controls(6);branch <=controls(5);memwrite<=controls(4);memtoreg<=controls(3);jump <=controls(2);aluop <=controls(1 downto 0);----------对应e类型的信号,相应各位决定了是否进行寄存器读写,存储器读写等操作end Behavioral;11.ALU control //ALU译码器,用于完成运算器的功能选择//library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity alucontrol isPort ( funct : in STD_LOGIC_VECTOR (5 downto 0);aluop1 : in STD_LOGIC_VECTOR (1 downto 0);aluoper : out STD_LOGIC_VECTOR (3 downto 0)); end alucontrol;architecture Behave of alucontrol isbeginprocess (aluop1,funct) begincase aluop1 iswhen"00"=>aluoper<="0010";--add(for 1w/sw/addi/lui/j) when"01"=>aluoper<="0110";--sub(for beq)when others=>case funct iswhen "100000"=>aluoper<="0010";------addwhen "100010"=>aluoper<="0110";-----subwhen "100100"=>aluoper<="0000";-----andwhen "100101"=>aluoper<="0001";----orwhen "101010"=>aluoper<="0111";-----sltwhen "100110"=>aluoper<="0011";-----xorwhen "100111"=>aluoper<="0100";----norwhen "000000"=>aluoper<="0101";-----sllwhen "000010"=>aluoper<="1000";-----srlwhen "000011"=>aluoper<="1001";-----incwhen "000100"=>aluoper<="1010";-----decwhen others =>aluoper<="----";end case;end case;end process;end Behave;12.DM //数据存储器,有预存//library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity dm isport(address: in std_logic_vector(31 downto 0);data_in: in std_logic_vector(31 downto 0);write,read: in std_logic;data_out: out std_logic_vector(31 downto 0);clock: in std_logic);end dm;architecture behave of dm istype ramtype is array(31 downto 0) of STD_LOGIC_VECTOR(31 DOWNTO 0);SIGNAL sram:ramtype:=((x"00000001"),(x"00000002"),(x"00000003"),(x"00000004"),(x"00000005" ),(x"00000006"),(x"00000007"),(x"00000008"),(x"00000001"),(x"00000002"),(x"00000003"),(x"00000004"),(x"00000005") ,(x"00000006"),(x"00000007"),(x"00000008"),(x"00000001"),(x"00000002"),(x"00000003"),(x"00000004"),(x"00000005") ,(x"00000006"),(x"00000007"),(x"00000008"),(x"00000001"),(x"00000002"),(x"00000003"),(x"00000004"),(x"00000005") ,(x"00000006"),(x"00000007"),(x"00000008"));------------预先存储在DM中的数据,用于对实验的进行验证使用beginwrite_op:process(write,clock)beginif(clock'event and clock='1') thenif(read='0' and write='1') thensram(conv_integer(address))<=data_in;-------数据读入DMend if;end if;end process;read_op:process(read,write,sram,address)beginif (read='1' and write='0') thendata_out<=sram(conv_integer(address));------------数据从DM中读出elsedata_out<=(others=>'Z');end if;end process;end behave;13.mux2_11 //32位二路选择器,实例化4次完成不同的功能//library ieee;use ieee.std_logic_1164.all;entity mux2_11 isgeneric (width:integer:=32);Port ( d01,d11 : in STD_LOGIC_VECTOR (width-1 downto 0);s1 : in STD_LOGIC;y1 : out STD_LOGIC_VECTOR (width-1 downto 0));end mux2_11;architecture Behavioral of mux2_11 isbeginy1<=d01 when s1='0' else d11;end Behavioral;14.tRf //测试模块,用于输出指令执行结果以检验是否正确//library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity tregfile isPort ( tclk : in STD_LOGIC;twe3 : in STD_LOGIC;tra1 : in STD_LOGIC_VECTOR (4 downto 0);tra2 : in STD_LOGIC_VECTOR (4 downto 0);twa3 : in STD_LOGIC_VECTOR (4 downto 0);twd3 : in STD_LOGIC_VECTOR (31 downto 0);trd1 : out STD_LOGIC_VECTOR (31 downto 0);trd2 : out STD_LOGIC_VECTOR (31 downto 0));end tregfile;architecture Behavioral of tregfile istype ramtype is array(31 downto 0) of STD_LOGIC_VECTOR(31 DOWNTO 0);SIGNAL mem:ramtype;beginprocess(tclk) beginif (tclk'event and tclk='1') thenif (twe3='1') then mem(CONV_INTEGER(twa3))<=twd3;--------向目的寄存器中写数据end if;end if;end process;process(tra1,tra2) beginif(conv_integer(tra1)=0)then trd1<=x"00000000";else trd1<=mem(conv_integer(tra1));-----读源寄存器1中的数据end if;if(conv_integer(tra2)=0) then trd2<=x"00000000";else trd2<=mem(conv_integer(tra2));------- 读源寄存器1中的数据end if;end process;end Behavioral;15.IRf //测试模块,用于输出当前执行的指令,与tRf搭配使用// library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity Iregfile isPort ( iclk : in STD_LOGIC;iwe3 : in STD_LOGIC;ira1 : in STD_LOGIC_VECTOR (4 downto 0);ira2 : in STD_LOGIC_VECTOR (4 downto 0);iwa3 : in STD_LOGIC_VECTOR (4 downto 0);iwd3 : in STD_LOGIC_VECTOR (31 downto 0);ird1 : out STD_LOGIC_VECTOR (31 downto 0);ird2 : out STD_LOGIC_VECTOR (31 downto 0));end Iregfile;architecture Behavioral of Iregfile istype ramtype is array(31 downto 0) of STD_LOGIC_VECTOR(31 DOWNTO 0); SIGNAL mem:ramtype;beginprocess(iclk) beginif (iclk'event and iclk='1') thenif (iwe3='1') then mem(CONV_INTEGER(iwa3))<=iwd3;end if;end if;end process;process(ira1,ira2) beginif(conv_integer(ira1)=0)then ird1<=x"00000000";else ird1<=mem(conv_integer(ira1));end if;if(conv_integer(ira2)=0) then ird2<=x"00000000";else ird2<=mem(conv_integer(ira2));end if;end process;end Behavioral;16.CPU //顶层模块//library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity CPU isport(rout1,rout2: out std_logic_vector(31 downto 0);--测试clk1,ret: in std_logic);end CPU;architecture behave of CPU issignal a1,a2,a3,a4:std_logic_vector(31 downto 0);signal b1:std_logic_vector(25 downto 0);signal b2,b7:std_logic_vector(5 downto 0);signal b3,b4,b5,b8:std_logic_vector(4 downto 0);signal b6:std_logic_vector(15 downto 0);signal c1,c2,c3,c4,c5,c6,c7,c8,c9,b20:std_logic_vector(31 downto 0); signal d1:std_logic_vector(1 downto 0);signal e1,e2,e3,e4,e5,e6,e7,e8,e9,e10 :std_logic;signal f1:std_logic_vector(3 downto 0);--signal g1:std_logic_vector(27 downto 0);--------------具体信号见前面,都具体解释了component Add4port(pcin:in std_logic_vector(31 downto 0);pcout:out std_logic_vector(31 downto 0));end component;component pcport(pc_in: in std_logic_vector(31 downto 0);clk,reset: in std_logic;pc_out: out std_logic_vector(31 downto 0)); end component;-----------pc模块component IMport(--clk,read,write:in std_logic;address:in std_logic_vector(31 downto 0);--im_in:in std_logic_vector(31 downto 0);im_out:out std_logic_vector(31 downto 0));end component;-----------IM模块component addPort ( a: in STD_LOGIC_VECTOR (31 downto 0);b : in STD_LOGIC_VECTOR (31 downto 0);y : out STD_LOGIC_VECTOR (31 downto 0));end component;----------add模块component mux2_1generic (width:integer:=5);Port ( d0,d1 : in STD_LOGIC_VECTOR (width-1 downto 0); s : in STD_LOGIC;y : out STD_LOGIC_VECTOR (width-1 downto 0)); end component;-------------mux2_1模块component mux2_11generic (width:integer:=32);Port ( d01,d11 : in STD_LOGIC_VECTOR (width-1 downto 0); s1 : in STD_LOGIC;y1 : out STD_LOGIC_VECTOR (width-1 downto 0)); end component;component and_gateport(a,b:in std_logic;c:out std_logic);end component;------------- mux2_11模块component controllerPort ( memtoreg,memwrite,memread : out STD_LOGIC;op : in STD_LOGIC_VECTOR (5 downto 0);branch,alusrc : out STD_LOGIC;regdst,regwrite : out STD_LOGIC;jump : out STD_LOGIC;aluop : out STD_LOGIC_VECTOR (1 downto 0));end component;component regfilePort ( clk : in STD_LOGIC;we3 : in STD_LOGIC;ra1 : in STD_LOGIC_VECTOR (4 downto 0);ra2 : in STD_LOGIC_VECTOR (4 downto 0);wa3 : in STD_LOGIC_VECTOR (4 downto 0);wd3 : in STD_LOGIC_VECTOR (31 downto 0);rd1 : out STD_LOGIC_VECTOR (31 downto 0);rd2 : out STD_LOGIC_VECTOR (31 downto 0)); end component;-----------controller模块component signextPort ( a : in STD_LOGIC_VECTOR (15 downto 0);y : out STD_LOGIC_VECTOR (31 downto 0));end component;-------------- signext模块component aluPort (a1, b1 : in STD_LOGIC_vector(31 downto 0);alucontr: in STD_LOGIC_VECTOR (3 downto 0);result : buffer STD_LOGIC_VECTOR (31 downto 0);zero : out STD_LOGIC);end component;--------- alu模块component alucontrolPort ( funct : in STD_LOGIC_VECTOR (5 downto 0);aluop1 : in STD_LOGIC_VECTOR (1 downto 0);aluoper : out STD_LOGIC_VECTOR (3 downto 0));end component;-------------- alucontrol模块component dmport(address: in std_logic_vector(31 downto 0);data_in: in std_logic_vector(31 downto 0);write,read: in std_logic;data_out: out std_logic_vector(31 downto 0);clock: in std_logic);end component;--------------DM模块component tregfilePort ( tclk : in STD_LOGIC;twe3 : in STD_LOGIC;tra1 : in STD_LOGIC_VECTOR (4 downto 0):=("00001"); tra2 : in STD_LOGIC_VECTOR (4 downto 0):=("00000"); twa3 : in STD_LOGIC_VECTOR (4 downto 0):=("00001"); twd3 : in STD_LOGIC_VECTOR (31 downto 0);trd1 : out STD_LOGIC_VECTOR (31 downto 0);trd2 : out STD_LOGIC_VECTOR (31 downto 0));end component;component IregfilePort ( iclk : in STD_LOGIC;iwe3 : in STD_LOGIC;ira1 : in STD_LOGIC_VECTOR (4 downto 0):=("00001"); ira2 : in STD_LOGIC_VECTOR (4 downto 0):=("00000"); iwa3 : in STD_LOGIC_VECTOR (4 downto 0):=("00001"); iwd3 : in STD_LOGIC_VECTOR (31 downto 0);ird1 : out STD_LOGIC_VECTOR (31 downto 0);ird2 : out STD_LOGIC_VECTOR (31 downto 0));end component;begina4<=(a3(31 downto 26))&(b1);z1:Add4 port map(pcin=>a1,pcout=>a3);z2:and_gate port map(a=>e2,b=>e9,c=>e10);z3:mux2_1 port map(d0=>b4,d1=>b5,s=>e7,y=>b8);z4:mux2_11 port map(d01=>c4,d11=>c1,s1=>e6,y1=>c5);z5:mux2_11 port map --memtoreg (d01=>c6,d11=>c7,s1=>e3,y1=>c2);z6:mux2_11 port map(d01=>a3,d11=>c8,y1=>c9,s1=>e10);z7:mux2_11 port map(d01=>c9,d11=>a4,y1=>a2,s1=>e8);z8:regfile port map (clk=>clk1,we3=>e1,ra1=>b3,ra2=>b4,wa3=>b8,wd3=>c2,rd1=>c3,rd2=>c4);z9:signext port map (a=>b6,y=>c1);z12:pc port map (pc_in=>a2,pc_out=>a1,clk=>clk1,reset=>ret);z13:IM port mapim_out(25 downto 0)=>b1, im_out(31 downto 26)=>b2, im_out(25 downto 21)=>b3, im_out(20 downto 16)=>b4, im_out(15 downto 11)=>b5, im_out(15 downto 0)=>b6, im_out(5 downto 0)=>b7, address=>a1,im_out(31 downto 0)=>b20 );z14:add port map(a=>a3,b=>c1,y=>c8);z15:controller port map (memtoreg=>e3,memwrite=>e4,memread=>e5,op=>b2,branch=>e2,alusrc=>e6,regdst=>e7,regwrite=>e1,jump=>e8,aluop=>d1);z16:alu port map(a1=>c3,b1=>c5,alucontr=>f1,result=>c6,zero=>e9);z17:alucontrol port map (funct=>b7,aluop1=>d1,aluoper=>f1);z18:dm port map(address=>c6,data_in=>c4,write=>e4,read=>e5,data_out=>c7,clock=>clk1);z19:tregfile port map(tclk=>clk1,twe3=>e1,trd1=>rout1,twd3=>c2);z20:Iregfile port map(iclk=>clk1,iwe3=>e1,ird1=>rout2,iwd3=>b20);end behave;五.实验结果分析根据Rf、DM及IM存储情况,每一条指令执行结果为:结果11011 00001 1010 01001 00001 00000 1..100 00001 同<7> 序号<9> <10> <11> <13> <14> <15> <17> <18> 指令lw addi beq srl sll J inc dec 结果00110 00111 00111 00011 111000000 同<14> 00010 00001 仿真结果:加法add的实现:源寄存器1为10001,第17个,源寄存器2为10010,为第18个,17号寄存器里存放的是14,18号寄存器李存放的是13(可由上面查表获得数值),两数相加结果为27,应存放到10000,16号寄存器里。