计算机组成原理期末考试A卷-含答案

2022年南昌大学软件工程专业《计算机组成原理》科目期末试卷A(有答案)

2022年南昌大学软件工程专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、主存储器主要性能指标有()。

1.存储周期Ⅱ.存储容量Ⅲ.存取时间Ⅳ.存储器带宽A.I、IⅡB.I、IⅡ、IVC. I、Ⅲ、lVD.全部都是2、某机器字长32位,存储容量64MB,若按字编址,它的寻址范围是()。

A.8MB.16MBC.16MD.8MB3、完整的计算机系统应该包括()。

A.运算器、存储器、控制器B.外部设备和主机C.主机和应用程序D.主机、外部设备、配套的软件系统4、下列关于计算机操作的单位时间的关系中,正确的是()。

A.时钟周期>指令周期>CPU周期B.指令周期CPU周期>时钟周期C.CPU周期>指令周期>时钟周期D.CPU周期>时钟周期>指令周期5、()可区分存储单元中在放的是指令还是数据。

A.存储器B.运算C.用户D.控制器6、某总线共有88根信号线,其中数据总线为32根,地址总线为20根,控制总线36根,总线工作频率为66MHz、则总线宽度为(),传输速率为()A.32bit 264MB/sB.20bit 254MB/sC.20bit 264MB/sD.32bit 254MB/s7、总线的半同步通信方式是()。

A.既不采用时钟信号,也不采用握手信号B.只采用时钟信号,不采用握手信号C.不采用时钟信号,只采用握手信号D.既采用时钟信号,又采用握手信号8、某计算机的指令流水线由4个功能段组成,指令流经各功能段的时间(忽略各功能段之间的缓存时间)分别为90ns,80ns、70ns和60ns,则该计算机的CPU时钟周期至少是)()。

A.90nsB.80nsC.70nsD.60ns9、同步控制是()。

A.只适用于CPU控制的方式B.由统一时序信号控制的方式C.所有指令执行时问都相同的方式D.不强调统一时序信号控制的方式10、下列选项中,用于设备和设备控制器(I/O接口)之间互连的接口标准是()。

计算机组成原理试卷A卷答案

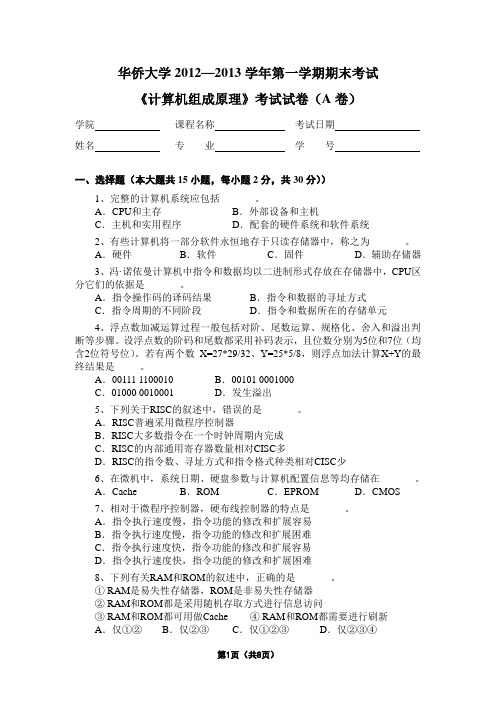

华侨大学2012—2013学年第一学期期末考试《计算机组成原理》考试试卷(A卷)学院课程名称考试日期姓名专业学号一、选择题(本大题共15小题,每小题2分,共30分))1、完整的计算机系统应包括_______。

A.CPU和主存B.外部设备和主机C.主机和实用程序D.配套的硬件系统和软件系统2、有些计算机将一部分软件永恒地存于只读存储器中,称之为_______。

A.硬件B.软件C.固件D.辅助存储器3、冯·诺依曼计算机中指令和数据均以二进制形式存放在存储器中,CPU区分它们的依据是_______。

A.指令操作码的译码结果B.指令和数据的寻址方式C.指令周期的不同阶段D.指令和数据所在的存储单元4、浮点数加减运算过程一般包括对阶、尾数运算、规格化、舍入和溢出判断等步骤。

设浮点数的阶码和尾数都采用补码表示,且位数分别为5位和7位(均含2位符号位)。

若有两个数X=27*29/32、Y=25*5/8,则浮点加法计算X+Y的最终结果是_____。

A.00111 1100010 B.00101 0001000C.01000 0010001 D.发生溢出5、下列关于RISC的叙述中,错误的是_______。

A.RISC普遍采用微程序控制器B.RISC大多数指令在一个时钟周期内完成C.RISC的内部通用寄存器数量相对CISC多D.RISC的指令数、寻址方式和指令格式种类相对CISC少6、在微机中,系统日期、硬盘参数与计算机配置信息等均存储在_______。

A.Cache B.ROM C.EPROM D.CMOS7、相对于微程序控制器,硬布线控制器的特点是_______。

A.指令执行速度慢,指令功能的修改和扩展容易B.指令执行速度慢,指令功能的修改和扩展困难C.指令执行速度快,指令功能的修改和扩展容易D.指令执行速度快,指令功能的修改和扩展困难8、下列有关RAM和ROM的叙述中,正确的是_______。

① RAM是易失性存储器,ROM是非易失性存储器② RAM和ROM都是采用随机存取方式进行信息访问③ RAM和ROM都可用做Cache ④ RAM和ROM都需要进行刷新A.仅①②B.仅②③C.仅①②③D.仅②③④9、下列不会引起指令流水阻塞的是_______。

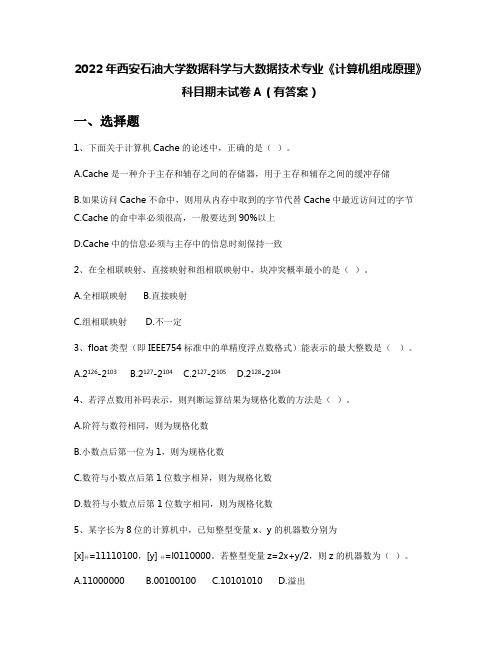

2022年西安石油大学数据科学与大数据技术专业《计算机组成原理》科目期末试卷A(有答案)

2022年西安石油大学数据科学与大数据技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、下面关于计算机Cache的论述中,正确的是()。

A.Cache是一种介于主存和辅存之间的存储器,用于主存和辅存之间的缓冲存储B.如果访问Cache不命中,则用从内存中取到的字节代替Cache中最近访问过的字节C.Cache的命中率必须很高,一般要达到90%以上D.Cache中的信息必须与主存中的信息时刻保持一致2、在全相联映射、直接映射和组相联映射中,块冲突概率最小的是()。

A.全相联映射B.直接映射C.组相联映射D.不一定3、float类型(即IEEE754标准中的单精度浮点数格式)能表示的最大整数是()。

A.2126-2103B.2127-2104C.2127-2105D.2128-21044、若浮点数用补码表示,则判断运算结果为规格化数的方法是()。

A.阶符与数符相同,则为规格化数B.小数点后第一位为1,则为规格化数C.数符与小数点后第1位数字相异,则为规格化数D.数符与小数点后第1位数字相同,则为规格化数5、某字长为8位的计算机中,已知整型变量x、y的机器数分别为[x]补=11110100,[y] 补=l0110000。

若整型变量z=2x+y/2,则z的机器数为()。

A.11000000 B.00100100 C.10101010 D.溢出6、中断判优逻辑和总线仲裁方式相类似,下列说法中,正确的是()。

I.在总线仲裁方式中,独立请求方式响应时间最快,是以增加处理器开销和增加控制线数为代价的II.在总线仲裁方式中计数器查询方式,若每次计数都从“0”开始,则所有设备使用总线的优先级相等III.总线仲裁方式一般是指I/O设备争用总线的判优方式,而中断判优方式一般是指I/O设备争用CPU的判优方式IV.中断判优逻辑既可以通过硬件实现,也可以通过软件实现,A. I,IIB. I,III,IVC. I,II,IVD.I,IV7、在链式查询方式下,若有N个设备,则()。

计算机组成原理期末考试及答案

计算机组成原理期末考试及答案A卷基础知识(50分)1、名词解释(10分)机器字长SRAMEPROM指令系统微指令2、选择题(10分)1)设字长32位,使⽤IEEE格式,则阶码采⽤______表⽰。

A.补码B. 原码C. 移码D. 反码2) 四⽚74181ALU和⼀⽚74182CLA器件相配合,具有如下进位传递功能______。

A.形波进位B. 组内先⾏进位,组间先⾏进位C.组内先⾏进位,组间⾏波进位D. 组内形波进位,组间先⾏进位3) 某SARM芯⽚,其存储容量为64K×16位,该芯⽚的地址线数⽬和数据线数⽬分别是___。

A. 16, 16 B .16, 64, C. 64, 8 D. 64, 164)单地址指令中为了完成两个数的算术运算,除地址码指明的⼀个操作数外,另⼀个数常需采⽤______。

A. 堆栈寻址⽅式B. ⽴即寻址⽅式C. 隐含寻址⽅式D. 间接寻址⽅式微5)程序控制器中,机器指令与微指令的关系是______。

A.每⼀条机器指令由⼀条微指令来执⾏B.⼀段机器指令组成的程序可由⼀条微指令执⾏C.⼀条微指令由若⼲条机器指令组成D. 每⼀条机器指令由⼀段⽤微指令编成的微程序来解释执⾏3、填空题(10分)1)存储___①___并按__②____顺序执⾏,这是冯?诺依曼型计算机的⼯作原理。

2)相联存储器是按③访问的存储器。

3) 主存与cache的地址映射有__④___、⑤、⑥三种⽅式。

4)通常指令编码的第⼀个字段是⑦。

5) 异步通信⽅式可分为⑧、⑨、⑩三种类型。

4、问答题(20分)1)在计算机中,为什么要采⽤多级结构的存储器系统2)简述CPU的功能.3)试⽐较⽔平型微指令与垂直型微指令。

4)简述总线集中控制的优先权仲裁⽅式。

⼆、综合应⽤(50分)1、已知X=-0.1101,Y=0.1011,试⽤补码⼀位乘法计算X×Y (15分)2、指令格式如下所⽰。

OP为操作码字段,试分析指令格式特点。

计算机组成原理期末考试试卷及答案(1)

计算机组成原理期末考试试卷(1)一.选择题(下列每题有且仅有一个正确答案,每小题2分,共20分)1.假设下列字符码中最后一位为校验码,如果数据没有错误,则采用偶校验的字符码的是____。

A. 11001011B. 11010110C. 11000001D. 110010012.在定点二进制运算器中,减法运算一般通过______ 来实现。

A. 补码运算的二进制加法器B. 补码运算的二进制减法器C. 补码运算的十进制加法器D. 原码运算的二进制减法器3.下列关于虚拟存储器的说法,正确的是____。

A. 提高了主存储器的存取速度B. 扩大了主存储器的存储空间,并能进行自动管理和调度C. 提高了外存储器的存取速度D. 程序执行时,利用硬件完成地址映射4.下列说法正确的是____。

A. 存储周期就是存储器读出或写入的时间B. 双端口存储器采用了两套相互独立的读写电路,实现并行存取C. 双端口存储器在左右端口地址码不同时会发生读/写冲突D. 在cache中,任意主存块均可映射到cache中任意一行,该方法称为直接映射方式5.单地址指令中,为了完成两个数的算术运算,除地址码指明的一个操作数外,另一个操作数一般采用____寻址方式。

A. 堆栈B. 立即C. 隐含D. 间接6.指令系统中采用不同寻址方式的目的主要是______ 。

A.实现存储程序和程序控制 B.提供扩展操作码的可能并降低指令译码难度C.可以直接访问外存 D.缩短指令长度,扩大寻址空间,提高编程灵活性7.下列说法中,不符合RISC指令系统特点的是____。

A. 指令长度固定,指令种类少B. 寻址方式种类尽量少,指令功能尽可能强C. 增加寄存器的数目,以尽量减少访存的次数D. 选取使用频率最高的一些简单指令,以及很有用但不复杂的指令8. 指令周期是指______。

A .CPU 从主存取出一条指令的时间B .CPU 执行一条指令的时间C .CPU 从主存取出一条指令加上执行这条指令的时间D .时钟周期时间 9. 假设微操作控制信号用n C 表示,指令操作码译码输出用m I 表示,节拍电位信号用k M 表示,节拍脉冲信号用i T 表示,状态反馈信息用i B 表示,则硬布线控制器的控制信号n C 可描述为____。

2022年太原科技大学计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)

2022年太原科技大学计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、某计算机的存储系统由Cache一主存系统构成,Cache的存取周期为10ms,主存的存取周期为50ms。

在CPU执行一段程序时,Cache完成存取的次数为4800次,主存完成的存取次数为200次,该Cache一主存系统的效率是()。

【注:计算机存取时,同时访问Cache和主存,Cache访问命中,则主存访问失效;Cache访问未命中,则等待主存访问】A.0.833B.0.856C.0.95 8D.0.8622、局部性原理是一个持久的概念,对硬件和软件系统的设计和性能都有着极大的影响。

局部性通常有两种不同的形式:时间局部性和空间局部性。

程序员是否编写出高速缓存友好的代码,就取决于这两方面的问题。

对于下面这个函数,说法正确的是()。

int sumvec(int v[N]){int i, sum=0;for(i=0;i<N;i++)sum+= v[i]eturn sum;}A.对于变量i和sum,循环体具有良好的空间局部性B.对于变量i、sum和v[N],循环体具有良好的空间局部性C.对于变量i和sum,循环体具有良好的时间局部性D.对于变量i、sum和v[N],循环体具有良好的时间局部性23、假设在网络中传送采用偶校验码,当收到的数据位为10101010时,则可以得出结论()A.传送过程中未出错B.出现偶数位错C.出现奇数位错D.未出错或出现偶数位错4、某机器字长为8位,采用原码表示法(其中一位为符号位),则机器数所能表示的范围是()。

A.-127~+127B.-127~+128C.-128~+127D.-128~+1285、并行加法器中,每位全和的形成除与本位相加两数数值位有关外,还与()有A.低位数值大小B.低位数的全和C.高位数值大小D.低位数送来的进位6、总线宽度与下列()有关。

A.控制线根数B.数据线根数C.地址线根数D.以上都不对7、下列关于同步总线的说法中,正确的有()。

2022年成都文理学院计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)

2022年成都文理学院计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、访问相联存储器时,()A.根据内容,不需要地址B.不根据内容,只需要地址C.既要内容,又要地址D.不要内容也不要地址2、某C语言程序段如下:for(i=0;i<9;i++){temp=1;for(j=0;j<=i;j++)temp+=a[J];sum+=temp;}下列关于数组a的访问局部性的描述中,正确的是()。

A.时间局部性和空间局部性皆有B.无时间局部性,有空间局部性C.有时间局部性,无空间局部性D.时间局部性和空间局部性皆无3、下列关于各种移位的说法中正确的是()。

I.假设机器数采用反码表示,当机器数为负时,左移时最高数位丢0,结果出错;右移时最低数位丢0,影响精度Ⅱ在算术移位的情况下,补码左移的前提条件是其原最高有效位与原符号位要相同Ⅲ.在算术移位的情况下,双符号位的移位操作中只有低符号位需要参加移位操作()A. Ⅲ、ⅡB.只有ⅡC.只有ⅢD.全错4、下列说法正确的是()。

A.当机器采用补码表示时,0有两种编码方式B.当机器采用原码表示时,0有两种编码方式C.当机器采用反码表示时,0有一种编码方式D.无论机器数采用何种码表示,0都有两种编码方式5、某机字长8位,含一位数符,采用原码表示,则定点小数所能表示的非零最小正数为()A.2-9B.2-8C.2-7D.2-66、某机器I/O设备采用异步串行传送方式传送字符信息,字符信息格式为1位起始位、8位数据位、1位校验位和1位停止位。

若要求每秒传送640个字符,那么该设备的有效数据传输率应为()。

A.640b/sB.640B/sC.6400B/sD.6400b/s7、某同步总线采用数据线和地址线复用方式,其中地址/数据线有32根,总线时钟频率为66MHz,每个时钟周期传送两次数据(上升沿和下降沿各传送一次数据),该总线的最大数据传输率(总线带宽)是()。

计算机组成原理期末考试试题及答案

计算机组成原理期末考试试题及答案一、选择题(每题2分,共20分)1. 计算机硬件系统主要由哪两部分组成?A. 控制器和运算器B. 输入设备和输出设备C. 中央处理器和外部设备D. 存储器和输入输出设备答案:C2. 下面哪个不是计算机的五大组成部分?A. 控制器B. 运算器C. 输入设备D. 电源答案:D3. 下面哪个寄存器用于存放将要执行的下一条指令的地址?A. 指令寄存器B. 程序计数器C. 地址寄存器D. 数据寄存器答案:B4. 下面哪个不是计算机的数据表示方法?A. 二进制B. 十进制C. 八进制D. 十六进制答案:B5. 下面哪个不是计算机的存储器层次结构?A. 寄存器B. 高速缓存C. 主存储器D. 硬盘答案:D6. 下面哪个不是计算机的输入设备?A. 鼠标B. 键盘C. 扫描仪D. 显示器答案:D7. 下面哪个不是计算机的输出设备?A. 显示器B. 打印机C. 扬声器D. 键盘答案:D8. 下面哪个不是计算机的总线类型?A. 数据总线B. 地址总线C. 控制总线D. 通信总线答案:D9. 下面哪个不是计算机的指令类型?A. 数据传输指令B. 算术运算指令C. 逻辑运算指令D. 中断指令答案:D10. 下面哪个不是计算机的并行计算技术?A. 流水线技术B. 向量处理技术C. 多线程技术D. 分布式计算技术答案:D二、填空题(每题2分,共20分)1. 计算机硬件系统主要由______和______组成。

答案:中央处理器,外部设备2. 计算机的五大组成部分包括:控制器、运算器、______、______和______。

答案:存储器,输入设备,输出设备3. 计算机的数据表示方法有:二进制、八进制、十六进制等,其中计算机内部使用的是______。

答案:二进制4. 计算机的存储器层次结构包括:寄存器、高速缓存、______和______。

答案:主存储器,硬盘5. 计算机的指令分为:数据传输指令、算术运算指令、逻辑运算指令和______。

2022年南京农业大学计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)

2022年南京农业大学计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、若数据在存储器中采用以低字节地址为字地址的存放方式(小端存储),则十六进制数12345678H按自己地址由小到大依次存为()。

A.12345678B.87654321C.78563412D.341278562、一个存储器系统中,常常同时包含ROM和RAM两种类型的存储器,如果用lK×8位的ROM芯片和lK×4位的RAM芯片,组成4K×8位的ROM和1K×8位的RAM存储系统,按先ROM后RAM进行编址。

采用3-8译码器选片,译码信号输出信号为Y0~Y7,其中Y4选择的是()。

A.第一片ROMB.第五片ROMC.第一片RAMD.第一片RAM和第二片RAM3、假定有4个整数用8位补码分别表示:rl=FEH,r2=F2H,r3=90H,r4=F8H,若将运算结果存放在一个8位寄存器中,则下列运算会发生溢出的是()。

A.rlxr4B.r2xr3C.rlxr4D.r2xr44、用海明码对长度为8位的数据进行检/纠错时,若能纠正一位错,则校验位数至少为()。

A.2B.3C.4D.55、浮点数加/减运算过程一般包括对阶、尾数运算、规格化、舍入和判断溢出等步骤。

设浮点数的阶码和尾数均采用补码表示,且位数分别为5位和7位(均含两位符号位)。

若有两个数,即x=2×29/32,y=25×5/8,则用浮点数加法计算xty的最终结果是()。

A.001111100010B.001110100010C.010*********D.发生溢出6、关于同步控制说法正确的是()。

A.采用握手信号B.由统一时序电路控制的方式C.允许速度差别较大的设备一起接入工作D.B和C7、下列关于总线仲裁方式的说法中,正确的有()。

I.独立请求方式响应时间最快,是以增加处理器开销和增加控制线数为代价的II.计数器定时查询方式下,有,根总线请求(BR)线和一根设备地址线,若每次计数都从0开始,则设备号小的优先级高III.链式查询方式对电路故障最敏感IV.分布式仲裁控制逻辑分散在总线各部件中,不需要中央仲裁器A.III,IVB. I,III,IVC. I,II,IVD.II,III,IV8、下列关于计算机操作的单位时间的关系中,正确的是()。

2022年深圳大学计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)

2022年深圳大学计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、设存储器容量为32字,字长为64位。

模块数m=4,采用低位交叉方式。

存储周期T=200ns,数据总线宽度为64位,总线传输周期r=50ns。

该交叉存储器的带宽是()。

A.32×107bit/sB.8×107bit/sC.73×107bit/sD.18×107bit/s2、某机器的主存储器共32KB,由16片16K×l位(内部采用128×128存储阵列)的DRAM芯片字和位同时扩展构成。

若采用集中式刷新方式,且刷新周期为2ms,那么所有存储单元刷新一遍需要()个存储周期。

A.128B.256C.1024D.163843、假设机器字长为16位,用定点补码小数表示时,一个字所能表示的范围是()。

A.0~(1-2-15)B.-(1-2-15)~(1-2-15)C.-1~1D.-1~(1-2-15)4、float型数据通常用IEEE754标准中的单精度浮点数格式表示。

如果编译器将float型变量x分配在一个32位浮点寄存器FR1中,且x=-8.25,则FR1的内容是()。

A.C1040000HB.C2420000HC. C1840000HD.CIC20000H5、在浮点机中,判断原码规格化的形式的原则是()。

A.尾数的符号位与第一数位不同B.尾数的第一数位为1,数符任意C.尾数的符号位与第一位相同D.阶符与数符不同6、下列关于总线设计的叙述中,错误的是()。

A.并行总线传输比串行总线传输速度快B.采用信号线复用技术可减少信号线数量C.采用突发传输方式可提高总线数据传输率D.采用分离事务通信方式可提高总线利用率7、某同步总线的时钟频率为100MHz,宽度为32位,地址/数据线复用,每传输一个地址或数据占用一个时钟周期。

若该总线支持突发(猝发)传输方式,则一次“主存写”总线事务传输128位数据所需要的时间至少是()。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

广东外语外贸大学信息学院计算机系

2004—2005学年第2学期

《计算机组成原理》期末考试试卷A

考卷适用班级:计算机专业03级考试时间:120分钟

班级_______ 学号_____________姓名_________成绩_______ 一、填空题(每空1分,共20分)

1.8位二进制补码表示整数的最小值为__-128____,最大值为__127___。

2.计算机常用的校验码有奇偶校验码、海明校验码、____CRC码_____。

3.一个浮点数,当其补码尾数右移1位时,为使其值不变,阶码应该__加1____。

4.ALU的基本逻辑结构是__快速进位__加法器,它比行波进位加法器优越,具有先行进位逻辑,不仅可以实现高速运算,还能完成逻辑运算。

5.采用双符号位的方法进行溢出检测时,若运算结果中两个符号位__不相同__,则表明发生了溢出。

6.要组成容量为4M×8位的存储器,需要__8__片4M×1位的存储器芯片并联,或者需要__4____片1M×8位的存储器芯片串联。

7.一台计算机所具有的各种机器指令的集合称为该计算机的__指令系统__。

8.指令编码中,操作码用来指定__操作的类型__,n位操作码最多可以表示___2n____条指令。

9.CPU中,保存当前正在执行的指令的寄存器为__指令寄存器IR_,保存下一条指令地址的寄存器为_程序计数器PC__,保存CPU访存地址的寄存器为__内存地址寄存器AR__。

10.控制器在生成各种控制信号时,必须按照一定的__时序__进行,以便对各种操作实施时间上的控制。

11.微程序控制器的核心部件是存储微程序的__控制存储器____,它一般用_只读存储器_构成。

12.任何指令周期的第一步必定是__取指__周期。

13.异步方式下,总线操作周期时间不固定,通过_握手(就绪/应答)_信号相互联络。

14.输入输出操作实现的CPU与I/O设备的数据传输实际上是CPU与__IO设备接口寄存器__之间的数据传输。

二、选择题(每小题1分,共20分)

1.冯·诺曼机工作方式的基本特点是___________。

A.多指令流单数据流B.按地址访问并顺序执行指令

C.堆栈操作D.存储器按内容选择地址

2.主机中能对指令进行译码的器件是_________。

A.ALU B.运算器

C.控制器D.存储器

3.运算器的主要功能是进行_______。

A.逻辑运算B.算术运算

C.逻辑运算和算术运算D.中作加法

4.32位微型计算机的乘除法部件位于________中。

A.CPU B.接口

C.控制器D.专用芯片

5.串行运算器是一种最简单的运算器,其运算规则是:按时间先后次序_________。

A.由低位到高位逐位运算B.由高位到低位逐位运算

C.由低位到高位先行进位运算D.由高位到低位先行借位运算

6.内存若为16兆(MB),则表示其容量为__________KB。

A.16 B.16384

C.1024 D.16000

7.若RAM芯片的容量是2M×8位,则该芯片引脚中地址线和数据线的数目之和是________。

A.21 B.29

C.18 D.不可估计

8.计算机的存储器采用分级方式是为了__________。

A.减少主机箱的体积

B.解决容量、价格、速度三者之间的矛盾

C.保存大量数据方便

D.操作方便

9.软磁盘、硬磁盘、磁带机、光盘、固态盘属于_________设备。

A.远程通信B.外存储器

C.内存储器D.人机界面的I/O

10.假设微处理器的主振频率为50MHz,两个时钟周期组成一个机器周期,平均三个机器周期完成一条指令,则它的平均运算速度近似为________MIPS。

A.2 B.3 C.8D.15

11.CPU内通用寄存器的位数取决于__________。

A.存储器容量B.机器字长

C.指令的长度D.CPU的管脚数

12.以硬连线方式构成的控制器也称为_________。

A.组合逻辑控制器B.微程序控制器

C.存储逻辑型控制器D.运算器

13.一节拍脉冲持续的时间长短是___________。

A.指令周期B.机器周期

C.时钟周期D.以上都不对

14.在微程序控制器中,机器指令和微指令的关系是____________。

A.每一条机器指令由一条微指令来执行

B.一条微指令由若干条机器指令组成

C.每一条机器指令由一段用微指令组成的微程序来解释执行

D.一段微程序由一条机器指令来执行

15.由于CPU内部的操作速度较快,而CPU访问一次主存所花的时间较长,因此机器周期通常用_________来规定。

A.主存中读取一个指令字的最短时间

B.主存中读取一个数据字的最长时间

C.主存中写入一个数据字的平均时间

D.主存中取一个数据字的平均时间

16.系统总线中地址线的功能是________。

A.用于选择主存单元地址

B.用于选择进行信息传输的设备

C.用于选择外存地址

D.用于指定主存和I/O设备接口电路的地址

17.在集中式总线仲裁中,_________方式响应时间最快。

A.菊花链B.独立请求

C.计数器定时查询

18.微型机系统中,主机和高速硬盘进行数据交换一般采用__________方式。

A.程序中断控制B.直接存储器访问(DMA)

C.程序直接控制D.通道控制

19.在微机中,VGA代表_________。

A.微机的型号B.键盘的型号

C.显示标准D.显示器的型号

20.在中断响应过程中,保护程序计数器PC的作用是____________。

A.使CPU能找到中断处理程序的入口地址

B.使中断返回后,能回到断点处继续原程序的执行

C.使CPU和外部设备能并行工作

D.为了实现中断嵌套

三、简答题(每小题5分,共20分)

1.什么叫总线?它有什么用途?试举例说明。

答:

2.机器指令包括哪两个基本要素?微指令又包括哪两个基本要素?程序靠什么实现顺序执行?

答:

3.说明层次结构的存储系统中Cache和虚拟存储器的作用有何不同。

答:

4.说明程序I/O方式和中断I/O方式的差别。

答:

四、综合题(每小题10分,共20分)

1.设CPU内有下列部件:PC、IR、MAR、MDR、AC、CU。

(1)写出取指周期的全部微操作;

(2)写出加法指令ADD X ,无条件转移指令JMP Y ,结果为零则转指令BAZ Y 在执行阶段所需的全部微操作;

(3)当上述的加法指令为间接寻址时,写出运行加法指令所需的全部微操作。

解:(1)取指周期的全部微操作:

T0 PC→MAR, 1→R

T1 Ad(CMDR)→CMAR

T2 M(MAR)→MDR, (PC)+1→PC

T3 Ad(CMDR)→CMAR

T4 MDR→IR

T5 OP(IR)→微地址形成部件→CMAR

(2)加法指令ADD @X 在间址周期和执行周期的全部微操作

间址周期

T0 Ad (IR) →MAR, 1→R

T1 Ad(CMDR)→CMAR

T2 M(MAR)→MDR

T3 Ad(CMDR)→CMAR

T4 MDR→ Ad (IR)

T5 OP(IR)→微地址形成部件→CMAR

执行周期

T0 Ad (IR) →MAR, 1→R

T1 Ad(CMDR)→CMAR

T2 M(MAR)→MDR

T3 Ad(CMDR)→CMAR

T4 (AC)+(MDR)→ AC

T5 Ad(CMDR)→CMAR

2. 某机有五个中断源L 0、L 1、L 2、L 3、L 4,按中断响应的优先次序由高向低排序为L 0→L 1→L 2→L 3→L 4,现要求中断处理次序改为L 1→L 3→L 4→L 0→L 2,根据下示格式,写出各中断源的屏蔽字。

五、 计算题(共20分)

1.设有效信息为101,试用生成多项式G(x)=11011,将其编成循环冗余校验码(7分)。

解:有效信息M(x)=101=x 2+1 (n=3)

G(x)=11011= x 4+ x 3+x+1 得k+1=5 k=4

M(x)·x 4=1010000= x 6+ x 4

11011

1010110110111010000)()(4+==x G x x M M(x)·x 4+R(x)=1010000+1010=1011010 为CRC 码

2.设机器数字长为8位(含1位符号位在内),写出真值-87对应的原码、补码和反码(7分)。

解:原码=11010111

反码=10101000

补码=10101001

3.设机器数字长为8位(含1位符号位在内),用补码运算规则计算A -B (6分)。

其中:A=18/32,B=15/128

解:A=0.1001000 B=0.0001111

[-B]补=1.1110001

A -B=A+[-B]补=0.0111001=57/128。