FPGA设计中DAC7512控制的Verilog实现

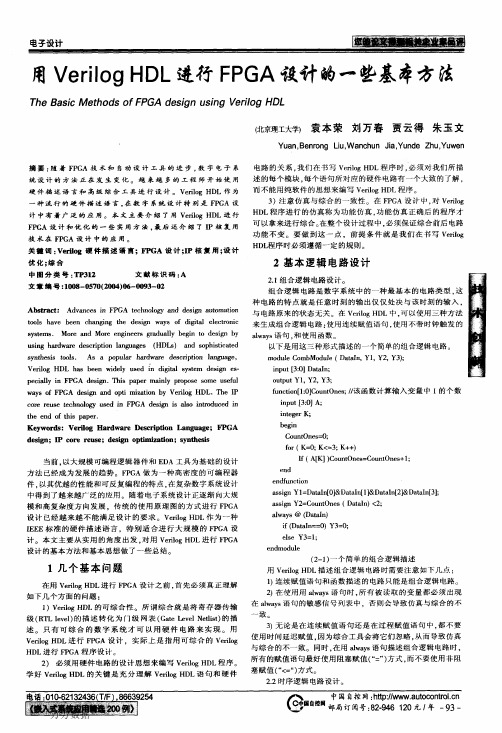

用Verilog+HDL进行FPGA设计的一些基本方法

Dout<=Dout+1;

end

endmodule

f2—2)一个简单的8位计数器电路描述

用Verilog HDL描述时序逻辑电路时需要注意以下两点:

1)在用always语句描述时序逻辑电路时,只可能出现如下

三种形式:

a)always@(posedge Clk):不包含任何异步复位信号.但可

能包含同步复位信号。

3)注意仿真与综合的一致性。在FPGA设计中,对Verilog HDL程序进行的仿真称为功能仿真.功能仿真正确后的程序才 可以拿来进行综合。在整个设计过程中,必须保证综合前后电路 功能不变。要做到这一点,前提条件就是我们在书写Verilog HDD程序时必须遵循一定的规则。

2基本逻辑电路设计

2.1组合逻辑电路设计。 组合逻辑电路是数字系统中的一种最基本的电路类型。这 种电路的特点就是任意时刻的输出仅仅处决与该时刻的输入, 与电路原来的状态无关。在Verilog HDL中,可以使用三种方法 来生成组合逻辑电路:使用连续赋值语句,使用不带时钟触发的

if fDataln==qDl Y3=0; else Y3=1:

ห้องสมุดไป่ตู้

endmodule

(2-一1)一个简单的组合逻辑描述 用Verilog HDL描述组合逻辑电路时需要注意如下几点: 1)连续赋值语句和函数描述的电路只能是组合逻辑电路。

2)在使用用always语句时,所有被读取的变量都必须出现 在always语句的敏感信号列表中.否则会导致仿真与综合的不 一致。

≮穆国自控弼邮局订阅号:82.946 120元/年一93—

圈豳圈圜图豳堕圃豳豳蛋

《微计算机信息>(测控自动化)2004年第20卷第6期

FPGA与CPLD相比。最大的一个特点就是它的寄存器相当 丰富,因此.更加适合设计时序逻辑电路。实际上,由于FPGA内 部延迟的不确定.用FPGA描述的电路大多是时序逻辑电路。

时序约束实例

用Quartus II Timequest Timing Analyzer进展时序分析:实例讲解(一)(2012-06-21 10:25:54)▼标签:杂谈一,概述用Altera的话来讲,timequest timing analyzer是一个功能强大的,ASIC-style的时序分析工具。

采用工业标准--SDC〔synopsys design contraints〕--的约束、分析和报告方法来验证你的设计是否满足时序设计的要求。

在用户的角度,从我使用TimeQuest的经历看,它与IC 设计中经常用到的比方prime time,time craft等STA软件是比拟类似的。

用过prime time或time craft的朋友是非常容易上手的。

在这一系列的文章里,我将会拿一个DAC7512控制器的verilog设计作为例子,详细讲解如何使用TimeQuest进展时序设计和分析。

二,TimeQuest的根本操作流程做为altera FPGA开发流程中的一个组成局部,TimeQuest执行从验证约束到时序仿真的所有工作。

Altera推荐使用下面的流程来完成TimeQuest的操作。

1. 建立项目并参加相关设计文件不管做什么事情,都需要有一个目标或者说对象。

我们用TimeQuest做时序分析,当然也需要一个对象,这个对象实际上就是我们的设计。

所以首先是要建立一个Quartus II的项目,并把所有需要的设计文件都参加到项目中去。

需要注意的一点是,这里的设计文件,不仅仅包含逻辑设计相关的文件,也包含已经存在的时序约束文件,当然,需要以synopsys Design Constraints(.sdc)的格式存在的。

2. 对项目进展预编译〔initial compilation〕项目建立以后,如果从来没有对项目进展过编译的话,就需要对项目进展预编译。

这里的预编译是对应于全编译〔full compilation〕来讲的,我们可以理解为预编译是对项目进展局部的编译,而全编译是对项目进展完整的编译。

fpga dac设计注意事项

一、FPGA DAC设计注意事项在进行FPGA DAC设计时,有一些重要的注意事项需要我们特别关注。

这些注意事项涉及到硬件设计、时序控制、电源管理和性能优化等方面。

下面,我将根据这些关键要点来探讨FPGA DAC设计的注意事项。

1. 硬件设计硬件设计是FPGA DAC设计中至关重要的一环。

在进行硬件设计时,我们需要特别关注PCB布局、时序优化和信号完整性。

良好的PCB布局可以减小信号传输的损耗和噪声干扰,从而提高系统的性能和稳定性。

时序优化可以确保数字信号的准确采样和转换,从而保证DAC的输出精度和准确性。

信号完整性也是硬件设计中需要特别关注的问题,良好的信号完整性可以有效减小信号失真和串扰,从而提高系统的性能和可靠性。

2. 时序控制时序控制是FPGA DAC设计中的另一个重要方面。

在进行时序控制时,我们需要特别关注时钟频率、数据同步和时序校准等问题。

合理的时钟频率可以确保数字信号的准确采样和转换,同时也能减小时序误差和时序不稳定性。

数据同步是时序控制中需要特别关注的问题,良好的数据同步可以确保各路数字信号的同步输出,从而提高系统的性能和稳定性。

时序校准也是时序控制中需要重点关注的问题,合理的时序校准可以有效减小时序误差和时序不稳定性,从而提高系统的性能和可靠性。

3. 电源管理电源管理是FPGA DAC设计中另一个值得重视的方面。

在进行电源管理时,我们需要特别关注电源精度、电源噪声和电源稳定性等问题。

良好的电源精度可以确保DAC的输出精度和准确性,同时也能减小电源噪声对系统性能的影响。

电源稳定性也是电源管理中需要特别关注的问题,稳定的电源可以确保DAC的稳定输出和长期可靠性,从而提高系统的性能和可靠性。

4. 性能优化性能优化是FPGA DAC设计中不可忽视的一环。

在进行性能优化时,我们需要特别关注输出带宽、动态范围和信噪比等问题。

合理的输出带宽可以确保数字信号的准确采样和转换,同时也能保证系统的高速输出和快速响应。

虚拟数字存储示波器设计

虚拟数字存储示波器设计张佑春;张公永【摘要】Aiming at series of problems of traditional digital oscilloscope,such as difficult signal analy-sis, weak data storage capacity, high cost and so on, a design scheme of virtual digital storage oscilloscope based on LabVIEW is proposed.The hardware system consists of four parts, namely, attenuation and gain control, A/D conversion, sampling control and data storage.The software system is constructed on the basis of LabVIEW platform which has friendly interface and easy operation.The virtual digital storage oscilloscope has functions of seven gear vertical sensitivities, eighteen scanning speeds, seven trigger modes chosen freely etc., which can realize signal acquisition, analysis, processing, display and so on.After three kinds of signal test, such as sine wave, square wave and triangle wave, the virtual digital storage oscilloscope has stable oper-ation, high reliability, good performance and certain application prospect.%给出了一种基于LabVIEW的虚拟数字存储示波器设计方案,硬件部分由衰减和增益控制、A/D转换、采样控制和数据存储4部分构成,软件部分基于LabVIEW平台搭建。

dac的veriloga语句

dac的veriloga语句

嘿,你知道 DAC 的 Verilog 语句吗?这玩意儿可神奇啦!就好像是搭建数字电路世界的魔法积木。

比如说,你想设计一个超级酷炫的计数器,那 Verilog 语句就能帮你实现。

“module counter (input clk, output reg [7:0] count); always

@(posedge clk) count <= count + 1; endmodule”,看,就这么几行语句,一个简单的计数器就出来了,神奇不神奇?

再想想,这 Verilog 语句就像是一个指挥家,能让那些电子元件们乖乖听话,按照你设定的规则来运行。

你可以用它来创造各种各样的数字电路,小到一个简单的逻辑门,大到一个复杂的处理器,都不在话下!

我之前和我的小伙伴一起做项目的时候,我们就对 Verilog 语句又爱又恨。

有时候,为了让一个功能完美实现,我们得绞尽脑汁去想合适的语句,不断地尝试和修改。

“哎呀,这段语句怎么又出错啦!”“别急别急,再仔细看看呢!”我们互相打气,一起攻克一个又一个难题。

当我们终于看到自己设计的电路按照我们的想法工作时,那种成就感简直爆棚!“哇塞,我们成功啦!”那感觉就像是我们创造了一个小小的奇迹。

在这个数字电路的世界里,Verilog 语句就是我们手中的利器,让我们能尽情发挥自己的想象力和创造力。

它虽然有时候会让我们头疼,但更多的时候是给我们带来无尽的乐趣和挑战。

所以啊,DAC 的 Verilog 语句,真的是超级有趣又超级重要的东西呢!别小看这些语句,它们可是能创造出无数精彩的数字世界的哟!。

UnconstrainedPaths解决办法

UnconstrainedPaths解决办法⽤TimeQuest对DAC7512控制器进⾏时序分析在对某个对象下时序约束的时候,⾸先要能正确识别它,TimeQuest 会对设计中各组成部分根据属性进⾏归类,我们在下时序约束的时候,可以通过命令查找对应类别的某个对象。

TimeQuest对设计中各组成部分的归类主要有cells,pins,nets和ports ⼏种。

寄存器,门电路等为cells;设计的输⼊输出端⼝为ports;寄存器,门电路等的输⼊输出引脚为pins;ports和pins之间的连线为nets。

具体可以参照下图(此图出⾃Altera Time Quest的使⽤说明)。

下⾯我们按照本⽂第⼆部分⽤TimeQuest做时序分析的基本操作流程所描述的流程对DAC7512控制器进⾏时序分析。

建⽴和预编译项⽬的部分相对简单,涉及到的也只是QuartusII的⼀些基本操作,这⾥我们就不再做具体的叙述。

主要介绍如何向项⽬中添加时序约束和如何进⾏时序验证。

⾸先建⽴⼀个名称与项⽬top层名字⼀致的sdc⽂件,然后按照下⾯的步骤添加时序约束。

1. 创建时钟添加时序约束的第⼀步就是创建时钟。

为了确保STA结果的准确性,必须定义设计中所有的时钟,并指定时钟所有相关参数。

TimeQuest⽀持下⾯的时钟类型:a) 基准时钟(Base clocks)b) 虚拟时钟(Virtual clocks)c) 多频率时钟(Multifrequency clocks)d) ⽣成时钟(Generated clocks)我们在添加时序约束的时候,⾸先创建时钟的原因是后⾯其它的时序约束都要参考相关的时钟的。

基准时钟:基准时钟是输⼊到FPGA中的原始输⼊时钟。

与PLLs输出的时钟不同,基准时钟⼀般是由⽚外晶振产⽣的。

定义基准时钟的原因是其他⽣成时钟和时序约束通常都以基准时钟为参照。

很明显,在DAC7512控制器中,CLK_IN是基准时钟。

FPGAverilog课程设计报告

FPGA verilog课程设计报告一、教学目标本课程旨在通过FPGA Verilog的学习,让学生掌握数字电路设计的基本原理和方法,学会使用Verilog硬件描述语言进行数字电路设计和仿真。

具体目标如下:1.理解FPGA的基本原理和结构。

2.掌握Verilog语言的基本语法和编程技巧。

3.熟悉数字电路的设计方法和流程。

4.能够使用Verilog语言编写简单的数字电路模块。

5.能够进行FPGA的配置和编程。

6.能够使用FPGA开发工具进行数字电路的仿真和测试。

情感态度价值观目标:1.培养学生的创新意识和团队合作精神。

2.增强学生对新技术的敏感性和学习兴趣。

3.培养学生对工程实践的热爱和责任感。

二、教学内容本课程的教学内容主要包括FPGA的基本原理和结构、Verilog语言的基本语法和编程技巧、数字电路的设计方法和流程。

具体安排如下:第1-2课时:FPGA的基本原理和结构1.FPGA的定义和发展历程。

2.FPGA的内部结构和组成。

3.FPGA的配置和编程方法。

第3-4课时:Verilog语言的基本语法和编程技巧1.Verilog语言的基本数据类型和操作符。

2.Verilog语言的逻辑表达式和语句。

3.Verilog语言的模块结构和参数传递。

第5-6课时:数字电路的设计方法和流程1.数字电路的设计原则和技巧。

2.数字电路的设计流程和步骤。

3.数字电路的仿真和测试方法。

三、教学方法本课程采用讲授法、案例分析法和实验法相结合的教学方法。

1.讲授法:通过讲解和演示,让学生掌握FPGA和Verilog的基本知识和技巧。

2.案例分析法:通过分析具体的数字电路设计案例,让学生熟悉设计方法和流程。

3.实验法:通过动手实验,让学生亲手配置FPGA、编写Verilog代码并进行仿真测试,提高学生的实际操作能力。

四、教学资源1.教材:《FPGA Verilog设计与实践》。

2.参考书:《数字电路与FPGA设计入门》、《Verilog HDL入门与提高》。

基于FPGA的风电机组振动监测系统设计

基于FPGA的风电机组振动监测系统设计龙磊;邓艾东【摘要】通过监测传动系统的振动状态,能够有效诊断机组的运行故障.设计了一种以ARM为主控制器、FPGA为从控制器的风电机组振动监测系统.提出了系统的总体设计方案,介绍了振动信号预处理流程,重点阐述了FPGA模块的设计方法,详细介绍了数字倍频器的设计流程.该系统可接入不同类型传感器,根据传感器类型自动选择预处理电路,实现了8通道信号同步采样.FPGA主要用于实现振动信号滤波、A/D转换、数据存取、片选及逻辑控制等功能.利用FPGA的高速数据处理能力,实现了振动信号的全自动采集;通过转速的变化,实现了滤波中心频率与A/D转换速率的自适应.FPGA与ARM之间采用增强型直接内存存取(EDMA)方式进行数据传输,底层软件设计平台采用Linux操作系统,主要完成数据采集、与上位机通信等功能.该监控系统信号处理能力强、数据传输速度快,实现了风电机组振动状态的实时监测.【期刊名称】《自动化仪表》【年(卷),期】2018(039)002【总页数】4页(P29-32)【关键词】新能源;风电;FPGA;ARM;数字倍频器;振动监测【作者】龙磊;邓艾东【作者单位】东南大学火电机组振动国家工程研究中心,江苏南京 210096;东南大学火电机组振动国家工程研究中心,江苏南京 210096【正文语种】中文【中图分类】TH-39;TP274.20 引言风力发电机组单机容量向兆瓦级以上的发展,对风力发电设备的可靠性和安全性提出了更高的要求。

大型风电机组工作环境恶劣,风机传动系统故障率高。

目前,通常采用定期检修方式对其进行维护。

但由于机组自带的运行监控设备不足,很难准确掌握风电机组传动系统的运行状况。

这往往导致系统部件发生损坏时无法及时排除故障,大大降低了设备的利用率[1-2]。

振动信号在众多特征信息中能够有效判断风机传动系统的运行状态[3-5]。

配备完善的振动状态监测系统,对于及时发现传动系统故障、合理安排检修及提高机组的经济效益具有重要意义。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA设计中DAC7512控制的Verilog实现

一,概述

DAC7512是一个12-BIT,串行接口的DAC。

低功耗,RAIL-TO-RAIL输出,SOT23-6封装。

3线串行端口最高工作频率可以达到30MHZ,并兼容SPI,QSPI,MICROWIRE等总线。

DAC7512没有专用的基准电压输入,直接把VDD和GND作为基准电压,12BIT的分辨率,其输出电压为VOUT = VDD * D/4096。

其中D是12BIT电压数值。

SOT23-6封装的DAC7512的引脚图如下。

DAC7512具有3线串行端口,其信号定义如下所示:

对DAC7512来讲,在总线上只会接收控制器发出的16BIT的数字信号(2BIT 无效数据,2bit控制数据和12bit(信号幅值数据)。

所以对于控制器来讲,在总线操作上,只需要串行写这一种操作。

总线串行写操作在SYNC的下降沿开始。

16 bit的数据在SCLK的下降沿被依次送入到DAC7512内部的移位寄存器中。

从功耗的角度上讲,如果SYNC在空闲状态保持低电平,则有利于功耗的降低,但从总线操作的角度上讲,需要SYNC的下降沿来启动一次传输。

下面的图和表是总线操作的时序要求:

二,总线控制器的设计

根据总线控制器的特性,采用状态机来实现总线控制器的设计。

从上面DAC7512的操作时序上来看,用一个三状态的状态机实现总线控制器是比较好的选择。

在系统初始化或者没有数据传输时,系统处于空闲状态(DAC_IDLE),为了降低功耗,在这个状态下,SYNC信号为低电平;当有数据需要传输时,先进入DAC_PRE状态,在这个状态下,使SYNC信号为高电平,DAC_PRE状态保持的时间最短为SYNC需要保持为高电平的时间,即上图的T8,在VDD为3.6V~5.5V的时候,为33ns;当DAC_PRE状态结束时,进入DAC_DATA状态,在这个状态下,依次把16bit数据送到总线上去。

下图是状态机状态转换图。

系统初始化或者数据传输结束时,进入

DAC_IDLE状态。

当有数据需要传输时,进入DAC_PRE状态。

在DAC_PRE状态保持的时间,根据SYNC保持高电平的时间来决定,采用一个计数器来实现保持时间。

系统进入DAC_DATA时,开始传输数据,当16bit数据全部传输完毕后,系统回归到IDLE状态。

DAC_DATA状态下,送往总线的数据由计数器来控制,DAC_DATA状态保持的时间也由计数器控制。

由于总线上,数据在SCLK的下降沿被DAC7512锁存,所以控制器需要在SCLK的下降沿之前把数据送到总线上,并且要保证数据SETUP TIME的要求。

为了便于控制,我们采用一个比SCLK的频率高一倍,且相位相同的时钟(CLK_IN)来控制总线上数据的转换。

DAC_DATA状态计数器也工作在这个时钟频率下。

下面是状态机部分的verilog实现:

reg DA_SCLK; //串口时钟,由CLK_IN二分频得到,本例中CLK_IN为50MHz 时钟,DA_SCLK为25MHz

always @(posedge CLK_IN or negedge RESET)

begin

if(~RESET)

DA_SCLK <= 1'b0;

else

DA_SCLK <= ~DA_SCLK;

end

parameter DAC_IDLE = 3'b001, //系统空闲

DAC_PRE = 3'b010, //系统数据预传输状态

DAC_DATA = 3'b100; //系统数据传输状态

reg [2:0] DACSM, DACSMNXT;

wire PHASE_DAC_IDLE = DACSM[0];

wire PHASE_DAC_PRE = DACSM[1];

wire PHASE_DAC_DATA = DACSM[2];

wire PHASENXT_DAC_IDLE = DACSMNXT[0];

wire PHASENXT_DAC_PRE = DACSMNXT[1];

wire PHASENXT_DAC_DATA = DACSMNXT[2];

reg [2:0] DAC_PRE_CNT; //系统预传输保持时间计数器,工作在CLK_IN时钟频率下,生成的DAC_PRE_END信号作为状态机跳转信号。

always @(posedge CLK_IN or negedge RESET)

begin

if(~RESET)

DAC_PRE_CNT <= 3'b0;

else if(PHASE_DAC_PRE)

DAC_PRE_CNT <= DAC_PRE_CNT + 3'b1;

else

DAC_PRE_CNT <= 3'b0;

end

wire DAC_PRE_END = (DAC_PRE_CNT >= 3'b110);

reg [7:0] DAC_DATA_CNT; //DAC_DATA状态计数器,工作在CLK_IN时钟频率下,是总线上数据传输频率的两倍,所以在需要传输16bit数据的时候,该时钟需要计数到32。

always @(posedge CLK_IN or negedge RESET)

begin

if(~RESET)

DAC_DATA_CNT <= 8'b0;

else if(DAC_DATA_CNT == 8'd32)

DAC_DATA_CNT <= 8'd0;

else if(PHASENXT_DAC_DATA | PHASE_DAC_DATA)

DAC_DATA_CNT <= DAC_DATA_CNT + 8'b1;

else

DAC_DATA_CNT <= 8'b0;

end

wire DAC_DATA_END; //数据传输结束信号

assign DAC_DATA_END = (DAC_DATA_CNT >= 8'd31);

always @(posedge DA_SCLK or negedge RESET)

begin

if(~RESET)

DACSM <= DAC_IDLE;

else

DACSM <= DACSMNXT;

end

always @(DACSM or DA_DATA_EN or DAC_PRE_END or DAC_DATA_END) begin

DACSMNXT = DACSM;

case(DACSM)

DAC_IDLE:

if(DA_DATA_EN)

DACSMNXT = DAC_PRE;

else

DACSMNXT = DAC_IDLE;

DAC_PRE:

if(DAC_PRE_END)

DACSMNXT = DAC_DATA;

else

DACSMNXT = DAC_PRE;

DAC_DATA:

if(DAC_DATA_END)

DACSMNXT = DAC_IDLE;

else

DACSMNXT = DAC_DATA;

default:

DACSMNXT = DAC_IDLE;

endcase

end

按之前的讨论,SYNC信号在DAC_IDLE和DAC_DATA状态下,都为低电平,在DAC_PRE状态下,为高电平。

所以,用下面的逻辑生成SYNC信号。

assign DA_SYNC = PHASE_DAC_IDLE ? 1'b0: ( PHASE_DAC_PRE ? 1'b1 : (PHASE_DAC_DATA ? 1'b0 : 1'b1) );

通过一个12bit的端口向控制器写入需要送到DAC7312的数据

(DA_DATA),用一个使能信号(DA_DATA_EN)表示DA_DATA是否有效。

同时DA_DATA_EN也作为系统有数据传输的开始信号。

当DA_DATA_EN有效时,我们将DA_DATA上的数据所存到寄存器中,然后在DAC_DATA的状态下,依次将16bit数据送到总线上,verilog的逻辑实现如下所示。

wire DA_DIN;

reg [15:0] DA_DATA_CP;

always @(posedge CLK_IN or negedge RESET)

begin

if(~RESET)

DA_DATA_CP <= 16'b0;

else if(DA_DATA_EN)

DA_DATA_CP <= {4'b0, DA_DATA};

else if((PHASENXT_DAC_DATA & ~PHASE_DAC_DATA) |

( PHASE_DAC_DATA & DAC_DATA_CNT[0] == 1'b1))

DA_DATA_CP <= {DA_DATA_CP[14:0], DA_DATA_CP[15] };

else

DA_DATA_CP <= DA_DATA_CP;

end

assign DA_DIN = DA_DATA_CP[15] & PHASE_DAC_DATA;

采用CLK_IN来控制数据的输出,便于做STA的分析,也更容易满足系统的时序要求。

至于时序约束方面的内容,会在后面的文章中给出。