debussy和modelsim协同仿真(VHDL)

基于modelsim和debussy的批处理仿真

基于modelsim和debussy的批处理仿真本文将会叙述采用批处理的方法进行modelsim结合debussy仿真调试。

目的在于提高仿真效率。

该流程只适用于FPGA的前仿真,使用verilog文件以及测试文件。

如此操作有以下几个优点:1、虽然开始的时候需要稍作准备,但等你完成了一次仿真后,以后只需要略微修改一下就可以直接应用到其他工程里边去。

相对于采用用modelsim的界面操作,省去了很多例如创建工程、添加仿真文件、进行编译、进行仿真等等节省了宝贵的工作时间。

当然可以提高工作效率。

2、文件管理非常清楚。

所有的verilog文件都放在一个文件夹,所有仿真需要的文件以及仿真结果都放在另外一个文件里边,而且仿真后的文件也相对于使用modelsim界面操作仿真结果要少。

3、还有就是,因为没有界面操作,仿真速度会快很多,特别是采用modelsim进行稍微大的仿真的时候,这时候采用这种方法的优势就更加明显了。

以下是进行仿真前的准备工作第一步:安装modelsim、debussy软件以及编译相应的仿真库,如何安装以及破解,网络上有很多的资料说明,在这里就不详细说了。

对于仿真库的编译,也有很多的方法,可以参考文章《modelsim添加仿真库方法》by Craftor。

许多工程师也在自己的博客写过或转载过相似的库编译的方法。

这些都是我进行批处理仿真前已经做好了。

我的软件都是装在D盘分别是:D:\modeltech_6.5e和D:\Novas\Debussy第二步:创建do文件。

如下(行号不需要):1、vlib work2、vlog-f vfile.f-incr3、vsim-L xilinxcorelib_ver-L unisims_ver-L simprims_ver-L uni9000_ver-L unisims_ver-pli novas_fli.dll-lib work tuner_iic_tb4、run40ms5、exit然后保存为sim.do解析:1表示创建仿真工作库,也就是将你编译文件之后的文件存在这个work文件夹下。

VHDL仿真,Verilog_HDL仿真入门--ModelSim使用简介

VHDL仿真,Verilog_HDL仿真入门--ModelSim使用简介VHDL仿真,Verilog HDL仿真入门--ModelSim使用简介学硬件描述语言当然得实践,就得用软件仿真。

入门其实就是讲下仿真软件怎么用,是很简单的一件事,但是对于刚学的人来说可能有点无从下手。

我之前就有点迷茫,所以写这个入门当自己的笔记,也希望能给自学的新手有所帮助。

仿真VHDL和Verilog HDL并没有什么区别,一般的软件两种语言也都支持,仿真的步骤和方法也都是一样的。

常用的软件有Model Sim和Quartus II。

Quartus II功能很强大!实际的工作经常用它,它提供了功能仿真和时序仿真两种方式,但是作为学习HDL 并不方便,因为它compile编译的时候很慢,对于复杂的逻辑更是要很长时间。

好的一点是,Quartus II编译后可以清楚的看到它使用了芯片的多少资源,各信号不同的延时等等。

另外,Quartus II编译后也可以调用第三方的仿真工具,如Model Sim进行仿真。

而Model Sim只完成逻辑功能的仿真,并不考虑具体使用什么器件,学习HDL 或者设计逻辑的时候compile一次所用的时间很短,便于调试找出逻辑的错误。

所以初学仿真推荐使用Model Sim。

本文也只讲下用Model Sim仿真逻辑的方法。

以下部分基本是参照软件帮助简写的,只是原来是英文的而且说的比较繁琐一些,也更详细内容更多。

详见Model Sim菜单Help--SE PDFDocumentation--tutorial。

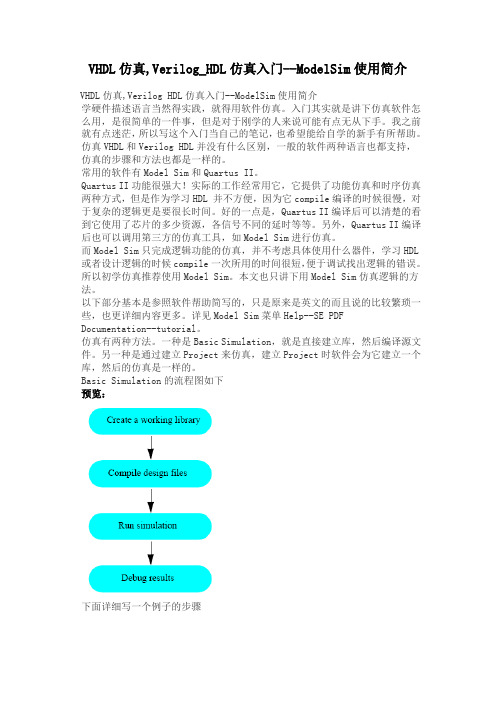

仿真有两种方法。

一种是Basic Simulation,就是直接建立库,然后编译源文件。

另一种是通过建立Project来仿真,建立Project时软件会为它建立一个库,然后的仿真是一样的。

Basic Simulation的流程图如下预览:下面详细写一个例子的步骤1. 建立库。

选择菜单File>New>Library。

如何使用debussy与modelsim做co-simulation(soc)(verilog)(vhdl)(debussy)(modelsim)

如何使用Debussy與ModelSim做Co-Simulation (SOC) (Verilog) (VHDL) (Debussy) (ModelSim) Abstract本文介紹如何使用Debussy與ModelSim做Co-Simulation,並使用Verilog、VHDL以及Verilog搭配VHDL交叉一起simulation。

Introduction使用環境:Debussy v9 + ModelSim SE我之前一直使用Debussy + NC-Verilog做simulation,Debussy (Verdi)可以說是HDL的Source Insight,是trace與debug的神兵利器,NC-Verilog也是Verilog simulator中速度最快的,可是最近因工作需要,拿到的一包code卻是用Verilog寫RTL,用VHDL寫testbench,所以必須2種語言一起做simulation,我在NC-Verilog一直無法成功讓兩種語言一起simulation。

ModelSim雖然支援Verilog + VHDL co-simulation,但用慣Debussy的我還是無法忘懷其方便的trace code方式,所以若能讓ModelSim也能dump出Debussy所需要的fsdb檔案,這樣就太完美了。

接下來會分4個方式討論與testbench皆使用Verilog與testbench皆使用VHDL使用VHDL,testbench使用Verilog使用Verilog,testbench使用VHDL與testbench皆使用VerilogStep 1:設定ModeSim使用Verilog PLI (因為testbench使用Verilog)將C:\Novas\Debussy\share\PLI\modelsim_pli\WINNT\複製到C:\\win32\下修改C:\\,將Veriuser部分修改成如下所示:; List of dynamically loaded objects for Verilog PLI applications; Veriuser =; use by verilogVeriuser =; use by vhdl; Veriuser =复制代码是個read only檔,要修改前記得修改其屬性才能存檔。

Debussy是一个VerilogVHDL调试工具

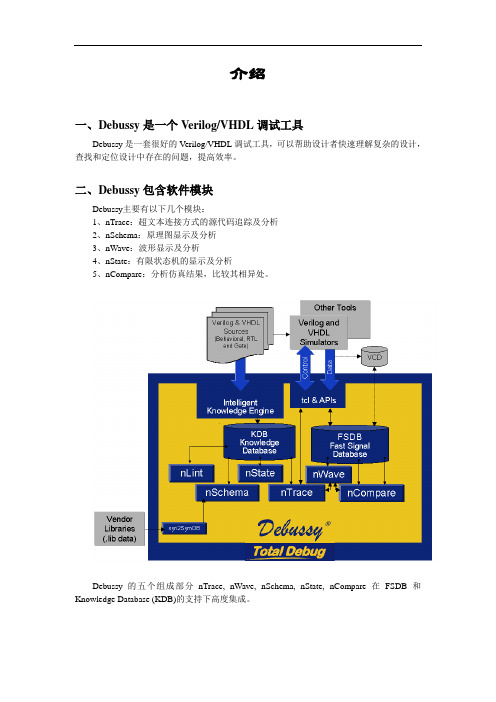

介绍一、Debussy是一个Verilog/VHDL调试工具Debussy是一套很好的Verilog/VHDL调试工具,可以帮助设计者快速理解复杂的设计,查找和定位设计中存在的问题,提高效率。

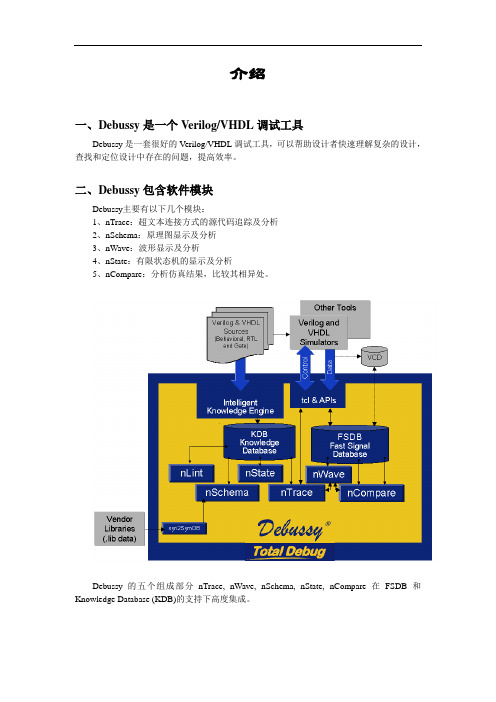

二、Debussy包含软件模块Debussy主要有以下几个模块:1、nTrace:超文本连接方式的源代码追踪及分析2、nSchema:原理图显示及分析3、nWave:波形显示及分析4、nState:有限状态机的显示及分析5、nCompare:分析仿真结果,比较其相异处。

Debussy的五个组成部分nTrace, nWave, nSchema, nState, nCompare在FSDB和Knowledge Database (KDB)的支持下高度集成。

三、Debussy功能Debussy直接编译Verilog/VHDL源代码,并且采用了预综合技术识别电路的单元,可以生成原理图。

在导入仿真结果后,可以用Active Annotation在源代码、原理图、状态图上动态显示变量的仿真值。

Debussy的输入为:Verilog/VHDL或混合语言源代码,仿真波形文件,SDF支持的波形格式:vcd,fsdb,模拟波形文件(PowerMill,TimeMill,Avant! Star-Sim,SmartSpice)支持的仿真器:VCS,Verilog-XL,NC-verilog,NC-VHDL,Modelsim,Leapfrog,Ploaris。

操作一、启动1. 启动%debussy启动debussy时,弹出一个nTrace窗口,包含三个子窗口:a、左边是Hierarchical Browser窗口,用来显示设计的层次(design hierachy)。

b、右边是Source Code window,显示源代码。

跟踪信号的驱动、负载。

c、底下是Message window(消息窗口),用来报告操作的结果。

2.导入设计File->Import DesignDebussy提供了两种导入设计的方法:A、从设计源文件直接导入B、从库导入(先将源文件编译成库)Note: 可以用命令的方式直接启动debussy并导入设计文件,即在命令行上列出所有的选项和源文件,或者把这些选项和源文件写到一个文件中,用-f选项指定这个文件。

debussy和modelsim协同仿真(VHDL)

debussy和modelsim协同仿真(VHDL)1、编辑modelsim根目录下的modelsim.ini文件,将; Veriuser = veriuser.sl 更换为Veriuser = novas_fli.dll。

2、将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas_fli.dll 拷贝至C:\Modeltech_6.1d\win32中3、将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas.vhd拷贝至工程所在目录4、打开modelsim,在工程所在目录新建一个novas的LIB,然后编译novas.vhd文件。

5、在testbentch中增加library novas;use novas.pkg.all;6、在testbentch中添加debussy_debug:processbeginfsdbDumpfile("**.fsdb");fsdbDumpvars(0,"顶层文件名(有testbench的话即为testbench名)");wait;end process debussy_debug;7、编译整个工程,然后仿真8、打开debussy, import design加载文件,设置好顶层文件,打开nWARE,加入信号即可为了更加方便的使用DEBUSSY,我们可以编写DO文件来达到这一目的:1、先新建dc16_tca目录。

比如在E:/WORK/TEMP里新建该目录,把源程序都放在dc16_tca/soure里头。

2、编写tca.do文件:下面是以TCA为例说明一下这个步骤:tca.do:#start#建立并编译novas库vlib novasvmap novas novasvcom -work novas D:/WORK/temp/dc16_TCA/source/novas.vhd#建立并编译work库vlib workvcom -work work d:/work/temp/dc16_tca/source/dc16_constant_def.vhdvcom -work work d:/work/temp/dc16_tca/source/dc16_tca.vhdvcom -work work d:/work/temp/dc16_tca/source/dc16_tca_tb.vhdvsim dc16_tca_tb#仿真运行时间run 10000usquit#end3、然后在dos界面先进入到dc16_tca目录里,比如E:/WORK/TEMP/dc16_tca然后再输入>c:\modeltech_6.1b\win32/vsim -c -do tca.do这里假设modelsim装在C盘个人感觉modelsim的仿真速度用DO文件的方式比用modelsim的GUI方式要快很多。

Debussy是一个VerilogVHDL调试工具

介绍一、Debussy是一个Verilog/VHDL调试工具Debussy是一套很好的Verilog/VHDL调试工具,可以帮助设计者快速理解复杂的设计,查找和定位设计中存在的问题,提高效率。

二、Debussy包含软件模块Debussy主要有以下几个模块:1、nTrace:超文本连接方式的源代码追踪及分析2、nSchema:原理图显示及分析3、nWave:波形显示及分析4、nState:有限状态机的显示及分析5、nCompare:分析仿真结果,比较其相异处。

Debussy的五个组成部分nTrace, nWave, nSchema, nState, nCompare在FSDB和Knowledge Database (KDB)的支持下高度集成。

三、Debussy功能Debussy直接编译Verilog/VHDL源代码,并且采用了预综合技术识别电路的单元,可以生成原理图。

在导入仿真结果后,可以用Active Annotation在源代码、原理图、状态图上动态显示变量的仿真值。

Debussy的输入为:Verilog/VHDL或混合语言源代码,仿真波形文件,SDF支持的波形格式:vcd,fsdb,模拟波形文件(PowerMill,TimeMill,Avant! Star-Sim,SmartSpice)支持的仿真器:VCS,Verilog-XL,NC-verilog,NC-VHDL,Modelsim,Leapfrog,Ploaris。

操作一、启动1. 启动%debussy启动debussy时,弹出一个nTrace窗口,包含三个子窗口:a、左边是Hierarchical Browser窗口,用来显示设计的层次(design hierachy)。

b、右边是Source Code window,显示源代码。

跟踪信号的驱动、负载。

c、底下是Message window(消息窗口),用来报告操作的结果。

2.导入设计File->Import DesignDebussy提供了两种导入设计的方法:A、从设计源文件直接导入B、从库导入(先将源文件编译成库)Note: 可以用命令的方式直接启动debussy并导入设计文件,即在命令行上列出所有的选项和源文件,或者把这些选项和源文件写到一个文件中,用-f选项指定这个文件。

EDK工程ModelSim仿真流程

EDK工程ModelSim仿真流程前期准备:1.已经安装软件工具:Xilinx ISE 11.1ModelSim 6.5Debussy5.4v92.EDK和ModelSim6.5联合仿真库设置完毕3.EDK和ModelSim6.5可以生成”.FSDB”文件,供Debussy波形查看器观察波形以参加电子设计竞赛的H.264工程为例,进行仿真演示。

1.首先确保工程simulation文件夹下没有文件。

2.如果有文件,要通过如下方式清除,不能直接删除。

3.清除后,点击Simulation Generate Simulation HDLFiles,重新生成工程仿真的库文件。

Console控制台显示生成了Simulation ModelSimulation文件夹下生成了一堆文件。

4.在Simulation文件夹下,找到“system_tb.v”文件,打开,添加如下语句initial begin$dumpfile("aa.fsdb");$dumpvars;end以便仿真时,生成fsdb文件。

5.返回XPS界面,选择Simulation->Launch HDL Simulator,通过这种方式,打开了ModelSim6.5软件6.打开了ModelSim6.5软件,如下图所示7.打开Simulation文件夹中的system_setup.do文件,该文件中存放了系统生成的仿真脚本语句。

8.返回ModelSim6.5,在命令行下先输入“do system.do”命令。

9.输入如下命令“vsim -novopt -t ps D:/modeltech_6.5/win32/novas.dll -Lxilinxcorelib_ver -L secureip -L unisims_ver +notimingchecks system_tb glbl”理由(复制system_setup.do文件中第二条脚本语句”vsim -novopt -t ps -L xilinxcorelib_ver -L secureip -L unisims_ver +notimingchecks system_tb glbl”,注意到要仿真生成fsdb波形文件,所以在ps和-L前添加一条新的语句”D:/modeltech_6.5/win32/novas.dll”,要链接这个“novas.dll”动态链接文件。

FPGA开发-使用modelsim和debussy做rtl仿真

1 引言

做 ASIC 或者 FPGA 设计中,选择合适的软件工具,对工作的开展有很大的帮助,一杆 利器,绝对可以使工作事半功倍。在 Windows 环境下做 rtl 开发(Verilog/VHDL),modelsim 是主流的仿真工具。Modelsim 虽然仿真速度快,功能强大。但是在调试查看波形时,便利 性远比不上 debussy。 或许大家对 debussy 有些陌生, 但是说到 linux 下被广泛使用的 verdi, 应该熟悉。Debussy 就是 verdi 的 Windows 版本,都是思源科技 NOVAS 开发的波形调试工 具,具有相同的源码。Debussy 和 verdi 具有相同的操作界面,熟悉 verdi 的工程师,使用 debussy 很容易上手。

图 6 Debussy 导入设计

4.

选中”From File”选项卡,然后在左下方的窗口中,按路径依次双击文件夹并打开, 找到 nv_lab1.f 的位置, 这时右下侧窗口显示出 nv_lab.f 文件, 双击该文件, 把 nv_lab.f 添加到了 Design Files 列表中,如图 7。然后点击 OK 按钮,则在 Debussy 中打开 了 lab1 的设计。

图 8 Debussy 中打开波形窗口

图 9 打开的波形窗口

6.

在波形窗口菜单栏,点击 File Open,在弹出的对话框中按路径找到 sim_top.fsdb 文件,双击,打开波性文件,如图 10 所示。

图 10 找到并打开波性文件

7.

查看信号波形。如图 11 所示,切换到 debussy 主界面,通过左边的导航栏,找到 想查看的文件并双击打开, 在文件中选中需要观察的信号, 可以按住鼠标左键拖动, 选中多个新号,选中后按 ctrl+w 键,把信号添加到波形窗口中。

matlab和modelsim联合仿真(一)

基于VerilogHDL语言的FPGA设计课程作业学院:电子工程学院专业班级:集电11级3班姓名:朱潮勇学号:05116079作业题目:Matlab和modelsim联合仿真(一)完成日期:2013年11月20日一、设计要求 (2)二、规范说明 (2)三、顶层设计结构图 (2)四、模块详细设计 (3)1 功能说明 (3)2 端口定义 (3)3 设计激励代码 (3)4 matlab代码 (5)5 仿真结果 (6)五、结论和问题: (8)六、补充:..................................................................................................... 错误!未定义书签。

一、设计要求虽然Modelsim的功能非常强大,仿真的波形可以以多种形式进行显示,但是当涉及到数字信号处理的算法的仿真验证的时候,则显得有点不足。

而进行数字信号处理是Matlab 的强项,不但有大量的关于数字信号处理的函数,而且图形显示功能也很强大,所以在做数字信号处理算法的FPGA验证的时候借助Matlab会大大加快算法验证的速度。

关于matlab与modelsim联合仿真有两种,一是以matlab或者modelsim分别产生数据,保存为文本的形式在给modelsim或matlab来调用。

这是一种间接的联合仿真的方式。

二是用matlab的link for modelsim的功能,将两者联合。

后者的联合仿真功能更加强大。

此次实验将进行第一种联合仿真。

分为两个例子。

第一个例子说明如何用Matlab产生的数据用作Modelsim仿真。

第二个例子说明如何用modelsim产生数据用作matlab进行分析。

二、规范说明1. Matlab产生数据用作Modelsim仿真首先利用matlab产生一个周期256点8bit的正弦波数据,然后以16进制形式写入sin.txt文件,然后将产生的sin.txt文件复制到Modelsim的工程下,在Verilog文件中先定义一个8bit X 256数组,然后通过$readmemh命令,将文件中的数据读入2. Matlab对Modelsim仿真生成的数据进行分析Matlab对Modelsim仿真生成数据的处理也是通过文件读写实现的。

VHDLQuartusII调用Modelsim进行仿真

VHDL ----- Quartus II(11.1版本)调用Modelsim进行仿真之前仿真一直是用Quartus II自带的“Vector Waveform File”,但因其功能有限,在老师的推荐下接触了Modelsim,捣腾了一段时间之后总算有所收获了。

在查资料的过程中,发现好多二者联合的讲解都是用Verilog语言写的例子,而VHDL很少。

以下是我总结的用VHDL 语言的具体步骤以及要注意的细节~~坎坷的路就略过了,直接展示成果。

例子是‘八位七段数码管的动态扫描显示’一.用Quartus II 进行VHDL语言编译1.首先建立工程File->New project Wizard(第三个图标)填入所建工程的目录以及名称,注意稍后的源程序中实体名必须和这里的名称相同。

填好后单击finish,然后单击yes。

2.新建VHDL源程序文件File->New->VHDL File->OK将程序写进去(这里只讲步骤,不讲源程序的写法)注意:程序中的实体名必须和之前建工程时所命名的文件名相同!然后保存一下,不用改动,直接单击保存。

3.编译快捷键按钮在界面中上方的红色倒三角,显示编译成功之后关闭编译报告。

4.设备设置具体的实验器件根据提供的实验板设定Assignment->Device4.引脚分配Assignment->Pin Planner在Location下的方格中填入对应的硬件引脚,也是根据实验板而定6.引脚分配好之后再次编译一下,使分配的引脚起作用。

一、调用Modelsim1、设置仿真工具为Modelsim-alteraTool->Options->EDA Tool Options,在Modelsim-Altera后面的地址改为Modelsim-Altera.exe在你电脑中的位置,然后点击OK。

2、写TestBench文件,这里使用Quartus II生成的模板Processing->start->Start TestBench Template Writer,显示成功后关闭生成报告。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1、编辑modelsim根目录下的modelsim.ini文件,将; Veriuser = veriuser.sl 更换为Veriuser = novas_fli.dll。

2、将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas_fli.dll 拷贝至

C:\Modeltech_6.1d\win32中

3、将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas.vhd拷贝至工程所在目录

4、打开modelsim,在工程所在目录新建一个novas的LIB,然后编译novas.vhd文件。

5、在testbentch中增加library novas;use novas.pkg.all;

6、在testbentch中添加

debussy_debug:process

begin

fsdbDumpfile("**.fsdb");

fsdbDumpvars(0,"顶层文件名(有testbench的话即为testbench名)");

wait;

end process debussy_debug;

7、编译整个工程,然后仿真

8、打开debussy, import design加载文件,设置好顶层文件,打开nWARE,加入信号即可为了更加方便的使用DEBUSSY,我们可以编写DO文件来达到这一目的:

1、先新建dc16_tca目录。

比如在E:/WORK/TEMP里新建该目录,把源程序都放在

dc16_tca/soure里头。

2、编写tca.do文件:

下面是以TCA为例说明一下这个步骤:

tca.do:

#start

#建立并编译novas库

vlib novas

vmap novas novas

vcom -work novas D:/WORK/temp/dc16_TCA/source/novas.vhd

#建立并编译work库

vlib work

vcom -work work d:/work/temp/dc16_tca/source/dc16_constant_def.vhd

vcom -work work d:/work/temp/dc16_tca/source/dc16_tca.vhd

vcom -work work d:/work/temp/dc16_tca/source/dc16_tca_tb.vhd

vsim dc16_tca_tb

#仿真运行时间

run 10000us

quit

#end

3、然后在dos界面先进入到dc16_tca目录里,比如E:/WORK/TEMP/dc16_tca

然后再输入>c:\modeltech_6.1b\win32/vsim -c -do tca.do

这里假设modelsim装在C盘

个人感觉modelsim的仿真速度用DO文件的方式比用modelsim的GUI方式要快很多。

而且每次只要输入一次命令就可以产生.FSDB文件,真的不错。

各位可以体会一下。

4、打开debussy再打开nWARE加入*.*.fedb文件即可看到波形大功告成!!。