图像采集系统的Camera Link标准接口设计

CameraLink协议和FPGA的数字图像信号源设计

CameraLink协议和FPGA的数字图像信号源设计关键字: FPGA Camera Link 标准 CMOS1 引言目前,各种图像设备已广泛应用到航空航天、军事、医疗等领域。

图像信号源作为地面图像采集装置测试系统中的一部分,其传输方式及信号精度都是影响系统性能的重要因素。

由于图像信号的传输速率高,数据量大,在传输过程中,其精度和传输距离易受影响。

为了提高信号传输距离和精度设计了由FPGA内部发出图像数据,并通过FPGA进行整体时序控制;输出接口信号转换成符合Camera Link标准的低电压差分信号(LVDS)进行传输。

该图像信号源已成功应用于某弹载记录器的地面测试台系统中。

2 Camera Link接口及图像数据接口信号Camera Link标准是由国家半导体实验室(National Semiconductor)提出的一种Channel Link技术标准发展而来的,该接口具有开放式的接口协议,使得不同厂家既能保持产品的差异性,又能互相兼容。

它在传统LVDS传输数据的基础上又加载了并转串发送器和串转并接收器,可在并行组合的单向链路、串行链路和点对点链路上,利用SER,DES(串行化,解串行化)技术以高达4.8 Gb,s的速度发送数据。

CameraLink标准使用每条链路需两根导线的LVDS传输技术。

驱动器接收28个单端数据信号和1个时钟信号,这些信号以7:1的比例被串行发送,也就是5对LVDS信号通道上分别传输4组LVDS数据流和1组LVDS时钟信号,即完成28位数据的同步传输只需5对线,而且在多通道66 MHz像素时钟频率下传输距离可达6 m。

Camera Link是在Channel Link的基础上增加了一些相机控制信号和串行通信信号,定义出标准的接头也就是标准化信号线,让Camera及影像卡的信号传输更简单化,同时提供基本架构(Base Configuration)、中阶架构(Medium Configuration)及完整架构(Full Configuration)三种:基本架构属单一Camera Link元件,为单一接头;中阶架构属双组Camera Link元件,为双组接头;完整架构属三组Camera Link元件,为三组接头。

基于Camera Link的串行图像采集系统设计

H T ik 号格 式 , 远 程 C D采 集 的 图像 信 号 进 行 串行 传 输 , F G 乒 乓 操 作 进 行 缓 存 , 过 C m r Ln O Ln 信 将 C 由 PA 通 a ea ik接 口 ,

将 图像数据 以 串行 方式高速传输至 图像 采集板卡 P I12 。实验 中以 10ls的速度连 续采集 18×10大 小的 串行 X一 8 4 5 o 2 3 LD V S图像或 5 0fs H T ik图像 , 0 的 O Ln p 最大传输速率达到 3 0Mb s 实验 结果表 明, a r i 2 p。 C meaLn k是 实现 高速 串行 图

第3 0卷 第 6期

21 0 0年 6月

计算机应 用

J u n lo o u e p ia in o r a fC mp t rAp l t s c o

VoI3 . _ 0 No 6

J n 01 u e2 0

文 章 编 号 :0 1 0 1 2 1 )6—10 0 10 —9 8 ( 0 0 0 7 1— 3

基 于 C m r ik的 串行 图像 采 集 系统 设 计 a eaLn

徐 志跃 , 田甜 张

( 北京航空航天大学 自动化科学与电气工程学院 ,北京 10 8 ) 00 3

(uhye sh .o ) xziu@ ou cr n

摘

要: 在设计测试 系统时 , 求 高速 、 靠地 传输 大量 的图像 信 息至 上位机 进 行存 储 和 处理。采 用 L D 要 可 V S或

h g pe d t r b rPXI1 28 t r ug me a Li i h s e o g a be 一 4 h o h Ca r nk.Theg a be a c iea ma e o 28 × 1 x l tas e d o 50 b rc n a qu r n i g f1 r 30 pies a p e f1

基于FPGA的CameraLink图像数据接口设计

㊀2020年㊀第9期仪表技术与传感器Instrument㊀Technique㊀and㊀Sensor2020㊀No.9㊀收稿日期:2019-07-16基于FPGA的CameraLink图像数据接口设计单彦虎,张晋顼,任勇峰,武慧军(中北大学电子测试技术国家重点实验室,山西太原㊀030051)㊀㊀摘要:依据航天测试领域对于图像采集系统中特定格式图像数据传输与处理的技术要求以及小型化低成本的设计要求,设计了一种基于FPGA的CameraLink图像数据接口㊂此接口选用可编程逻辑器件FPGA作为主控制芯片,通过编程FPGA代替接口转换芯片,实现CameraLink协议的LVDS信号在FPGA端口的直接接收,有效数据速率可达110MB/s㊂关键词:FPGA;CameraLink;LVDS;数据编帧;IP核;原语中图分类号:TH7㊀㊀㊀文献标识码:A㊀㊀㊀文章编号:1002-1841(2020)09-0051-04DesignofCameraLinkImageDataInterfaceBasedonFPGASHANYan⁃hu,ZHANGJin⁃xu,RENYong⁃feng,WUhui⁃jun(NationalKeyLaboratoryforElectronicMeasurementTechnology,NorthUniversityofChina,Taiyuan030051,China)Abstract:Accordingtothetechnicalrequirementsoftheaerospacetestfieldforthetransmissionandprocessingofimageda⁃tainaspecificformatinanimageacquisitionsystem,andthedesignrequirementsforminiaturizationandlowcost,anFPGA⁃basedCameraLinkimagedatainterfacewasdesigned.ThisinterfaceselectstheprogrammablelogicdeviceFPGAasthemaincon⁃trolchip,andreplacestheinterfaceconversionchipbyprogrammingFPGAtorealizethedirectreceptionoftheLVDSsignaloftheCameraLinkprotocolattheFPGAport,andtheeffectivedataratecanreach110MB/s.Keywords:FPGA;CameraLink;LVDS;dataframe;IPcore;primitive0㊀引言图像数据的采集与处理在航天测试领域中发挥着重要作用㊂CameraLink接口作为高速相机最主要的标准接口之一,它的出现使得高速图像源数据和图像采集装置之间的速度得到匹配㊂目前多采用串并转换芯片组成的多种驱动器和接收器来实现Camera⁃Link接口,通过CameraLink接口接收两路图像数据至少需要两块接口芯片,需要占据PCB较大的面积,由于FPGA需要接收28位并行数据所以占用了大量布线面积以及IO口资源,同时传输数据的速率也受转换芯片的限制㊂但是使用这种方法可以减小主控芯片对CameraLink接口数据的编解码压力,一定程度上降低了接口开发的难度㊂因此,这也是目前应用最广泛的CameraLink接口实现方法[1-3]㊂为了适应图像采集装置小型化低成本的开发要求,本设计提出采用CameraLink接口实现方案,在FPGA内部的SelectIOIP核源码的基础上,对IP核源码进行适当更改,实现了一种基于FPGA内部原语的CameraLink接口的实现方法[4],速率可达192MB/s,其中有效数据速率达110MB/s㊂1㊀设计方案1.1㊀总体方案本设计基于主控芯片FPGA,在不通过CameraLink串转并芯片的情况下直接接收带有编帧格式LVDS数据,完成更高速率㊁无误码的传输㊂数据流从FPGA的IO口到FIFO缓存的实现过程如图1所示㊂图1㊀图像数据流框图1.2㊀CameraLink接口接收端的FPGA实现CameraLink接口的数据传输基础就是低压差分信号(LVDS)形式传输㊂完整的CameraLink接口至少应该包含1对TX端和RX端(发送端和接收端)㊂发送端采用3.5mA的恒流源发送数据,在接收端口处差分端串接1个100Ω电阻,将电流形式的数据传输转换为低压差分电压㊂发送端通过改变电流流向控制接收端电压极性,从而控制接收端的逻辑 0 和 1 ㊂RX端接收5路LVDS信号,其中4路为串行数据流和㊀㊀㊀㊀㊀52㊀InstrumentTechniqueandSensorSep.2020㊀1路为专用串行时钟流㊂接收端的主要功能是将串行数据单端信号按照解串比为1ʒ7进行解串,将这5条LVDS信号还原为28路并行的单端数据信号以及1路伴随时钟的单端信号[5]㊂FPGA内含丰富的原语和专业IP核可以将FPGA的IO例化为多种形式的电平接口㊂例如本设计选用的主控芯片Spartan-6FPGA,通过配置它内部SelectIOIP核可以将FPGA的IO引脚匹配为差分引脚,并且通过设置IP核的一些基本参数就可以将5对差分对配置为符合CameraLink接口标准的电气接口㊂此设计通过调用FPGA内核,配置IO引脚为差分模式,实现CameraLink接口,用来接收发送端的5路LVDS信号㊂内部原理框图如图2所示㊂图2㊀FPGA内部串转并原理框图2㊀数据接收端控制逻辑2.1㊀约定数据格式本文采用图像标准卡作为图像数据源㊂标准卡基于PCI设计,此卡作用除了产生特定格式数据源外还包括后期数据的回读与回读数据的校验[6-7]㊂约定图像数据传输格式为1024ˑ1024如表1所示㊂数据源通过CameraLink接口并转串芯片按数据格式发送数据㊂表1㊀数据格式行序号(递增)行计数(2字)行标志(2字)模拟数据(1020字)10000EB903366EB903366102403FF146F33662.2㊀数据接收逻辑CameraLink标准规定将28位的数据信号中的4位用作同步信号,保证高速传输模式下数据能正确接收,这4位信号中有1位保留信号,其余3位信号定义为帧同步信号(FVAL)㊁行同步信号(LVAL)㊁数据有效信号(DVAL)㊂当发送新一帧数据时首先将FVAL拉高表示一帧数据即将发送,然后将LVAL拉高则表示相机要发送一行有效数据,当FVAL和LVAl同时为高后DVAL只要为高即表示有相机发送有效数据[8]㊂由于有效像素数据为16bit,设计的CameraLink接收模块解串出来的数据位28bit,因此需要剔除28bit数据中的无效数据位㊂CameraLink标准中规定3个PORT的像素数据信号与4bit使能信号与28bitTX端接口位映射关系如表2所示㊂28⁃bit数据位置映射如图3所示,其中 RxIOclk 为对像素时钟 RxCLKIN 的解码时钟,芯片内部根据该时钟对串行数据进行采样㊂同时根据CameraLink接口标准16bit像素数据占用PORTA和PORTB两个PORT,结合表2,接收的27位数据中的低16位即为16bit的有效像素数据,同时高3位为视频图像数据的同步信息位㊂图3㊀28⁃bit数据位置映射图表2㊀28⁃bitTX端口与PORT的映射依靠FVAL㊁LVAL㊁DVAL3个信号对数据图像数据进行接收㊂数据接收逻辑时钟采用55MHz,该时钟使用经BUFG输出的Gclk,数据在Gclk的上升沿由CameraLink接收模块输出,为了保证数据的准确性,数据接收模块在时钟Gclk的下降沿对数据进行接收㊂采用BUFPLL的LOCKOUT引脚作为数据接收模块的复位信号,当LOCKOUT输出为高时表示时钟已经同步㊂采用单位传输速率(signaldatarate,SDR)模式,在55MHz时钟下有效像素传输速率可达110MHz/s,㊀㊀㊀㊀㊀第9期单彦虎等:基于FPGA的CameraLink图像数据接口设计53㊀㊀图4为SDR模式下数据与时钟的对应关系㊂图5为数据接收模块接收一行数据的逻辑实现流程图㊂在进行数据接收时需要依靠行同步和帧同步信号,由图6可知当帧同步信号由低变高时表示数据新一幅图像开始传输,没有数据同步信号,当行同步信号由低变高的上升沿即开始新一行数据传输㊂接收到数据后需要对数据进行编帧便于数据存储和分析,根据设计需求如表3所示帧结构,其中帧头用于开始新一幅图像,帧计数用于计算图像幅数,数据校验和用来后期数据处理时校验每一幅图像中是否有误码丢数情况㊂图4㊀SDR模式时序图图5㊀数据接收流程图6㊀CameraLink接口时序需求表3㊀数据编帧结构帧头帧计数数据校验位C8BB0000数据校验和C8BB数据校验和C8BBFFFF数据校验和3㊀接口逻辑功能仿真本设计CameraLink数据接收采用SDR接收模式㊂当数据流的变化频率和对应时钟的变化频率相同时称为单倍传输速率(signaldatarate,SDR)模式,每个数据位均在时钟的上升沿(或者下降沿)时变化[9]㊂SDR模式下通过时钟的上升沿和下降沿可以比较精确的控制采样点落到数据保持时间的中部,逻辑实现相对复杂,对数据的建立时间要求较低㊂采用FPGA中的PLL和BUFPLL实现对像素时钟的倍频和同步㊂图2CameraLink接收端FPGA实现原理框图中像素时钟CLKpixel首先经过延时模块平衡掉7位数据深度的延时后输入PLL㊂PLL的只输出2个时钟信号,一个是对CLKpixel进行7倍频得到PLL_clk用于数据和时钟解串,另一个经BUFG后作为全局时钟Gclk㊂当PLL用于数据接收时必须使能反馈时钟CLKfb引脚,CLKfb是ISSERDES的时钟反馈引脚的输出时钟输出后经BUFIOFB原语转换后输入,这种机制可以保证进行倍频后的时钟PLL_clk和原始输入的时钟CLKpixel保持相位相同㊂为了便于分析,采用28Bit独热码作为数据源激励对Cameralink接口进行仿真㊂图7为仿真波形截图(没有执行PORT映射等操作)㊂根据仿真波形截图,容易分析出接口逻辑满足设计需求㊂图7㊀FPGA实现CameraLink接口接收端仿真波形图㊀㊀㊀㊀㊀54㊀InstrumentTechniqueandSensorSep.2020㊀4㊀试验验证测试时将标准卡安装在CPCI机箱上,模拟图像数据通过2m电缆发送至接收单元㊂作为图像数据源,标准卡按照表1通过DS90285芯片发送数据㊂接收数据后,读取并校验数据的准确性,发现数据出现误码㊂查看回读后的原始数据发现:数据行计数低二位数据容易出现错误(如图8行计数0C错接为0E)㊂考虑到数据衰减,改用0.4m电缆传输,数据没有出现误码㊂分析长线衰减程度:通过示波器抓取并比对发送端及接收端数据波形,接收端数据虽然衰减但仍然在LVDS信号协议可接受范围(250 450mV)(量取的接收端差分电压如表4所示),从而确定长线衰减不为主要原因㊂图8㊀数据错误示意图表4㊀接收端差分电压序号1234压差/mV262761479318㊀㊀在抓取接收端数据波形时发现有频率约为400kHz的干扰信号一直存在㊂考虑到是由于开关电源引起的干扰,量取DC/DC电源壳地间发现如图9所示干扰,从波形图中可以看出干扰峰峰值接近1.8V,频率大约为420kHz,从而定位干扰源为DC/DC电源㊂在DC/DC接壳引脚与信号地间串接103电容,削弱干扰㊂量取干扰源波形如图10,幅值被削弱㊂使用2m电缆测试,数据无误㊂验证了此次接口设计的可行性㊂图9㊀DC/DC电源壳地间干扰图10㊀削弱后的DC/DC电源壳地间干扰5㊀结论本次设计使用FPGA内部原语ISERDES和OS⁃ERDES实现了CameraLink接口数据的串并之间的相互转换,利用VHDL语言设计了数据接收逻辑和编帧逻辑㊂本设计基于FPGA的CameraLink接口在55MHz时钟下实现110MHz/s的数据接收㊂在FPGA的IO口短缺或是内部资源足够的情况下,完全可以使用原语编程代替串并转换芯片实现CameraLink接口数据的串并转换㊂参考文献:[1]㊀吴振锋.基于FPGA的CameraLink相机图像采集及处理技术研究[D].哈尔滨:哈尔滨工业大学,2013.[2]㊀韩魏.基于FPGA的一种CameraLink高速图像传输系统设计[D].西安:西安电子科技大学,2014.[3]㊀陈龙险.针对高速灰度相机的CameraLink接口电路设计研究[J].信息与电脑(理论版),2017(11):177-179.[4]㊀隋延林,何斌,张立国,等.基于FPGA的超高速CameraLink图像传输[J].吉林大学学报(工学版),2017,47(5):1634-1643.[5]㊀朱浩然.基于CAMERALINK接口的高速数据传输与存储系统[D].哈尔滨:哈尔滨工业大学,2014.[6]㊀兰功盾.基于FPGA的PCIe⁃CameraLink图像信号模拟源研究[D].哈尔滨:哈尔滨工业大学,2017.[7]㊀刘彪,王建立,吕耀文,等.基于FPGA的CameraLink输出编码设计[J].液晶与显示,2015,30(2):269-274.[8]㊀黄影.基于PCIe总线的CameraLink图像采集卡设计[D].大连:大连理工大学,2013.[9]㊀郭佳欣.基于LVDS的图像采集存储装置的设计与实现[D].太原:中北大学,2017.作者简介:单彦虎(1985 ),讲师,博士,主要研究方向为动态测试㊁微系统及集成技术㊁信号处理㊂E⁃mail:shanyanhu@126.com张晋顼(1994 ),硕士研究生,主要研究方向为动态测试㊁数据采编存储㊂E⁃mail:1531827537@qq.com。

3-CameraLink接口-时序控制

CameraLink接口

1.CameraLink接口简介

1.1CameraLink标准概述

CameraLink技术标准是基于NationalSemiconductor公司的ChannelLink标准发展而来的,而ChannelLink标准是一种多路并行LVDS传输接口标准。

低压差分信号(LVDS)是一种低摆幅的差分信号技术,电压摆幅在350mV左右,具有扰动小,跳变速率快的特点,在无失传输介质里的理论最大传输速率在1.923Gbps。

90年代美国国家半导体公司(NationalSemiconductor)为了找到平板显示技术的解决方案,开发了基于LVDS物理层平台的

如图

位

5路LVDS

恢复成

A、B 和C

口G和芯

E和H,

那么

H的8

从

中读取处FPGA DDR 包括2RAM 另外,

子模块来完成位宽的转换。

2.4modelsim仿真结果

图2.4modelsim仿真结果

如图2.4,被测FPGA每来一个行同步,CameraLink模块获取行地址后读取DDR2中的数据写入缓存模块,等到下一个行同步来的时候把所读的数据从缓存模块中输出。

实际要求的是每个行同步来后要读取一行数据,大小为2048x12bit,为了缩小仿真时间,仿真时没一行的数据长度为:80x12bit。

图2.5五路CameraLink仿真输出

如图2.5,当下个行同步来的时候缓存数据输出,输出的数据时连续的。

cameralink引脚定义

Camera Link连接器与电缆引脚定义发布时间:2010-2-10 来源:admin 阅读次数:3234Camera Link连接器与电缆引脚定义Channel Link 的高速速率传输使选择连接器和电缆这一环节变得非常重要。

必须严格依照Camera Link 标准中关于对连接器与电缆的引脚定义去设计相机和采集卡的相关连接信号。

1. 连接器连接器规定的制造商是 3M 公司,其规格化的 3M 26-pin MDR ( Mini D Ribbon )产品是 Channel Link 的标准连接器(如图3 所示),故而 Camera Link 标准的连接器也选择此型号。

图3 26-pin MDR 连接器当将这些连接器安装到一个相机或者图像采集卡上时要用到插槽(如图4 所示)。

插槽上的连接器固定螺母要与标准的 Camera Link 电缆连接器上的固定螺丝匹配。

图4 26-pin MDR 连接器插槽示意图2 .电缆3M 按照 Camera Link 标准设计了一种专门用于相机和图像采集卡之间的集成电缆。

这种双绞屏蔽电缆能够满足高速差分信号应用中的所有严格要求。

3M 电缆产品的通用型号为 14X23 —SZLB —XXX —OLC 。

它的有效长度在 1m 至 10m 之间。

另外,它有 2 种外壳可供选择。

关于电缆的选型参数说明如图5 所示。

本设计中采用的是 14B23 — SZLB — 200 — OLC ,即带固定螺丝的 2m 长电缆。

图5 3M 电缆产品选型说明图3 .连接器的引脚分布表4 给出了安装于相机或者图像采集卡上的 26-pin MDR 连接器的引脚定义。

表4 MDR-26 连接器引脚定义中级、完整配置模式基本配置模式(含控制与串行通信)相机端图像采集卡端Channel Link 信号电缆相机端图像采集卡端连接器Channel Link 信号1 1 Inner shield Inner shield 1 1 Inner shield 14 14 Inner shield Inner shield 14 14 Inner shield2 25 Y0- PAIR1- 2 25 X0-15 12 Y0+ PAIR1+ 15 12 X0+3 24 Y1- PAIR2- 3 24 X1-16 11 Y1+ PAIR2+ 16 11 X1+4 23 Y2- PAIR3- 4 23 X2-17 10 Y2+ PAIR3+ 17 10 X2+5 22 Yclk- PAIR4- 5 22 Xclk-18 9 Yclk+ PAIR4+ 18 9 Xclk+6 21 Y3- PAIR5- 6 21 X3-19 8 Y3+ PAIR5+ 19 8 X3+7 20 100Ω PAIR6+ 7 20 SerTC+20 7 Terminated PAIR6- 20 7 SerTC-8 19 Z0- PAIR7- 8 19 SerTFG-4 .屏蔽Camera Link 标准推荐连接器和电缆的内部屏蔽( Inner shield )与相机的数字地连接。

CameraLink图像采集接口电路1(2)详解

CameraLink 图像采集接口电路1.Camera Link标准概述Camera Link 技术标准是基于 National Semiconductor 公司的 Channel Link 标准发展而来的,而 Channel Link 标准是一种多路并行 LVDS 传输接口标准。

低压差分信号( LVDS )是一种低摆幅的差分信号技术,电压摆幅在 350mV 左右,具有扰动小,跳变速率快的特点,在无失传输介质里的理论最大传输速率在 1.923Gbps 。

90 年代美国国家半导体公司( National Semiconductor )为了找到平板显示技术的解决方案,开发了基于 LVDS 物理层平台的 Channel Link 技术。

此技术一诞生就被进行了扩展,用来作为新的通用视频数据传输技术使用。

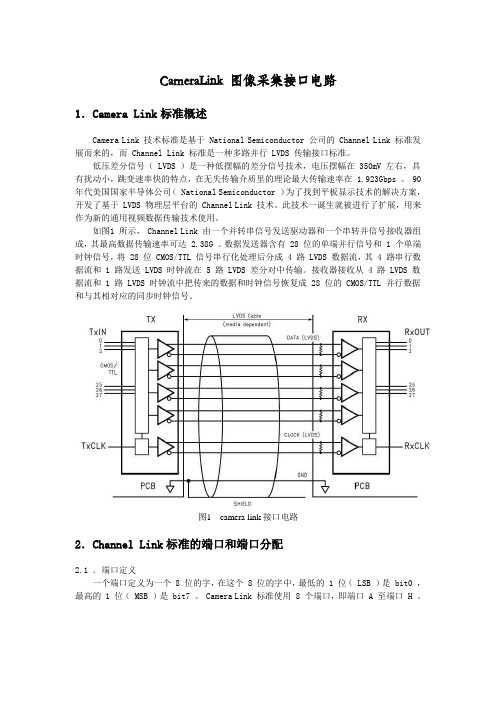

如图1 所示, Channel Link 由一个并转串信号发送驱动器和一个串转并信号接收器组成,其最高数据传输速率可达 2.38G 。

数据发送器含有 28 位的单端并行信号和 1 个单端时钟信号,将 28 位 CMOS/TTL 信号串行化处理后分成 4 路 LVDS 数据流,其 4 路串行数据流和 1 路发送 LVDS 时钟流在 5 路 LVDS 差分对中传输。

接收器接收从 4 路 LVDS 数据流和 1 路 LVDS 时钟流中把传来的数据和时钟信号恢复成 28 位的 CMOS/TTL 并行数据和与其相对应的同步时钟信号。

图1 camera link接口电路2.Channel Link标准的端口和端口分配2.1 .端口定义一个端口定义为一个 8 位的字,在这个 8 位的字中,最低的 1 位( LSB )是 bit0 ,最高的 1 位( MSB )是 bit7 。

Camera Link 标准使用 8 个端口,即端口 A 至端口 H 。

2.2 .端口分配在基本配置模式中,端口 A 、 B 和 C 被分配到唯一的 Camera Link 驱动器 / 接收器对上;在中级配置模式中,端口 D 、 E 和 F 被分配到第二个驱动器 / 接收器对上;在完整配置模式中,端口 A 、 B 和 C 被分配到第一个驱动器 / 接收器对上,端口 D 、 E 和 F 被分配到第二个驱动器 / 接收器对上,端口 G 和 H 被分配到第三个驱动器 / 接收器对上(见图2 )。

标准cameralink接口

标准cameralink接口Cameralink是一种数字接口标准,用于连接工业相机和数字信号处理器。

它提供了一种高速、可靠的方式来传输图像数据,适用于工业自动化、机器视觉和医疗成像等领域。

本文将介绍标准cameralink接口的基本原理、特点和应用。

1. 基本原理。

标准cameralink接口基于同步传输技术,采用了基于像素的并行数据传输方式。

它使用了三种不同的信号线,基础相机线、中继相机线和扩展相机线。

基础相机线用于传输图像数据、触发信号和相机控制信号,中继相机线用于传输额外的图像数据,扩展相机线用于传输高速图像数据。

通过这些信号线的组合,cameralink接口可以实现高速、稳定的图像数据传输。

2. 特点。

标准cameralink接口具有以下特点:高速传输,cameralink接口支持高达850MB/s的数据传输速率,能够满足工业相机对于高速图像采集的需求。

灵活性,cameralink接口可以支持不同分辨率、不同帧率的图像传输,适用于各种不同的应用场景。

可靠性,cameralink接口采用了差分信号传输技术,具有抗干扰能力强、传输稳定可靠的特点。

易于集成,cameralink接口标准化,各种厂家生产的工业相机和数字信号处理器都可以实现互操作性,方便用户进行系统集成。

3. 应用。

标准cameralink接口广泛应用于工业自动化、机器视觉和医疗成像等领域。

在工业自动化领域,cameralink接口可以实现高速、精准的图像采集和处理,用于产品质量检测、物体识别和测量等应用。

在机器视觉领域,cameralink接口可以实现高分辨率、高帧率的图像传输,用于无人驾驶、智能监控等应用。

在医疗成像领域,cameralink接口可以实现高清晰度、高对比度的图像传输,用于医学诊断、手术导航等应用。

总结。

标准cameralink接口是一种高速、可靠的数字接口标准,适用于工业相机和数字信号处理器之间的图像数据传输。

CameraLink接口数字相机图像显示装置解读

Camera Link接口数字相机图像显示装置(技术)摘要:由于目前基于CameraLink接口的各种相机都不能直接显示,因此本文基于Xilinx公司的Spartan3系列FPGA XC3S1000-6FG456I设计了一套实时显示系统,该系统可以在不通过系统机的情况下,完成对相机CameraLink信号的接收、缓存、读取并显示。

系统采用两片SDRAM作为帧缓存,将输入的CameraLink信号转换成帧频为75Hz,分辨率为1,024×768的XGA格式信号,并采用ADV7123JST芯片实现数模转换,将芯片输出的信号送到VGA接口,通过VGA显示器显示出来。

设计的系统可以应用于各种基于CameraLink接口的相机输出信号的实时显示。

关键词:CameraLink; FPGA; SDRAM控制器;实时显示Research on the Real-time Display Technology Based on CameraLinkAbstract: All cameras based on the CameraLink interface cannot be displayed directly at present. Therefore, we designed a real-time display system based on the Xilinx Spartan3 FPGA XC3S1000-6FG456I.Our system could receive, store, read and display the CameraLink signal without the system computer. Two SDRAMs were used as frame storage. Input CameraLink signal was converted to XGA signal with 1024×768 pixles/frame at 75 frame/s. The ADV7123JST was used as D/A convertor. Its output signal was transmitted to the VGA interface and displayed on the screen of the VGA monitor. Our system could display the output signal of all cameras based on the CameraLink interface.Keywords: CameraLink; FPGA; SDRAM controller; real-time display目录第一章绪论 (3)1.1 引言 (3)1.2数字图像处理的发展 (3)1.3 目的及意义 (4)1.4 国内外研究现状 (5)第2章视频显示原理和显示格式的转换算法综述 (7)2.1视频显示的原理 (7)2.2目前视频显示格式转换算法综述 (8)2.2.1图像尺寸变换的插值方法综述 (9)2.2.2每秒帧数变换方法综述 (11)2.2.3插值算法选择判断的原则 (11)第三章视频显示格式转换的插值算法方案 (11)3.1图像尺寸变换采用的算法方案 (12)3.2每秒帧数变换采用的算法方案 (14)3.3视频显示格式转换中的像素处理方案 (15)第四章实时显示系统装置 (17)4.1.实时显示系统总体设计 (17)4.2 FPGA概述 (18)4.3 Camera Link结构与原理 (20)4.4 SDRAM控制器设计 (22)4.5 VGA显示接口设计 (23)参考文献 (25)第一章绪论1.1 引言Cameralink相机以其可靠性高,稳定性好,独立性好和易用等优势,成为现阶段工业大分辨率数字相机的必配接口,相机LVDS信号由专业图像采集卡解码通过一台性能良好的计算机计算最后在计算机显示器上完成图像显示或在计算机硬盘上存储等后续数字图像处理操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图像采集系统的Camera Link标准接口设计

2009/9/24/10:20 来源:单片机与嵌入式系统作者:李天文赵磊

引言

高速数据采集系统可对相机采集得到的实时图像进行传输、实时处理,同时实现视频采集卡和计算机之间的通信。

系统连接相机的接口用的是Camera Link接口,通过Camera Link接口把实时图像高速传输到FPGA图像采集卡中进行数据实时处理,并通过PCI接口实现采集卡和计算机之间的通信。

本文主要研究数据采集系统 Cam-era Link接口技术。

Camera Link是专门为数字摄像机的数据传输提出的接口标准,是2000年10月由一些摄像头供应商和图像采集公司联合推出的。

Camera Link标准简化了计算机和摄像头之间的连接。

本设计选用Dalsa公司的DS-21-02M30相机,该相机支持Camera Link接口。

相机数据通过Camera Link接口传输到一块Altera公司的FPGAStratixII中进行处理。

在FPGA中进行数据的高速缓存,可以在FPGA

中设计各种图像处理程序对图像进行实时处理。

1 DS-21-02M30相机简介

DS-21-02M30相机可提供高灵敏度的8/10位图像。

为了同时获得卓越的分辨率和灰度级,DS-21-02M30相机图像分辨率为1 600×1 200,像素尺寸为7.4

μm×7.4 μm,像素数据输出时钟为40 MHz,最高帧频可达60帧/s。

通过设定像素数据格式命令,可以设定像素数据为8位、10位。

功耗低于15 W,供电电源电压为12~25 V。

通过异步串口向DS-21-02M30相机发送ASCII码控制命令和诊断命令,可以控制相机输出图像的增益、补偿、帧频、曝光时间、曝光模式和测试图像的输出,还可以对相机进行诊断。

串口协议:1位开始位,8位数据位,无奇偶校验位,1位停止位;通信波特率为9 600 bps(相机默认),通过设定波特率命令可将其设定为19 200 bps、57 600 bps和115 200 bps。

DS-21-02M30相机共有4种曝光模式,可以通过设定曝光模式命令来为相机选择合适的曝光模式。

模式2:内部触发方式(相机的默认曝光模式)。

帧频和曝光时间可用相应的命令控制。

模式3:最大曝光时间的外部触发方式。

模式4:外部触发方式。

帧频和曝光时间都由外部触发信号控制,即外部触发信号的高电平阶段为曝光时间,外部触发信号的频率为帧频。

模式6:外部触发方式控制帧频,曝光时间可用相应内部命令控制。

DS-21-02M30相机的命令以ASCII码的形式发

送。

向相机发送命令时,以回车符作为结束。

相机上电后,相机背后的指示灯闪烁,同时通过串口发送“CameraInitial ization in process,Please Wait…OK>”字符串。

当收到“OK>”字符串时,表明相机要开始传送图像数据,相机背后的指示灯不再闪烁。

当相机收到有效的命令时,会返回“OK>”字符串作为应答;否则,返回“Error x:Error Massage>”字符串作为应答。

其中,x

为错误标号,Error Massage表示对错误的具体说明。

相机的应答字符串以符号“>”作为结束符。

2 Camera Link结构与原理

Camera Link是专门为数字摄像机的数据传输提出的接口标准,专为数字相机制定的一种图像数据、视频数据控制信号及相机控制信号传输的总线接口,数据传输速率最高可达2.38 Gbps。

该标准规定了接口模式、相机信号、端口配置、图像数据位配置、连接器引脚定义及连接线、标准接收器芯片组。

采用这种标准后,使得数字摄像机的数据接口输出采用更少的线数,连接电缆更容易制造,更具有通用性,而且数据的传输距离比普通传输方式更远。

其最主要的特点是采用了LVDS(Low VoltageDifferential Signaling,低压差分信号)技术,使摄像机的数据传输速率大大提高。

在Careera Link标准出现之前,业界有一些标准(如较流行的IEEE-1394:接口)作为一种数据传输的技术标准。

IEEE-1394被应用到众多的领域,数字相机、摄像机等数字成像领域也有很广泛的应用。

IEEE-1394接口具有廉价,速度快,支持热拔插,数据传输速率可扩展,标准开放等特点。

但随着数字图像采集速度的提高、数据量的增大,原有的标准已无法满足需求。

为了简化数据的连接,实现高速、高精度、灵活、简单的连接,在 NationalSemiconductor公司开发的Channel Link总线技术基础上,由多家相机制造商共同制定推出了Camera Link 标准。

基于Camera Link的数字相机的采集速度和数据量均好于基于IEEE-1394标准。

Camera Link是一种基于物理层的LVDS的平面显示解决方案。

图1为Camera Link 总线发送端与接收端的连接框图,也是该总线的基本模式。

总线发送端,将28位并行数据转换为4对LVDS串行差分数据传送出去,还有一对LVDS 串行差分数据线用来传输图像数据输出同步时钟;而总线接收端,将串行差分数据转换成28位并行数据,同时转换出同步时钟。

这样不但减少了传输线的使用量,而且由于采用串行差分传输方式,还减少了传输过程中的电磁干扰。

3 高速数据采集卡Camera Link接口设计

高速数据采集系统的基本框图如图2所示。

FPGA给相机发出控制信号,相机中的数据通过Careera Link接口传送到图像采集卡;数据由FPGA读入,缓存在SDRAM中。

可以在FPGA中根据用户的需求实现高速的图像处理,根据图像处理的结果可以由 FPGA完成用户所需的控制。

图像采集卡通过PCI接口和计算机相连接,通过计算机可以配置图像采集卡和相机,计算机也可以从采集卡中获得图像处理数据。

接下来详细研究FPGA和相机间的Camera Link接口技术。

3.1 DS-21-02M30相机的Camera Link接口

Camela Link总线标准规定:在完整模式下,最多可以使用8个端口(Port A~Port H)传输数据,每个端口为8位数据。

DS-21-02M30相机使用Port A~Port C 端口,用的是基本模式(Base)。

相机后端有一个MDR26连接口,分别对应A、B、C三个端口各8位数据,加上FVAL、LVAL、DVAL和SP 四位数据控制信号,共28位并行数据位。

3.2 Camera Link接口的硬件设计

Camera Link的硬件连接框图如图3所示。

硬件电路包括3部分:相机通过MDR26连接图像采集卡;CameraLink接口的LVDS信号和CMOS信号转换电路;FPGA接收相机数据和发送控制部分。

为了对相机进行外部触发方式控制以及向相机发送命令,用四通道CMOS 信号转换为LVDS 差分信号的芯,片。

DS90LV047作为图像采集卡,向相机发送外同步触发信号和转换命令。

由于DS-21-02M30相机只用到CC1,FPGA 构成的图像采集卡,对相机的控制通过CC1和SerTC 信号实现。

为了接收相机向图像处理系统发送的应答字符串,选用DS90LV048芯片作为图像处理系统接收器。

DS90LV048芯片是四通道LVDS 差分信号转换为CMOS 信号的驱动器。

4 总 结

基于FPGA 的高速图像采集系统,通过Camera Link 接口和相机连接;从相机获得高分辨率的实时图像,并传输到FPGA 中进行实时图像处理并输出。

本文结合DS-21-02M30相机的基本功能,详细研究了Camera Link 接口技术,并给出了相机和高速图像采集卡之间CameraLink 接口设计,为正在研制的实时高速图像采集卡奠定了基础。