高速PCB板的电磁兼容设计

Hyperlynx

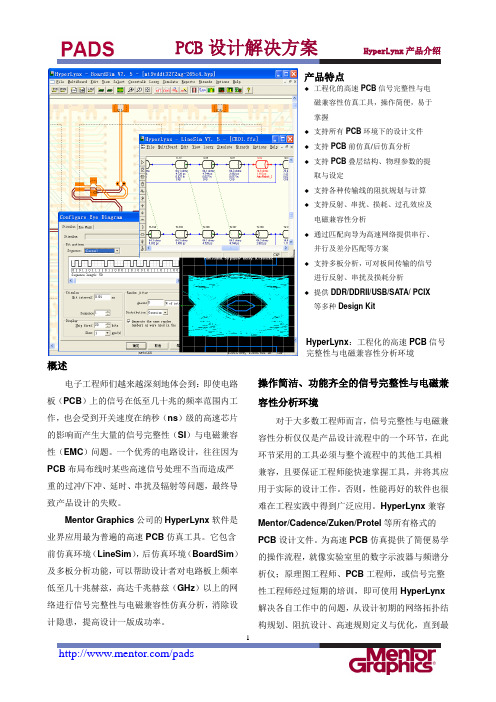

HyperLynx :工程化的高速PCB 信号完整性与电磁兼容性分析环境概述电子工程师们越来越深刻地体会到:即使电路板(PCB )上的信号在低至几十兆的频率范围内工作,也会受到开关速度在纳秒(ns )级的高速芯片的影响而产生大量的信号完整性(SI )与电磁兼容性(EMC )问题。

一个优秀的电路设计,往往因为PCB 布局布线时某些高速信号处理不当而造成严重的过冲/下冲、延时、串扰及辐射等问题,最终导致产品设计的失败。

Mentor Graphics 公司的HyperLynx 软件是 业界应用最为普遍的高速PCB 仿真工具。

它包含前仿真环境(LineSim ),后仿真环境(BoardSim ) 及多板分析功能,可以帮助设计者对电路板上频率低至几十兆赫兹,高达千兆赫兹(GHz)以上的网络进行信号完整性与电磁兼容性仿真分析,消除设 计隐患,提高设计一版成功率。

操作简洁、功能齐全的信号完整性与电磁兼容性分析环境对于大多数工程师而言,信号完整性与电磁兼容性分析仅仅是产品设计流程中的一个环节,在此环节采用的工具必须与整个流程中的其他工具相兼容,且要保证工程师能快速掌握工具,并将其应用于实际的设计工作。

否则,性能再好的软件也很难在工程实践中得到广泛应用。

HyperLynx 兼容Mentor/Cadence/Zuken/Protel 等所有格式的PCB 设计文件。

为高速PCB 仿真提供了简便易学的操作流程,就像实验室里的数字示波器与频谱分析仪;原理图工程师、PCB 工程师,或信号完整性工程师经过短期的培训,即可使用HyperLynx 解决各自工作中的问题,从设计初期的网络拓扑结构规划、阻抗设计、高速规则定义与优化,直到最产品特点◆工程化的高速PCB 信号完整性与电磁兼容性仿真工具,操作简便,易于掌握◆ 支持所有PCB 环境下的设计文件 ◆ 支持PCB 前仿真/后仿真分析 ◆支持PCB 叠层结构、物理参数的提取与设定◆ 支持各种传输线的阻抗规划与计算 ◆支持反射、串扰、损耗、过孔效应及电磁兼容性分析◆通过匹配向导为高速网络提供串行、并行及差分匹配等方案◆支持多板分析,可对板间传输的信号进行反射、串扰及损耗分析◆提供DDR/DDRII/USB/SA TA/ PCIX 等多种Design Kit终的板级验证等工作均可在HyperLynx中完成,可以有效地避免过度设计与设计反复。

高速PCB电磁兼容的研究

可 能 有 较 高 的 电 压 , 应 加 大 他 们 之 间 的 距 离 , 免 放 电 引 出 意 外 以

短 路 。

计 已 成 为 高 速 PC 设 计 中 急 待 解 B 决 的技 术难 题 。

( 2)某 些 元 器 件 或 导 线 之 间

系 到 电 子 设 备 质 量 的 好 坏 。 随 着 电 子 技 术 的 飞 速 发 展 , 电 子 产 品 越 来 越 趋 向 高 速 , 高 灵 敏 度 , 高 密 度 , 这 种 趋 势 导 致 了 P CB电 路 板 设 计 中 的 电 磁 兼 容 ( MC 和 电 E )

线之 间容 易 发生 串扰 , 且散 热性 而

( )综 合 考 虑 各 元 件 之 间 的 6 分 布 参 数 。 尽 可 能 使 元 器 件 平 行 排 列 , 这 样 不 仅 有 利 于 增 强 抗 干

扰 能 力 , 而 且 外 观 美 观 , 易 于 批

量生 产 。

能 不 好 。 确 定 P B 寸 之 后 , 就 可 C 尺 以 根 据 电 路 的 功 能 模 块 x- 部 器 ,全 j 件 进 行 布 局 。 高 速 P B 布 局 通 常 C 的

和 传 输 线 的 设 计 几 个 方 面 分 析 研 究 了 改 善 高 速 P B M 性 能 的 方 法 , 并 介 绍 了 其 它 的 一 些 抗 C E C

电磁干扰 技术 。

关 键 词 : 磁 兼 容 ; 速 P B 电 磁 干 扰 电 高 C; 中 图 分 类 号 :N 0 T7 1 文 献 标 识 码 : A 文 章 编 号 : 0 3 0 0 (0 7 0 - 0 2 0 10-1 72 0)B 09- 3

CLC um herTN7 i t = 01

电磁兼容中三大类PCB布线设计详解

电磁兼容中三大类PCB布线设计详解从电磁兼容的角度,我们需要对以下四种布线加以关注:A 强辐射信号线(高频、高速、时钟走线为代表)B 敏感信号(如复位信号)C 功率电源信号D 接口信号(模拟接口或数字通信接口)一、单双面布线设计1.在单层板中,电源走线附近必须有地线与其紧邻、平行走线。

减小电源电流回路面积,减小差模环路辐射。

2.电源走线单面板或双面板,电源线走线很长,每隔3000mil 对地加去耦电容(10uF +1000pF)。

滤除电源线上地高频噪声。

3.Guide Ground Line对于单、双层板,关键信号线两侧应该布“Guide GroundLine”。

关键信号线两侧地“包地线”一方面可以减小信号回路面积,另外还可以防止信号与其他信号线之间的串扰。

4.回流设计在单层板或双层板中,布线时应该注意“回流面积最小化”设计,回路面积越小,回路对外辐射越小,并且搞干扰能力越强。

对于多层板来说,要求关键信号线有完整的信号回流,最后是GND 平面回流。

次重要信号有完整平面回流。

通过减小回路来防止信号串扰,同时降低对外的辐射。

5.直角走线PCB 走线不能有直角走线。

直角走线导致阻抗不连续,导致信号发射,从而产生振铃或过冲,形成强烈的EMI 辐射。

6.PCB走线粗细应一致。

粗细不一致时,走线阻抗突变,导致信号反射,从而产生振铃或过冲,形成强烈的EMI 辐射。

7.相邻布线层注意在分层设计时,应避免布线层相邻。

如果无法避免,应适当拉大两布线层上的平行信号走线会导致信号串扰。

线层之间的层间距,缩小布线层与其信号回路之间的层间距,布线层1与布线层2不宜相邻。

相邻布尽可能避免相邻布线层的层设置,无法避免时,尽量使两布线层中的走线相互垂直或平行走线长度小于1000mil ,这样减小平行走线之间的串扰。

PCB的板级电磁兼容问题

PCB的板级电磁兼容问题一、(芯片)(集成电路)现状现阶段,(电子)系统正向高速化和高密度化飞跃发展。

在电子系统的设计过程中,系统的体积越来越小,IC引脚(in(te)grated circuit,集成电路)却越来越多,因此(PCB)(Printed Circuit Board,印制电路板)上的元件与布线越来越密集;与此同时,(信号)的(时钟)频率越来越大,并且信号上升沿越来越陡峭。

这些因素都导致了电磁环境的日益复杂,设备之间以及设备内部因互感和互容引发的种种(电磁兼容)问题已不容忽视。

这一问题在现今的强辐射源与高功率(微波)系统中也显得日益突出。

如在某高功率微波系统中,需要在限定的体积和尺寸下,采用(FPGA)芯片实现对多路(电机)的并行控制,就需要设计高速高密度的PCB。

本文就研究该情况下PCB的板级电磁兼容问题,主要包括信号完整性(Signal Integrity, SI)和(电源)完整性(PowerIntegrity,PD问题。

二、信号完整性及电源完整性问题信号完整性概括地说,是指信号在信号线上传输质量的好坏。

在(数字电路)中,体现在信号能在电路中能以正确的电压、带宽和时序做出响应。

若在PCB中,信号可以以正确的电压大小、带宽和时序都到达接收端,就能说明该PCB具有较好的信号完整性。

如果不能,则说明PCB中岀现了严重的信号完整性问题。

在高速高密度的数字电路中,信号完整性问题大致表现在一下几个方面:振铃、过冲、欠冲和时延等。

为了正确读取数据并对数据进行处理,数据在集成电路中需要在时钟边沿的前后处于稳定状态。

这个时间段内,如果信号不稳定或者发生状态的改变,集成电路就可能误判甚至发生丢失部分数据的情况,影响信号的正常传输。

如图1所示,若岀现振铃、上冲或下冲等信号完整性问题,就会影响数据的正常传输,从而影响PCB的正常工作,也可以从眼图直观判断信号传输的好坏,如图2图1PCB中信号完整性问题的表现图2 表征信号完整性问题的眼图信号完整性问题既会导致信号明显的失真和时序混乱,也会造成数据的错误,从而造成系统出错甚至瘫痪。

高速pcb设计注意事项

高速pcb设计注意事项

1. 确定信号层之间适当的间距,以避免串扰和交叉干扰。

2. 选择合适的PCB 材料和厚度,在考虑信号完整性和散热的情况下进行权衡。

3. 尽可能地减小电路板上的回流焊盘和贴片元件之间的距离。

4. 仔细规划电源和信号地面,保证良好的接地和电流分布。

5. 在PCB 设计过程中使用模拟和数字仿真工具来确保信号完整性。

6. 使用独立的点对点连接来减少多层PCB 堆叠中的交叉干扰。

7. 尽可能避免倒角和锐角,并确保尽可能平滑的布线。

8. 做好EMI/EMC 电磁兼容设计,遵循相关国际标准。

9. 在PCB 较大时,在焊盘附近添加焊点来保持稳定连接。

10. 验证PCB 布线是否正确,并遵循相关图像制造指南。

高速电路板的设计方法介绍

高速电路板的设计方法介绍高速电路板的设计方法介绍一、引言高速电路板的设计是现代电子设备设计中的一个重要环节。

随着数字通信、计算机网络和移动通信的迅猛发展,高速电路板的需求也越来越迫切。

在高速电路板设计过程中,如何保证信号传输的稳定性和可靠性是一个非常重要的问题。

本文将介绍一些高速电路板的设计方法,以帮助读者更好地进行高速电路板设计。

二、高速电路板的特点高速电路板的特点是信号频率高、传输速度快、信号波形陡峭。

这些特点造成了以下几个问题:1. 信号完整性:由于信号传输速度快,信号波形陡峭,会导致信号完整性问题,例如信号的反射、串扰、时钟抖动等。

这些问题都会影响信号的传输稳定性,因此需要采取一系列措施来解决。

2. 电磁兼容性:高速电路板上的信号传输往往伴随着电磁辐射和敏感度,因此需要采取一系列电磁屏蔽和抑制方法来保证电磁兼容性。

3. 导线长度和走线布局:在高速电路板设计中,导线长度和走线布局的合理安排对信号传输有很大的影响。

合理的布局可以减小信号传输的延迟和串扰,保证信号的传输稳定性。

三、高速电路板设计的方法1. 信号完整性设计方法:(1)端口匹配:由于高速信号传输速度快,对于驱动输出和接收输入端口的匹配非常重要。

可以通过匹配控制阻抗和使用差分信号传输等方式来提高信号完整性。

(2)布线规则:在布线过程中,需要考虑信号线的走向、长度和层次。

可以采用等长电平、分层布线、减小串扰等方法来提高信号完整性。

(3)控制信号源:信号源的波形和电平控制也是保证信号完整性的重要因素。

需要通过合理的设计来减小信号的反射和串扰。

2. 电磁兼容性设计方法:(1)屏蔽和抑制:可以通过采用屏蔽盒、层间屏蔽、电磁屏蔽材料等方式来减小电磁辐射。

同时,还可以采用电源捶击器、衰减器等抑制器件来减小敏感度。

(2)地线设计:地线是高速电路板设计中的一个重要因素,合理的地线设计能减小电流回路的环路面积,降低电磁辐射。

(3)滤波器设计:可以在高速电路板上增加一些滤波器来减小电磁辐射和敏感度。

PCB电磁兼容性的设计和相关注意事项

。机械 与电子 o

S IN E&T C NO O F MA I CE C E H L GYI OR TON N

21 0 1年

第 1 期 7

P B电磁兼容性的设计和相关注意事项 C

赵 英 ( 龙 江 斯 福 电 气 有 限 公 司 黑 龙 江 黑

【 摘

哈尔 滨

100 ) 5兼 容 问题 C

P B设 计 中 常 见 的 电 磁 干扰 C

路板上 : 6 D /C变 换 器 、开 关 元 件 和 整 流 器 应尽 可 能靠 近 变压 器 放 置 , ) CD

以使 其 导 线 长 度 最 小 : P B设 计 中 的 电磁 兼 容 问 题 , 先 应 该 了 解 P B 中各 种 电 磁 干 C 首 C, 7) 噪 声 敏感 的 布线 不 要 与 大 电流 , 速 开 关 线 平行 。 对 高 扰 的产 生 机 理 和传 播 途径 , 后 才 能 依 此 提 出相 应 的解 决 方 案 。通 常 33 多 层 板 设计 然 - P B 中存 在 的 电 磁 干 扰 有 : 导 干 扰 、 C , 传 串音 干 扰 以及 辐 射 干扰 。产 生 在 多 层 板 设计 中 电源 平 面应 靠 近 接 地 平 面 , 且 安 排 在 接 地 平 面 并 干 扰 的 根 源 是 电路 中 电压 或 电流 的 变 化 。 之 下 。 这样 可 以利 用 两 金 属 平 板 问 的 电 容 作 电 源 的平 滑 电容 , 同时 接 21 传 导 干 扰 . 地 平 面 还对 电 源平 面上 分 布 的辐 射 电流 起 到 屏 蔽 作 用 ; 了产 生 通 量 为 传 导 干扰 主要 通 过 导 线 耦 合 及 共模 阻 抗耦 合来 影 响其 它 电路 。 例 对 消作 用 布 线 层 应 安 排 与 整 块 金 属 平 面 相 邻 : 中 间 层 的 印 制 线 条 形 在 如 噪音 通 过 电源 电路 进 入 某 一 系 统 , 有使 用 该 电 源 的 电 路 就 会 受 到 成平 面 波 导 , 表 面 形 成 微 带 线 , 者 传 输 特 性 不 同 ;时 钟 电路 和 高 所 在 两 它 的 影 响 。 噪音 通 过 共 模 阻 抗 耦 合 的 。 电路 与 电 路 共 同 使 用 一 根 导 线 频 电路 是 主要 的干 扰 和 辐 射 源 , 一定 要 单 独 安 排 、 离 敏 感 电 路 ; 有 远 所 获取 电源 电压 和 接 地 回路 ,如果 其 中一 个 电路 的 电压 突 然需 要 升 高 , 的具 有 一 定 电 压 的 印制 板 都 会 向空 间辐 射 电 磁 能 量 ,为 减 小 这 个 效 那 么另 一 电路 必 将 因 为 共 用 电 源 以及 两 回路 之 间 的阻 抗 而 降 低 。 于 应 , 印制 板 的 物 理 尺 寸 都 应 该 比最 靠 近 的接 地 板 的物 理 尺 寸 小 2 H, 对 0 地 回路 也 是 如 此 。 其 中 H是 两个 印制 板 面 的间 距 。按 照 一 般 典 型 印 制 板 尺 寸 ,0 一 般 2H

《PCB电磁兼容设计》课件

合理的PCB布局与布线可以有效降低电磁干扰和提高设备的电磁敏感性。

03 PCB电磁兼容性设计方法

CHAPTER

接地设计

接地方式选择

根据电路需求选择合适的接地方式,如单点接地 、多点接地等。

接地线宽与长度

信号完整性设计

信号线宽与间距

根据信号速率和传输需求,合理设置信号线 的宽度和间距。

信号反射与串扰

通过优化信号端接方式和布局,减小信号反 射和串扰的影响。

信号完整性仿真

利用仿真工具对信号完整性进行评估和优化 。

屏蔽与滤波技术

屏蔽方式选择

根据电磁干扰源和敏感设备的特性,选择合适的屏蔽 方式。

滤波器设计

元器件的集成化程度越来越高, 导致PCB上电流和电压的急剧变 化,加剧了电磁干扰的产生。

接地设计复杂化

接地设计对于PCB电磁兼容性至 关重要,但随着电路的复杂化, 接地设计也变得越来越复杂,需 要综合考虑多种因素。

PCB电磁兼容性标准与规范

01

国际标准

如IEC 61000系列标准,主要涉 及电磁干扰的发射和敏感度要求 。

国际合作与标准化进展

国际合作

全球范围内的科研机构和企业正在加 强合作,共同研究和制定PCB电磁兼 容性的国际标准,推动行业的发展和 进步。

标准化进展

国际电工委员会(IEC)等标准化组织 正在制定和完善PCB电磁兼容性相关 的标准,这些标准将为PCB的设计、 生产和测试提供更加明确的指导。

未来研究方向与挑战

03

波、接地等。

电磁场与电路相互作用

电磁场与电路的相互作用是电 磁兼容性的核心问题之一。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

高速PCB 板的电磁兼容设计林 瑜,陈家能,陈贻焕,张 芳(海军航空工程学院 山东烟台 264001)摘 要:以某一嵌入式系统核心PCB 板设计为例,介绍了电磁兼容的基本概念及一些高速PCB 板设计的基本知识,着重分析了无高频器件时高速PCB 板设计中存在的电源系统干扰、地线噪声干扰和信号线间的串扰等电磁干扰,并分析了这些电磁干扰产生的主要原因,从PCB 总体设计和元器件布局、布线等方面考虑,对可能存在的这些干扰,提出了防止和抑制方法以及一些提高PCB 板电磁兼容性的具体措施;在工程实践中证明这些方法和措施有效可靠。

关键词:高速电路板;电磁兼容性;电磁干扰;PCB中图分类号:T P 211+15 文献标识码:B 文章编号:1004373X (2005)1511003D esign ofE M C for the H igh Speed C ircu it PCBL I N Yu ,CH EN J ianeng ,CH EN Y ihuan ,ZHAN G Fang(N aval A viati on Engineering Co llege ,Yantai ,264001,Ch ina )Abs tra c t :T ak ing one em bedded system as examp le ,th is paper introduces the basic concep ti on of electrom agnetic compatibility andelem entary know ledge of h igh speed circuit PCB design ;it analyzes the E M I such as pow er system interference ,GND no ise interferenceand interference of signal trans m issi on line w h ich exist in designing h igh speed circuit PCB w hen there are no h igh frequency devices ;then it analyzes the p ri m e reason of causing tho se E M I 1F rom view of w ho le design of PCB ,outline ,w iring and so on ,th is paper brings fo r w ard the m ethod of how to be sh ielded from interference and gives the specific m easure to i m p rove the E M C of circuit PCB ;all these m ethods p rove effective and reliable in p ractice 1Ke yw o rds :h igh speed circuit ;E M C ;E M I ;PCB收稿日期:20050428 印制电路板(PCB )是电子产品中电路元件工作的平台,他提供电路元件和器件之间的电气连接,他的性能直接关系到电子设备质量的好坏。

随着电子芯片技术的发展和电路集成度的提高,PCB 板上的元器件密度越来越高,系统工作速度越来越快。

高频电路的一些特性,使得PCB 板设计过程中电磁兼容性设计非常重要,他不仅关系到电路能否获得最佳性能,而且关系到电路系统能否正常稳定的工作。

本文以某一嵌入式系统的PCB 板设计为例,介绍一些高速PCB 电磁兼容设计方法。

1 高速PCB 板存在的电磁兼容问题111 系统简介该嵌入式系统是一手持式设备,处理器采用三星的S 3C 2410,经过芯片内的倍频电路将系统频率设为200M H z ,其核心板的电路结构如图1所示。

112 电磁兼容问题根据美国电气和电子工程师协会(IEEE )对电磁兼容性的定义,电磁兼容性是指电子设备在其所处的电磁环境中满意的工作,同时又不向该环境及同一环境中的其他装置排放超过允许范围的电磁扰动[1]。

电磁兼容性设计的目的是使电子设备既能抑制各种外来的干扰,使电子设备在特定的电磁环境中能够正常工作,同时又能减少电子设备本身对其他电子设备的电磁干扰。

图1 系统核心板的电路结构对此嵌入式系统的PCB 板而言,没有辐射电磁干扰的高频器件,可能存在的电磁干扰有以下3种:电源系统干扰 一是由于系统电源供能源的同时,也将其寄生的干扰噪声加到了供电电路上;二是由于一些高速逻辑电路工作时的高速转换,不可避免地在电源线上产生含高频分量丰富的压降并且产生干扰(辐射);三是由于温度变化时的直流干扰,使系统中的一些对高频噪声特别敏感的电路,特别是模拟信号电路很容易受到来自电源的噪声干扰。

地线的噪声干扰 一是地线存在阻抗,当电流流过地线时,会在地线上产生电压。

在这个电压的驱动下,会产生地线环路电流,形成地环路干扰;当2个或2个以上电路共用一段地线时,会形成公共阻抗耦合;二是频率高于一定值时,任何金属导线都要看成是由电阻、电感构成的器件,结果可能造成各部分地线的不平衡,在地线之间出现电位差,引起电路的误操作;如果引线长度适当,还会造成传导和辐射。

电子技术林 瑜等:高速PCB 板的电磁兼容设计信号传输线间的串扰[2] 由于传输信号的高频特性,各传输线路的特性阻抗的不同或与负载阻抗不匹配,所传输的信号在终端或临界部位会发生发射,使传输信号发生或产生振荡。

另外,传输线的走向、宽度、线间的间距的不合理设计,还会造成线间的信号叠加和附加延时,这些都可能造成信号传输线之间的串扰。

2 高速PCB板电磁兼容性设计PCB板有单面板(单层板)、双面板(双层板)和多层板之分。

单面板和双面板一般用于低、中密度布线的电路和集成度较低的电路,多层板使用高密度布线和集成度高的电路。

从电磁兼容的角度看单面板和双面板不适宜高速电路,多采用多层PCB板[3]。

本文中所设计的高速PCB采用6层板,4个信号层,1个电源层,1个地层;在多层板的设计中,应注意PCB的尺寸大小适中。

尺寸过大,成本高、布线长、阻抗增加、抗噪声能力下降;尺寸过小,PCB上元器件密度增加、散热不好、线条间距近,易相互干扰。

211 电源系统干扰的抑制为抑制干扰,在PCB总体设计上,采用电源层供电的方法,因为这样做,不但电源层的分布电阻较电源总线低,实际供电平稳,而且电源层可以作为噪声回路,降低干扰;同时电源层还为系统所有信号提供回路,消除公共阻抗耦合干扰。

在元器件布局和布线上采取以下措施:(1)将模拟与数字电源的电源分开。

高频器件一般对数字噪音非常敏感,所以两者要分开,在电源的入口处接在一起。

若信号要跨越模拟和数字两部分的话,可以在信号跨越处放置一条回路以减小环路面积。

(2)电源线尽可能与地线平行,同时使电源线、地线的走向与数据传输的方向一致,以提高电路的抗干扰能力。

电源线加粗,以减少环路电阻。

(3)在集成芯片的附近安装去耦电容。

在直流电源回路中,负载的变化会引起电源噪声。

例如在数字电路中,当电路从一个状态转换为另一种状态时,就会在电源线上产生一个很大的尖峰电流,形成瞬变的噪声电压。

配置去耦电容一方面可减少电源线的负载,另一方面可克服电源线的电压波动,是印制电路板的可靠性设计的一种常规做法,配置原则如下:①电源输入端跨接一个10~100ΛF的电解电容器,如果印制电路板的位置允许,采用100ΛF以上的电解电容器的抗干扰效果会更好。

②为每个集成电路芯片配置一个0101ΛF的陶瓷电容器。

如遇到印制电路板空间小而装不下时,可每4~10个芯片配置一个1~10ΛF钽电解电容器,这种器件的高频阻抗特别小,在500kH z~20M H z范围内阻抗小于1 8,而且漏电流很小(015ΛA以下)。

③对于噪声能力弱、关断时电流变化大的器件和ROM,RAM等存储型器件,应在芯片的电源线(V CC)和地线(GND)间直接接入去耦电容。

④去耦电容的引线不能过长,特别是高频旁路电容不能带引线。

212 地线噪声干扰的抑制在PCB板中,地线结构大致有系统地、机壳地(屏蔽地)、数字地和模拟地等,消除地线干扰的重要措施就是接地。

针对系统可能存在的地线环路干扰和辐射干扰,在布线和布局上还可采取以下措施:(1)解决地环路干扰的方法是切断地环路,增加地环路的阻抗,使用平衡电路等。

解决公共阻抗耦合的方法是减小公共地线部分的阻抗,或采用并联单点接地,彻底消除公共阻抗,所谓并联单点接地:即为PCB板上各个电路模块提供一个公共电位参考点,这样信号就可以在不同的电路模块之间传输,单点接地要求每个电路模块的接地线最终汇流于公共电位参考点,该点称为总地线由于只存在一个参考点,回此没有公共阻抗耦合存在,从而也就没有干扰问题;如果条件允许,可以考虑用单独一层作接地层,这样电路中的任何接地点可直接接至此接地面,这样大大减少了接地电阻,并起到屏蔽作用。

还可以将地线构成回路,以减少电流环路面积,减少接地电位差,但成本就会提高。

(2)将地线布线成网格[4]。

PCB中布地线时不应追求宽地线,应追求多地线网格。

因为地线网格提供了大量的平行地线,并联后的线电感很小,能有效减小地线的电感,从而减小地线的阻抗。

地线的一个主要作用是提供信号回流途径,信号回流要求环路面积最小,此时路径电感最小,阻抗也最小;因此布地线网的关键是:看地线是否减少了信号的环路面积,或给特殊的信号线起到了保护作用,而不是看地线在PCB上的分布情况。

213 信号传输线间串扰的抑制高频下元器件之间存在分布参数。

串扰就是由电路间存在的分布参数通过耦合而引起的。

他包括容性耦合和感性耦合。

容性耦合是指某一电路对另一电路通过导线间电容而形成的电磁耦合。

容性耦合将导致一条导线上的电流串入另一条导线,形成噪声干扰。

所以为了避免串扰,应设法减少他们的分布参数和相互间的电磁干扰;易受干扰的元器件不能放置太近,输人、输出元器件应尽量远离。

根据这一原则,采取如下措施:(1)布置元器件时,所有的连接器都放在印制电路板的一侧,避免从两侧引出电缆。

这样可尽量减少共模辐射干扰的可能性。

互相有关的元器件尽量靠近,使元器件间的引线尽量短,以获得较好的抗干扰效果。

把模拟电路、高速数字电路、干扰源(如功率电路)合理分开,使相互间的信号耦合减至最小。

特别《现代电子技术》2005年第15期总第206期 电子技术应用地,时钟回路应该远离干扰源。

I O驱动电路尽量靠近PCB 边缘,使其尽快离开PCB。

(2)布线时,尽可能缩短高速信号线的长度[5]。