数字频率计电路

.VHDL数字频率计(一)

VHDL数字频率计数字频率计是数字电路中的一个典型应用,实际的硬件设计用到的器件较多,连线比较复杂,而且会产生比较大的延时,造成测量误差、可靠性差。

随着复杂可编程逻辑器件(CPLD)的广泛应用,以EDA工具作为开发手段,运用VHDL语言。

将使整个系统大大简化。

提高整体的性能和可靠性。

VHDL(Very High Speed Integrated Circuit Hardware Description Language,超高速集成电路硬件描述语言)诞生于1982年,是由美国国防部开发的一种快速设计电路的工具,目前已经成为IEEE(The Institute of Electrical and Electronics Engineers)的一种工业标准硬件描述语言。

相比传统的电路系统的设计方法,VHDL具有多层次描述系统硬件功能的能力,支持自顶向下(Top to Down)和基于库(LibraryBased)的设计的特点,因此设计者可以不必了解硬件结构。

从系统设计入手,在顶层进行系统方框图的划分和结构设计,在方框图一级用VHDL对电路的行为进行描述,并进行仿真和纠错,然后在系统一级进行验证,最后再用逻辑综合优化工具生成具体的门级逻辑电路的网表,下载到具体的CPLD器件中去,从而实现可编程的专用集成电路(ASIC)的设计。

数字频率计是直接用十进制数字来显示被测信号频率的一种测量装置。

它不仅可以测量正弦波、方波、三角波、尖脉冲信号和其他具有周期特性的信号的频率,而且还可以测量它们的周期。

经过改装,可以测量脉冲宽度,做成数字式脉宽测量仪;可以测量电容做成数字式电容测量仪;在电路中增加传感器,还可以做成数字脉搏仪、计价器等。

因此数字频率计在测量物理量方面应用广泛。

本设计用VHDL在CPLD器件上实现数字频率计测频系统,能够用十进制数码显示被测信号的频率,能够测量正弦波、方波和三角波等信号的频率,而且还能对其他多种物理量进行测量。

东华大学数电实验-数字频率计报告

目录第一章技术指标1.1整体功能要求1.2系统结构要求1.3电气指标第二章设计原理分析2.1 测频方法分析2.2 低频信号的周期测量方法2.3 整体设计过程第三章单元电路设计3.1 测频采样定时信号及测周时基信号产生3.2计数,锁存和显示3.3控制信号产生3.4 信号选择及量切换控制3.5自校调试信号产生3.6整体电路图第四章测试与调整4.1测频采样电路的调测4.2计数,锁存和显示电路的调测4.3控制信号电路的调测4.4 信号选择及量切换电路的调测4.5测试方法步骤、记录的数据4.6整体电路图第五章设计小结参考文献第一章技术指标1.整体功能要求要求设计一个测量TTL方波信号频率或周期的数字系统。

用按键选择测量信号频率或周期。

测量值采用4个LED七段数码管显示,并以发光二极管指示测量对象:频率(周期)以及测量值的单位:Hz(s)、KHz(ms)。

频率和周期的测量范围都有4档量程。

2.系统结构要求数字频率计的整体结构要求如图所示。

图中被测信号为外部信号,送入测量电路进行处理、测量,档位转换用于选择测试的项目------频率、周期,若测量频率则进一步选择档位。

3.电气指标3.1被测信号波形:矩形波。

3.2 测量频率范围:0.1Hz~999.9KHz,分4档:第一档:100.1Hz~999.9Hz第二档:1.000kHz~9.999kHz第三档:10.00kHz~99.99kHz第四档:100.0kHz~999.9kHz3.3 测量周期范围:0.1us~999.9ms第一档:1.000ms~9.999ms第二档:10.00ms~99.99ms第三档:100.0ms~999.9m第四档:1.000s~9.999s3.4 测量结果显示4位有效数字,测量精度为万分之一。

3.5 量程切换可以采用两个按键手动切换或由电路控制自动切换。

3.6 设计一个周期性方波电路输出频率/周期计调试所需的信号。

输出信号的频率范围与测量范围相同,分为四个量程。

数字频率计设计(PCB图+电路图+源程序)-课程设计

数字频率计设计(PCB图+电路图+源程序)-课程设计数字频率计设计开题报告选题意义及国内外发展状况本课题主要研究如何用单片机来设计数字频率计。

因为在电子技术中,频率的测量十分重要,这就要求频率计要不断的提高其测量的精度和速度。

在科技以日新月异的速度向前发展,经济全球一体化的社会中,简洁、高效、经济成为人们办事的一大宗旨。

在电子技术中这一点表现的尤为突出,人们在设计电路时, 都趋向于用尽可能少的硬件来实现, 并且尽力把以前由硬件实现的功能部分, 通过软件来解决。

因为软件实现比硬件实现具有易修改的优点, 如简单地修改几行源代码就比在印制电路板上改变几条连线要容易得多, 故基于微处理器的电路往往比传统的电路设计具有更大的灵活性。

单片机就属于这一类设计电路,单片机因其功能独特和廉价已在全球有数???千种成功的范例, 在国内也开发出了充电器、空调控制器、电子定时器、汽车防盗器、卫星接收机以及各种智能仪表等实用产品。

频率计也是单片机的一种很重要的应用, 价格低廉且具有实际意义。

虽然使用逻辑分析仪也可以很好的测量信号的频率等参数,但其价格太昂贵。

实现测量的数字化、自动化、智能化已成为各类仪表设计的方向,而由单片机控制的、全自动的、数字显示的频率计就符合这一设计理念。

说到用单片机设计的频率计,这里说一下单片频率计ICM7216D。

单片频率计ICM7216D是美国Intersil公司首先研制的专用测频大规模集成芯片。

它是标准的28引脚的双列直插式集成电路,采用单一的+5V稳压电源工作。

它内含高频振荡器、10进制计数器、7段译码器、位多路复用器、能够直接驱动LED显示器的8段段码驱动器、8位位码驱动器。

其基本的测频范围为DC至10MHz,若加预置的分频电路,则上限频率可达40MHz或100MHz,单片频率计ICM7216D只要加上晶振、量程选择、LED显示器等少数器件即可构成一个DC至40MHz的微型频率计,可用于频率测量、机械转速测量等方面的应用。

实验六基于Multisim8的简易数字频率计仿真

闸门

门控

B 放大 整形

S2

1000Tx

1Tx

10Tx 100Tx

÷10

÷10

计数锁存译码 显示系统

÷10

四、实验参考电路

(1)控制时序产生电路

图4.8.5 是由秒脉冲发生器(可由晶体振荡器和 多级分频器组成)和可重触发单稳态74LS123 组成

的控制时序产生电路。秒脉冲发生器产生脉冲宽度 为的定时脉冲,74LS123单稳态电路产生锁存和清 零脉冲。(仿真软件Multisim 8的元件库中,没有 74LS123单稳态电路,可用555定时器组成单稳态 电路)。 5V

4. 闸门电路

闸门电路由与门组成,该电路有两个输入端和一 个输出端,输入端的一端,接门控信号,另一端接 整形后的被测方波信号。闸门是否开通,受门控信 号的控制,当门控信号为高电平“1”时,闸门开启; 而门控信号为低电平“0”时,闸门关闭。显然,只 有在闸门开启的时间内,被测信号才能通过闸门进 入计数器,计数器计数时间就是闸门开启时间。可 见,门控信号的宽度一定时,闸门的输出值正比于 被测信号的频率,通过计数显示系统把闸门的输出 结果显示出来,就可以得到被测信号的频率。

5. 电子计数器测量周期

当被测信号频率比较低时,用测量周期的方法来 测量频率比直接测量频率有更高的准确度和分辨率, 且便于测量过程自动化。该测量方法在许多科学技 术领域中都得到普遍使用。图4.8.4是用电子计数器 测量信号周期的原理方框图。

晶振

Tx

时基 分频

1µs

S1 Tc

10µs 1ms 100µs Tx1

①可控制的计数、锁存、译码显示系统; ②石英晶体振荡器及分频系统(可用Multisim 8中

的函数发生器替代);

数字频率计分频电路的设计

f

=

1 (65536 ×n +

m)

× T R ×2 K

其中 : n 为溢出次数 , m 为最后一次计数值 , K CL K CL R CL K MOV C ,DOU T RLC A DJ NZ R0 ,RD - AD

RET

312 MAX7219 显示子程序 MAX7219 显示程序就是 89C51 在 CL K ( P212) ,

LOAD ( P210) 时序的配合下 , 通过 D IN ( P211) 向

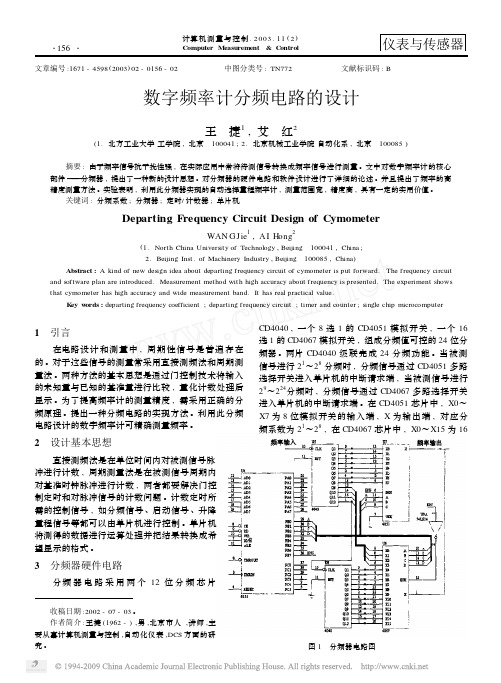

3 分频器硬件电路

分频 器 电 路 采 用 两 个 12 位 分 频 芯 片

CD4040 , 一个 8 选 1 的 CD4051 模拟开关 , 一个 16 选 1 的 CD4067 模拟开关 , 组成分频值可控的 24 位分 频器 。两片 CD4040 级联完成 24 分频功能 。当被测 信号进行 21~28 分频时 , 分频信号通过 CD4051 多路 选择开关进入单片机的中断请求端 , 当被测信号进行 29~224分频时 , 分频信号通过 CD4067 多路选择开关 进入单片机的中断请求端 。在 CD4051 芯片中 , X0~ X7 为 8 位模拟开关的输入端 , X 为输出端 , 对应分 频系数为 21~28 , 在 CD4067 芯片中 , X0~X15 为 16

4 分频原理

为了迅速确定分频系数 , 采用 16 位定时/ 计数器

进行定时计数 。方法如下 : 单片机内部定时计数器的

计数范围为 0~65535 。为保证测量精度 , 选择计数

(完整版)数字频率计电路

(完整版)数字频率计电路

数字频率计电路是一种电子电路,可以测量信号的频率。

它广泛应用于电信、无线电、音频、视频等领域。

数字频率计电路基于计数器的原理,将输入信号的边沿计数,然后将计数的结果通过

数字显示在显示器上。

其基本组成部分包括计数器、计数控制器、时钟、频率分频器和数

字显示器。

计数器是数字频率计电路最重要的部分之一,用于计算输入信号的频率。

计数器输出

的二进制数可以通过计数控制器和时钟信号进行处理,得到输入信号的实际频率。

时钟信号用于控制计数器的计数速度,通常使用晶体振荡器来产生。

频率分频器用于

将输入signal的高频分频到计数器能够接受的范围内,常见的分频比为10,100等。

数字显示器通常采用七段LED数码管来显示,可实现高精度数字显示。

数字频率计电路的优点是精度高、显示方便,并且可适用于多种信号频率的测量。

缺

点是由于计数的误差和时间滞后,所以测量周期较长,无法测量非周期性信号的频率。

在实际应用中,数字频率计电路可以与其他电路模块组合成系统,如频率计、频率控

制器等。

在工业、科研等领域,数字频率计电路广泛应用于信号源、频率合成器、调制解

调器、通信系统等设备中。

VHDL实现的数字频率计

第5节 利用VHDL语言实现单片简易自动量程数字频率计[学习要求] 能利用VHDL语法实现较为复杂的数字系统。

[重点与难点]重点:复杂数字系统的设计方法。

难点:频率计自动量程的设计;动态显示的原理。

[理论内容]一、数字频率计系统概述该频率计的具体电路如图1所示,图中CPLD可采用FLEX10K10系列实现,数码管采用共阴极方式。

Funknown引脚为未知频率输入,ref_clk为10MHz参考频率输入,sys_rst_l 为复位引脚。

从图中可以看出,使用可编程器件使系统器件数降至最低。

该频率计的计数范围从DC到9.999MHz,共分为四个量程,每个量程的阀门如下表所示:图1 单片CPLD数字频率计电路图量程与阀门宽度对应表频率范围/KHz 阀门宽度/sDC~0.9999 110.00~99.99 0.1100.0~999.9 0.011000~9999 0.001该频率计基本原理是通过对来临的未知频率上升沿在设定的时间段内计数,这个时间段就是所谓的阀门。

当计数溢出时,说明所选择的阀门较宽,此时自动选择较窄的阀门。

阀门开关的切换是立即的。

该频率计CPLD 内部逻辑电路通过VHDL 语言编程实现。

系统大致可分为图2所示的四个模块:控制单元(CONTROL ),主要完成时序生成和量程自动切换等。

计数单元(COUNT ),在阀门内对输入频率进行计数,计数结果为四位十进制数。

显示单元(DISPLAY )对计数结果进行动态的数码显示。

分频单元(DIVIDE )比较简单,将参考频率分频得到动态显示所需的频率。

以下对各单元功能具体分析。

二、系统内部各单元概述1、显示单元(DISPLAY )图3 频率计控制单元工作流图其对外接口如图2所示。

sys_rst_l 为总体复位信号,disp_clk 为动态刷新频率,由ref_clk (10MHz )经DIVIDE 单元分频而来,频率为100KHz 。

其输出digit_out(7:0)和gate_l(3:0)如图1和图2所示。

数字频率计电路设计

数字频率计电路设计摘要:在数字电路中,数字频率计属于时序电路,它主要由具有记忆功能的触发器构成。

在计算机及各种数字仪表中,都得到了广泛的应用。

在CMOS电路系列产品中,数字频率计是用量最大、品种多的产品,是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量仪器,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此,频率的测量就显得更为重要。

本课题主要选择以集成芯片作为核心器件,设计了一个简易数字频率计,以触发器和计数器为核心,由信号输入、隔直,触发、计数、数据处理和数据显示等功能模块组成。

放大整型电路:对被测信号进行预处理;计数器译码电路:计数译码集成在一块芯片上,计算单位时间内脉冲个数,把十进制计数器计数结果译成BCD码;显示:把BCD码译码在数码管显示出来。

设计中采用了模块化设计方法,采用适当的放大和整形,提高了测量频率的范围。

关键词:集成电路;译码电路;计数电路The frequency of digital circuit designAbstract: In digital circuits, digital frequency meter belongs to and it mainly consists of sequential circuits with function of memory flip-flop constitutes. In computer and various digital instrument have been widely used. In CMOS circuit series products, digital frequency meter is the most consumable, many varieties products, is a computer, communication equipment, audio video etc scientific research production field indispensable measuring instrument, and with many electric parameter measurement system, measurement results are very close relations, and therefore, frequency measurement becomes even more important.This topic is choose with integrated chips as the core component, designs a simple digital frequency gauge to trigger and counter as the core, the signal input, lie between straight, triggering, counting, data processing and data display function module. Enlarge integer circuit: to be measured signal pretreatment; Counter decoder circuit: count decode integration on a single chip, plan time unit, the decimal counter pulse number count the results translated into BCD; Display: put BCD in digital tube displayed decoding. Design using modular design method, the adoption of appropriate amplifier and plastic and improve the measuring range of frequencies.Keywords: integrated circuits ;decode circuit ;counting circuit目录1概述 (1)1.1课题研究背景 (1)1.2课题研究意义 (1)2整体方案设计(测量频率的方案设计) (1)3主要元器件介绍 (2)3.1 CC4518 (2)3.2 CC4553 (3)3.3 CC4013 (4)3.4 CC4011 (5)3.5 CC4069 (6)3.6 CC4001 (7)3.7 CC4071 (8)4设计任务和要求 (9)5 数字频率计工作原理 (10)6 有关单元电路的设计及工作原理 (11)6.1控制电路 (11)6.2微分、整形电路 (12)6.3延时电路 (12)6.4自动清零电路 (13)7 PCB板的制作 (13)7.1 PCB板设计的设计原则 (14)7.1.1布局 (14)7.1.2布线 (14)7.1.3焊盘 (14)7.2 PCB板电路抗干扰措施 (15)7.2.1电源线设计 (15)7.2.2地线设计 (15)7.3制板 (15)7.4焊接的基本常知识 (15)7.5元器件的安装 (16)8组装和调试 (17)总结与体会 (17)参考文献 (19)谢辞 (21)附录一 (23)附录二 (23)附录三 (23)1 概述1.1 课题研究背景数字频率计是一种基础测量仪器,到目前为止已有30多年的历史,早期设计师们追求的目标主要是扩展测量范围,再加上提高测量的精度、稳定度等,这些也是人们衡量数字频率计的技术水平,决定数字频率计价格高低的主要依据[1]。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第二章电路的总体设计方案2.1方案论证与选择2.1.1方案的提出方案一电路整体框架如图一所示。

被测信号经过放大,整形电路将其转换成同频率的脉动信号,送入计数器进行计数,闸门的一个输入信号是秒脉冲发出的标准脉冲信号,秒脉冲信号源含有个高稳定的石英振荡器和一个多级分频器共同决定,其时间是相当精确的,计数器显示电路采用七段共阴极LED数码管。

图2-1 方案一框架图方案二:本方案采用单片机程序处理输入信号并且将结果直接送往LED显示,为了提高系统的稳定性,输入信号前进行放大整形,在通过A/D转换器输入单片机系统,采用这种方法可大大提高测试频率的精度和灵活性,并且能极大的减少外部干扰,采用VDHL编程设计实现的数字频率计,除被测信号的整形部分、键输入部分和数码显示部分以外,其余全部在一片FPGA芯片上实现,整个系统非常精简,而且具有灵活的现场可更改性。

但采用这种方案相对设计复杂度将会大大提高并且采用单片机系统成本也会大大提高。

图2-2 方案二框架图方案三:采用频率计专用模块,即大规模集成电路将计数器、锁存器、译码、位和段驱动,量程及小数点选择等电路集成在一块芯片中,该方案在技术上是可行的,可以简化电路的设计,当对于设计要求中的某些指标,采用专用模块来完成比较困难,即扩展极为不便。

图2-3 方案三框架图2.1.2方案的的比较方案一:具有设计复杂度小、电路简洁、功能实用且成本低廉等特点,其稳定性较好基本能满足设计要求。

方案二:采用单片机处理能较高要求,但成本提高且设计复杂,虽然可以达到很高的精度要求,但是,VHDL编程语言是我们在学习过程中没有接触过的,短期内也很难掌握并且熟练运用。

方案三:用专用频率计设计模块固然设计简单且稳定但系统可扩展性能较差。

2.1.3方案的选择综合三种方案比较:我感觉方案一和我以前学的专业知识更接加近些,电路原理容易理解,所设计的数字频率计稳定性好,基本上能够满足设计要求,所以我采用第一种设计方案。

图2—5 数字频率计组成框图在我的毕业设计中,数字频率计由信号输入电路、分频电路、放大整形电路、闸门电路、时基电路、逻辑控制电路、计数电路、锁存电路、译码显示电路,小数点移位电路,量程选择开关等组成。

所谓频率,就是周期性信号的在单位时间(1s )内变化的次数,若在一定时间间隔T 内测得这个周期性信号的重复变化次数为N ,则其频率可表示为:T N f (2—1)上图是数字频率计的结构框图。

被测信号经放大整形电路变成计数器所要求的脉冲信号Ⅰ,其频率与被测信号的频率fx 相同。

时基电路提供标准时间基准信号Ⅱ,其高电平持续的时间t 1=1s ,当1s 信号来到时,闸门开通,被测脉冲信号通过闸门,计数器开始计数,直到1s 信号结束时闸门关闭,停止计数。

若在闸门时间1s 内计数器计得的脉冲个数为N ,则被测信号频率fx=N Hz 。

逻辑控制电路的作用有两个:一是产生锁存脉冲 ,使显示器上的数字稳定;二是产生清“0”脉冲Ⅴ,使计数器每次测量从零开始计数。

频率计中各信号波形如图2—6所示:图2—6 频率计中各信号波形说明:1、脉冲信号Ⅰ为被测信号经放大整形电路后变成的计数器所要求的脉冲信号,其频率与被测信号的频率fx 相同,或与被测信号的频率呈一定的比例关系。

2、信号Ⅱ为时基电路提供的标准时间基准信号,其高电平持续时间为1S ,当此信号来到,闸门开通,被测脉冲信号通过闸门,使计数器开始计数;此信号结束,则闸门关闭,计数器停止计数。

Ⅱ脉冲信号又可称为闸门时间脉冲,用T 表示。

3、脉冲信号Ⅲ为闸门时间脉冲控制下闸门所输出的脉冲,因为要将它送入计数器进行计数,所以又将闸门所输出的Ⅲ信号称为计数脉冲信号。

若在闸门时间1S内计数器计得的脉冲个数为N,则被测信号频率fx=N Hz 。

4、脉冲信号Ⅳ即为锁存信号,是逻辑控制电路产生的,控制锁存器锁存计数结果的控制信号,它由时基信号Ⅱ结束时产生的负跳变来产生。

5、脉冲信号Ⅴ是计数器的清零信号,也是逻辑控制电路所产生,用于控制计数器进行清零,使计数器每次测量从零开始计数。

它是由锁存信号Ⅳ结束产生的负跳变来产生。

在这个总的电路设计中包含有几个不同功能的分电路,每个电路在本设计中都有着自己特有的功能,也只有这几个分电路组合在一起才使得整个的电路实现其所要达到的功能。

所以还是先介绍一下每一个分电路的功能特点。

第三章硬件电路设计3.1时基电路和闸门电路3.1.1时基电路时基电路的作用是产生一个标准时间信号,其高电平持续时间为1s,由555定时器构成的多谐荡器产生。

a.555定时器内部结构555定时器是一种模拟电路和数字电路相结合的中规模集成电路,其内部逻辑电路结构如图3—1(a)所示及管脚图如图3—1(b)所示:图3—1(a )555定时器内部逻辑电路结构图3—1(b )555定时器管脚图它由分压器、比较器、基本R--S 触发器和放电三极管等部分组成。

分压器由三个5K 的等值电阻串联而成。

分压器为比较器1A 、2A 提供参考电压,比较器1A 的参考电压为23c cV,加在同相输入端,比较器2A 的参考电压为c cV,加在反相输入端。

比较器由两个结构相同的集成运放1A 、2A 组成。

高电平触发信号加在1A 的反相输入端,与同相输入端的参考电压比较后,其结果作为基本R--S 触发器_DR端的输入信号;低电平触发信号加在2A 的同相输入端,与反相输入端的参考电压比较后,其结果作为基本R —S 触发器_DS 端的输入信号。

基本R--S触发器的输出状态受比较器1A 、2A 的输出端控制。

b .多谐振荡器工作原理由555定时器组成的多谐振荡器如图3—2(a)所示,其中R1、R2和电容C为外接元件。

其工作波如图3—2(b) 所示:图3—2(a) 由555定时器构成的多谐谢振荡器图3—2(b) 由555定时器构成的多谐谢振荡器工作波形设电容的初始电压cU =0,t =0时接通电源,由于电容电压不能突变,所以高、低触发端T H V =T LV=0<VCC,比较器A1输出为高电平,A2输出为低电平,即_1D R =,_0D S =(1表示高电位,0表示低电位),R S -触发器置1,定时器输出01u =此时_0Q =,定时器内部放电三极管截止,电源c cV经1R ,2R 向电容C充电,u 逐渐升高。

当u 上升到13c cV时,2A 输出由0翻转为1,这时__1D D R S ==,R S -触发顺保持状态不变。

所以0<t<期间,定时器输出0u 为高电平1。

1t t =时刻,u 上升到23c cV,比较器1A 的输出由1变为0,这时_0D R =,_1D S =,R S -触发器复0,定时器输出00u =。

12t t t <<期间,_1Q =,放电三极管T导通,电容C通过2R 放电。

u 按指数规律下降,当c u <23c cV 时比较器1A 输出由0变为1,R-S触发器的_DR=_1D S =,Q的状态不变,0u 的状态仍为低电平。

2t t =时刻,u 下降到c cV,比较器2A 输出由1变为0,R---S 触发器的_DR=1,_DS=0,触发器处于1,定时器输出01u =。

此时电源再次向电容C 放电,重复上述过程。

表3—1 555集成定时器的功能表本设计需要的时基信号波形如图3-3所示图3-3本设计要求的时基波形振荡器的输出波形如图3-3所示,其中s t s t 25.0,121==。

由公式()C R R t 2117.0+=和C R t 227.0=,可计算出电阻21R R ,及电容C 的值.若取电容闸门电路部分的与非门选用74LS00,74LS00是四2输入与非门。

其管脚图如图3-6所示。

图3-6 74LS00管脚图表3-2 74LS00真值表3.2放大和整形电路为了能测量不同电平值与波形的周期信号的频率,必须对被测信号进行放大与整形处理,使之成为能被计数器有效识别的脉冲信号。

信号放大与波形整形电路的作用即在于此。

3.2.1放大电设计低频放大电路采用由3DG100构成带电流串联负反馈的分压式单管共射放大电路比较合适,工作点稳定,工作频率范围较宽,放大器输入阻抗比较大。

电路结构如图3-7所示:图3-7 低频信号放大电路在图3-7所示低频信号放大电路中,三极管3DG100起电流放大作用,是组成放大器电路的关键元件。

直流电源Vcc 提供整个放大电路的能源,并且与电阻R1,R2,Rp 确定三极管合适的静态工作状态,即保证三极管的发射结正向偏置,集电结反向偏置,使三极管处于正常放大的状态。

集电极通过一个电阻R e 接地,通过该电阻的反馈来自动调节Ube 的大小,使Ube 基本保持不变。

为了增大放大倍数,减少输入阻抗,在R e 的两端并联一个较大的旁路电容C e ,若C e 两端的交流压降可以忽略,则电压放大倍数将不会因此而下降。

电容C 的作用是隔直流。

高频放大电路采用的是ucp1651芯片对高频信号进行放大,放大电路如图3-8所示:C 310pFC 110pFC 210pF R ?RES 2被测信号2up c1651+5图3-8 高频信号放大电路3.2.2整形电路设计23C ?10pF R 110KR 239K R p47K+53DG100100uF47K 10K1K C e被测信号2Vi 10uF 1K 100k OP37NOT -++5V7404图3-11 放大与整形原理图3.3逻辑控制电路控制电路是通用电子计数器完成逻辑控制的指挥系统,控制着主闸门的开启和关闭。

在控制电路的协调指挥下,全机各部分电路协调动作,完成各项测量工作。

通用电子计数器的测量程序是计数—显示—复零。

也就是说,在主门开启的时间内进行计数,然后由显示电路将计数结果显示出来,接着发出复零信号使仪器又恢复到测量前的初始工作状态。

逻辑控制电路用来产生两种控制信号,一种是控制锁存器锁存的脉冲信号,另一种是产生计数器的清零信号,这两种信号都需要由信号负跳变触发,其中控制锁存的信号是由时基信号负跳变触发,清零信号则是由锁存信号的负跳变触发产生,这里就需要用到单稳态触发器,两种信号各由一单稳态触发器负责产生。

经选择采用双单稳态触发器74LS123,手动复位开关S 按下时,计数器清“0”。

其电路如图3-12所示:321A 1B 2C L R3Q 4Q 13C e x t14R C e x t 15U?A74LS 123A 1B 2C L R3Q 4Q 13C e x t 14R C e x t 15U?A 74LS 123+5+5V 123G6A 74ALS 00R ?3.3k+5S?SW-PBR ?10k R ?10k C ?4.7u FC ?4.7u F +5+5信号输入清零信号输出锁存信号输出图3-12 逻辑控制电路图图3-13 74LS123管脚图表3-4 74LS123功能表设锁存信号和清零信号的脉冲宽度ωt 相同,如果要求 ωt =0.02s,则得s C R t extext 02.045.0==ω 若取 ext R =10K 则f R t C extext μω4.445.0== 取标称值f μ7.4 3.4锁存器3.4.1电路的选择锁存器是构成各种时序电路的存储单元,具有0和1两种状态,一旦状态确定就能自行保持,即长期保持一位二进制码,直到有外部信号作用时才有可能改变。