MCS-51作业讲解

MCS51单片机讲义C语言编程,清华大学出版社第四章

TF0:MCS-51 片内定时器/计数器 T1 溢出中断申请标志位。当启动 T0 计数 后,定时器/计数器 T0 从初值开始加 1 计数,当最高位产生溢出时,TF0 由硬 件 置“1”,向 CPU 申请中断,CPU 响应 T0 中断时,TF0 由硬件清“0”,TF0 也 可 由软件清 0(查询方式)。 TFl:MCS-51 片内的定时器所数器 T1 的溢出中断申请标志 位,功能和 TF0 类同。 TR1 和 TR0 这 2 个位与中断无关,仅与定时器/计数器 T1 和 T0 有关,它们 的功能在后续章节介绍。 当 MCS-51 复位后,TCON 被清 0。则 CPU 关中断,所有中断请求被禁止。 SCON 为串行口控制寄存器,字节地址为 98H, SCON 的低二位为串行口的接 收中断和发送中断标志,其格式如下表 4.3: 表 4.3 SCON 中的中断请求标志位 位 D7 D6 D5 D4 D3 D2 D1 D0 SCON TI RI 位地址 99H 9 8H 各位的功能如下: TI:MCS-51 串行口的发送中断标志位,在串行口以方式 0 发 送时,每当发 送完 8 位数据,TI 由硬件置“1”;若以方式 1、方式 2 或方式 3 发送时,在发 送停止位的开始时,TI 由硬件置“1”,TI=l 表示串行口发送正在向 CPU 申请 中断,要发送的数据一旦写入串行口的数据缓冲器班 SBUF,单片机内部的 硬件 就立即启动发送器继续发送。值得注意的是 CPU 响应发送器中断请求,转向执 行 中断服务程序时 TI 并不清“0”,T1 必须由用户的断服务程序清 0,即中断服务 程序中必须用 TI 清“0”的指令。 RI:串行口接收中断标志位,若串行口接收器允 许接收,并以方式 0 工作, 每当接收到第 8 位数据时 RI 由硬件置“1”,;若以 方式 1、2、3 工作,且 SM2=0 时,每当接收器接收到停止位的中间时 RI 由硬件置 “l,当串行口干以方式 2 或方式 3 进行工作,且 SM2=1 时仅当接收到的第 9 位 数据 RB8 为 1 后,同时还 要在接收到停止位的中间时,RI 由硬件置“l”,RI 为 1,表示串行口接收器正 在向 CPU 申请中断,同样 RI 必须由用户的中断服务程序 清 0。 SCON 其它各位后续章节介绍。 MCS-51 复位后,SCON 也被清零。 4.2.2 中断控制 MCS-51 的 CPU 对中断源的开放或屏蔽,由片内的中断允许寄存器 IE 控制, IE 的字节地址为 A8H,其格式如下表 4.4: 表 4.4 IE 中的中断允许标志位 位 D7 D6 D5 D4 D3 D2 D1 D0 IE EA ES ET1 EX1 ET0 EX0 位地址 AFH ACH ABH AAH A9H A8H EA:MCS-51 的 CPU 的总的开放中断标志位。EA=1,CPU 开放中断,但五个中 断 源的中断请求是否允许,还要由 IE 中的低 5 位所对应的 5 个中断请求允许控 制位 的状态来决定;EA=0,CPU 屏蔽所有的中断申请。 ES:中行口中断允许位。ES=1,允许串行口中断;ES=0 禁止串行口中断。 ET1 :定时器/计数器 T1 的溢出中断允许位。ETl=1 允许 Tl 中断;ETl=0 禁止 ETl 中断。 EXl:外部中断 1 中断允许位。 EXl=1 允许外部中断 1 中断;EXl=0 禁止 外 部中断 1 中断。 ET0:定时器/计数器 0 的溢出中断允许位。ET0=1 允许 T0 中 断;ET0=0 禁 止 T0 中断。 EX0:外部中断 0 中断允许位。EX0=1 允许外部中断 0 中断,EX0=0 禁止外 部中断 0 中断。 MCS-51 复位以后,IE 被清 0,由用户程序 置“1”,或清“0”EI 相应的位, 实现允许或禁止各中断源的中断申请。若使某一 个中断源允计中断必须同时使 CPU 开放中断。更新 IE 的内容,可由位操作指令来实 现,也可用字节操作指令 实现。 4.2.3 中断优先级 MCS-51 有两个中断允许优先级,对于每一个中断请求源可编程为高优先级 中断 或低优先级中断,可实现二级中断嵌套,二级中断嵌套的过程如图 4.2。 CPU执 行 主 程 序 CPU执 行 低 级 中断服务程序 求 请 断 中 级 高级 低 应 响 中断 请求 CPU执 行 高 级 中断服务程序 中 断 请 求 低级 中断 请求 响 应 高 级 返 返 回 主 程 序 回

MCS-51作业讲解

③ 位地址7CH与字节地址7CH如何区别?位地址 7CH具体在片内RAM中什么位置?

答:位地址7CH与字节地址7CH靠所使用的指令 或指令中所使用的寄存器来区别,当使用 位指令或指令中使用“C”寄存器时表明此 时的地址是位地址,其余情况均为字节地 址。 位地址7CH具体在片内RAM2FH单元中D4位。

CJNE A,30H,NEXT ;两数比较,不等转NEXT SJMP NOCHA ;相等转NOCHA(不交换位置)

NEXT:JNC NOCHA;C=0则(A)>(30H)不交换, 转NOCHA(@R1>R0@)

MOV @R0,A;交换R0与R1指向单元的数 XCH A,30H ;将@R1中的数(A)与30H

⒍ MCS-51单片机如何实现工作寄存器组 R0-R7的选择?

答:用户可通过改变PSW中的RS1和RS0的 两位的值选择相应的工作寄存器组。

⒎什么是时钟周期、机器周期、指令周期?当 单片机时钟频率为12 MHz时,一个机器周期 是多少?ALE引脚的输出频率是多少?

答:时钟周期:指为单片机提供时钟信号的振 荡源的周期.

(原R0 )交换 MOV @R1,A;使A(原R0中数)→@R1 NOCHA:INC R0;调节地址指针

INC R1 DJNZ R3,LOOP1;内循环结束判别 DJNZ R2,LOOP0;外循环结束判别

RET

MOV R0,#51H MOV R5,#07H MOV R4,#00H MOV A, @R0 INC R0 LP: ADD A, @R0 JNC LP1 INC R4 CLR C LP1:INC R0 DJNZ R5,LP

⒉在以3000H为首地址的外部单元中,存放了14 个ASCII码表示的0~9之间的数,试编写程序 将它们转换为BCD码,并以压缩型BCD码的 形式存放在以2000H为首地址的外部单元中. MOV DPTR,#2000H MOV P2,#20H MOV R0,#00H MOV R3,#07H LOOP: MOVX A,@R0

51作业(指令系统)

指令系统作业一、基础知识1.设内部RAM中59H单元的内容为50H,写出当执行下列程序段后寄存器A、R0和内部RAM中50H、51H、52H单元的内容为何值?MOV A,59HMOV R0,AMOV A,#00HMOV @R0,AMOV A,#25HMOV 51H,AMOV 52H,#70H2.执行下列程序后,A和B寄存器的内容是多少?MOV SP,#3AHMOV A,#20HMOV B,#30HPUSH ACCPUSH BPOP ACCPOP B3.假定外部RAM2000H单元的内容为80H,那么执行下列程序后,A的内容是多少?MOV P2,#20HMOV R0,#00HMOVX A,@R04.假定累加器A的内容为30H。

1000H:MOVC A,@A十PC执行指令后,把程序存储器的哪个单元的内容送累加器A中?5.假定DPTR的内容为8100H,累加器的内容为40H,执行下列指令后,送入的是程序存储器的哪个元的内容?MOVC A,@A十DPTR6.假定(SP)=60H,(ACC)=30H,(B)=70H,(60H)=0FDH,执行下列程序后,SP、60H、61H、62H的内容各是多少?PUSH ACCPUSH B7.假定(SP)=62H,(60H)=0FDH,(61H) =50H,(62H)=7AH,执行下列程序后SP、60H、61H、62H及DPTR的内容各是多少?8.假定(A)=85H,(R0)=20H,(20H) =0AFH,下列执行指令后累加器A的内容及Cy、AC、OV、P的内容是多少?9.假定(A)=85H,(20H)= 0FEH,(Cy)= 1,执行下列指令后累加器A的内容及Cy、AC、OV、P的内容是多少?ADD A,20H10.假定(A)=0FFH,(R3)=0FH,(30H)=0F0H,(R0)= 40H,(40H)=00H,执行下列指令后,上述寄存器和存储单元的内容是多少?INC AINC R3INC 30HINC @ R011.假定(A)=56H,(R5)=67H,执行下列指令后A和Cy的内容是多少?A DD A, R5DA A12.假定(A)=0FH,(R7)=19H,(30H)=00H,(R1)= 40H,(40H)=0FFH,执行下列指令后,上述寄存器和存储单元的内容是多少?DEC ADEC R7DEC 30HDEC @R113.分析下列指令序列,写出它所实现的逻辑表达式。

单片机原理及应用与C51程序设计(第三版)第8章作业

单片机原理及应用与C51程序设计(第三版)第8章作业习题1. 什么是MCS-51单片机的最小系统?答:所谓最小系统,是指一个真正可用的单片机的最小配置系统。

对于单片机内部资源已能够满足系统需要的,可直接采用最小系统。

2. 简述半导体存储器的分类?答:半导体存储器按读写工作方式可分为两种:只读存储器ROM(Read Only Memory)和随机读写存储器RAM(Random Access Memory)。

只读存储器ROM 有MROM-掩膜型ROM, PROM-可编程ROM, EPROM-可擦除的PROM, E2PROM -电擦除的PROM, Flash Memory-快擦型存储器; 随机读写存储器RAM有静态RAM-SRAM, 动态RAM-DRAM, 非易失性RAM-NVRAM。

3. 简述存储器扩展的一般方法。

答:存储器芯片与单片机扩展连接具有共同的规律。

即不论何种存储器芯片,其引脚都呈三总线结构,与单片机连接都是三总线对接。

另外,电源线接电源线,地线接地线。

4. 什么是部分译码法?什么是全译码法?它们各有什么特点?用于形成什么信号?答:部分译码就是存储器芯片的地址线与单片机系统的地址线顺次相接后,剩余的高位地址线仅用一部分参加译码。

部分译码使存储器芯片的地址空间有重叠,造成系统存储器空间的浪费。

全译码就是存储器芯片的地址线与单片机系统的地址线顺次相接后,剩余的高位地址线全部参加译码。

这种译码方法中存储器芯片的地址空间是唯一确定的,但译码电路要相对复杂。

译码形成存储器芯片的片选信号线CE。

5. 采用部分译码为什么会出现地址重叠情况,它对存储器容量有何影响?答:部分译码就是存储器芯片的地址线与单片机系统的地址线顺次相接后,剩余的高位地址线仅用一部分参加译码。

参加译码的地址线对于选中某一存储器芯片有一个确定的状态,而与不参加译码的地址线无关。

也可以说,只要参加译码的地址线处于对某一存储器芯片的选中状态,不参加译码的地址线的任意状态都可以选中该芯片。

清华大学出版社MCS51单片机第七章作业讲解

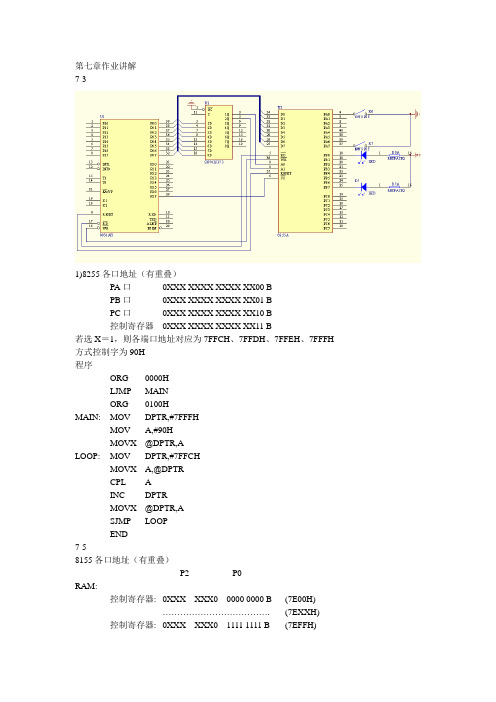

第七章作业讲解7-31)8255各口地址(有重叠)PA口0XXX XXXX XXXX XX00 BPB口0XXX XXXX XXXX XX01 BPC口0XXX XXXX XXXX XX10 B控制寄存器0XXX XXXX XXXX XX11 B若选X=1,则各端口地址对应为7FFCH、7FFDH、7FFEH、7FFFH 方式控制字为90H程序ORG 0000HLJMP MAINORG 0100HMAIN: MOV DPTR,#7FFFHMOV A,#90HMOVX @DPTR,ALOOP: MOV DPTR,#7FFCHMOVX A,@DPTRCPL AINC DPTRMOVX @DPTR,ASJMP LOOPEND7-58155各口地址(有重叠)P2 P0RAM:控制寄存器: 0XXX XXX0 0000 0000 B (7E00H)………………………………. (7EXXH) 控制寄存器: 0XXX XXX0 1111 1111 B (7EFFH)IO口寄存器:控制寄存器: 0XXX XXX1 XXXX X000 B (7F00)PA口: 0XXX XXX1 XXXX X001 B (7F01)PB口: 0XXX XXX1 XXXX X010 B (7F02)PC口: 0XXX XXX1 XXXX X011 B (7F03)TL寄存器: 0XXX XXX1 XXXX X100 B (7F04)TH寄存器: 0XXX XXX1 XXXX X101 B (7F05)1)命令字应该为0000 1110B=0EH(PA口为方式0输入,PB和PC均为方式0输出)诊断程序编制方法:先对B口写XXH,检查A口读入是否为XXH,。

正确则循环点亮C口发光管。

程序:ORG 0000HLJMP MAINORG 0030HMAIN: MOV DPTR,#7F00H ;命令口MOV A,#0EHMOVX @DPTR,AMOV DPTR,#7F02H ;写B口MOV A.#XXHMOVX @DPTR,AMOV DPTR,#7F01H ;读A口MOVX A,@DPTRCJNE A,#XXH,ERRMOV DPTR,#7F03H ;C口循环点亮LED灯NOMAL: M OV R7,#06HMOV A,#01HLOOP: MOVX @DPTR,A;LCALL DELAYRL ADJNZ R7,LOOPSJMP NOMALERR: MOV DPTR,#7F03HMOV A.#3FHMOVX @DPTR,ASJMP FINISHDELAY: MOV R7,#0FFHDJNZ R7,$RETFINISH : END2)RAM:控制寄存器: 0XXX XXX0 0000 0000 B (7E00H)………………………………. (7EXXH)控制寄存器: 0XXX XXX0 1111 1111 B (7EFFH)诊断程序编制方法:依次对256个字节循环检测(先对某RAM单元写入XXH,再读取该单元是否为XXH。

MCS-51单片机定时器-计数器常见习题解答

MCS-51 单片机定时器/计数器常见习题解答1、根据定时器/计数器0 方式1 逻辑结构图,分析门控位GATE 取不同值时,启动定时器的工作过程。

答:当GATE=0:软件启动定时器,即用指令使TCON 中的TR0 置1 即可启动定时器0。

GATE=1:软件和硬件共同启动定时器,即用指令使TCON 中的TR0 置1 时,只有外部中断INT0 引脚输入高电平时才能启动定时器0。

2、当定时器/计数器的加1 计数器计满溢出时, 溢出标志位TF1 由硬件自动置1,简述对该标志位的两种处理方法。

答:一种是以中断方式工作,即TF1 置1 并申请中断,响应中断后,执行中断服务程序,并由硬件自动使TF1 清0;另一种以查询方式工作,即通过查询该位是否为1 来判断是否溢出,TF1 置1 后必须用软件使TF1 清0。

3、设MCS-51 单片机fosc=12MHz,要求T0 定时150µs,分别计算采用定时方式0、方式1 和方式2 时的定时初值。

答:方式0 的定时初值:IF6AH方式1 的定时初值:FF6AH方式2 的定时初值:6AH4、设MCS-51 单片机fosc=6MHz,问单片机处于不同的工作方式时,最大定时范围是多少?答:方式0 的最大定时范围:131,072µs方式1 的最大定时范围:16,384µs方式2 的最大定时范围:512µs5、设MCS-51 的单片机晶振为6MHZ,使用T1 对外部事件进行计数,每计数200 次后,T1 转为定时工作方式,定时5ms 后,又转为计数方式,如此反复的工作,试编程实现。

答:#includebit F0=0;void main() {TMOD=0x60; TL1=56;TH1=56;TR1=1;ET1=1;EA =1; While(1);}void serve() interrupt 3 {if (!F0){ TMOD=0x10;TL1=63036%16;TH1=63036/16;F0=~F0;}else{TMOD=0x60;TL1=56;TH1=56;F0=~F0;}}6、用方式0 设计两个不同频率的方波,P1.0 输出频率为200Hz,P1.1 输出频率为100Hz,晶振频率12MHz。

MCS51讲义

第一章MCS-51 硬件结构1.1引言单片计算机是把CPU(中央处理单元)、一定容量的存储器和若干输入、输出接口等部件集成在一块硅片上的微型计算机,简称单片机。

自1976年美国Intel公司推出第一代单片机系列MCS-48以来,单片机技术蓬勃发展,质量和性能逐年提高,应用领域日益扩大。

目前世界上各大半导体公司所开发并生产的单片机系列,各具特色,阵容强大,品种齐全。

已有几十个系列,数百余品种,可满足各类系统设计的需求。

单片机一问世,就以体积小、功能全、应用便捷和价格低等优点赢得了市场的的欢迎和用户青睐。

目前单片机正在过程控制、数据收集、智能仪表、机电一体化、家用电器以及网络技术等领域中发挥着重要的控制作用。

所有单片机也称微控制器。

微控制器1.2MCS-51 系列早期的MCS-51微控制器具有以下基本特点:(1)8位CPU;(2)片内带振荡器,振荡频率f osc范围1.2~12MHz ,可有时钟输出;(3)128字节片内数据存储器(MCS-52及以上有256字节片内数据存储器);(4)程序存储器寻址范围:64K字节;(5)片外数据程序存储器寻址范围:64K字节;(6)21个字节专用特殊功能寄存器(SFR)(52子序列有26字节,SFR是51系列单片机的重要内部结构,其他51子序列单片机都基于SFR扩展更为强大的功能);(7)4个8位并行I/O接口:P0、P1、P2、P3;(8)1个全双工串行I/O接口,可多机通信;(9)2个(52子序列,3个)16位定时器/计数器;(10)中断系统有5个(52子序列,6个)中断源,可编程为两个优先级;(11)111条指令,含乘法和除法指令;(12)具有独特的位寻址、位处理能力(13)片内采用单总线结构;(14)用单一+5V电源;(15)此外,89C51及89C52还分别有4K或8K字节EEPROM作为程序存储器。

而52子序列是51单片机的最早衍生品,其片内数据存储器增至256个字节;在SFR内增加了一个16位定时器/计数器T2,其功能更为强大和实用,并增加了一个与T2相关的中断源;其他性能均与51子序列相同。

MCS-51作业解答PPT教学课件

(6) ADD A, R0 有溢出

(7) ADD A, 30H (8) ADD A, #30H

同(6) (9) ADDC A, 30H

有辅助进位 (10)SUBB A, #30H

2020/12/10

(A)= AAH , (PSW)= 04H

3-8 已知(A)=7AH, (R0)=30H, (30H)=A5H, (PSW)=80H, 写出分别执行下列各条指令后A

和PSW(Cy,AC,F0,RS1,RS0,OV,-,P)的结果

(1) XCH A, R0 (2) XCH A, 30H (3) XCH A, @R0

同(2) (4) XCHD A, @R0 (5) SWAP A

CPL C

;(C)= 1

SETB 01H

;(01H)=1

LOOP1:ORL C, ACC.0 ; (C)= 1

JB ACC.2, LOOP2 ;jump to LOOP2

CLR 00H

LOOP2:MOV P1, A ; (P1)= 66H

位地址00H的内容不变, 位地址01H的内容为 1

2020/12/10

DJNZ R7, LOOP

SJMP $

2020/12/10

b1y0wky

习题4-13 将外部RAM 1000H开始的100个数据 传送到外部RAM 2000H开始的连续单元

MOV DPTR, #1000H ; 数据起始地址

MOV R7, #100

; 数据个数

LOOP:MOVX A , @DPTR

PUSH DPH

by8wky

习题4-11 内部RAM 30H开始有若干无符号数,

MCS-51单片机大作业

MCS-51单片机大作业通过学习51单片机资料完成以下作业题:1、简述电子计算机的冯诺依曼结构与哈弗结构,指出两种结构的本质区别。

(1)冯诺依曼结构:冯诺依曼结构也称普林斯顿结构,是一种将程序指令存储器和数据存储器合并在一起的存储器结构。

程序指令存储地址和数据存储地址指向同一个存储器的不同物理位置,因此程序指令和数据的宽度相同,如英特尔公司的8086中央处理器的程序指令和数据都是16位宽。

如图1所示:图1冯诺依曼结构冯诺依曼结构特点:●采用存储程序方式,指令和数据混合存储在同一个存储器中。

即数据和程序在内存中是没有区别的,它们都是内存中的数据,当EIP指针指向哪CPU就加载哪段内存中的数据,如果是不正确的指令格式,CPU就会发生错误中断. 指令和数据都可以送到运算器进行运算,即由指令组成的程序是可以修改的。

●存储器是按地址访问的线性编址的一维结构,每个单元的位数是固定的。

●指令由操作码和地址组成。

操作码指明本指令的操作类型,地址码指明操作数和地址。

操作数本身无数据类型的标志,它的数据类型由操作码确定。

●通过执行指令直接发出控制信号控制计算机的操作。

指令在存储器中按其执行顺序存放,由指令计数器指明要执行的指令所在的单元地址。

指令计数器只有一个,一般按顺序递增,但执行顺序可按运算结果或当时的外界条件而改变。

●以运算器为中心,I/O设备与存储器间的数据传送都要经过运算器。

●数据以二进制表示。

(2)哈弗结构简述:哈佛结构是一种将程序指令存储和数据存储分开的存储器结构。

哈佛结构是一种并行体系结构。

如图2所示:图2,哈弗结构哈弗结构处理器的主要特点是:●使用两个独立的存储器模块,如图程序存储器和数据存储器,分别存储指令和数据,每个存储模块都不允许指令和数据并存,每个存储器独立编址、独立访问;●使用独立的两条总线,分别作为CPU与每个存储器之间的专用通信路径,而这两条总线之间毫无关联。

程序指令存储和数据存储分开,可以在硬件上读取指令代码和传输数据时使用不同的传输线宽度。

MCS-51指令详解

MCS-51指令详解说明:为了使MCS-51单片机初学者快速入门,迅速掌握单片机指令含意、操作码、操作数及对应地址,汇编语言怎样编写等,现按指令操作码按顺序编写。

ORG 0000HNOP ; 空操作指令AJMP L0003 ; 绝对转移指令L0003: LJMP L0006 ; 长调用指令L0006: RR A ; 累加器A内容右移(先置A为88H)INC A ; 累加器A 内容加1INC 01H ; 直接地址(字节01H)内容加1INC @R0 ; R0的内容(为地址) 的内容即间接RAM加1;设R0=02H,02H=03H,单步执行后02H=04HINC @R1 ; R1的内容(为地址) 的内容即间接RAM加1;设R1=02H,02H=03H,单步执行后02H=04HINC R0 ; R0的内容加1 (设R0为00H,单步执行后查R0内容为多少)INC R1 ; R1的内容加1(设R1为01H,单步执行后查R1内容为多少)INC R2 ; R2的内容加1 (设R2为02H,单步执行后查R2内容为多少)INC R3 ; R3的内容加1(设R3为03H,单步执行后查R3内容为多少)INC R4 ; R4的内容加1(设R4为04H,单步执行后查R4内容为多少)INC R5 ; R5的内容加1(设R5为05H,单步执行后查R5内容为多少)INC R6 ; R6的内容加1(设R6为06H,单步执行后查R6内容为多少)INC R7 ; R7的内容加1(设R7为07H,单步执行后查R7内容为多少)JBC 20H,L0017; 如果位(如20H,即24H的0位)为1,则转移并清0该位L0017: ACALL S0019 ; 绝对调用S0019: LCALL S001C ; 长调用S001C: RRC A ; 累加器A的内容带进位位右移(设A=11H,C=0; 单步执行后查A和C内容为多少)DEC A ; A的内容减1DEC 01H ; 直接地址(01H)内容减1DEC @R0 ; R0间址减1,即R0的内容为地址,该地址的内容减1DEC @R1 ; R1间址减1DEC R0 ; R0内容减1DEC R1 ; R1内容减1DEC R2 ; R2内容减1DEC R3 ; R3内容减1DEC R4 ; R4内容减1DEC R5 ; R5内容减1DEC R6 ; R6内容减1DEC R7 ; R7内容减1JB 20H,L002D ; 如果位(20H,即24H的0位)为1则转移L002D: AJMP L0017 ; 绝对转移RET ; 子程序返回指令RL A ; A左移ADD A,#01H ; A的内容与立即数(01H)相加ADD A,01H ; A的内容与直接地址(01H内容)相加ADD A,@R0 ; A的内容与寄存器R0的间址内容相加ADD A,@R1 ; A的内容与寄存器R1的间址内容相加ADD A,R0 ; A的内容与寄存器R0的内容相加ADD A,R1 ; A的内容与寄存器R1的内容相加ADD A,R2 ; A的内容与寄存器R2的内容相加ADD A,R3 ; A的内容与寄存器R3的内容相加ADD A,R4 ; A的内容与寄存器R4的内容相加ADD A,R5 ; A的内容与寄存器R5的内容相加ADD A,R6 ; A的内容与寄存器R6的内容相加ADD A,R7 ; A的内容与寄存器R7的内容相加JNB 30H,L0041 ; 直接位(30H)为0相对转移L0041: ACALL S0100 ; 绝对调用RETI ; 中断返回指令RLC A; 带进位位左移ADDC A,#02H ; A带进位位与立即数(#02H)相加ADDC A,02H ; A带进位位与直接地扯(02H内容)相加ADDC A,@R0 ; A带进位位与R0间扯内容相加ADDC A,@R1 ; A带进位位与R1间扯内容相加ADDC A,R0 ; A带进位位与R0内容相加ADDC A,R1 ; A带进位位与R1内容相加ADDC A,R2 ; A带进位位与R2内容相加ADDC A,R3 ; A带进位位与R3内容相加ADDC A,R4 ; A带进位位与R4内容相加ADDC A,R5 ; A带进位位与R5内容相加ADDC A,R6 ; A带进位位与R6内容相加ADDC A,R7 ; A带进位位与R7内容相加JC L0095 ; 进位为1转移NOPAJMP L0017 ; 绝对转移ORL 02H,A ; 直接地址内容与A或ORL 02H,#02H; 直接地址内容与立即数或ORL A,#44H ; A与立即数或ORL A,02H ; A与直接地址内容或ORL A,@R0 ; A与R0间址内容或ORL A,@R1 ; A与R1间址内容或ORL A,R0 ; A与R0内容或ORL A,R1 ; A与R1内容或ORL A,R2 ; A与R2内容或ORL A,R3 ; A与R3内容或ORL A,R4 ; A与R4内容或ORL A,R5 ; A与R5内容或ORL A,R6 ; A与R6内容或ORL A,R7 ; A与R7内容或JNC L0017 ; 进位为0转移ACALL L0017 ; 绝对调用ANL 02H,A ; 直接地址与A与ANL 02H,#02H; 立即数与直接地址与ANL A,#02H ; A与立即数与ANL A,02H ; A与直接地址与ANL A,@R0 ; A与R0间址与ANL A,@R1 ; A与R1间址与ANL A,R0 ; A与R0与ANL A,R1 ; A与R1与ANL A,R2 ; A与R2与ANL A,R3 ; A与R3与ANL A,R4 ; A与R4与ANL A,R5 ; A与R5与ANL A,R6 ; A与R6与ANL A,R7 ; A与R7与JZ L0084 ; A为零转移L0084: AJMP L0017 ; 绝对转移XRL 01H,A ; 直接地址与A异或XRL 02H,#01H; 直接地址与立即数异或XRL A,#01H ; A与立即数异或XRL A,01H ; A与直接地址异或XRL A,@R0 ; A与R0间址址异或XRL A,@R1 ; A与R1间址址异或XRL A,R0 ; A与R0异或XRL A,R1 ; A与R1异或XRL A,R2 ; A与R2异或XRL A,R3 ; A与R3异或XRL A,R4 ; A与R4异或L0095: XRL A,R5 ; A与R5异或XRL A,R6 ; A与R6异或XRL A,R7 ; A与R7异或JNZ L0084 ; A不为零转L009A: ACALL L0084 ; 绝对调用ORL C,01H ; 直接位或到进位JMP @A+DPTR ; 相对于DPTR间接转MOV A,#01H ; 立即数送AMOV 01H,#02H ; 立即数送直接地址MOV @R0,#01H ; 立即数送间址R0MOV @R1,#02H ; 立即数送间址R1MOV R0,#01H ; 立即数送R0MOV R1,#01H ; 立即数送R1MOV R2,#01H ; 立即数送R2MOV R3,#01H ; 立即数送R3MOV R5,#01H ; 立即数送R5MOV R6,#01H ; 立即数送R6MOV R7,#01H ; 立即数送R7SJMP L00BA ; 短转移L00BA: AJMP L0095 ; 绝对转移ANL C,02H ; 直接地址与进位与ORG 00C0H ;MOV 02H,01H ; 直接地址送直接地址MOV 01H,@R0 ; 间址R0送直接地址MOV 01H,@R1 ; 间址R1送直接地址MOV 01H,R0 ; R0送直接地址MOV 01H,R1 ; R1送直接地址MOV 01H,R2 ; R2送直接地址MOV 01H,R3 ; R3送直接地址MOV 01H,R4 ; R4送直接地址MOV 01H,R5 ; R5送直接地址MOV 01H,R6 ; R6送直接地址MOV 01H,R7 ; R7送直接地址NOPMOV DPTR,#1234H; 建立数据指针地址为1234HACALL L00BA ; 绝对调用MOV 03H,C ; 进位送03H位(即20H的03位)MOVC A,@A+DPTR ; 由A+DPTR寻扯的程序存贮器字节送ASUBB A,#01H ; A减去立即数和进位位SUBB A,02H ; A减去直接地址内容和进位位SUBB A,@R0 ; A减去R0间接RAM和进位位SUBB A,@R1 ; A减去R1间接RAM和进位位SUBB A,R0 ; A减去R0和进位位SUBB A,R1 ; A减去R1和进位位SUBB A,R2 ; A减去R2和进位位SUBB A,R3 ; A减去R3和进位位SUBB A,R4 ; A减去R4和进位位SUBB A,R5 ; A减去R5和进位位SUBB A,R6 ; A减去R6和进位位SUBB A,R7 ; A减去R7和进位位ORL C,/00H ; 直接位的反或到进位AJMP L0084 ; 绝对转移MOV C,03H ; 直接位数送进位INC DPTR ; 数据指针加1MUL AB ; A乘以BNOP ; A5H为二字节空操作指令NOPMOV @R0,05H ; 直接字芯送R0间接RAMMOV @R1,05H ; 直接字芯送R1间接RAMMOV R1,05H ; 直接字芯送R1S0100: MOV R2,05H ; 直接字芯送R2MOV R3,05H ; 直接字芯送R3MOV R4,05H ; 直接字芯送R4MOV R5,05H ; 直接字芯送R5MOV R6,05H ; 直接字芯送R6MOV R7,05H ; 直接字芯送R7ANL C,/04H ; 直接位的反与到进位ACALL S0100 ; 绝对调用CPL 04H ; 直接位取反CPL C ; 进位取反CJNE A,#01H,L0139 ; 立即数与A比较,不相等则转移CJNE A,01H,L0139 ; 直接字节与A比较,不相等则转移CJNE @R0,#01H,L0139 ; 立即数与R0间接RAM比较,不相等则转移CJNE @R1,#01H,L0139 ; 立即数与R1间接RAM比较,不相等则转移CJNE R0,#01H,L0139 ; 立即数与R0比较,不相等则转移CJNE R1,#01H,L0139 ; 立即数与R1比较,不相等则转移CJNE R2,#01H,L0139 ; 立即数与R2比较,不相等则转移CJNE R3,#01H,L0139 ; 立即数与R3比较,不相等则转移CJNE R4,#01H,L0139 ; 立即数与R4比较,不相等则转移CJNE R5,#01H,L0139 ; 立即数与R5比较,不相等则转移CJNE R6,#01H,L0139 ; 立即数与R6比较,不相等则转移CJNE R7,#01H,L0139 ; 立即数与R7比较,不相等则转移PUSH 00H ; 直接字节进栈,SP加1L0139: AJMP L0084 ; 绝对转移CLR 04H ; 直接位清零CLR C; 清零进位SWAP A ; A左环移四位(A的二个半字节交换)XCH A,05H ; 交换A和直接字节XCH A,@R0 ; 交换A和R0间接RAMXCH A,@R1 ; 交换A和R1间接RAMXCH A,R0 ; 交换A和R0XCH A,R1 ; 交换A和R1XCH A,R2 ; 交换A和R2XCH A,R3 ; 交换A和R3XCH A,R4 ; 交换A和R4XCH A,R5 ; 交换A和R5XCH A,R6 ; 交换A和R6XCH A,R7 ; 交换A和R7POP 00H ; 直接字节出栈,SP减1ACALL L0139 ; 绝对调用SETB 03H ; 置位直接位SETB C ; 置位进位DA A ; A的十进制加法调熊DJNZ 01H,L0139 ; 直接字节减1,不为零则转移XCHD A,@R0 ; 交换A和R0间接RAM的低4位XCHD A,@R1 ; 交换A和R1间接RAM的低4位L0158: DJNZ R0,L0139 ; R0减1,不为零则转移DJNZ R1,L0158 ; R1减1,不为零则转移DJNZ R2,L0158 ; R2减1,不为零则转移DJNZ R3,L0158 ; R3减1,不为零则转移DJNZ R4,L0158 ; R4减1,不为零则转移DJNZ R5,L0158 ; R5减1,不为零则转移DJNZ R6,L0158 ; R6减1,不为零则转移DJNZ R7,L0158 ; R7减1,不为零则转移MOVX A,@DPTR ; 外部数据(16位地址)送AL0169: NOPAJMP L0139 ; 绝对转移MOVX A,@R0 ; R0间址即外部数据(8位地址)送AMOVX A,@R1 ; R1间址即外部数据(8位地址)送ACLR A; 清零AMOV A,05H ; 直接字节送AMOV A,@R0 ; R0间接RAM送AMOV A,@R1 ; R1间接RAM送AMOV A,R0 ; R0送AMOV A,R1 ; R1送AMOV A,R2 ; R2送AMOV A,R3 ; R3送AMOV A,R4 ; R4送AMOV A,R5 ; R5送AMOV A,R6 ; R6送AMOV A,R7 ; R7送AMOVX @DPTR,A ; A送外部数据(16位地址)ACALL L0169 ; 绝对调用MOVX @R0,A ; A送R0间址即外部数据(8位地址)MOVX @R1,A ; A送R1间址即外部数据(8位地址)CPL A ; A取反MOV 05H,A ; A送直接字节MOV @R0,A ; A送R0间址即间接RAMMOV @R1,A ; A送R1间址即间接RAMMOV R0,A ; A送R0MOV R1,A ; A送R1MOV R2,A ; A送R2MOV R3,A ; A送R3MOV R4,A ; A送R4MOV R5,A ; A送R5MOV R6,A ; A送R6MOV R7,A ; A送R7END。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.举例说明你所知道的MCS-51有哪些典型产

品,它们有何区别?

答:有8031、8051、8751。 8051内部有4KB ROM; 8751内部有4KB EPROM 8031片内无ROM; 除此之外,三者的内部结构及引脚完全相同。

2.MCS-51单片机内部包含哪些主要逻辑功能

部件?

ANL A,#17H ;(A)=03H ORL 17H,A ;(17H)=37H

XRL A,@R0 ;(A)=34H

CPL A

;(A)=0CBH

13.请用位操作指令编写实现下面逻辑表达式的程序。

⑴ PSW.5=P1.3×Acc.2+B.5×P1.1

MOV ANL MOV MOV

C,P1.3 C,Acc.2 PSW.5,C C,B.5

⒋以BUF1为起始地址的外部数据存储器区中, 存放有16个单字节无符号二进制数,试编写 一程序,求其平均值并送BUF2单元. MOV DPTR,#BUF

MOV R5,#0FH

MOV R4,#00H

MOV A, @DPTR

INC DPTR

LP: ADD A, @DPTR

JNC LP1

INC R4

MOV R4,A

ALE信号输出,在其后沿将P0口输出的低

8位地址锁存于外部地址锁存器中; ② 访问外部memory的过程中,ALE端仍以 不变的频率周期性的输出正脉冲信号,且

fALE=1/6fosc ,所以可用作对外输出的时钟

信号和定时作用;

③当片内有EPROM时,可作为编程脉冲输入

端使用。

PSEN:外部程序memory(EPROM)选通

址都是0000~FFFFH,但CPU对它们的访问 是相互独立的,不会产生二意性,即CPU 给出一个地址,不会同时选中二个存储单 元。因为数据存储器在硬件上有RD或WR信 号选通,软件上有MOVX类指令访问。而程 序存储器在硬件上有PSEN信号选通,软件 上有MOVC类指令访问。

③ 位地址7CH与字节地址7CH如何区别?位地址 7CH具体在片内RAM中什么位置? 答:位地址7CH与字节地址7CH靠所使用的指令

MOV P2,#20H

MOV R0,#00H

MOV R3,#07H

LOOP: MOVX A,@R0

INC

R0

SUBB MOV MOVX INC

A,#30H B,A A,@R0 R0

SUBB A,#30H SWAP A ORL A,B MOVX @DPTR,A INC DPTR DJNZ RET R3,LOOP

BINBCD1:MOV B,#100 DIV AB ;A=百位数,

B=余数(十位及个位数)

MOV @R0,A ;百位数存入RAM INC R0

MOV A,#10 ;

XCH A,B ;

DIV

AB

; A=十位数,B=个位数,

(A、B中高4位一定为0)

SWAP A

ADD A,B ;数组合到A MOV @R0,A ;存入RAM

MOV A,@R0 MUL AB

INC R0 ADD A,@R0

XCH

A,B

ADDC A,#00H MOV @R0,A RET

⒉在以3000H为首地址的外部单元中,存放了14 个ASCII码表示的0~9之间的数,试编写程序 将它们转换为BCD码,并以压缩型BCD码的 形式存放在以2000H为首地址的外部单元中. MOV DPTR,#2000H

前工作寄存器组?

答:开机复位后,CPU使用第0组工作寄存器,

地址是00H~07H,可通过对PSW状态字寄存

器中RS1 及RS0两位的设置来确定和改变

CPU当前使用的工作寄存器组。

② MCS-51单片机的程序存储器和数据存储器共

处同一地址空间为什么不会发生总线冲突? 答:虽然数据存储器的地址与程序存储器的地

⒏在内部RAM的BLOCK开始的单元中有一无

符号数据块,数据块长度存入LEN单元.试编 程求其中的最大数并存入MAX单元中.

MOV R0,#BLOCK MOV R2,LEN SJMP LP1

LP2:JNC LP1

MOV A,@R0

DEC

R2

MOV A,@R0

LP: INC R0

CLR C CJNE A,@R0,LP2

LP1:DJNZ R2,LP

MOV MAX,A

RET

⒐试编程将内部RAM中41H~43H单元中的 数左移4位,移出部分送40H单元.

MOV 40H,#00H

MOV R4,#04H

MOV @R0,A;交换R0与R1指向单元的数

XCH A,30H ;将@R1中的数(A)与30H (原R0 )交换

MOV @R1,A;使A(原R0中数)→@R1

NOCHA:INC INC R0;调节地址指针 R1

DJNZ R3,LOOP1;内循环结束判别

DJNZ R2,LOOP0;外循环结束判别 RET

ANL

W.5,C

第四章 习题与思考题(P

73)

⒈ 若有两个符号数x,y分别存放在内部存储 器50H、51H单元中,试编写一个程序实现 x×10+y,结果存入52H,53H单元中.

CLR C INC R0

MOV R0,#50H MOV B,#10 MOV @R0,A INC R0

信号线,当CPU读取外部程序时,

PSEN每个机器周期两次有效。

⒍ MCS-51单片机如何实现工作寄存器组

R0-R7的选择?

答:用户可通过改变PSW中的RS1和RS0的 两位的值选择相应的工作寄存器组。

⒎什么是时钟周期、机器周期、指令周期?当

单片机时钟频率为12 MHz时,一个机器周期

是多少?ALE引脚的输出频率是多少? 答:时钟周期:指为单片机提供时钟信号的振

LOOP1:MOV A,@R0 ;取相邻两单元中的数 MOV 30H,A ; 低地址内容→30H

MOV A,@R1 ;高地址内容→A中

CJNE A,30H,NEXT ;两数比较,不等转NEXT SJMP NOCHA ;相等转NOCHA(不交换位置) NEXT:JNC NOCHA;C=0则(A)>(30H)不交换, 转NOCHA(@R1>R0@)

或指令中所使用的寄存器来区别,当使用

位指令或指令中使用“C”寄存器时表明此

时的地址是位地址,其余情况均为字节地

址。

位地址7CH具体在片内RAM2FH单元中D4位。

第三章习题与思考题

2.设内部RAM中59H单元的内容为50H,写 出当执行下列程序断后寄存器A,R0和内 部RAM中50H、51H单元的内容为何值?

答:有8位CPU、4KB的ROM、可寻址64KB的程 序存储器和数据存储器、128B的片内RAM

和21个SFR、两个16位的定时/计数器、

4个8位的I/O并行口、一个全双工异步 串行口、5个中断源,两个中断优先级、 一个内部时钟发生器。

3. MCS-51单片机内256B的数据存储器可分为几

个区?分别作什么用?

答:分为二大部分四个不同的区: ⑴ 00H~7FH单元组成低128字节的片内RAM区, 其中00H~1FH共32个单元通常作为工作寄存 器区; 20H ~2FH共16个字节,这些单元可 以构成布尔处理机的存储器空间; 30H~7FH 共80个单元为用户RAM区,作堆栈或数据缓冲 区。 ⑵ 80H~FFH单元组成高128字节的专用寄存器 (SFR)区。

LP: ADD A, @R0 JNC LP1 INC R4

MOV A,R3

RRC A MOV R3,A CLR C

CLR C LP1:INC R0

DJNZ R5,LP2 RET

DJNZ R5,LP

⒎编写将一个单字节十六进制数转换为十进制

数的子程序.

入口:A←十六进制数

出口:R0=十位数和个位数地址指针

荡源的周期.

机器周期T机:指CPU完成某些基本操作的 所需要的时间。

指令周期T指:指令周期是指执行一条指令

所需要的时间。

当单片机时钟频率为12 MHz时:

T机= 12T振=fosc/12=1us 。

fALE=fosc/6=2MHz

补充作业:

①开机复位后,CPU使用的是哪组工作寄存器? 它们的地址是什么?CPU如何确定和改变当

5. MCS一51单片机的EA、ALE、PSEN信号各自的 功能是什么? 答:EA的主要作用是选择程序memory。

当EA=0时CPU只能访问片外memory;

当EA=1时,如果PC﹤﹦0FFFH时,则CPU

访问片内ROM ,否则CPU自动转向外部

EPROM。

ALE有三个作用。

① 当CPU访问外部memory初时,产生正脉冲

MOV A,59H;

(A)=50H (R0)=50H

MOV R0,A;

MOV A,#00; MOV @R0, A;

(A)=00H

(50H)=00H (A)=25H

MOV A, #25H; MOV 51H, A;

(51H)=25H

MOV 52H, #70H; (52H)=70H

⒋ MOVC

A,@A+DPTR 与 MOVX

8.要完成以下的数据传送,应如何用

MCS-51指令实现?

(4)片外RAM 1000H单元的内容送片内

RAM 20H单元;

MOV

DPTR, #1000H;

MOVX A, @DPTR;

MOV

20H, A;

⒑已知:(A)=83H,(R0)=17H,

(17H)=34H,

请写出下列程序段执行后A中的内容。

LOOP1:MOV A,@R0 ;取相邻两单元中的数 MOV 30H,A ; 低地址内容→30H