时序逻辑电路典型例题分析

第9章 时序逻辑电路部分习题解答

第9章时序逻辑电路习题解答9.1 d R端和d S端的输入信号如题9.1图所示,设基本RS触发器的初始状态分别为1和0两种情况,试画出Q端的输出波形。

题9.1图9.2 同步RS触发器的CP、R、S端的状态波形如题9.2图所示。

设初始状态为0和1两种情况,试画出Q端的状态波形。

题9.2图9.3 设主从型JK触发器的初始状态为0,J、K、CP端的输入波形如题9.3图所示。

试画出Q端的输出波形(下降沿触发翻转)。

解:9.4 设主从型JK触发器的初始状态为0,J、K、CP端输入波形如题9.4图所示。

试画出Q端的输出波形(下降沿触发翻转)。

如初始状态为1态,Q端的波形又如何?解:第9章时序逻辑电路2259.5 设维持阻塞型D触发器的初始状态为0,D端和CP端的输入波形如题9.5图所示,试画出Q端的输出波形(上升沿触发翻转)。

如初始状态为1态,Q端的波形又如何?题9.3图题9.4图题9.5图9.6 根据CP时钟脉冲,画出题9.6图所示各触发器Q端的波形。

(1)设初始状态为0;(2)设初始状态为1。

(各输入端悬空时相当于“1”)题9.6图第9章时序逻辑电路2269.7 题9.7图所示的逻辑电路中,有J和K两个输入端,试分析其逻辑功能,并说明它是何种触发器。

题9.7图9.8 根据题9.8图所示的逻辑图和相应的CP、d R、D的波形,试画出Q1和Q2端的输出波形。

设初始状态Q1=Q2=0。

题9.8图第9章 时序逻辑电路 2279.9 试用4个D 触发器组成一个四位右移移位寄存器。

设原存数码为“1101”,待存数码为“1001”。

试列出移位寄存器的状态变化表。

9.10 在题9.10图所示的逻辑电路中,试画出Q 1和Q 2端的输出波形,时钟脉冲是一连续的方波脉冲。

如果时钟脉冲频率是4000Hz ,那么Q 1和Q 2波形的频率各为多少?设初始状态Q 1=Q 2=0。

9.11 题9.11图是用主从JK 触发器组成的8421码异步十进制计数器,试分析其计数功能。

习题5 时序逻辑电路分析与设计 数电 含答案.

1习题 5时序逻辑电路分析与设计数字电子技术[题 5.1] 分析图题 5.1所示电路的逻辑功能。

并画出电路在输入端 X 收到序列为 10110100时的时序图。

解:首先从电路图写出它的驱动方程:1221212(D X Q D X Q Q X Q Q ⎧=⎪⎨==+⎪⎩将上式代入 D 触发器的特性方程后得到电路的状态方程:1121212(n n Q X Q Q X Q Q ++⎧=⎪⎨=+⎪⎩电路的输出方程为:12Y X Q Q =根据状态方程和输出方程画出的状态转换图如下图示:所以,电路的功能是可重叠 111序列检测器。

当 X 收到 10110100时的时序图是:X/YC PX Q1 Q22[题 5.2] 分析图题 5.2所示电路的逻辑功能。

并画出电路在连续的时钟脉冲作用下的时序图。

解:首先从电路图写出它的驱动方程:1121112J Q Q K J Q Q ⎧=+⎪⎨==+⎪⎩ 2122212J Q Q K J Q Q =+⎧⎨==+⎩将上式代入 D 触发器的特性方程后得到电路的状态方程:1111111212222212n n Q J Q K Q Q Q Q J Q K Q Q Q ++⎧=+=⎪⎨=+=⎪⎩电路的输出方程为:12Y Q Q =根据状态方程和输出方程画出的状态转换图如下图示:图题 5.1 图题 5.2C P Q1 Q2 Z3所以,电路的功能是模 3记数器。

[题 5.3] 试画出“ 1011” 不可重叠序列检测器的原始状态图和原始状态表。

当输入信号 X 依序收到 1011时,输出 Z 为 1,否则 Z 为 0。

例如:当 X =0 1 0 1 1 0 1 1 0 1 1 0 0, 则 Z =0 0 0 0 1 0 0 0 0 0 1 0 0。

解:原始状态图如下所示:[题 5.4] 试画出“ 1001” 可重叠序列检测器的原始状态图和原始状态表。

该电路在输入端 X 依序收到 1001时,输出 Z 为 1。

《时序逻辑电路》练习题及答案 (2)

《时序逻辑电路》练习题及答案[6.1]分析图P6-1时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。

图P6-1[解]驱动方程:311QKJ==,状态方程:nnnnnnn QQQQQQQ13131311⊕=+=+;122QKJ==,nnnnnnn QQQQQQQ12212112⊕=+=+;33213QKQQJ==,,nnnn QQQQ12313=+;输出方程:3QY=由状态方程可得状态转换表,如表6-1所示;由状态转换表可得状态转换图,如图A6-1所示。

电路可以自启动。

表6-1nnn QQQ123YQQQ nnn111213+++nnn QQQ123YQQQ nnn111213+++00000 101001 1001001000110100010010 111011 1000 1011 1010 1001 1图A6-1电路的逻辑功能:是一个五进制计数器,计数顺序是从0到4循环。

[6.2]试分析图P6-2时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。

A为输入逻辑变量。

图P6-2[解]驱动方程:21QAD=,212QQAD=状态方程:nn QAQ211=+,)(122112nnnnn QQAQQAQ+==+输出方程:21QQAY=表6-2由状态方程可得状态转换表,如表6-2所示;由状态转换表可得状态转换图,如图A6-2所示。

电路的逻辑功能是:判断A是否连续输入四个和四个以上“1”信号,是则Y=1,否则Y=0。

图A6-2[6.3]试分析图P6-3时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,检查电路能否自启动。

图P6-3[解]321QQJ=,11=K;12QJ=,312QQK=;23213QKQQJ==,=+11nQ32QQ·1Q;2112QQQ n=++231QQQ;3232113QQQQQQ n+=+Y = 32QQ电路的状态转换图如图A6-3所示,电路能够自启动。

第5章时序逻辑电路习题解答分析

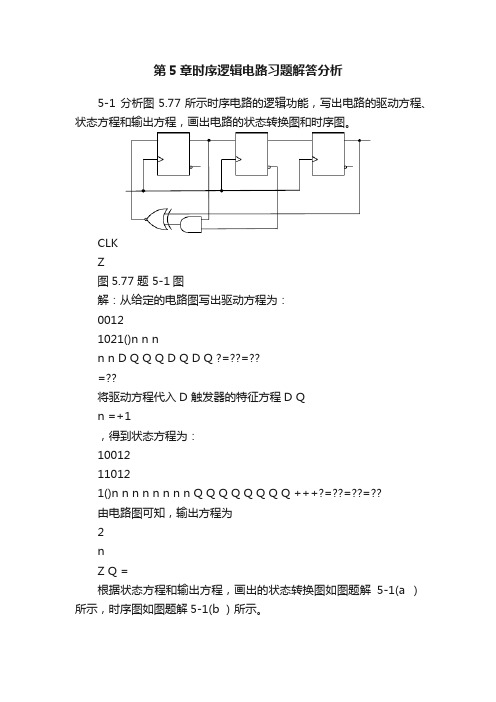

第5章时序逻辑电路习题解答分析5-1 分析图5.77所示时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图。

CLKZ图5.77 题 5-1图解:从给定的电路图写出驱动方程为:00121021()n n nn n D Q Q Q D Q D Q ?=??=??=??将驱动方程代入D 触发器的特征方程D Qn =+1,得到状态方程为:10012110121()n n n n n n n n Q Q Q Q Q Q Q Q +++?=??=??=??由电路图可知,输出方程为2nZ Q =根据状态方程和输出方程,画出的状态转换图如图题解5-1(a )所示,时序图如图题解5-1(b )所示。

题解5-1(a )状态转换图1Q 2/Q ZQ题解5-1(b )时序图综上分析可知,该电路是一个四进制计数器。

5-2 分析图5.78所示电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。

A 为输入变量。

YA图5.78 题 5-2图解:首先从电路图写出驱动方程为:()0110101()n n n n nD AQ D A Q Q A Q Q ?=?==+??将上式代入触发器的特征方程后得到状态方程()101110101()n n n n n n nQ AQ Q A Q Q A Q Q ++?=?==+??电路的输出方程为:01n nY AQ Q =根据状态方程和输出方程,画出的状态转换图如图题解5-2所示YA题解5-2 状态转换图综上分析可知该电路的逻辑功能为:当输入为0时,无论电路初态为何,次态均为状态“00”,即均复位;当输入为1时,无论电路初态为何,在若干CLK 的作用下,电路最终回到状态“10”。

5-3 已知同步时序电路如图5.79(a)所示,其输入波形如图5.79 (b)所示。

试写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图,并说明该电路的功能。

时序逻辑电路分析举例

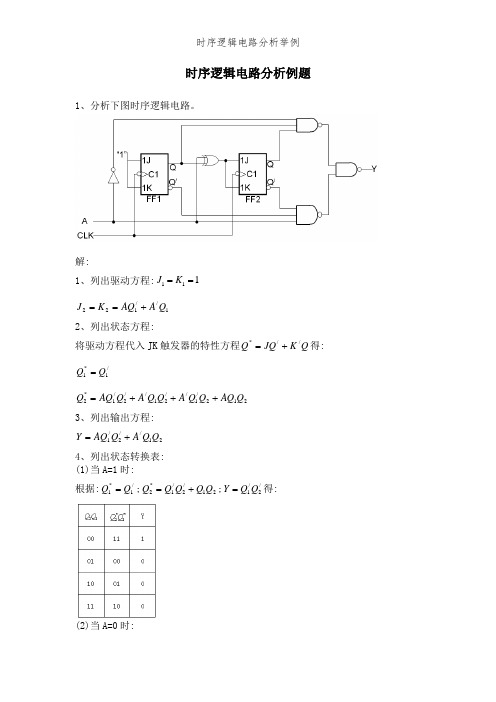

时序逻辑电路分析例题1、分析下图时序逻辑电路。

解:1、列出驱动方程:111==K J1//122Q A AQ K J +==2、列出状态方程:将驱动方程代入JK 触发器的特性方程Q K JQ Q //*+=得:/1*1Q Q =212/1//21//2/1*2Q AQ Q Q A Q Q A Q AQ Q +++=3、列出输出方程:21//2/1Q Q A Q AQ Y +=4、列出状态转换表: (1)当A=1时:根据:/1*1Q Q =;21/2/1*2Q Q Q Q Q +=;/2/1Q Q Y =得:(2)当A=0时:根据:/1*1Q Q =;2/1/21*2Q Q Q Q Q +=;21Q Q Y =得:5、画状态转换图:6、说明电路实现的逻辑功能:此电路就是一个可逆4进制(二位二进制)计数器,CLK 就是计数脉冲输入端,A 就是加减控制端,Y 就是进位与借位输出端。

当控制输入端A 为低电平0时,对输入的脉冲进行加法计数,计满4个脉冲,Y 输出端输出一个高电平进位信号。

当控制输入端A 为高电平1时,对输入的脉冲进行减法计数,计满4个脉冲,Y 输出端输出一个高电平借位信号。

2、如图所示时序逻辑电路,试写出驱动方程、状态方程,画出状态图,说明该电路的功能。

解:驱动方程⎩⎨⎧=⊕=1010K Q X J n ⎩⎨⎧=⊕=111K Q X J n 状态方程()()n n n n n n n n n n n n nn QXQ Q Q X Q Q X QQ Q X Q Q X Q Q X Q 0111101011011+=⊕=+=⊕=++1J 1K C11J 1K C11Q 0Q CPXZ=1=1=1&FF 1FF 011输出方程()01Q Q X Z ⊕=1、 状态转换表,如表所示。

状态转换图,略。

2、这就是一个3进制加减计数器,当X=0时为加计数器,计满后通过Z 向高位进位;X=1时为减计数器,计满后通过Z 向高位借位;能自启动。

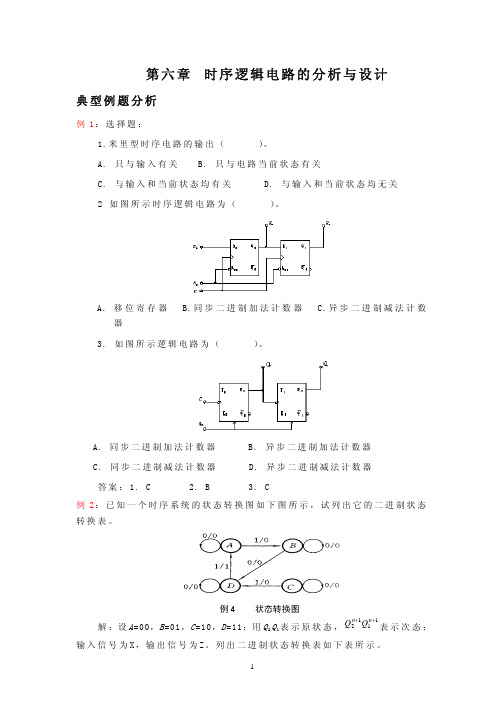

第六章 时序逻辑电路的分析与设计典型例题

解:解题步骤如下: ( 1) 求 激 励 输 入 议 程 :

⎧ J 3 = Q2 , ⎨ ⎩K 3 = Q2 ⎧ J 2 = Q1 , ⎨ ⎩ K 2 = Q1 ⎧ J 1 = Q3 ⊕Q1 ⎨ ⎩K1 = J 1

因 为 将 J 3 = Q 2 , K 3 = Q2 代 入 J - K 触 发 器 次 态 方 程 , 有

3

n +1 励 方 程 D3、 D2、 D1中 , 然 后 根 据 D触 发 器 次 态 方 程 Q = D , 可 知 所 有 的 非 工

作 状 态 都 能 进 入 工 作 状 态 , 即 101→ 001; 110→ 101→ 001; 111→ 001。 因 此 电路可以自启动。 ( 6) 画 完 整 状 态 转 换 图 如 下 图 所 示 。

J 1 = Q3 Q1 + Q3 Q1 + Q2 Q1 = Q3 ⊕ Q1 + Q2 Q1

修改后,具有自启动功能的电路如下图所示。

修改后的可自启动电路

5

Q1n +1 0 0 1 1 0

D3

0 1 0 0 0

D2

1 0 0 1 0

D1

0 0 1 1 0

0 1 0 0 0

1 0 0 1 0

( 3) 求 激 励 输 入 方 程 组 。 首 先 要 根 据 状 态 转 换 真 值 表 , 画 D3、 D2、 D1的 卡 诺 图 , 然 后 通 过 卡 诺 图 化 简 得 到 激 励 输 入 方 程 。 D3、 D2、 D1的 卡 诺 图 如 下 图所示。

S0— — 为 初 始 状 态 以 及 不 属 于 以 下 定 义 的 状 态 ; S1— — 收 到 首 个 1; S2— — 收 1 后 再 收 1; S3— — 收 11 后 再 收 0; S4— — 收 110 后 再 收 1。

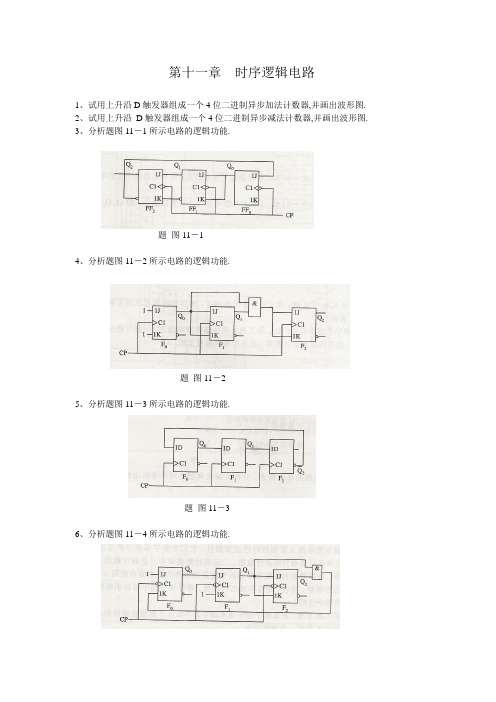

第十一章时序逻辑电路

第十一章时序逻辑电路

1、试用上升沿D触发器组成一个4位二进制异步加法计数器,并画出波形图.

2、试用上升沿D触发器组成一个4位二进制异步减法计数器,并画出波形图.

3、分析题图11-1所示电路的逻辑功能.

题图11-1

4、分析题图11-2所示电路的逻辑功能.

题图11-2

5、分析题图11-3所示电路的逻辑功能.

题图11-3

6、分析题图11-4所示电路的逻辑功能.

题图11-4

7、分析题图11-5所示电路的逻辑功能.

题图11-5

8、已知计数器波形如题图11-6所示,试确定该计数器的模.

题图11-6

9、试分析题图11-7所示的由74LS290构成的各电路分别组成几进制计数器.

题图11-7

10、试分析题图11-8所示的由74LS290构成的电路组成几进制计数器.

题图11-8

11、试分析题图11-9所示的由74LS161构成的电路组成几进制计数器.

题图11-9

12、试用74LS290构成九进制计数器

13、试用74LS161构成九进制计数器

14、试用74LS290构成86进制计数器

15、试用74LS161构成82进制计数器。

时序逻辑电路习题解答解读

自我测验题1.图T4.1所示为由或非门构成的基本SR锁存器,输入S、R的约束条件是。

A.SR=0B.SR=1C.S+R=0D.S+R=1QG22QRS图T4.1图T4.22.图T4.2所示为由与非门组成的基本SR锁存器,为使锁存器处于“置1”状态,其RS⋅应为。

A.RS⋅=.RS⋅=10D.RS⋅=113.SR锁存器电路如图T4.3所示,已知X、Y波形,判断Q的波形应为A、B、C、D 中的。

假定锁存器的初始状态为0。

XYXYABCD不定不定(a)(b)图T4.34.有一T触发器,在T=1时,加上时钟脉冲,则触发器。

A.保持原态B.置0C.置1D.翻转5.假设JK触发器的现态Q n=0,要求Q n+1=0,则应使。

A.J=×,K=0B.J=0,K=×C.J=1,K=×D.J=K=16.电路如图T4.6所示。

实现AQQ nn+=+1的电路是。

A AA AA .B .C .D .图T4.67.电路如图T4.7所示。

实现n n Q Q =+1的电路是 。

CPCPCPA .B .C .D .图T4.78.电路如图T4.8所示。

输出端Q 所得波形的频率为CP 信号二分频的电路为。

1A .B .C .D .图T4.89.将D 触发器改造成TTQ图T4.9A .或非门B .与非门C .异或门D .同或门 10.触发器异步输入端的作用是。

A .清0B .置1C .接收时钟脉冲D .清0或置1 11.米里型时序逻辑电路的输出是。

A .只与输入有关B.只与电路当前状态有关C.与输入和电路当前状态均有关D.与输入和电路当前状态均无关12.摩尔型时序逻辑电路的输出是。

A.只与输入有关B.只与电路当前状态有关C.与输入和电路当前状态均有关D.与输入和电路当前状态均无关13.用n只触发器组成计数器,其最大计数模为。

A.n B.2n C.n2D.2 n14.一个5位的二进制加计数器,由00000状态开始,经过75个时钟脉冲后,此计数器的状态为:A.01011B.01100C.01010D.00111图T4.1516.电路如图T4.16所示,假设电路中各触发器的当前状态Q2Q1Q0为100,请问在时钟作用下,触发器下一状态Q2 Q1 Q0为。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第六章时序逻辑电路典型例题分析第一部分:例题剖析触发器分析例1在教材图6.1所示的基本RS 触发器电路中,若R, S 的波形如图P6」(a )和(b ), 试分别画出对应的Q 和Q 端的波形。

豆R J SS解:基本RS 触发器,当R 、£同时为0时,输岀端Q 、Q 均为1,当R=0. S=1 时,输岀端Q 为0、Q 为1,当4 灵1时,输岀保持原态不变,当R=l.灵0时,输出 端Q 为1、Q 为0,根据给左的输入波形,输岀端对应波形分别见答图P6」(a )和(b )« 需要注意的是,图(a )中,当R 、£同时由0 (见图中h )变为1时,输出端的状态分析 时不好确定(见图中t2),图中用虚线表示。

R _1S」LJ U L_S -LTUTJtl t2 t3Q "LTU• • • • Q _lQLJL.J -◎ -------------(a)(b)答图P6.1例2在教材图623 (a )所示的门控RS 触发器电路中,若输入S . R 和E 的波形如图 P6.2 (a )和(b ),试分别画岀对应的输岀Q 和Q 端的波形。

ER _n_ri_n_n_ s J ~LTU1_解:门控RS 触发器,当E=1时,实现基本RS 触发器功能,即:R=0 ( 41)、S=1R J I ---- 1 ~LJ£__________ I_L(a)图 P6.2(b)(S=0),输岀端Q 为1、◎为0; R=1 ( R=0). S=0 ( S=1)输出端Q 为0. ©为1:当E=0 时,输出保持原态不变。

输出端波形见答图P6.2,例3在教材图6.2.5所示的D 锁存器电路中,若输入D 、E 的波形如图P6.3 (a)和(b) 所示,试分别对应地画岀输出Q 和Q 端的波形。

E JWWWLDD _I~解:D 锁存器,当E=1时,实现D 锁存器功能,即:Q n+I =D,当E=0时,输岀保持原 态不变。

输出端波形见答图P6.3OD J~L-n--rL D -Ji_i ~o^LQQ Uu P oHJ-1 i~n(a)答图P6.3(b)例4在图P6.4 (a)所示的四个边沿触发器中,若已知CP 、A 、B 的波形如图(b)所示, 试对应画出其输出Q 端的波形。

设触发器的初始状态均为0。

R _n_n_n_n_ s J I —ru — Q_J ~~u~~u"■': Q I__n__n__:....;R J~I _____ I ~Uq _n _________________Q答图 P6.2(b )(a)图(b)(a)CPC -----------------------------------------------(b)解:图中各电路为具有异步控制信号的边沿触发器。

图(a)为边沿D触发器,CP上升沿触发,Q严A,异步控制端S D接信号C (R D =0),当C=1时,触发器被异步置位,输出CT-1 ;图(b〉为边沿JK触发器,CP上升沿触发,Q2n+1= A Q2n+ BQ2n ,异步控制端瓦)接信号C ( S D=1),当C=0时,触发器被异步复位,输岀Q n+1=0:图(c)为边沿D触发器,CP下降沿触发,Q严*=A,异步控制端弘接信号C ( Ro=l),当C=0时,触发器被异步置位,输出Q n+,= 1:图(d)为边沿JK触发器,CP下降沿触发,Q严—A Q4n + BQ4n ,异步控制端R D接信号C (S D=0),当C=1时,触发器被异步复位,输出Q n+,=0o 对应输出波形见答图P6.4所示。

CP ―I _I_I _I_I _I_I _I__I _I__I _I__I ~I—A」I ----------------------- 1 I ----------------- LB ___________________C ------------------------------------------ 1 _______Qi ----------------------------------------------- 1 _------- 1~I ---------- 1I -------------答图P6.4例5边沿触发器电路如图P6.5 (a)所示。

试根据图(b)中CP. A的波形,对应画出输岀Q 和Q?的波形。

解:电路是带异步控制信号的触发器电路•当Q口时,Qi n+,=Oc Qi是边沿JK触发器,Q严一Qi n, CPT降沿触发:Q2是边沿D触发器,Q2*=Qr,A信号的上升沿触发。

输出端波形见答图P6.5,A —II_II_ LCP -------1 I -----Qi —I I ------------Q2 ---------- 11—答图P6.5例6试分析图P6.6由边沿触发器组成的电路。

列出状态转换表、画出状态转换图,说明功能。

图P6.6解:列出驱动方程:Ji= K l=l, J2= K2=A㊉QC写出状态方程:Q严一Qi n , Q2n+1 =A©Qi n© Qz n,写出输岀方程:Y= AQ2n Qi n+A Q2n Qi"设初态.求次态,列出真值表:图P6.5(b)1CPACPAQF QF Q 严 Q 严1 Y0 0 0 1 0 01] 1 1 0 0 1 0 1 1 0 1 1 0 0 10 0 1 1 1 11] 1 0 0 0 1 0 0 1 01 11当A=0时,四进制加法计数器:当A=1时,四进制减法汁数器。

计数器分析及脉冲波形的产生与整形例1・同步四位二进制加法讣数器T4161功能表如图,分析以下电路为几进制计数器。

解:Q3Q2Q1Q00000—►OOOl -H»1G-HK>1 i OlOdOlO 卜+0110 t mi t 1 ] 10 Jl 101 J 11(XM —1011<—1010<-4001-4-4000当计数器输出为Q3Q2Q1Q 尸1100 (过渡态)时, 乔6计数器立即淸零。

(异步清零〉Q3Q2Q1Q0—M)01G~H)01 J —► 0100-X)10i —>0110I0111I1100-^ 1011-4—1010-4-4001-4—KMM)结果为N=12进制计数器cQ3 Q2 QI Qo51 52 T4161LDRDCP _CPD3 r>2 Dl DOCP R D L D S I S2 工作状态X 0 x X X清零1 10 X X 预置数 X 111保持(包括C 的状态) x 1 1 x 0保持 t 1 1 1 1计数第三步 ooogfoooi & OT4161功能表国写出清写瑤的 方程及译码状态R D =Q?Q2S L D M CP 工作状态 0 1 0 t 加法计数 0 1 1 t 减法计数 x 0 x x预置数 11 x X保持例2・用74LS161同步四位二进制加法计数器构成的汁数电路如图,试分析说明为几进 制计数。

例3・同步四位二进制可逆计数器T4191电路及功能表如下,分析电路为几进制计数器, 如何工作,画岀状态转换图。

解:CP R D L D S I S2 工作状态 x 0 x x x 清零t 1 0 x x 预置数x 1 1 0 1 保持(包拾C 的状态)x 11 x 0 保持 t 11 1 1计数第一步僅曲74LS161状态图Q3Q2Q1Q0OOOOfXXn fXHQ-XWli OKXKHOKHIO fJmi0111tI1110-4—1101-4—1100-4-^0ll-<—1010^-1001^-1000图写岀k 數轴的 方程及译码状态1___ 当计数器输出为QsQiQiQ 尸10101也工尊心 此 LD -Q 3Q 1时等到一个时钟脉冲到达,计数器 Q J Q Z Q I Q O ^D J IW I D O H )011O (同步置数)第兰步画出有效状态循环:结果为N=8的计数器74LS16I 功能表 Q3Q2Q1Q0RD0011 fOiooTinoi Tpi /OLDT4191功能表1 •由功能表和电路可知:当M=1时为减法计数,且LD 与CP 无关。

2.LD^Qo, 当计数器输出为Q3Q2Q I Q O =O1O1 (过渡态)时,LD=O,此时计数器的输出立即被置为 Q3Q2Q1Q O =D3D2D1D O =1100。

(异步置数) 3 •有效状态循环图:4•结果为N=7进制计数器。

例4・同步四位二进制可逆讣数器T4191电路及功能表如下,分析电路为几进制计数器, 如何工作,画岀状态转换图解:1 •由功能表和电路可知:当M=0时为加法计数,且LD 与CP 无关。

2 丄 D=Q3Q2Qh当计数器输出为Q3Q2Q1QO=111O (过渡态)时,LD=0,此时计数器的输出立即被置 为 Q3Q2Q1QO=D3D2D1DO =0010o (异步置数)3 •有效状态循环图:0010->0011—>0100—>0101—>0110—>0111—>1000 1110<T101—1100KH1T010 —1001S LD M CP工作状态 o i o T加法计数 0 1 1 t 减法计数x 0 x x 预置数11XX保持1100—>1011—>1010 1001010H 0110^ 01 lb —1000T4191功能表4•结果为N=12进制计数器。

例5:同步四位二进制可逆计数器T4191电路及功能表如下,分析电路为几进制计数器. 如何工作,画岀状态转换图。

2囲和电嘯®Q3Q2Q1Q O =D3D2D1D O =0011 o (异步置数)3 •有效状态循环图:ooii^ioo —^)ior-n )i io —>011 r-^iooov l\ \ 11 lk …1110<—1101^—1100^01k —1010^—10014•结果为N=12进制计数器。

例6:由JK 边沿触发器构成的同步时序逻辑电路如图,试分析电路,写出驱动方程、状态 方程.输出方程,画出状态表、状态方程及状态转换图,说明电路的逻辑功能。

驱动方程 J1=Q3 J2=Q3Q1 J3=Q TK1=Q3Q2 K2=Q3Q1K3=Q2Q1 输出方程C=Q3Q2Q1S L D M CP工作状态 0 1 0 t 加法计数 0 1 1 t 减法计数x 0 x x预置数 11 X X保持JI Q1 J3 Q3 解:T4191功能表KI OfJ2 Q2 K3 Q3K2 Q2时钟方程CP1二CP2二CP3二CP 同步时序电路。