简易频率特性测试仪的设计与制作

简易频率特性测试仪论文设计

2013年全国大学生电子设计竞赛简易频率特性测试仪(E题)【本科组】2013年9月6日摘要本实验以DDS芯片AD9854为信号发生器,以单片机STM32F103RBT6为核心控制芯片。

系统由5个模块组成:正弦扫频信号模块,待测阻容双T网络模块,整形滤波模块,A/D转换模块及显示模块。

先以单片机送给AD9854控制字产生1MHZ —40MHZ的扫频信号,经过阻容双T网络检测电路,两路路信号通过AD9283对有效值进行采集后进入单片机进行幅值转换,最终由TFTLCD显示输出。

ABSTRACTIn this experiment, the DDS chip AD9854 as the signal generator, MCU STM32F103RBT6 as the core control chip, and with FPGA as auxiliary, and on the peripheral circuit to realize the detection of amplitude frequency and phase frequency. The system comprises 6 modules: signal sine sweep signal module, the measured resistance capacitance of double T module, filter module, A/D conversion module and display module. The first single-chip microcomputer to AD9854 control word generate sweep signal of 10MHZ - 40MHZ, the resistance and capacitance of double T detection circuit, two road signals are collected on the effective value through the AD9283 into the microcontroller to amplitude conversion, the LCD display output, finally to complete the amplitude frequency and phase frequency of simple test.目录1系统方案 (1)1.1 AD9854模块的论证与选择 (1)1.2 单片机控制系统模块的论证与选择 (1)1.3 显示模块的论证与选择 (2)1.3 电源模块的论证与选择 (2)2系统理论分析与计算 (2)2.1 系统原理的分析 (2)2.2 滤波器的设计 (3)2.2.1 滤波器电参数的计算 (3)2.2.2 Multisim仿真电路 (3)2.3 ADC设计 (4)2.3.1 AD9283 匹配电路设计 (4)2.3.2 电路图 (5)2.4 被测网络设计 (5)2.4.1 被测网络的电参数选择 (5)2.4.2 Multisim仿真 (5)3电路与程序设计 (6)3.1电路的设计 (6)3.1.1系统总体框图 (6)3.1.2 正交扫频信号子系统框图与电路原理图 (7)3.1.3 单片机显示系统模块子系统框图与电路原理图 (8)3.1.4电源 (9)3.2程序的设计 (9)3.2.1程序功能描述与设计思路 (9)3.2.2程序流程图 (10)4测试方案与测试结果 (11)4.1测试方案 (11)4.2 测试条件与仪器 (12)4.3 测试结果及分析 (13)4.3.1测试结果(数据) (13)4.3.2测试分析与结论 (13)附录1:电路原理图 (14)附录2:源程序 (16)简易频率测试仪(E题)【本科组】1系统方案本系统主要由AD9854模块、单片机控制系统模块、显示模块、电源模块组成,下面分别论证这几个模块的选择。

频率特性测量仪

频率特性测量仪摘要该频率特性测量仪采用89C52最小系统为控制核心,主要由正弦波发生器、数据采集存储、处理、显示、打印等功能模块组成。

通过键盘控制来实现幅频特性和相频特性的测量,包括参数预置、点测结果的显示与打印,以及用普通示波器单独或同时显示幅频特性曲线和相频特性曲线。

本系统采用可编程器件(CPLD)和DDS技术实现信号发生电路,频率值与步长均能灵活准确地预置。

被测网络采用有源带通双T网络,中心频率及带宽均达到要求:f0=5KHZ 、50Q。

另外,我们还制作了线性稳压电源,扩展了幅频特性曲线和相频特性曲线的打印功能。

设计中,较好地应用了EDA工具,软件设计模块化,总体较好地完成了基本部分和发挥部分的要求。

关键词:DDS,EDA,CPLD,双T网络,有源滤波,鉴相,数据采集一.总体方案论证㈠.总体设计思想本频率特性测试仪的设计思想为:1、尽量做到测试准确,自动化、智能化程度高,操作方便。

2、尽量采用大规模集成电路如可编程逻辑器件等,使系统简洁、调试修改方便,可靠性高。

3、尽量采用现代化设计工具和EDA软件平台,使设计快捷,先进。

㈡.总体设计方案基于以上设计思想,本系统采用单片机和可编程器件(CPLD)作为控制及数据处理的核心,将设计任务分解为正弦信号发生器、被测网络、数据采集与存储、幅频特性测量、相频特性测量、结果显示、打印等功能模块。

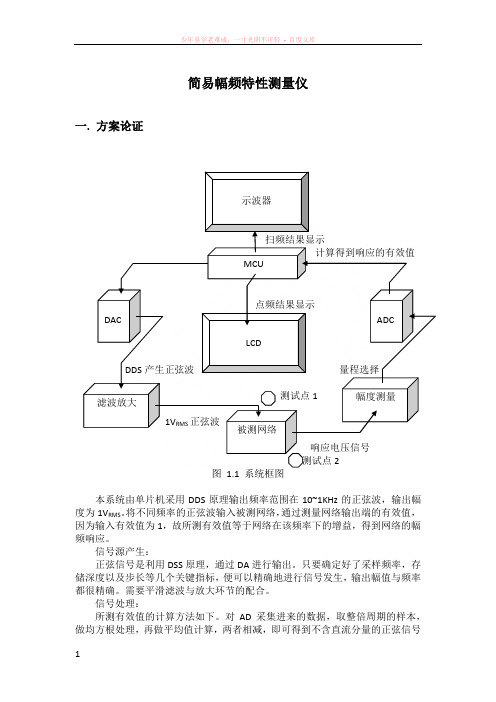

图1-1给出该系统的总体框图。

图1-1系统总框图如上图所示正弦波发生器采用DDS直接数字频率合成技术,其逻辑控制部分用可编程器件CPLD实现。

幅度测量采用峰值检波技术,相位测量则利用数字鉴相器实现。

检波电路和鉴相电路输出分别经A/D 采集后由89C52 读进存储在RAM 中,再经分析处理后输出到LED显示电路、波形显示控制电路或控制打印输出电路,以实现频率特性参数和频率特性曲线的显示或打印。

由于使用了89C52 单片机和CPLD器件,使系统具有很大的灵活性,便于实现各种复杂控制,从而能方便地对系统进行功能扩展和性能改进。

简易频率特性测试仪的设计

简易频率特性测试仪的设计加在前面:术业有专攻。

一般写一些东西我也不会在空间瞎发,弄的别人以为自己瞎显摆。

不过我觉得我们电子设计的过程确实值得其他小组学习一下,比如说老葛焊板子那种芯片的布局,还有我们用4个按键解决所有数字的设置的思想。

我希望大家看到文章的时候不是觉得怎么吊炸天,其实我们这种水平比我们吊炸天的多了去。

我们之所以有敢厚着脸皮把这么次的设计思想分享出来,主要希望能把其中的某一些发光点分享给大家,同时希望他人给我们的更宝贵的意见和建议。

----end----电子设计三中,仪器仪表组的第一个题目,是简易频率特性测试仪的设计。

这个题目取自2013年的E题:简易频率特性测试仪(E 题)。

为了纪念近一个月的工作,特撰以此文纪念我们第七小组历经了的艰辛岁月。

在此,感谢组长葛家瑾大神、还有范一华同学的辛勤付出,还有李煜及其他一些学长的帮助。

特发上图,以作纪念。

在本次完成题目的过程中,葛大神早早完成了公式推导、电路理论和原理的分析,并组织我们在工作上分工(虽然他好像对“被我和范一华排挤去焊电路板”很不满意私下抱怨并耿耿于怀,哈哈)。

下面我简单的回顾一下我们的这次设计:其中,有关硬件电路的部分是葛大神负责的,我只是略懂了原理,故仅仅略述。

我主要承担的是AD采样部分的程序,还有就是通过操作液晶屏和按键实现的程序的总体逻辑控制程序。

范一华同学主要完成的是AD9854部分的程序,正弦波输出及其幅度补偿,还有扫频部分的程序。

下面,我从入手这道题目的开始状态,来一步步回顾一下。

下面,先把题目贴出来:/*=======================开始贴题目=======================*/【本科组】一、任务根据零中频正交解调原理,设计并制作一个双端口网络频率特性测试仪,包括幅频特性和相频特性,其示意图如图 1 所示。

二、要求1.基本要求制作一个正交扫频信号源。

(1)频率范围为1MHz~40MHz,频率稳定度≤10^-4;频率可设置,最小设置单位100kHz。

频率特性测试仪的设计

频率特性测试仪的设计1引言频率特性是一个网络性能最直观的反映。

频率特性测试仪用于测量网络的幅频特性和相频特性,是根据扫频法的测量原理设计,是一种快速、简便、实时、动态、多参数、直观的测量仪器,可广泛应用于电子工程等领域。

由于模拟式扫频仪价格昂贵,不能直接得到相频特性,更不能打印网络的频率响应曲线,给使用带来诸多不便。

为此,设计了低频段数字式频率特性测试仪。

该测试仪采用数字直接频率合成技术专用的集成电路AD9851产生扫频信号,以单片机和FPGA为控制核心,通过A/D和D/A转换器等接口电路,实现扫频信号频率的步进调整、数字显示及被测网络幅频特性与相频特性的数显等。

该系统成本低廉,扫频范围较宽(10 Hz〜1MHz), 可方便地与打印机连接,实现频率特性曲线的打印。

2多功能计数器设计方案2.1幅频和相频特性测量方案方案1:利用公式H(s)=R(s)/E(s),以冲击函数为激励,则输出信号的拉氏变换与系统函数相等。

但是产生性能很好的冲击函数比较困难,需要对采集的数据做FFT变换,需要占用大量的硬件和软件资源,且精度也受到限制。

方案2:扫频测试法。

当系统在正弦信号的激励下,稳态时,响应信号与输入激励信号频率相同,其幅值比即为该频率的幅频响应值,而两者的相位差即为相频特性值。

采用频率逐点步进的测试方法。

无需对信号进行时域与频域的变换计算,通过对模拟量的测量与计算完成,且精度较高。

综上所述,选择方案2。

2.2扫描信号产生方案方案1:采用单片函数发生器。

其频率可由外围电路控制。

产生的信号频率稳定度低,抗干扰能力差,灵活性差。

方案2:采用数字锁相环频率合成技术。

但锁相环本身是一个惰性环节,频率转换时间长,整个测试仪的反应速度就会很慢,而且带宽不高。

方案3:采用数字直接频率合成技术(DDFS)。

以单片机和FPGA为控制核心,通过相位累加器的输出寻址波形存储器中的数据,以产生固定频率的正弦信号。

该方案实现简单,频率稳定,抗干扰能力强。

(完整)年简易频率特性测试仪

摘要本设计的实现的简易频率测试仪中主要包括正交扫频信号源的设计、被测网络的设计、信号混合电路的设计、低通滤波器的设计以及模数转换和显示模块的设计。

利用直接数字式频率合成器AD9854实现正交扫频信号源的设计,被测网络我们采用LRC谐振电路设计实现,利用AD835设计了乘法混合电路,自己利用滤波器设计软件设计了滤波器软件,利用C8051f020单片机最小系统控制高速AD7862完成模数的转换,最后在LCD屏上显示得到的相频曲线和幅频曲线.本系统中设计中我们及设计完成了要求完成任务外,设计了友好人机交互接口,实现了频率可设置、在实现的过程中不仅能够改变频率,而且可以改变频率改变的分度值,最重要的是我们不论是改变频率还是频率改变的分度值我们都使用了同一个按键,设置了确认键让使用者有一个良好的体验。

关键词:简易频率测试仪,AD9854,正交扫频信号源,C8051f020单片机AbstractThe design of a simple realization of the frequency measuring instrument mainly includes orthogonal frequency sweep signal source design, the tested network design, mixed signal circuit design, the design of low pass filter and analog to digital conversion and display module design。

The design of direct digital frequency synthesizer AD9854 to achieve orthogonal frequency sweep signal source, the measured network we use LRC resonant circuit design, the multiplication of mixed circuit design using AD835, their use of filter design software to design filter software, using C8051f020 single chip minimize system control of high speed AD7862 analog—to-digital conversion, finally shows the phase frequency curve the amplitude frequency curve in the LCD screen。

频率特性测试仪设计与总结报告(国赛一等奖)

频率特性测试仪设计与总结报告(国赛一等奖) 频率特性测试仪设计与总结报告(国赛一等奖)频率特性测试仪设计与总结报告作者:仇飞、徐川川、王雅灏摘要:本设计以ARM红牛开发板作为整个系统的控制核心,通过软件产生频率线性变化的正弦波,并将其提供给被测网络测试。

变化前后正弦波使用软件测试,并计算其幅频特性和相频特性。

使用阻容双T网络制作被测网络。

关键词:ARM开发板、阻容双T网络、加法器。

一、方案论证与选择总体方案设计:根据题目要求,频率特性测试仪的功能是能够将输出可调正弦波给被测电路,并测量经过测量电路后正弦波的变化,从而得出幅频特性和相频特性。

①方案一:信号源采用RC正弦波振荡电路产生信号。

用R、C元件组成选频网络的振荡电路为RC正弦波振荡电路,该电路适于产生1Hz~1MHz范围内的低频信号。

振荡频率由R、C值决定。

需要改善输出电压幅度的稳定问题,在放大电路的负反馈回路里采用非线性元件来自动调整反馈的强弱来维持输出电压恒定。

所需信号源为频率连续变化信号,因此要随时改变R、C 值进而改变输出信号频率。

将产生的信号送至被测网络,变化后的信号和变化前信号同时送至集成有效值转换芯片AD637计算其有效值,经过A/D转换后,再使用模拟除法器得到其幅频特性。

该方案电路结构简单造价低,不需软件调试。

但对于测量相频特性较为困难。

原理框图如图一所示。

②方案二:使用DDS芯片AD9834产生正弦波信号,产生正弦波频率最高可到25MHz。

AD9834是由28位的相位累加器、正弦只读存储器和一个10位的DA构成的数字控制式振荡器。

利用直接数字合成技术,和AD9834内部的两个频率寄存器、FSK技术可以实现单周期内的频率切换,以及占空比调节的实现。

通过外部引脚控制或控制字控制频率寄存器和相位寄存器调节输出,可以改变输出波形种类。

原理图如下。

图一:方案一原理框图图二:方案二原理框图③方案三:使用ARM通过软件编程产生连续正弦波且频率在100Hz到100KHz内连续变化。

简易幅频特性测量仪设计

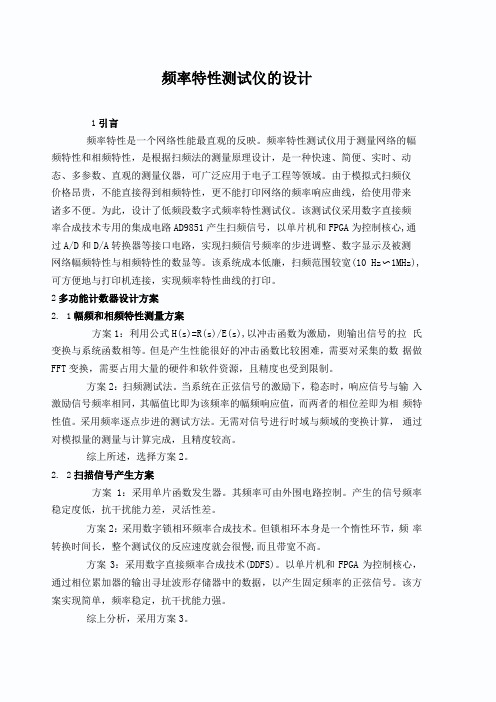

简易幅频特性测量仪一. 方案论证扫频结果显示计算得到响应的有效值点频结果显示DDS 产生正弦波 量程选择测试点11V RMS 正弦波响应电压信号测试点2本系统由单片机采用DDS 原理输出频率范围在10~1KHz 的正弦波,输出幅度为1V RMS 。

将不同频率的正弦波输入被测网络,通过测量网络输出端的有效值,因为输入有效值为1,故所测有效值等于网络在该频率下的增益,得到网络的幅频响应。

信号源产生:正弦信号是利用DSS 原理,通过DA 进行输出。

只要确定好了采样频率,存储深度以及步长等几个关键指标,便可以精确地进行信号发生,输出幅值与频率都很精确。

需要平滑滤波与放大环节的配合。

信号处理:所测有效值的计算方法如下。

对AD 采集进来的数据,取整倍周期的样本,做均方根处理,再做平均值计算,两者相减,即可得到不含直流分量的正弦信号MCU 被测网络DAC 滤波放大 ADC幅度测量LCD示波器有效值。

可以通过固定频率的点频方法测得特定点的响应,也可也通过频率步进得到一系列点的响应,最终绘得响应曲线。

最终结果通过示波器与液晶共同显示。

点测与扫测:DDS产生正弦波的方案,我们存储一个周期采样点的幅值信息,通过改变步长来达到不同频率输出。

在点频方式下,我们输出指定频率的正弦波,并读取响应电压信号,计算其有效值,即可知道所测网络在特定频率点的增益信息(幅频特性)。

在扫频方式下,由于10Hz步进到1KHz所需时间太长,而且参照我们需要完成的功能,我们加大步进量,以100Hz为步进长度,测出10~1KHz中的十个点,并通过插值等算法计算幅频响应曲线,在示波器上予以输出。

开始初始化显示菜单点测功能扫频功能设定频率采样并计算有效值频率步进采样并计算有效值显示响应有效值示波器显示曲线图 1.2 软件流程发挥部分:发挥部分主要有扫频功能,扩展频率范围,以及可控增益几部分。

扫频功能主要是对基础的点测功能的扩展,应用多次自动步进电测来得到幅频响应曲线。

课程设计实验报告(简易频率计)

实验二:简易电子琴一、实验目的(1)学习采用状态机方法设计时序逻辑电路。

(2)掌握ispLEVER 软件的使用方法。

(3)掌握用VHDL 语言设计数字逻辑电路。

(4)掌握ISP 器件的使用。

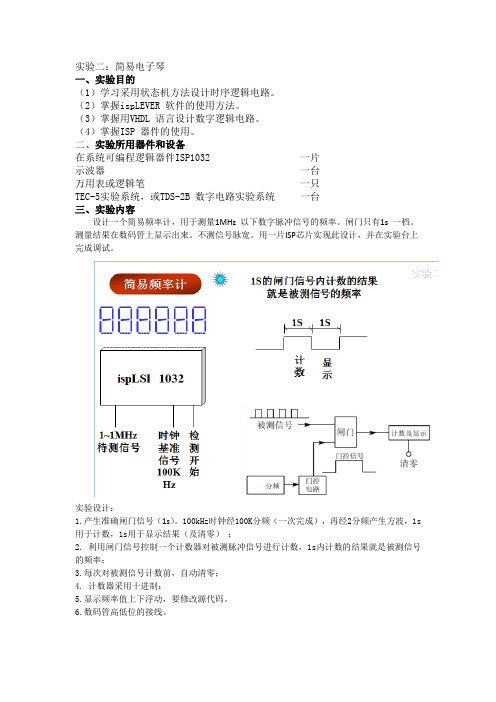

二、实验所用器件和设备在系统可编程逻辑器件ISP1032一片示波器一台万用表或逻辑笔一只TEC-5实验系统,或TDS-2B 数字电路实验系统一台三、实验内容设计一个简易频率计,用于测量1MHz 以下数字脉冲信号的频率。

闸门只有1s 一档。

测量结果在数码管上显示出来。

不测信号脉宽。

用一片ISP芯片实现此设计,并在实验台上完成调试。

实验设计:1.产生准确闸门信号(1s)。

100kHz时钟经100K分频(一次完成),再经2分频产生方波,1s 用于计数,1s用于显示结果(及清零);2. 利用闸门信号控制一个计数器对被测脉冲信号进行计数, 1s内计数的结果就是被测信号的频率;3.每次对被测信号计数前,自动清零;4. 计数器采用十进制;5.显示频率值上下浮动,要修改源代码。

6.数码管高低位的接线。

VHDL源代码:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity fget isport(clk:in std_logic; --输入时钟源 bclk:in std_logic;kout:out std_logic_vector(26 downto 0));end fget;architecture top of fget iscomponent divideport(clk1:in std_logic;cl:out std_logic;co:out std_logic;ro:out std_logic);end component;component gateport(bc1:in std_logic;cl1:in std_logic;co1:in std_logic;op:out std_logic_vector(26 downto 0));end component;component saveport(op1:in std_logic_vector(26 downto 0);ro1:in std_logic;eout:out std_logic_vector(26 downto 0));end component;signal scl:std_logic;signal sco:std_logic;signal sro:std_logic;signal sop:std_logic_vector(26 downto 0);BEGINu1:divide PORT MAP(clk,scl,sco,sro);u2:gate PORT MAP(bclk,scl,sco,sop);u3:save PORT MAP(sop,sro,kout);end;--闸门模块library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity gate isport(bc1:in std_logic;cl1:in std_logic;co1:in std_logic;op:out std_logic_vector(26 downto 0) --5个8421,一个七段译码);end;architecture art2 of gate iscomponent cnt10 --十进制计数模块port(clk2:in std_logic;en:in std_logic;--使能端clr:in std_logic;--重置qout:out std_logic_vector(3 downto 0 );cout:out std_logic);end component;component seventranse --七段模块port(clk6:in std_logic_vector(3 downto 0 );op2:out std_logic_vector(6 downto 0 ));end component;signal scout1:std_logic;--输出(十进制)signal scout2:std_logic;signal scout3:std_logic;signal scout4:std_logic;signal scout5:std_logic;signal scout6:std_logic;signal qout1:std_logic_vector(3 downto 0);--8421(下同)signal qout2:std_logic_vector(3 downto 0);signal qout3:std_logic_vector(3 downto 0);signal qout4:std_logic_vector(3 downto 0);signal qout5:std_logic_vector(3 downto 0);signal qout6:std_logic_vector(3 downto 0);signal op2: std_logic_vector(6 downto 0);--七段beginr1:cnt10 PORT MAP(bc1,co1,cl1,qout1,scout1);r2:cnt10 PORT MAP(scout1,co1,cl1,qout2,scout2);r3:cnt10 PORT MAP(scout2,co1,cl1,qout3,scout3);r4:cnt10 PORT MAP(scout3,co1,cl1,qout4,scout4);r5:cnt10 PORT MAP(scout4,co1,cl1,qout5,scout5);r6:cnt10 PORT MAP(scout5,co1,cl1,qout6,scout6);t1:seventranse PORT MAP(qout6,op2);process(co1)beginif (co1'event and co1='0') thenop<=op2&qout5&qout4&qout3&qout2&qout1;--结果显示end if;end process;end;--寄存器模块library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity save isport(op1:in std_logic_vector(26 downto 0);ro1:in std_logic;eout:out std_logic_vector(26 downto 0));end entity;architecture art4 of save issignal temp:std_logic_vector(26 downto 0);beginprocess(ro1)beginif ro1'event and ro1='1'then --上升沿判断temp<=op1;end if;eout<=temp;end process;end art4;--十进制计数器模块library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity cnt10 isport(clk2:in std_logic;en:in std_logic;clr:in std_logic;qout:out std_logic_vector(3 downto 0 );cout:out std_logic);end entity;architecture art3 of cnt10 issignal temp:std_logic_vector(3 downto 0 );beginprocess(clk2,en,clr)beginif (clr='1') then --重置时清0temp<="0000";elsif (en='1') thenif(clk2'event and clk2='1')then --上升沿判断进位if(temp="1001")thentemp<="0000";elsetemp<=temp+1;end if;end if;end if;end process;qout<=temp;cout<='1' when temp="1001" else '0';end art3;--分频模块library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity divide isport(clk1:in std_logic;cl:out std_logic;co:out std_logic;ro:out std_logic);end;architecture art1 of divide issignal preclk:std_logic;signal temp1:std_logic;signal temp2:std_logic;beginp1: process(clk1) --先进行2500分频variable count:integer range 0 to 2500;beginif clk1'event and clk1='1'thenif count=2499 thencount:=0;preclk<='1';else count:=count+1;preclk<='0';end if;end if;end process;p2: process(preclk) --依次二分频实现闸门beginif preclk'event and preclk='1'thentemp2<=not temp2;end if;end process;p3: process(temp2)variable count2:std_logic;beginif temp2'event and temp2='1'thencount2:=not count2;if count2='1'thenco<='1';temp1<='0';else co<='0';temp1<='1';end if;end if;end process;p4:process(temp2)beginif (temp1='1' and temp2='0') thencl<='1';elsecl<='0';end if;end process;ro<=temp1;end;--七段译码器模块library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity seventranse isport(clk6:in std_logic_vector(3 downto 0 );op2:out std_logic_vector(6 downto 0 ));end entity;architecture art5 of seventranse isbeginprocess(clk6)begincase clk6 iswhen "0000"=> op2<="1111110";when "0001"=> op2<="0110000";when "0010"=> op2<="1101101";when "0011"=> op2<="1111001";when "0100"=> op2<="0110011";when "0101"=> op2<="1011011";when "0110"=> op2<="1011111";when "0111"=> op2<="1110000";when others=> op2<="0000000";end case;end process;end art5;四、实验小结:实验要求用闸门信号控制计数器计时,于是在十进制计数器模块中添加使能信号en(en=‘1’计数器进行加1 计数,en=‘0’时计数器保持),将闸门信号作为使能信号接入,即可实现1s计数,1s显示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

控制和运算芯片,利用零中频正交解调原理,使用 DDS 芯片 AD9854 设计并制作了一款简易频率特

性测试仪。该测试仪能够输出 100 kHz~50 MHz 范围的正交信号,能正确的绘制被测网络的幅频特

性曲线和相频特性曲线。可通过键盘以 100 kHz 为步进频率进行扫频和点频输出。测试仪测给定

RLC 网络,中心频率的相对误差小于 0.1%,有载品质因数相对误差小于 2%。测试结果表明,该测

电子产品的生产和调试过程中,很多时候需要 理系统,利用零中频正交解调原理,采用 AD9854 设

测量设备或网络的频率特性,然而模拟式扫频仪硬 计并制作了一款频率特性测试仪。该测试仪能够输

件 设 计 复 杂 、功 耗 大 ,且 体 积 庞 大 、价 格 也 很 昂 贵 。 出 100 kHz~50 MHz 范 围 的 正 交 信 号 ,能 正 确 的 绘

| | VPHS = -RF IΦ( Φ(V ) INA - Φ(VINB) - 90°) + VCP

- 46 -

图 3 AD8302 典型应用电路

AD8302 的幅度和相位响应特性曲线如图 4、图 5 所示。在幅度测量过程中斜率为 30 mV/dB,在中心 点 0.9 V 处,其幅度比为 0 dB,幅度比在-30~+30 dB 之 间变化时,输出电压对应的范围为 0~1.8V;而在相 位测量过程中,斜率为 10 mV/度,中心点 0.9 V 所对 应的相位为 90 度,信号的相位在 0 到 180 度之间变 化时对应的输出电压从 1.8 V 到 0 V 之间变化 。 [3]

作 ,提 高 工 作 效 率 。 [1] 为 此 ,文 中 充 分 利 用 FPGA 和 DSP 的 优 势 ,基 于 FPGA+DSP 的 数 据 采 集 和 信 号 处

1 系统设计方案

收稿日期:2018-07-15 稿件编号:201807073

系 统 主 要 由 正 交 扫 频 信 号 源 模 块 、FPGA+DSP

线接口。TLV2548 具有高速模数转换器和多种控制

功能,可以达到设计要求。ADC 电路如图 6 所示。

2.3 被测网络

为 了 系 统 进 行 误 差 分 析 的 需 要 ,我 们 设 计 了 一

个 RLC 串联谐振电路,该电路的谐振频率为 20 MHz,

电路如图 7 所示。

设 计 原 理 为 :当 电 路 中

图 4 幅度响应特性曲线

图 5 相位响应特性曲线

图 3 中,C2 和 C8 起到低通滤波器的作用,经过计

算 ,我 们 取 幅 度 输 出 的 滤 波 电 容 C2=0.1 μF,相 位 输

出的滤波电容 C8=0.047 μF。 3)ADC 电路

放大器输出的信号需要通过 ADC 进行模数转

换 并 串 行 传 输 进 入 FPGA,本 设 计 中 ADC 芯 片 选 用

第 27 卷 第 8 期 Vol.27 No.8

电子设计工程 Electronic Design Engineering

2019 年 4 月 Apr. 2019

简易频率特性测试仪的设计与制作

濮 霞,李 楠,陶炳坤

(陆军工程大学石家庄校区 车辆与电气工程系,河北 石家庄 050003)

摘要:文中采用 FPGA 芯片 EP1C3T144C8、DSP 芯片 TMS320VC5416 和单片机 STC12C5A60S2 作为

Hale Waihona Puke 2.1 正交扫频信号源设计 正交扫频信号源由 AD9854 芯片来实现,该芯片

是集成度较高的 DDS 芯片,内部有两路正交 D/A 转 换 器 ,具 有 速 度 快 、性 能 高 的 优 点 ,且 频 率 分 辨 率 可 达 48 位 。 [2] 当 驱 动 时 钟 稳 定 度 较 高 时 ,通 过 编 程 的 方 式 产 生 稳 定 度 较 高 的 正 弦 和 余 弦 信 号 ,并 且 信 号 的相位和幅度都是可编程的,硬件电路简单,软件编

ωL

-

1 ωC

=

0

时 ,电 路 呈

纯阻性,电路中的电流达到最大,此时电路处于谐振

濮 霞,等 简易频率特性测试仪的设计与制作

图 6 ADC 电路图

图 7 RLC 串联谐振电路

图 1 频率特性测试仪结构框图

理核心,由 DDS 芯片 AD9854 作为正交扫频信号源, 根 据 零 中 频 正 交 解 调 原 理 ,实 现 测 试 双 端 口 网 络 幅

2

单元电路设计

频特性、相频特性的功能。AD9854 作为正交扫频信 号源,产生余弦和正弦两路信号,余弦信号作为激励 信 号 加 入 被 测 网 络 ,其 响 应 信 号 分 别 与 正 交 扫 频 信 号源产生的余弦和正弦信号通过 AD8302(包括乘法 器和滤波器)、放大器、ADC、FPGA 及 DSP 进行数据 变 换 、运 算 和 处 理 。 而 单 片 机 通 过 FPGA 串 行 通 信 进行交互,实现键控、显示、测量等功能。

作者简介:濮 霞(1977—),女,新疆沙湾人,硕士研究生,讲师。研究方向:电工电子技术教学研究及科研。

- 44 -

濮 霞,等 简易频率特性测试仪的设计与制作

信号处理模块、运算与滤波模块以及数模转换 ADC 模 块 、单 片 机 键 盘 输 入 及 显 示 模 块 等 组 成 。 简 易 频

率特性测试仪的结构框图如图 1 所示。 本简易频率特性测试仪以 FPGA+DSP 为控制处

test instrument

PU Xia,LI Nan,TAO Bing⁃kun (Shijiazhuang Campus of Army Engineering University,Shijiazhuang 050003,China)

Abstract: In this paper,FPGA chip EP1C3T144C8, DSP chip TMS320VC5416 and single chip microcomputer STC12C5A60S2 are used as control and computing chips. Using the Orthogonal demodulation principle,a simple frequency characteristic tester is designed and fabricated by DDS chip AD9854. The tester can output orthogonal signals in the range of 100KHz to 50MHz,and can correctly plot the amplitude- frequency characteristic curve and the phase- frequency characteristic curve of the tested network. The frequency sweep and point frequency output can be performed through the keyboard at a step frequency of 100 kHz. The tester measures the given RLC network,the relative error of the center frequency is less than 0.1%,and the relative error of the loaded quality factor is less than 2%.The test results show that the design of the tester is reasonable and meets the expected target requirements. The hardware circuit modules and software programs formed by this design can be used in practical teaching applications of electrical courses such as colleges and universities. Key words: frequency characteristic test;orthogonal demodulation;AD9854;FPGA;DSP

数字频率特性测试仪能够直观描述系统的频率特性 制被测网络的幅频特性曲线和相频特性曲线,可进

和动态特性,其优点是测量过程速度快、直观,测试 行扫频和点频输出,通过键盘可设置扫频范围、输出

方 便 、测 试 结 果 准 确 度 高 ,这 样 能 大 大 简 化 测 量 操 固定频率、控制测量光标,测试数据误差小,精度高。

试仪设计方案合理,达到了预期的指标要求。本设计形成的硬件电路模块和软件程序可以用于高

等学校等的电类课程的实践教学应用。